# プロセスインテグレーション、デバイス、および構造

# 概要

プロセスインテグレーション、デバイス、および構造(Process Integration, Devices, and Structure: PIDS)の章では、LSI に使われるデバイスと構造、新しいオプションの技術に関連した信頼性のトレードオフを踏まえた、LSI プロセスフローとそのインテグレーションを扱う。物理的寸法、キーデバイスの電気的パラメータ、受動素子、信頼性基準など、電気的要求値と特性が PIDS に含まれる。また、ターゲット値だけでなく統計的なばらつき幅も取り扱う。取り扱うデバイスはロジック、メモリ、それらの信頼性、無線通信用 Radio Frequency (RF)素子、アナログ/ミックストシグナル素子(Analog/Mixed-Signal; AMS)、新探求素子(Emerging Research Devices; ERD) である。無線通信用 RF と AMS の節は 2003 年版 ITRS から無線通信用途に注目した。これは無線通信が主な用途であることと、重要なテクノロジドライバになりつつあるためである。ERD の節は 2000 年 ITRS アップデート版から PIDS の章に加えられ、定量的な解析と種々な方法による評価を通して改版されてきた。

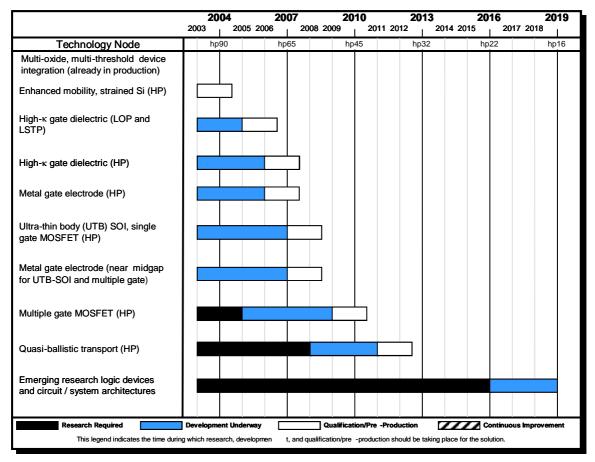

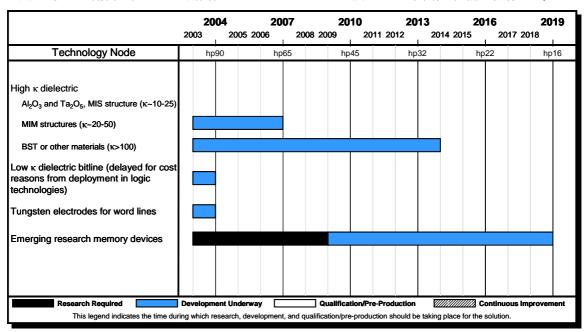

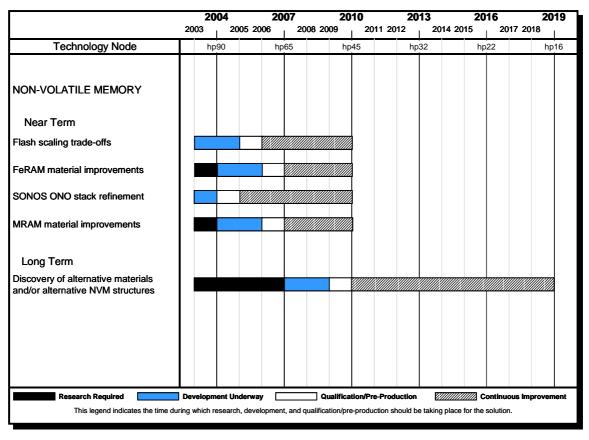

2003 年版 ITRS の PIDS の章には幾つかのキーとなるテーマがある。その一つが、トランジスタ性能向 上率のトレンドを維持するための、最先端ロジック技術の継続的かつ積極的なスケーリングである。この積 極的なスケーリングは、産業界に対して多くの重要な技術的革新を促進させている。例えば、高誘電率ゲ ート絶縁膜、メタルゲート電極など、材料とプロセスの変化を推進させた。長期的には薄膜 SOI、 マルチゲ ート MOSFET のような新しい構造をドライブしてきた。これらの革新的な技術が、加速されたペースで商品 に導入されることが期待されている。また、タイムリーな技術の解明、モデリング、信頼性の保障が産業界 にとって重要な課題となっている。二番目のテーマは幾つかのタイプの不揮発性メモリ(Non-Volatile Memory; NVM)である。シリコン-酸化膜-窒化膜-酸化膜-シリコン構造(Silicon-Oxide-Nitride-Oxide-Silicon; SONOS)、マグネティック RAM (Magnetic RAM; MRAM)は量産の時期が近づいており、メモリの 節で述べられている。三番目は無線通信システム用のバンド幅の広い(1GHz から 100GHz)、Si MOSFET、 バイポーラトランジスタ、SiGe-HBT、 - 族の FET や HBT である。四番目は、CMOS の範疇を超えた情 報処理能力を持つ、重要かつ新しい CMOS 後に向けたアプローチの紹介と評価である。 これはロードマッ プの終わりを越えて予測されており、ERD の節で詳しく述べられる。最後のキーのテーマは配線、消費電 力、信頼性、デバイス性能、コストを同時に満足させつつ種々な機能を一つの LSI で実現する混載技術 である。これは将来の LSI の重要なトレンドであるシステムオンチップ(System-on-a-Chip; SoC)応用領域 に関連した根本的なテーマである。SoC の課題は、幾つかの章で取り扱われるより大きな横断的な課題で あり、本章でも議論される。 特に、無線通信用の AMS 技術のところで議論される。 SoC 技術開発を促進す るために重要なことは、ロジックチップや AMS チップにメモリを混載したり、一つのチップに種々なタイプの トランジスタを搭載して、多様な機能の要求を満足することである。この章ではテクノロジーの進歩を促進さ せるトランジスタに主に注目する。一方で、システムインパッケージ(System-in-a-Package; SIP)も多様な機 能を満足させる手法である。多くの応用がある中、特に高密度に集積され、高性能かつ低コストユニットや RF、AMS 向けに SIP は適している。 これらは RF と AMS の節で述べられている。

ロードマップの目的は、従来の CMOS スケーリングトレンド(ムーアの法則)を維持するために、キーとなる技術要求と課題の解決に向けた手法を明確にすることと、課題解決に向けた研究開発を促進させることにある。特に、本章における解決策候補のリストアップとそれらに関しての議論の目的は、重要な技術課題に対しての解の例を示すことである。しかし、ここで挙げた解は包括的なものではなく、異なるアプローチの探求を制限するものではない。

#### ロジック

半導体デバイス生産の多くの割合をロジック LSI とメモリ LSI が占めている。この節には高性能ロジック 用および低消費電力ロジック用のトランジスタが含まれ、詳細な技術要求とその実現に向けた解決策候が 検討されている。キーとなる指標は速度性能、消費電力、集積度である。ここで着目しているのは技術開発を大きく前進させ最も高性能なトランジスタである。

### メモリー

ロジック LSI と同様に、メモリ LSI も半導体デバイス生産の中で大きな割合を示している。この章で取り扱うメモリのタイプは、DRAM と不揮発性メモリ(Non Volatile Memory; NVM)である。メモリ技術を牽引する汎用メモリを強調している。混載メモリチップは少しの時間差で汎用メモリと同じトレンドに従うと予想される。DRAMとNVMに対して、詳細な技術要求と解決策候補が述べられている。

上述したように、NVM に対しての技術要求と技術課題は、フラッシュ(NOR 型と NAND 型)、強誘電体メモリ(Ferroelectric RAM; FeRAM)、シリコン・酸化膜-窒化膜-酸化膜-シリコン型(Silicon-Oxide-Nitride-Oxide-Silicon; SONOS)、マグネティック RAM (Magnetic RAM; MRAM)を対象にしている。読み書き回数の多い NVM に限定しているため、ROM (Read Only Memory)や OTP (One-Time-Programmable)技術は含まない。

#### 信頼性

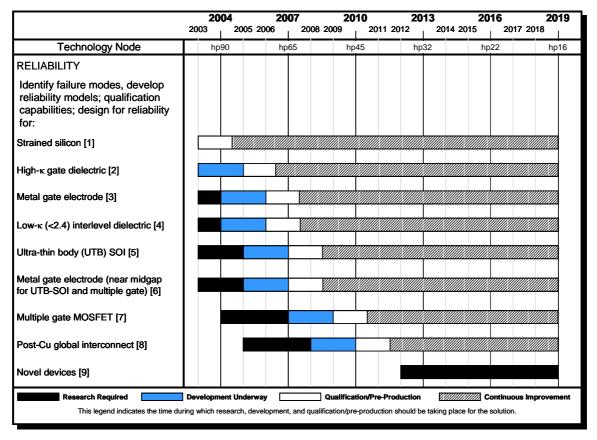

信頼性はプロセスインテグレーションにおいて重要な項目である。新しい技術ノード(Technology Nodes) は新材料と新プロセスの導入を要求するが、それらについての情報収集とデータベースの構築、新しい故障モードや欠陥のモデル化が間に合わない。プロセスインテグレーションは技術が習熟する前に完成する必要があるため、これまでの信頼性のレベルを維持することは困難になる。信頼性における不確かさは不必要な性能の要求、コスト増大、市場への製品投入時期の遅れなどを引き起こす。これらはテスト、ウエハーレベルの信頼性についても困難な技術課題を課す。実装の信頼性は新材料、新プロセス、狭ピッチのボンディング、耐環境性、接着性などに敏感である。

### 無線通信用 RF とアナログ/ミックストシグナル技術

無線通信応用における急速な半導体市場の成長の源は、RF および AMS LSI の高性能化である。RF および AMS LSI の機能は、アナログ回路、RF 回路、アナログ/RF 信号増幅、アナログ信号とデジタル信号の変換、周波数合成/変換などがある。無線通信システムの要求を満たすための技術要求は非常に多様で、しばしばそれらは矛盾した技術要求になったり、デジタルの場合の技術要求と大き〈異なる。2001

ITRS のミックストシグナルの節と比べて、2003 年版の RF および AMS の節のスコープと内容は本質的に拡張されている。始めて化合物半導体(ここでは III-V 族)デバイスとその技術が ITRS に含まれた。応用の周波数に依存して、RF および AMS 技術要求と解決策候補は四つのグループで述べられている。それらは、1) AMS (DC -10 GHz)、2) RF トランシーバ (0.8-10 GHz)、3)パワーアンプと電力制御 (0.8-10 GHz)、4)ミリ波 (10-100 GHz)である。これらの周波数はシステムの動作周波数であり、それらのシステムで使われるデバイスの周波数ではない。異なる材料を使った、異なる構造の種々なトランジスタに加えて、集積された受動素子についての技術要求と技術課題にも言及している。

# 新探求素子 (Emerging Research Devices; ERD)

ERD の目的はロードマップを延長させる概念の可能性を示す発明や研究を促進させることにある。また、興味深い新しい情報処理技術のアプローチに対してバランスのとれた紹介を行うことと、限定された技術課題の簡単な議論と、ロードマップが延長することへの重要な貢献を説明することを目的としている。これらを通して、二つの目的を目指している。一つは、マイクロエレクトニクス技術をこのロードマップの時間フレームの終わりまで進歩させ続けるために、従来と異なる CMOS 構造とメモリー技術の候補を提供することである。二番目は現状のロードマップの終わりを超えて、情報、信号処理能力を引き伸ばすことを目的としたロジックとアーキテクチャの新しいコンセプトの紹介と評価(保障なしで)である。ERD についての活動は、バルクおよびノンクラシカル CMOS と、CMOS の次のマイクロエレクトロニクスの領域の間の橋渡しをすることである。

# 困難な技術課題(DIFFICULT CHALLENGES)

表 46a Process Integration Difficult Challenges—Near-term

| Difficult Challenges ≥ 45 nm/Through 2010                                                                 | Summary of Issues                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-performance applications: meeting performance and power dissipation requirements                     | Cost effectiveness, process control, and reliability of very thin oxy-nitride gate dielectrics, especially considering the high gate leakage                                                                                                                                                                                                     |

| for highly scaled MOSFETs                                                                                 | Difficulty in controlling short-channel effects for highly scaled devices                                                                                                                                                                                                                                                                        |

|                                                                                                           | Negative impact of high channel doping needed for highly scaled devices. Also, the difficulty in controlling threshold voltage due to statistical fluctuations in the doping                                                                                                                                                                     |

|                                                                                                           | Need to reduce series S/D parasitic resistance                                                                                                                                                                                                                                                                                                   |

|                                                                                                           | Controlling static power dissipation in the face of rapidly increasing leakage: architecture and circuit design improvement and innovation will be needed.                                                                                                                                                                                       |

| 2. Low-power applications: meeting performance and leakage requirements for                               | Early availability of manufacturing-worthy high-κ gate dielectrics is necessary to meet stringent gate leakage and performance requirements.                                                                                                                                                                                                     |

| highly scaled MOSFETs                                                                                     | Slow scaling of $V_{dd}$ for low standby power logic will make overall device scaling difficult.                                                                                                                                                                                                                                                 |

|                                                                                                           | Rapid scaling of V <sub>dd</sub> for low operating power logic will make overall device scaling difficult.                                                                                                                                                                                                                                       |

| 3. Assuring the reliability and implementing into manufacturing of multiple material, process, and        | Multiple material changes projected: high-κ gate dielectric, metal gate electrodes, strained Si, nickel silicide by 2008 or so                                                                                                                                                                                                                   |

| structural changes in a relatively short period of time                                                   | Elevated S/D (selective epi)                                                                                                                                                                                                                                                                                                                     |

|                                                                                                           | Ultra-thin body (UTB) SOI by 2008 or so, followed by multiple-gate structures. Near mid-gap metal gate electrodes will be desirable to set the threshold voltage for UTB SOI.                                                                                                                                                                    |

|                                                                                                           | Difficulty in ensuring reliability of all these new materials, processes, and structures in a timely manner                                                                                                                                                                                                                                      |

| 4. Implementation of DRAM, SRAM, and high-<br>density nonvolatile memory (NVM) for scaled<br>technologies | DRAM main issues—adequate storage capacitance for devices with reduced feature size, including difficulties in implementing high-κ storage dielectrics; access device design; holding the overall leakage to acceptably low levels; and deploying low sheet resistance materials for bit and word lines to ensure desired speed for scaled DRAMs |

|                                                                                                           | SRAM—Difficulties with maintaining adequate noise margin and controlling key instabilities with scaling. Also, difficult lithography and etch issues with scaling                                                                                                                                                                                |

|                                                                                                           | NVM, flash—Scaling of tunnel dielectric and interpoly dielectric involves many complex tradeoffs. Dielectric material properties and dimensional control are key issues                                                                                                                                                                          |

|                                                                                                           | NVM, FeRAM—Ferroelectric material properties and dimensional control. Sensitivity to IC processing temperatures and conditions                                                                                                                                                                                                                   |

|                                                                                                           | NVM, SONOS—ONO stack dimensions and material properties, including nitride layer trap distribution in space and energy                                                                                                                                                                                                                           |

|                                                                                                           | NVM, MRAM—Magnetic material properties and dimensional control. Sensitivity to IC processing temperatures and conditions                                                                                                                                                                                                                         |

| 5. High-performance and low-cost RF and                                                                   | Signal isolation                                                                                                                                                                                                                                                                                                                                 |

| analog/mixed-signal solutions                                                                             | Optimizing RF/analog CMOS devices with scaled technologies: mismatch, $1/f$ noise, and leakage with high- $\kappa$ gate dielectrics                                                                                                                                                                                                              |

|                                                                                                           | High density integrated passive element scaling and use of new materials: Q-factor value for inductors; matching and linearity for capacitors                                                                                                                                                                                                    |

|                                                                                                           | Reduced power supply voltages: degradation in SNR (signal-to-noise ratio) and signal distortion performance                                                                                                                                                                                                                                      |

|                                                                                                           | Reduced device breakdown voltage in scaled technologies                                                                                                                                                                                                                                                                                          |

|                                                                                                           | High-frequency devices with increased operating voltage for base station applications                                                                                                                                                                                                                                                            |

|                                                                                                           | Compound semiconductor substrates with good thermal dissipation and process equipment for fabrication at low cost                                                                                                                                                                                                                                |

|                                                                                                           | See section on RF and A/MS Technologies for Wireless Communications for detailed discussion of these issues                                                                                                                                                                                                                                      |

表 46b Process Integration Difficult Challenges—Long-term

| Difficult Challenges < 45 nm/Beyond 2010                                                                                                                | Summary of Issues                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6. Implementation of advanced, non-classical CMOS with enhanced drive current and acceptable control of short channel effects for highly scaled MOSFETs | Advanced non-classical CMOS (e.g., multiple-gate, ultra-thin body [UTB] MOSFETs) with lightly doped body will be needed to effectively scale MOSFETs to well under 20 nm gate length (Lg).                                        |

|                                                                                                                                                         | Most likely, advanced material solutions such as strained Si (enhanced mobility) channels, elevated source/drain, high-κ gate dielectric, metal gate electrode, etc., will be utilized along with the advanced non-classical CMOS |

|                                                                                                                                                         | Particularly for the highly scaled UTB MOSFETs required towards the end of the Roadmap, with body thickness well under 10 nm, electrical performance and the impact of quantum effects are not well understood                    |

|                                                                                                                                                         | To attain adequate drive current for the highly scaled MOSFETs, quasi-<br>ballistic operation with enhanced carrier saturation velocity appears to<br>be needed                                                                   |

|                                                                                                                                                         | See Emerging Research Devices section for more detail.                                                                                                                                                                            |

| 7. Dealing with atomic-level fluctuations and statistical process variations in sub-20 nm MOSFETs                                                       | Fundamental issues of atomic-level statistical fluctuations for sub-20 nm MOSFETs are not completely understood, including the impact of quantum effects.                                                                         |

| 8. Identifying, selecting, and implementing new memory                                                                                                  | Highly scaled, dense, fast, non-volatile memory will become highly desirable                                                                                                                                                      |

| 8. Identifying, selecting, and implementing new memory structures                                                                                       | Increasing difficulty is expected in scaling DRAMs, especially scaling down the dielectric equivalent oxide thickness, attaining the very low leakage currents that will be required, and reducing the cell area factor           |

|                                                                                                                                                         | All of the existing forms of nonvolatile memory face limitations based on material properties. Success will hinge on finding and developing alternative materials and/or development of alternative emerging technologies.        |

|                                                                                                                                                         | See Emerging Research Devices section for more detail.                                                                                                                                                                            |

| 9. Identifying, selecting, and implementing novel interconnect schemes                                                                                  | Eventually, it is projected that the performance of copper/low-κ interconnect will become inadequate to meet the speed and power dissipation goals of highly scaled ICs.                                                          |

|                                                                                                                                                         | Solutions (optical, microwave/RF, etc,) are currently unclear.                                                                                                                                                                    |

| 10. Toward the end of the Roadmap or beyond, identification,                                                                                            | Will drive major changes in process, materials, device physics, design, etc.                                                                                                                                                      |

| selection, and implementation of advanced, beyond-CMOS devices and architectures for advanced information processing                                    | Performance, power dissipation, etc., of beyond-CMOS devices need to extend well beyond CMOS limits.                                                                                                                              |

|                                                                                                                                                         | Beyond-CMOS devices need to integrate into a CMOS platform. Integration of the two may be difficult, especially for mixed signal.                                                                                                 |

|                                                                                                                                                         | See <i>Emerging Research Devices</i> sections for more discussion and detail.                                                                                                                                                     |

#### PIDS に関する困難な技術課題の説明

[1] 高性能用途 - 高度に微細化の進んだ MOSFET における性能と消費電力要求の整合 - ここでの基本的な課題は、ゲート酸窒化絶縁膜を EOT(Equivalent Oxide Thickness)で 1.0 nm 以下まで延命させることである。このように薄い酸窒化膜の信頼性を保証し、その膜厚のばらつき制御を行うことが大きなチャレンジであり、この酸窒化膜の大きなゲートリーク電流が重要な課題となる。急速に進むトランジスタのスケーリングに伴って、ソース/ドレインの寄生抵抗の許容される要求値に合わせていくことが、困難になりつつある。また、MOSFET のスケーリングによって短チャネル効果の抑制が困難になり、望ましくない高濃度のチャネルドーピングが求められている。さらに、チャネル不純物の統計的なばらつきが顕在化し、結果としてしきい値のばらつきが大きくなる。最終的にはチップの複雑度が増加することや、ここ数年に実現できる技術では大きなリーク電流が流れてしまうことから、チップの静的な消費電力はとりわけ制御が困難になると考えられている。このため、要求性能や消費電力に合致させるために、回路設計やアーキテクチャの革新が求められている。

- [2] 低消費電力用途 高度に微細化の進んだ MOSFET における性能とリーク電流要求の整合 重要な課題は、切迫してきたリーク電流の規格を満たすために、およそ2006年までに高誘電率ゲート絶縁膜が必要になることである。LSTPにおいては、電源電圧 (Vdd) がほとんどスケーリングされないために、横方向電界が許容できないほど大きくなってしまい、短チャネル効果やおそらく信頼性上の問題の制御を困難にする。LOPにおいては、電源電圧 (Vdd) が比較的速くスケーリングされるため、デバイスの性能要求に合わせていくことが困難になるだろう。

- [3] 比較的短い期間に複数材料の導入や、プロセスや構造の変更の製造への適用と信頼性の確認 MOSFET を適切にスケーリングし、デバイスの性能やリーク電流、その他の要求を満足させるために、高誘電率ゲート絶縁膜やメタルゲート電極、持ち上げソース/ドレイン、ニッケルシリサイドなどの多くの主要プロセスや材料の革新(イノベーション)が 10 年以内に実現される必要があると予測されている。適切な時期にこれらすべての主要な変更を製造現場に取り入れることは困難であろう。結果として、極薄膜 SOI MOSFET から始まって、極薄膜ボディーにマルチゲートを組み合わせた MOSFET へ移っていく、新しい構造の MOSFET が実現されると予測され、これが製造での主要なチャレンジになるであろう。さらに、これらすべての革新(イノベーション)の信頼性を適切な時期に確認することは非常に困難と思われる。

- [4] 微細化された技術による DRAM や SRAM、高密度不揮発メモリ(NVM)の構築 DRAM では、 高誘電率絶縁材料の実用化が主要な課題であり、たとえセルサイズが縮小されても、結果としてセル当り の適切な蓄積容量を確保するための MIM 構造の実現が必要となる。また、適当なデータ保持時間を確 保するために、絶縁膜のリーク電流や電荷蓄積部の接合リーク電流、アクセストランジスタのリーク電流を 含むすべてのリーク電流を制御することが重要である。必要なアクセストランジスタの性能を得ようとすると き、低リーク電流の要求は問題となる。 SRAM では、スケーリングに伴う困難さが予想されている。特に受 容可能なノイズマージンの維持と、ホットエレクトロンによる不安定性と負バイアス温度ストレスによる不安定 性(NBTI)などを制御することは困難になる。SRAM は、典型的には高速のオンチップメモリとして使われる ため、これらの SRAM の課題を解決することがシステム性能実現に重要となる。利用可能な不揮発の半導 体メモリには、二つの課題が内在する。第一の課題は、それぞれの NVM のメモリ要素構造がベースとな る CMOS 技術と幾分異なることと、メモリセルのスケーリングを行いながらこれらの困難さに適応していくこ とは、幾つかの困難な課題を引き起こし、これらの課題は、どの NVM を採用するかに依存して変わってく る。第二の課題は、メモリセルのセット/リセットで使用される通常のメモリ動作が、一般的に材料にストレスを 与えることであり、セル特性の劣化が想定される。通常劣化はデバイス固有の特性と言うより、欠陥の関係 するメカニズムに連動している。書き換え耐性やデータ保持特性への要求により、デバイスの確実そうな性 能に関してユーザにガイドを与えるとともに、利用の安全範囲を決める示唆を与える。両方のパラメータとも に、長期の振る舞いを現実的に予測できるようにする継続的なチャレンジが必要である。故障原因の同定 は困難であり、リアルタイムテストは現実的ではない。

- [5] 高性能、低コストの RF およびアナログ/ミックス・シグナルの解決策 スケーリングされる技術において、同一チップ上のデジタル/アナログ/RF などの異なるブロック間の信号の分離は、集積化されたシステムソリューションの中で特に次元の異なったチャレンジである。スケーリングされる技術において、能動素子のスケーリングや電源電圧の低減、新規材料の利用は、デバイスの整合性やノイズ、線形性、ノイズ

信号比、デバイスの耐圧に対して、重大な課題となる。また、高集積や高いQ値、良好な整合性、良好な線形性を有する受動素子を作ることも課題である。無線情報通信分野で必要となる高周波への要望や高耐圧デバイスは、継続的なデバイスの革新や化合物ICのための低コストの製造インフラが要求される。最後に、アナログ/RFを組み込む困難さやコスト(結果として、MEMS や GaAs や InP などの化合物半導体を含む)、およびオンチップの高性能デジタル機能やモジュールは、時間とともに増大していくことが予想される。

- [6] 高度にスケーリングの進んだ MOSFET において、ドライブ電流を増強し、短チャネル効果を受容可能なレベルに抑制した進歩的で非古典的な CMOS の実現 長期においてトランジスタのゲート長が20nm より十分に短い領域まで描かれたとき、極薄膜ボディーや、低濃度チャネル領域を有するマルチゲート MOSFET などの先進的で非古典的な構造が、デバイスを効果的にスケーリングするために活用され、また特に高度にスケーリングされたデバイスにおいて短チャネル効果を制御するために活用される。上記された高誘電率ゲート絶縁膜やメタルゲート電極、歪シリコン、持ち上げソース/ドレインなどの他の材料やプロセスによる解決策は、非古典的 CMOS 構造に対応して組み込まれていくことが予想される。最後に、これらの先進的で高度にスケーリングの進んだ MOSFET において、飽和速度が増強され、結果として駆動電流の増大が期待できる準バリスティック動作が、性能要求に整合させるために必要になることが予想される。これらの先進的で非古典的な MOSFET の作りこみと準バリスティック動作の理解と制御が、産業において主要なチャレンジであると考えられる。

- [7] 20nm 以下の MOSFET における原子レベルのふらつきや統計的なプロセス変動の扱い 非常に短チャネルのプレーナ型のバルクデバイスにおいて、空乏層領域の不純物の総数が相対的に減少し、よって統計的なばらつきが相対的に大きくなり、しきい値制御に制約を課することになる。さらに、そのような短チャネルデバイスの寸法制御の困難さが増しており、さらに MOSFET の電気特性に影響する統計的なプロセスばらつきが増加している。極薄膜ボディーや完全空乏型、非古典的デバイスにおいて、ボディーの膜厚やゲート長の統計的なばらつきが、主要な課題になると予想される。

- [8] 新しいメモリ構造の確認、選択と実現 長期にわたってスケーリングされていく DRAM において、製造の困難さは増大していくと予想され、高密度で、高速で、不揮発性を有し、特に消費電力を下げるための新しいメモリ構造へのニーズが増えると予想される。そのような先進的な不揮発構造の実現が、主要な課題である。

- [9] 新しい配線構成の確認、選択と実現 銅の抵抗は、スケーリングのよって下げることはできないし、k値が 1 から 1.5 くらいで低誘電率の限界に到達する。その時、更なる配線特性の改善は、新規のアーキテクチャーや材料などの解決策が必要となる。

- [10] ロードマップの終端に向けて、あるいはそれを超えた時点で、先進的な情報処理のための先進的な非 CMOS デバイスやアーキテクチャを導入 ロードマップの終端、およびその先に向けて、MOSFET のスケーリングは効果をもたらさなくなり、また非常にコストの掛かるものとなる。そのため先進的な非 CMOS の解決策が、性能や消費電力、集積度などの改善を継続していくために必要となる。そのよう

な解決策は、その時までに開発され使用されている、高性能で適正なコストで製造される非常に高密度の CMOS ロジックのメリットを有する CMOS 基本技術と一緒に集積化されることになる。

# ロジックに対する技術要求と解決策候補

# ロジックに対する技術要求

技術要求の表は、高性能版と低消費電力版デジタル IC の MOSFET の要求に対応したものである。 高 性能版のロジックとは、デスクトップやサーバー用などのマイクロプロセッサユニット(MPU)などの非常に複 雑で高性能であるが、大きな消費電力のチップを想定している。低消費電力版のロジックとは、許容消費 電力、即ち許容消費電流が電池の寿命で制限される携帯システムを想定している。低消費電力版のロジ ックは、低動作電力ロジック(Low Operation Power, LOP)と低待機電力ロジック(Low Standby Power, LSTP)に分類される。低動作電力用チップは、大容量電池を有したノート型コンピュータのような、比較的 高性能なモバイル用途であり、動作時の消費電力削減に注力している。低待機電力用チップは、小容量 の電池を有する携帯電話のような、それほど性能を要求されない民生用品に使用され、実現可能な最も 小さい待機時の消費電力、すなわち実現可能な最も小さいリーク電流に重点が置かれている。高性能IC 用のトランジスタは、高性能ロジックのために物理的なゲート長(および、トランジスタに係わる他のパラメー タも)が最も急速にケーリングされることによって、最も高い性能を示すが、リーク電流も最も多い。低動作 電力チップにおけるトランジスタは、幾分性能が低いが、十分に小さいリーク電流を実現する。一方、低待 機電力用のトランジスタは、最も性能が低いが、最も少ないリーク電流を実現する設定となる。低動作電力 トランジスタにおいて、高性能トランジスタのゲート長からのタイミング遅れは 2 年であり、歴史的な動向や 携帯用途における低リーク電流の要求を反映している。低待機電力トランジスタにおいては、高性能トラン ジスタのゲート長からのタイミング遅れは3年であり、超低リーク電流の要求を反映している。

ロジックの技術要求のテーブルを作成するために、スプレッドシートに組み込まれた単純化されたモデ ルが用いられた。これらのモデルは、リーク電流や飽和電流などのトランジスタの重要な電気特性に影響 を及ぼす電源電圧(Vdd)、等価ゲート酸化膜厚(EOT)、ゲート長などのキーとなる入力パラメータで構成さ れている。モデルから導出される一つの重要なパラメータは、イントリンシックな MOSFET の遅延時間( =CV/I である。ここで、C は寄生して発生するゲートオーバーラップやフリンジ容量を含むミクロンあたりの ゲート容量であり、V は電源電圧(Vdd)、Iはチャネル幅1ミクロン当りの飽和電流である。 は、イントリン シックな MOSFET の遅延時間に対する良い指標であり、よって1/ は、イントリンシックな MOSFET の最 大スイッチング周波数の指標となり、トランジスタ性能の主要な指標となる。技術要求の表のパラメータ値を 決定するために、リーク電流や 1/τ など重要な出力パラメータの目標値が設定されている。入力パラメータ は、スケーリング則やエンジニアリング的な判断、デバイスの物理的な原則に則って仮設定し、目標値を達 成するまで入力パラメータをスプレッドシート上で種々変えて計算を繰り返し、最終的な入力パラメータの 値を設定した。(ロジックの技術要求の表を作るのに使用された詳細のスプレッドシートはhttp://public.itrs.net で確認できる。) 各テーブルの予測されたパラメータセットの値は、特別なシナリオを反映してキーとなる 出力パラメータのターゲット値を満足するようなに設定されている。各テーブルのスケーリングシナリオを設 定する上で追加された目標は、同じ時間軸でできるだけ系統立った入力パラメータを用いて、high-k ゲー ト絶縁膜やメタルゲート電極、持ち上げソース/ドレイン、非古典的 CMOS トランジスタ構造(解決策候補の

図や説明を参照のこと)などの主要な技術革新の、予想される必要時期をできる限り遅らせることであった。しかし、調整することのできる入力パラメータが数多くあり、また出力パラメータがこれら多くの入力パラメータの複雑な関数になっているため、主要な出力パラメータの目標値を達成する他の入力パラメータの組合せ(すなわち、異なるスケーリングシナリオに従った)が存在しうる。例えばあるシナリオとして、ゲートリーク電流が急激に増大する、EOT を急速にスケーリングする場合、許容範囲にゲートリーク電流を抑えるために high-k ゲート絶縁膜の早期の導入が必要になる。他のスケーリングシナリオでは EOT をゆっくりとスケーリングさせることができる。この場合、ゲートリーク電流はゆっくり増加し、結果として high-k ゲート絶縁膜の導入を遅らせることができる。しかし、ゲート長やチャネルドーピングなどの他の幾つかのパラメータは、EOT のゆっくりとしたスケーリングを補償し、同じ出力パラメータを達成するために、より早くスケーリングさせなければならない。よって、これらのテーブルのスケーリングシナリオは、業界に良い指針を設定するが、各技術ノードで各メーカの採用する実際の道筋は相当食い違うことになると考えられる。

高速トランジスタの表において、作成の基準になるのは MOSFET の性能指標である 1/ $\tau$  である。1/ $\tau$  の目標は、過去の性能向上率に整合する年率平均 17%の向上である。表のその他のパラメータは、上記したように、この目標値を達成できるように設定されている。表から目標に合ったいくつかの重要な結果が読み取れる。NMOSFET の飽和電流 Id,sat は、1/の 17%/年の増大を維持するために、ロードマップの設定期間を通してかなり着実に増加していく。ソース/ドレイン間のサブスレッショルドリーク電流 Isd,leak は、2003 年において 0.03uA/um と相対的に大きいし、飽和しきい値電圧 Vt を年とともに減少させるために、年とともに増大していく(長期的には 0.1uA/um 以上となり、その時サブスレショルドリーク電流はかなり大きくなる)。Id,sat は、ゲートオーバードライブ(Vdd-Vt)に強く依存し、Vdd はデバイスのスケーリングと伴に低減されるので、Id,sat をある値以上に維持するためには、Vdd の減少に沿って Vt も減少させなければならない。しかし、(1/ Isd,leak)は、指数関数的に Vt に依存するため、Isd,leak は上記したように年と伴に増大する。この Isd,leak の増加は、スケーリングの沿った Vdd の減少にもかかわらず、一般的にデバイスのスケーリングと伴に増大する単位チャネル幅あたりの静的な消費電力の増加となり、この静的な消費電力は、チップの消費電力において重要な意味を持つようになる。(下記で議論を行う)。

高性能チップにおいては、微細化に伴うトランジスタのサブスレショルド電流は急激に増大するが、静的な消費電力を許容値以下に保つ必要がある。一つの一般的な解決策は、チップ内に低 Vt の高速トランジスタと高 Vt でゲート酸化膜が厚い低リークトランジスタの、二種類以上のトランジスタを搭載することである。低リークトランジスタは、高速トランジスタと比べて飽和電流は小さく、低いデバイス性能(デバイスの真性遅延時間  $\tau$  が大きい)である。高速トランジスタは、クリティカルパスや常時スイッチングしている回路にだけ使用され、低リークトランジスタはその他の全ての所で使われる。低リークトランジスタの積極的な使用は、チップ性能をそれほど犠牲にせずに静的な消費電力を大幅に低減させる。 静的な消費電力を縮小する電流の回路やアーキテクチャーとして、パスゲートを用いて電源とグランド間のパスを電気的に遮断するものや、回路ブロックのパワーを減らすテクニックなどがある。他の方法として、ウエルにバイアスを印加して、動的に Vt の制御を行う方法がある。よって、スケーリングされた高性能 IC の現実的な姿は、静的な消費電力に関して複数のしきい値を持つトランジスタを使用した、デバイス/回路/アーキテクチャーを活用するというものである。技術要求の表においては、高性能トランジスタが技術を牽引するので、このトランジスタだけを扱っている。

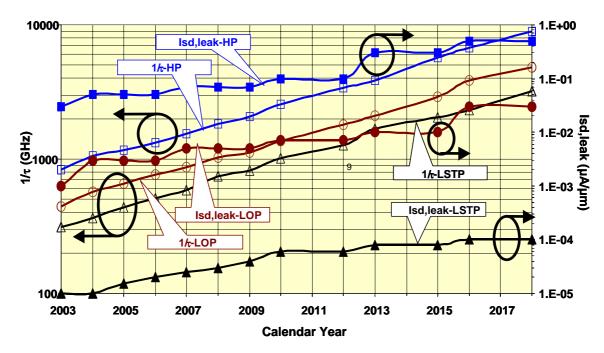

低消費電力チップにおいて注目される出力パラメータは、ソース/ドレイン間のサブスレッショルドリーク 電流(Isd,leak)であり、LSTPでは特にこの値は小さい。上記で議論したように、2003年の LOPの Isd,leak の値は 1nA/um であるが、LSTP の Isd,leak の値は 10pA/um である。両者の値は共に、スケーリングに対 応して緩やかに増大する。他のすべてのパラメータの値は、ターゲットの Isd,leak に整合するように選ばれ、 結果としてのデバイス性能(1/)の平均的な改善率は、歴史的に LOP、LSTP ともにおよそ年率 17%で ある。重要な課題の一つは、低消費電力トランジスタの比較的緩やかな電源電圧のスケーリングである。 LSTP 関しては、表 48c と 48d を参照のこと。これはサブスレショルドリーク電流の厳しい要求を満たすため に、Vt のスケーリングを比較的抑制したためである。電源電圧は次の二つの理由で Vt のスケーリングに 追随しなければならない。その理由は、目標の性能を得るためにゲートオーバードライブ(Vdd-Vt)は相対 的に大きくなければならないことと、十分なスイッチングノイズマージンを確保するために電源電圧は Vt の 2.3 倍以上でなければならないことである。動的な消費電力は電源電圧の2乗に比例するため、低消費電 力トランジスタの消費電力は高速用に比べて緩やかにスケーリングされるが、このタイプの活性化の度合 いは相対的に小さいと期待されるので、非常に小さいリーク電流によって静的な消費電力が下げられるこ との効果の方が大きい。他の課題は、横方向電界(~電源電圧/ゲート長)である。電源電圧(Vdd)のゆ っくりとしたスケーリングにより横方向電界がスケーリングと伴に急激に増大し、この結果、短チャネル効果 抑制を難しくするだけでなく、長期信頼性で問題を引き起こす。LSTP ロジックと対比して、LOP ロジック (LOPの技術要求の表 48aと 48b を参照のこと)用の電源電圧(Vdd)は比較的速〈スケーリングし、動作時 の消費電力(Vdd の二乗に比例する動的な消費電力)を最小化することに重点が置かれる。しかし、 Isd,leak は LSTP のものより大きく、飽和領域でのしきい値は十分に低い設定であり、相応のゲートオーバ ードライブ(Vdd-Vt)と適当な回路ノイズマージンが得られる。高性能版および LOP、LSTP の Isd,leak と MOSFET の性能指数(1/ )のスケーリングを図22に図示している。予想通り、高性能版ロジックの Isd,leakと1/ が一番大きく、LOP 用ロジックが中間で、LSTP 用のロジックが最も小さくなる。

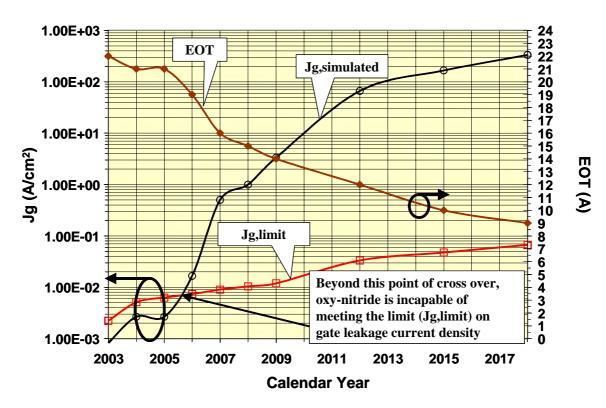

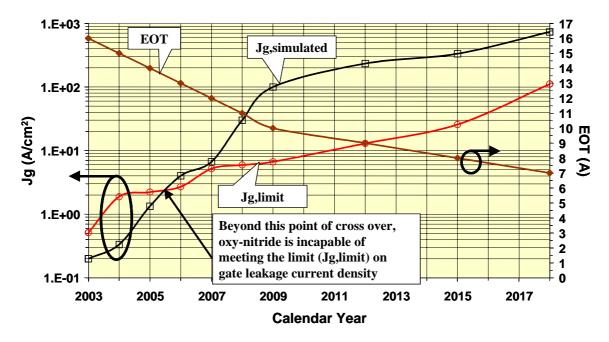

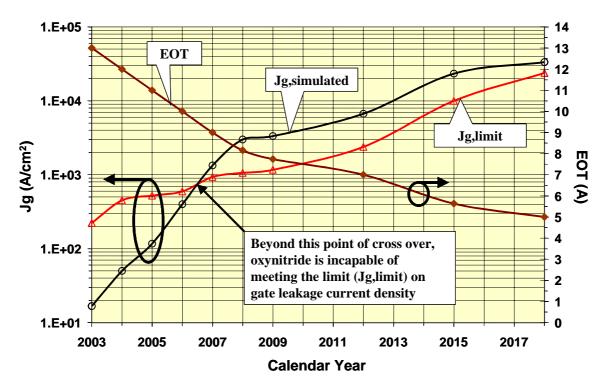

スケーリングによって酸窒化膜のゲート絶縁膜がますます薄くなるにつれて、ゲートリーク電流が重要な ポイントとなり、ゲートリーク電流密度の制限に酸窒化膜が適合するかが、決定的な課題となる(表 47a、 47b と 48a から 48d 及び注釈[2]と[5]を参照のこと)。FEP-TWG とノースカロライナ州立大学において、酸 化膜を通した直接トンネリング電流密度の詳細なシミュレーションが行われ、技術要求の表でスケーリング された Vdd と EOT を用いてトンネルによるゲートリーク電流密度の予想値が計算された。LSTP と LOP、 高性能ロジックにおいて、これらの計算されたゲートリーク電流密度と、システムからの要求であるゲートリ ーク電流密度の制約を比較し、図 23 から 25 にそれぞれ示した。ここで、Jg,limit はゲートリーク電流密度 の制約であり、Jg,simulated はシミュレーションより求められたゲートリーク電流密度である。また、技術要求 の表毎に EOT を参考としてプロットしている。 LSTPと LOP のトランジスタにおいて、二つの Jg は、2006 年 の直前に交差する。よって、2006年以降、直接トンネルのために酸窒化膜ではリーク電流の制約をクリア できない。 特に LSTP においては、 2006 年以降 Jg, simulated の曲線は、 Jg, limit の曲線から急速に乖離し ており、もし 2006 年以降にゲート絶縁膜として酸窒化膜を使い続けるとゲートリークは急速に規格から外 れること意味している。図 23 から 2004 年と 2005 年で EOT が同じであり、この期間ゲートリークの増加は ゆっくりに進み、酸窒化膜をゲート絶縁膜として利用できるように調整していることに注意すべきである。高 性能版のロジックにおいては、図 25 から酸窒化膜のゲート絶縁膜は、2007 年度以降ゲート電流密度の制 約に適合しなくなる。主要な解決策候補は、酸窒化膜の代わりに high-k ゲート絶縁膜を使うことである。更 なる詳細は、ロジックの解決策候補の章を参照のこと。

$\square$  22 1/ $\tau$  and  $I_{sd,leak}$  Scaling for High-performance (HP), Low-operating Power, and Low-standby Power Logic

**Z** 23 LSTP Logic Scaling-up of Gate Leakage Current Density Limit and of Simulated Gate Leakage due to Direct Tunneling

**Z** 24 LOP Logic Scaling-up of Gate Leakage Current Density Limit and of Simulated Gate Leakage due to Direct Tunneling

**Z** 25 High-performance Logic Scaling-up of Gate Leakage Current Density Limit and of Simulated Gate Leakage due to Direct Tunneling

# 13 プロセスインテグレーション、デバイス、および構造

表 47a High-performance Logic Technology Requirements—Near-term

| Year of Production                                                                                                | 2003           | 2004     | 2005     | 2006     | 2007     | 2008     | 2009     |

|-------------------------------------------------------------------------------------------------------------------|----------------|----------|----------|----------|----------|----------|----------|

| Technology Node                                                                                                   |                | hp90     |          |          | hp65     |          |          |

| DRAM ½ Pitch (nm)                                                                                                 | 100            | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                                | 120            | 107      | 95       | 85       | 76       | 67       | 60       |

| MPU/ASIC ½ Pitch (nm)                                                                                             | 107            | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU Printed Gate Length (nm)                                                                                      | 65             | 53       | 45       | 40       | 35       | 32       | 28       |

| MPU Physical Gate Length (nm)                                                                                     | 45             | 37       | 32       | 28       | 25       | 22       | 20       |

| Physical gate length high-performance (HP) (nm) [1]                                                               | 45             | 37       | 32       | 28       | 25       | 22       | 20       |

| EOT: equivalent oxide thickness (physical) for high-performance (nm) [2]                                          | 1.3            | 1.2      | 1.1      | 1.0      | 0.9      | 0.8      | 8.0      |

| Electrical thickness adjustment for gate depletion and inversion layer effects (nm) [3]                           | 0.8            | 0.8      | 0.7      | 0.7      | 0.4      | 0.4      | 0.4      |

| Equivalent electrical oxide thickness in inversion (nm) [4]                                                       | 2.1            | 2.0      | 1.8      | 1.7      | 1.3      | 1.2      | 1.2      |

| Nominal gate leakage current density limit (at 25°C) (A/cm²) [5]                                                  | 2.2E+02        | 4.5E+02  | 5.2E+02  | 6.0E+02  | 9.3E+02  | 1.1E+03  | 1.2E+03  |

| Nominal power supply voltage (V <sub>dd</sub> ) (V) [6]                                                           | 1.2            | 1.2      | 1.1      | 1.1      | 1.1      | 1.0      | 1.0      |

| Saturation threshold voltage (V) [7]                                                                              | 0.21           | 0.20     | 0.20     | 0.21     | 0.18     | 0.17     | 0.16     |

| Nominal high-performance NMOS sub-threshold leakage current, $I_{sd,leak}$ (at 25°C) ( $\mu$ A/ $\mu$ m) [8]      | 0.03           | 0.05     | 0.05     | 0.05     | 0.07     | 0.07     | 0.07     |

| Nominal high-performance NMOS saturation drive current, $I_{d,sat}$ (at $V_{dd}$ , at $25^{\circ}$ C) (mA/mm) [9] | <b>980</b>     | 1110     | 1090     | 1170     | 1510     | 1530     | 1590     |

| Required "mobility/transconductance improvement" factor [10]                                                      | 1.0            | 1.3      | 1.3      | 1.4      | 2.0      | 2.0      | 2.0      |

| Sub-threshold slope adjustment factor (full depletion/multiple-gate effects) $(0-1)$ [11]                         | 1.0            | 1.0      | 1.0      | 1.0      | 1.0      | 0.8      | 0.7      |

| Effective saturation carrier velocity enhancement factor (due to quasi-ballistic transport) [12]                  | 1.0            | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      |

| Parasitic source/drain series resistance (R <sub>sd</sub> ) (Ohm-µm) [13]                                         | <b>♦</b> 180   | 180      | 180      | 171      | 162      | 153      | 144      |

| Ideal NMOS device gate capacitance (F/µm) [14]                                                                    | 7.40E-16       | 6.39E-16 | 6.14E-16 | 5.69E-16 | 6.64E-16 | 6.33E-16 | 5.76E-16 |

| Parasitic fringe/overlap capacitance (F/µm) [15]                                                                  | 2.40E-16       | 2.40E-16 | 2.40E-16 | 2.30E-16 | 2.20E-16 | 2.00E-16 | 1.90E-16 |

| High-performance NMOS intrinsic delay, $\tau = C_{gate} * V_{dd} / I_{d,sat}(ps)$ [16]                            | <b>♦</b> 1.20  | 0.95     | 0.86     | 0.75     | 0.64     | 0.54     | 0.48     |

| Relative NMOS intrinsic switching speed, 1/\tau, normalized to 2003 [17]                                          | <b>1.00</b>    | 1.26     | 1.39     | 1.60     | 1.86     | 2.20     | 2.49     |

| Nominal logic gate delay (NAND Gate) (ps) [18]                                                                    | <b>♦</b> 30.24 | 23.94    | 21.72    | 18.92    | 16.23    | 13.72    | 12.13    |

| NMOSFET power-delay product (J/µm) [19]                                                                           | 1.41E-15       | 1.27E-15 | 1.03E-15 | 9.66E-16 | 1.07E-15 | 8.33E-16 | 7.66E-16 |

| NMOSFET static power dissipation due to drain and gate leakage (W/ $\mu$ m) [20]                                  | 3.96E-07       | 6.60E-07 | 6.05E-07 | 6.05E-07 | 8.47E-07 | 7.70E-07 | 7.70E-07 |

#### 14 プロセスインテグレーション、デバイス、および構造

表 47b High-performance Logic Technology Requirements—Long-term

| Year of Production                                                                                            | 2010     | 2012     | 2013     | 2015     | 2016     | 2018     |

|---------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|

| Technology Node                                                                                               | hp45     |          | hp32     |          | hp22     |          |

| DRAM ½ Pitch (nm)                                                                                             | 45       | 35       | 32       | 25       | 22       | 18       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                            | 54       | 42       | 38       | 30       | 27       | 21       |

| MPU/ASIC ½ Pitch (nm)                                                                                         | 45       | 35       | 32       | 25       | 22       | 18       |

| MPU Printed Gate Length (nm)                                                                                  | 25       | 20       | 18       | 14       | 13       | 10       |

| MPU Physical Gate Length (nm)                                                                                 | 18       | 14       | 13       | 10       | 9        | 7        |

| Physical gate length high-performance (HP) (nm) [1]                                                           | 18       | 14       | 13       | 10       | 9        | 7        |

| EOT: equivalent oxide thickness (physical) for high-performance (nm) [2]                                      | 0.7      | 0.7      | 0.6      | 0.6      | 0.5      | 0.5      |

| Electrical thickness adjustment for gate depletion and inversion layer effects (nm) [3]                       | 0.4      | 0.4      | 0.4      | 0.4      | 0.4      | 0.4      |

| Equivalent electrical oxide thickness in inversion (nm) [4]                                                   | 1.1      | 1.1      | 1.0      | 1.0      | 0.9      | 0.9      |

| Nominal gate leakage current density limit (at 25°C) (A/cm²) [5]                                              | 1.9E+03  | 2.4E+03  | 7.7E+03  | 1.0E+04  | 1.9E+04  | 2.4E+04  |

| Nominal power supply voltage $(V_{dd})$ $(V)$ [6]                                                             | 1.0      | 0.9      | 0.9      | 0.8      | 0.8      | 0.7      |

| Saturation threshold voltage (V) [7]                                                                          | 0.15     | 0.14     | 0.11     | 0.12     | 0.10     | 0.11     |

| Nominal high-performance NMOS<br>sub-threshold leakage current, I <sub>sd,leak</sub> (at 25°C) (mA/μm) [8]    | 0.1      | 0.1      | 0.3      | 0.3      | 0.5      | 0.5      |

| Nominal high-performance NMOS saturation drive current, $I_{d,sat}$ (at $V_{dd}$ , at 25°C) (mA/ $\mu$ m) [9] | 1900     | 1790     | 2050     | 2110     | 2400     | 2190     |

| Required "mobility/transconductance improvement" factor [10]                                                  | 2.0      | 2.0      | 2.0      | 2.0      | 2.0      | 2.0      |

| Sub-threshold slope adjustment factor (Full depletion/multiple-gate effects) (0–1) [11]                       | 0.6      | 0.5      | 0.5      | 0.5      | 0.5      | 0.5      |

| Effective saturation carrier velocity enhancement factor (due to quasi-ballistic transport) [12]              | 1.1      | 1.1      | 1.1      | 1.3      | 1.3      | 1.3      |

| Parasitic source/drain series resistance (R <sub>sd</sub> ) (Ohm-µm) [13]                                     | 135      | 116      | 107      | 88       | 79       | 60       |

| Ideal NMOS device gate capacitance (F/μm) [14]                                                                | 5.65E-16 | 4.39E-16 | 4.49E-16 | 3.45E-16 | 3.45E-16 | 2.69E-16 |

| Parasitic fringe/overlap capacitance (F/µm) [15]                                                              | 1.80E-16 | 1.50E-16 | 1.40E-16 | 1.20E-16 | 1.00E-16 | 8.00E-17 |

| High-performance NMOS intrinsic delay, $\tau = C_{gate} * V_{dd} / I_{d,sat}$ (ps) [16]                       | 0.39     | 0.30     | 0.26     | 0.18     | 0.15     | 0.11     |

| Relative NMOS intrinsic switching speed, 1/\tau, normalized to 2003 [17]                                      | 3.06     | 4.05     | 4.64     | 6.80     | 8.08     | 10.77    |

| Nominal logic gate delay (NAND gate) (ps) [18]                                                                | 9.88     | 7.47     | 6.52     | 4.45     | 3.74     | 2.81     |

| NMOSFET power-delay product (J/µm) [19]                                                                       | 7.45E-16 | 4.77E-16 | 4.77E-16 | 2.98E-16 | 2.85E-16 | 1.71E-16 |

| NMOSFET static power dissipation due to drain and gate leakage (W/µm) [20]                                    | 1.10E-06 | 9.90E-07 | 2.97E-06 | 2.64E-06 | 4.40E-06 | 3.85E-06 |

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

#### 表 47a と 47b の注

リンクした Microsoft Excel file は,モデルに基づいたスケーリングに関する詳細な項目が記載されたワークシートを含んでおり,MOSFET モデルで用いた式を取り込んでいる。High-performance Logic 技術要求表 47a,47b の全項目は,そのワークシートから選択されている。表に関する詳細な質問は,リンクされた Excel file を参照してください。

表に記載された数値のスケーリングは、以下の特定のスケーリング・シナリオを反映しており、それは高性能ロジックの目標を達成するために最適化してスケーリングするように試みたものである。具体的には、NMOSトランジスタの本

質的なスイッチング速度(注[16]を参照)を平均年率 17%改善する目標である。ただし, 目標を達成するために必要とされるいくつかの主な技術革新の実現が先に伸びると, 遅れることがある。主な技術革新とは, 金属ゲート電極, 高誘電率ゲート絶縁膜およびソース / ドレインの寄生抵抗値を低減するための新規な不純物ドーピング技術と熱処理技術である。しかしながら, 多くの可変パラメータ(EOT,  $V_{dd}$ ,  $I_{sd,leak}$  他) があることから, これらのパラメータのスケーリングに関して他の異なったスケーリング・シナリオを選択することも可能である。(この観点に関しての詳細は, 本文を参照)

- [1] エッチング後のゲート電極底部の最終寸法.数値は ORTC(総括ロードマップ技術指標)で設定。ゲート電極の寸法制御は, Lithography と FEP Etchの ITWGsで決定されており、3 で $\pm 10\% \times L_g$ と推察される。この 10%の要求を満足することは、スケーリングされるとともにますます困難になるであろうと考えられる(Lithography 章と FEP 章を参照)。駆動デバイス・パラメータの変動に対して、ゲート長の変動は主要な要因であると考えられる。

- [2] ゲート絶縁膜厚  $T_d$ と比誘電率  $\kappa$  に関して, $EOT=T_d$  /  $(\kappa$  / 3.9)と定義される。ここで 3.9 とは,熱二酸化シリコン膜の比誘電率である。ゲート絶縁膜厚  $T_d$ の MOSFET に関して,単位面積当たりの理想的なゲート容量は,熱酸化で形成された膜厚 EOT のゲート絶縁膜を有する MOSFET と同じ値である。 2006 年の黄色は FEP TWG が決定しており,薄いシリコン酸窒化ゲート絶縁膜の適切な膜厚制御と信頼性の確保をおこなうことが困難であることによる。 2007 年以降の赤色は,酸窒化ゲート絶縁膜がゲートリーク電流密度の制限を満たす能力がないことに起因する (注[5]参照,詳細は図 25 とともに本文参照)。 高誘電率ゲート絶縁膜の利用は,一つの解決策候補である。 EOT を測定することは複雑であり,一般的に MOS キャパシタを用いた精密な容量 電圧(CV)測定,および光学測定によっておこなわれる。

- [3] ゲート電極の空乏化および量子効果を含む反転層効果に(近似的に)相当する値.反転層効果による電気的な膜厚の調整分を 0.4nm 一定と仮定した。多結晶シリコンゲート電極に対して,ゲート電極の空乏化による電気的な膜厚の調整分は,多結晶シリコンのドーピングに依存する。ゲート空乏化による膜厚の調整分の要求値を満足するような適切な多結晶シリコンへのドーピング(特に  $P^+$ ホウ素ドープ電極に対して)は困難であると判断から,FET TWG によって 2005 年と 2006 年は黄色となった。2007 年以降の赤色は,ゲート空乏化による膜厚の調整分の要求値を満足するような適切な多結晶シリコンへのドーピングが不可能であることを反映している。金属ゲート電極の導入は一つの解決策候補であり,ゲート空乏化効果をゼロへ減少する。

- [4] EOT と電気的な膜厚調整値の合計(上記注[2],[3]参照)。MOSFET の反転では、単位面積当たりの理想的なゲート容量(注[14]参照)は、 $\epsilon_{ox}$  / (電気的シリコン酸化膜換算膜厚)であり、 $\epsilon_{ox}$  とは熱二酸化シリコンの誘電率である。反転における電気的シリコン酸化膜換算膜厚は、CV/I 本質的遅延(注[16]参照)および  $CV^2$  動的スイッチング・エネルギ(注[19]参照)の計算に用いられる。赤色 / 黄色は、EOT および電気的膜厚調整(上記注[2],[3]参照)に従う。

- [5] 25 における許容ゲートリーク電流の最大値であり、チャネル幅  $1\mu m$  当たりのサブスレッショルド・リーク電流  $I_{sd,leak}$  と関係する(下記注[8]参照)、許容ゲートリーク電流密度 =  $[I_{sd,leak}$  / (物理的ゲート長)] × [温度係数 / 積層オーバラップ係数]。 "温度係数" = 10 とは、高性能ロジックの予期される動作温度を考慮しており、 $I_{sd,leak}$  の温度上昇にともなう急激な増加およびゲートリーク電流(直接トンネル電流であるため)の温度鈍感性の両方に対して調整したものである。 "積層・オーバーラップ係数" = 3 とは、 $I_{sd,leak}$  とロジック・ゲートにおける積層トランジスタのゲートリーク電流との異なった効果およびトランジスタのゲート・オーバラップとを調整したものである。温度係数と積層オーバーラップ係数の両方の値は、桁の見積もり程度の大まかなものである。黄色と赤色は、EOTに従う(上記注[2]参照)。

- [6] 電源電圧は、必要とされる飽和駆動電流値を満たすための十分な電圧過駆動 $[V_{dd}$  飽和しきい値電圧(注[7]参照)]を維持するよう選択されており、またゲート絶縁膜にかかる合理的な縦方向電界強度を維持している。 実際の IC における電源電圧の目標値は、この表に示された値から  $\pm$  10%と考えられ、特定の回路設計用途もしくは技術最適化に依存する。

- [7]  $V_{dd}$  と等しい電圧をドレインに印加したときの最小ゲート長のトランジスタに対する計算されたしきい値電圧(注[6] 参照)。 しきい値電圧値とそれに対応したサブスレッショルド・リーク電流値(注[8]参照)は,必要とされる飽和駆動電流値(注[9]参照)を満たすための十分なゲート過駆動( $V_{dd}$  飽和しきい値電圧)を維持するよう選択されている。縮

小された MOSFET に対する短チャネル効果の制御は、ここでは主な課題であるために、黄色 / 赤色はサブスレッショルド傾き調整係数(下記注[11]参照)にしたがう。

[8] サブスレッショルド・リーク電流値は NMOSFET のチャネル幅 1 $\mu$ m 当たりの $\underline{V}$  ース電流によって定義され,25 ,ドレイン印加電圧を  $V_{dd}$  (注[6]参照) とし,ゲートとソースと基板の印加電圧を 0V とした条件である。MOSFET デバイスの全寸法は,基準値 / 目標値と仮定した。NMOS の全オフ状態電流は,25 におけるチャネル幅 1 $\mu$ m 当たりの NMOSFET のドレイン電流であり,NMOS のサブスレッショルド・リーク電流とゲートリーク電流と接合リーク電流の 3 要素の合計である。25 あるいは高温の条件では,サブスレッショルド・リーク電流は接合リーク電流よりも大きいと仮定した。 $I_{sd,leak}$  とゲートリーク電流密度の関係は,注[5]を参照.黄色と赤色は,サブスレッショルド傾き調整係数にしたがい,その係数は極薄膜基板,完全空乏 MOSFET,多重ゲート MOSFET といった進歩したデバイスを用いることを考慮した(下記注[11]参照)。上記サブスレッショルド・リーク電流,ゲートリーク電流(接合リーク電流のスケーリング・シナリオは,PMOS デバイスにも適用される。ここでのサブスレッショルド・リーク電流値は,最高速 MOSFET だけに適用されることに注意。現在および将来のチップが高リークと低リークの両デバイスの混載により構成されるならば,ここでのサブスレッショルド・リーク電流値は,低速 / 低リーク MOSFET にも適用される(詳細は本文参照)。

[9] 飽和電流駆動  $I_{d,sat}$  は NMOSFET のチャネル幅  $1\mu m$  当たりのドレイン電流によって定義され、25 、ゲートとドレインの印加電圧を  $V_{dd}$  (注[6]参照) とし、ソースと基板の印加電圧を 0V とした条件である。MOSFET デバイスの全寸法は、基準値 / 目標値と仮定した。飽和駆動電流値は、歴史的なスケーリングである年率約 17%のデバイス性能の向上を継続するように選択した(下記注[17]参照)。PMOS の飽和駆動電流値は、NMOS の飽和駆動電流値の(40-50)%と仮定した。黄色 / 赤色は、以下の3つの項目にしたがう。寄生ソース / ドレイン直列抵抗  $R_{sd}$  (下記注[13]参照),反転における電気的な酸化膜換算膜厚(注[4]参照),必要とされる移動度 / 相互コンダクタンス増加係数 (注 [10]参照)。ここでの飽和電流駆動値は、最高速 MOSFET だけに適用されることに注意。現在および将来のチップが高リークと低リークの両デバイスの混載により構成されるならば、ここでの飽和電流駆動値は低飽和駆動電流 / 低リーク MOSFET にも適用される (詳細は本文参照)。

[10] 基礎的なデバイス移動度 / 相互コンダクタンスの改善(ひずみ Si チャネルが現在実行可能な選択肢) は, キャリア移動度の倍数化によって可能である。そのような改善は,必要とされる飽和駆動電流値を満足するために 2004 年に目標設定されている(注[9]参照)。 2004 年以降の黄色は, ひずみ Si チャネル・デバイスの適用への目標の困難さを反映している。 2007 年以降の赤色は, この移動度増加係数を 2.0 とするような最適化が困難であることを反映している。 進歩した極薄膜基板デバイスに対する移動度の増加は困難である。

[11] サブスレッショルド傾き調整係数は、以下の影響を考慮している。それは、進歩した単一ゲート電極薄膜基板完全空乏 SOI MOSFET、さらには高度に縮小されたトランジスタに対する短チャネル効果を制御することが必要な極薄膜基板多重ゲート MOSFET が適用されることである。特に、この値はサブスレッショルド傾きへの掛け算係数であり、60 mV/decade という最小理論値へと減少する。係数 1.0 は古典的な平面バルク MOSFET に対応し、係数範囲 0.7 から 0.8 は単一ゲート極薄膜基板 MOSFET に対応し、係数範囲 0.6 から 0.5 は極薄膜基板多重ゲート MOSFET に対応する。これらの数値は、それらの進歩したデバイスの影響をおおまかに見積もったものである(極薄膜基板 MOSFET に対する議論は Emerging Research Devices 章の Non-Classical CMOS 表を参照)。黄色は 2008 年に単一ゲート極薄膜基板 MOSFET の導入目標を反映しており、赤色は 2010 年に多重ゲート MOSFET の導入目標を反映している。

[12] この値はキャリア飽和速度に対する掛け算係数であり、高度に縮小された極薄膜基板MOSFET, とりわけ多重ゲート MOSFET における準バリスティック輸送を反映している。2010 年以降の赤色は、必要とされる飽和電流駆動値を満足するために飽和速度の増加の目標を反映している(注[9]参照)。

[13]  $R_{sd}$  は,チャネル幅 1 $\mu$ m 当たりの<u>最大許容</u>寄生直列ソースとドレイン抵抗である.これらの値は,必要とされる飽和電流駆動値(注[9]参照)を満足するように縮小される。 黄色 / 赤色は,FET TWG の目標としたコンタクト抵抗,サリサイド・シート抵抗およびドレイン・エクステンションのスケーリングを反映している。

- [14]  $C_{g,ideal}$ , チャネル幅 1 $\mu$ m 当たりの理想的なゲート容量 .  $C_{g,ideal}$ =[ $\epsilon_{ox}$  / (EOT $_{inv}$ )] ×  $L_g$  , ここで $\epsilon_{ox}$  とは熱二酸化シリコンの誘電率 , EOT $_{inv}$  とは反転における電気的酸化膜換算膜厚(注[4]参照) ,  $L_g$  とは物理的なゲート長(注[1]参照)。 黄色 / 赤色は , EOT $_{inv}$ (注[4]参照) にしたがう。

- [15] チャネル幅1µm 当たりの寄生ゲート・オーバーラップ / フリンジ容量[3×Miller 効果を含む片側オーバーラップ / フリンジ容量]。これらの値は、バイアス条件に依存しないと仮定した。

- [16] で とは、25 における NMOS デバイスの本質的なトランジスタ遅延。 $\tau = (C_{gate} \times V_{dd} / I_{d,sat}, \text{ ここで } C_{gate}$ とは、チャネル幅  $1\mu \text{m}$  当たりの理想的なデバイス・ゲート容量 (注[14]参照)とチャネル幅  $1\mu \text{m}$  当たりの寄生ゲート・オーバーラップ / フリンジ容量 (注[15]参照)との合計。 PMOSFET の $\tau$  も同様に縮小されると仮定した。ただし、PMOS  $I_{d,sat} \sim (0.4 0.5) \times (\text{NMOS } I_{d,sat})$  (注[9]参照)。 $\tau$  はデバイスの本質的なスイッチング遅延時間に対する良い尺度であり、 $1/\tau$  はデバイスの本質的なスイッチング速度に対する良い尺度である。赤色 / 黄色は、飽和駆動電流 (注[9]参照)および理想的なゲート容量 (注[14]参照)の両方にしたがう。

- [17] NMOS 性能の尺度  $(1/\tau, NMOS)$  の本質的なスイッチング速度--注[16]参照), 2003 年を基準とした。 歴史的な年率約 17%のデバイス性能改善というスケーリング・トレンドの維持が, 高性能ロジックのスケーリングの最終目標である。 赤色 / 黄色は,  $\tau$ (注[16]参照)にしたがう。

- [18] 典型的なロジック・ゲートを表現するために選択された 2 入力 3 出力 NAND ゲートに対して計算された遅延時間(計算の詳細はリンク・ファイルを参照)。 赤色 / 黄色は ,  $\tau$ (注[16]参照) にしたがう。

- [19] フルスイッチング周期における MOSFET のチャネル幅1 $\mu$ m 当たりのエネルギー消費 ,  $C_{gate} \times V_{dd}^2$  で定義 , ここで  $C_{gate}$ とは , チャネル幅1 $\mu$ m 当たりの理想的なデバイス・ゲート容量 (注[14]参照)とチャネル幅1 $\mu$ m 当たりの寄生ゲート・オーバーラップ / フリンジ容量 (注[15]参照)との合計。 ( $\tau$ (注[16]参照)の計算に用いられた  $C_{gate}$ とおなじ)。動的電力消費は , 電力 遅延積の直接的に関係する。赤色 / 黄色は ,  $C_{g,idea}$ (注[14]参照)にしたがう。

- [20] MOSFET のチャネル幅1 $\mu$ m 当たりの静的電力消費, $V_{dd}$ ×[ $\{I_{sd,leak}$ (注[8]参照) $\}$ + $\{$ チャネル幅1 $\mu$ m 当たりの最大ゲートリーク電流( $L_g$ ×許容ゲートリーク電流密度で定義,注[5]より) $\}$ ] (接合リーク電流は,ソース / ドレインのサブスレッショルド・リーク電流もしくはゲートリーク電流より十分に小さいものと仮定した)。 黄色 / 赤色は,許容ゲートリーク電流密度(注[5])にしたがう。

# 18 プロセスインテグレーション、デバイス、および構造

表 48a Low Operating Power (LOP) Logic Technology Requirements—Near-term

| Year of Production                                                                                     | 2003     | 2004     | 2005     | 2006     | 2007     | 2008     | 2009     |

|--------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|

| Technology Node                                                                                        |          | hp90     |          |          | hp65     |          |          |

| DRAM ½ Pitch (nm)                                                                                      | 100      | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                     | 120      | 107      | 95       | 85       | 76       | 67       | 60       |

| MPU/ASIC ½ Pitch (nm)                                                                                  | 107      | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU Printed Gate Length (nm)                                                                           | 65       | 53       | 45       | 40       | 35       | 32       | 28       |

| MPU Physical Gate Length (nm)                                                                          | 45       | 37       | 32       | 28       | 25       | 22       | 20       |

| Physical gate length low operating power (LOP) (nm) [1]                                                | 65       | 53       | 45       | 37       | 32       | 28       | 25       |

| EOT: equivalent oxide thickness (physical) for LOP (nm) [2]                                            | 1.6      | 1.5      | 1.4      | 1.3      | 1.2      | 1.1      | 1.0      |

| Electrical thickness adjustment for gate depletion and inversion layer effects (nm) [3]                | 0.8      | 0.8      | 0.7      | 0.7      | 0.7      | 0.4      | 0.4      |

| Equivalent electrical oxide thickness in inversion (nm) [4]                                            | 2.4      | 2.3      | 2.1      | 2.0      | 1.9      | 1.5      | 1.4      |

| Nominal gate leakage current density limit (at 25°C) (A/cm²) [5]                                       | 0.51     | 1.89     | 2.22     | 2.70     | 5.21     | 5.95     | 6.67     |

| Nominal LOP power supply voltage (V <sub>dd</sub> ) (V) [6]                                            | 1.0      | 0.9      | 0.9      | 0.9      | 0.8      | 0.8      | 0.8      |

| Saturation threshold voltage (V) [7]                                                                   | 0.31     | 0.26     | 0.27     | 0.28     | 0.26     | 0.25     | 0.25     |

| Nominal LOP NMOS sub-threshold leakage current, $I_{sd,leak}$ (at 25°C) ( $\mu$ A/ $\mu$ m) [8]        | 1.0E-03  | 3.0E-03  | 3.0E-03  | 3.0E-03  | 5.0E-03  | 5.0E-03  | 5.0E-03  |

| Nominal LOP NMOS saturation drive current, $I_{d,sat}$ (at $V_{dd}$ , at 25°C) ( $\mu$ A/ $\mu$ m) [9] | 520      | 530      | 580      | 610      | 570      | 730      | 770      |

| Required "mobility/transconductance improvement" factor [10]                                           | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.3      | 1.3      |

| Sub-threshold slope adjustment factor (full depletion/multiple-gate effects) (0–1) [11]                | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      |

| Effective saturation carrier velocity enhancement factor (due to quasi-ballistic transport) [12]       | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      |

| Parasitic source/drain series resistance (R <sub>sd</sub> ) (Ohm-μm) [13]                              | 180      | 180      | 180      | 180      | 180      | 180      | 180      |

| Ideal NMOS device gate capacitance (F/µm) [14]                                                         | 9.35E-16 | 7.96E-16 | 7.40E-16 | 6.39E-16 | 5.82E-16 | 6.45E-16 | 6.17E-16 |

| Parasitic fringe/overlap capacitance (F/μm) [15]                                                       | 2.40E-16 |

| LOP NMOS intrinsic delay, $\tau = C_{gate} * V_{dd} / I_{d,sat} (ps)$ [16]                             | 2.26     | 1.76     | 1.52     | 1.30     | 1.15     | 0.97     | 0.89     |

| Relative NMOS intrinsic switching speed, 1/τ, normalized to 2003 [17]                                  | 1.00     | 1.29     | 1.49     | 1.74     | 1.96     | 2.33     | 2.54     |

| Nominal logic gate delay (NAND gate) (ps) [18]                                                         | 57.0     | 44.3     | 38.3     | 32.7     | 29.1     | 24.4     | 22.4     |

| NMOSFET power-delay product (J/µm) [19]                                                                | 1.18E-15 | 8.39E-16 | 7.94E-16 | 7.12E-16 | 5.26E-16 | 5.66E-16 | 5.48E-16 |

| NMOSFET static power dissipation due to drain and gate leakage (W/µm) [20]                             | 2.0E-09  | 5.4E-09  | 5.4E-09  | 5.4E-09  | 8.0E-09  | 8.0E-09  | 8.0E-09  |

表 48b Low Operating Power (LOP) Logic Technology Requirements—Long-term

| Year of Production                                                                                     | 2010     | 2012     | 2013     | 2015     | 2016     | 2018     |

|--------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|

| Technology Node                                                                                        | hp45     |          | hp32     |          | hp22     |          |

| DRAM ½ Pitch (nm)                                                                                      | 45       | 35       | 32       | 25       | 22       | 18       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                     | 54       | 42       | 38       | 30       | 27       | 21       |

| MPU/ASIC ½ Pitch (nm)                                                                                  | 45       | 35       | 32       | 25       | 22       | 18       |

| MPU Printed Gate Length (nm)                                                                           | 25       | 20       | 18       | 14       | 13       | 10       |

| MPU Physical Gate Length (nm)                                                                          | 18       | 14       | 13       | 10       | 9        | 7        |

| Physical gate length low operating power (LOP) (nm) [1]                                                | 22       | 18       | 16       | 13       | 11       | 9        |

| EOT: equivalent oxide thickness (physical) for LOP (nm) [2]                                            | 0.9      | 0.9      | 0.8      | 0.8      | 0.7      | 0.7      |

| Electrical thickness adjustment for gate depletion and inversion layer effects (nm) [3]                | 0.4      | 0.4      | 0.4      | 0.4      | 0.4      | 0.4      |

| Equivalent electrical oxide thickness in inversion (nm) [4]                                            | 1.3      | 1.3      | 1.2      | 1.2      | 1.1      | 1.1      |

| Nominal gate leakage current density limit (at 25°C) (A/cm²) [5]                                       | 11       | 13       | 21       | 26       | 91       | 111      |

| Nominal LOP power supply voltage $(V_{dd})$ $(V)$ [6]                                                  | 0.7      | 0.7      | 0.6      | 0.6      | 0.5      | 0.5      |

| Saturation threshold voltage (V) [7]                                                                   | 0.22     | 0.23     | 0.21     | 0.19     | 0.16     | 0.17     |

| Nominal LOP NMOS sub-threshold leakage current, $I_{sd,leak}$ (at 25°C) ( $\mu$ A/ $\mu$ m) [8]        | 0.007    | 0.007    | 0.01     | 0.01     | 0.03     | 0.03     |

| Nominal LOP NMOS saturation drive current, $I_{d,sat}$ (at $V_{dd}$ , at 25°C) ( $\mu$ A/ $\mu$ m) [9] | 770      | 830      | 780      | 900      | 920      | 950      |

| Required "mobility/transconductance improvement" factor [10]                                           | 1.3      | 2.0      | 2.0      | 2.0      | 2.0      | 2.0      |

| Sub-threshold slope adjustment factor (full depletion/multiple-gate effects) (0–1) [11]                | 0.8      | 0.8      | 0.8      | 0.5      | 0.5      | 0.5      |

| Effective saturation carrier velocity enhancement factor (due to quasi-ballistic transport) [12]       | 1.0      | 1.0      | 1.1      | 1.1      | 1.3      | 1.3      |

| Parasitic source/drain series resistance (R <sub>sd</sub> ) (Ohm-µm) [13]                              | 160      | 135      | 126      | 107      | 98       | 80       |

| Ideal NMOS device gate capacitance (F/µm) [14]                                                         | 5.84E-16 | 4.78E-16 | 4.60E-16 | 3.74E-16 | 3.45E-16 | 2.83E-16 |

| Parasitic fringe/overlap capacitance (F/µm) [15]                                                       | 2.20E-16 | 1.80E-16 | 1.60E-16 | 1.40E-16 | 1.30E-16 | 1.10E-16 |

| LOP NMOS intrinsic delay, $\tau = C_{gate} * V_{dd} / I_{d,sat}$ (ps) [16]                             | 0.73     | 0.56     | 0.48     | 0.34     | 0.26     | 0.21     |

| Relative NMOS intrinsic switching speed, 1/τ, normalized to 2003 [17]                                  | 3.1      | 4.1      | 4.7      | 6.6      | 8.7      | 10.9     |

| Nominal logic gate delay (NAND Gate) (ps) [18]                                                         | 18.4     | 14.0     | 12.0     | 8.6      | 6.5      | 5.2      |

| NMOSFET power-delay product (J/μm) [19]                                                                | 3.94E-16 | 3.22E-16 | 2.23E-16 | 1.85E-16 | 1.19E-16 | 9.81E-17 |

| NMOSFET static power dissipation due to drain and gate leakage (W/μm) [20]                             | 9.8E-09  | 9.8E-09  | 1.2E-08  | 1.2E-08  | 3.0E-08  | 3.0E-08  |

表 48c Low Standby Power (LSTP) Technology Requirements—Near-term

| Year of Production                                                                                      | 2003     | 2004     | 2005     | 2006     | 2007     | 2008     | 2009     |

|---------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|

| Technology Node                                                                                         |          | hp90     |          |          | hp65     |          |          |

| DRAM ½ Pitch (nm)                                                                                       | 100      | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                      | 120      | 107      | 95       | 85       | 76       | 67       | 60       |

| MPU/ASIC ½ Pitch (nm)                                                                                   | 107      | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU Printed Gate Length (nm)                                                                            | 65       | 53       | 45       | 40       | 35       | 32       | 28       |

| MPU Physical Gate Length (nm)                                                                           | 45       | 37       | 32       | 28       | 25       | 22       | 20       |

| Physical gate length low standby power (LSTP) (nm) [1]                                                  | 75       | 65       | 53       | 45       | 37       | 32       | 28       |

| EOT: equivalent oxide thickness (physical) for LSTP (nm) [2]                                            | 2.2      | 2.1      | 2.1      | 1.9      | 1.6      | 1.5      | 1.4      |

| Electrical thickness adjustment for gate depletion and inversion layer effects (nm) [3]                 | 0.8      | 0.8      | 0.7      | 0.7      | 0.7      | 0.4      | 0.4      |

| Equivalent electrical oxide thickness in inversion (nm) [4]                                             | 3        | 2.9      | 2.8      | 2.6      | 2.3      | 1.9      | 1.8      |

| Nominal gate leakage current density limit (at $25^{\circ}C$ ) (A/cm <sup>2</sup> ) [5]                 | 4.4E-03  | 5.1E-03  | 9.4E-03  | 1.5E-02  | 2.3E-02  | 3.1E-02  | 4.8E-02  |

| Nominal LSTP power supply voltage $(V_{dd})$ $(V)$ [6]                                                  | 1.2      | 1.2      | 1.2      | 1.2      | 1.1      | 1.1      | 1.1      |

| Saturation threshold voltage (V) [7]                                                                    | 0.50     | 0.50     | 0.51     | 0.52     | 0.50     | 0.47     | 0.47     |

| Nominal LSTP NMOS sub-threshold leakage current, $I_{sd,leak}$ (at 25°C) ( $\mu$ A/ $\mu$ m) [8]        | 1.0E-05  | 1.0E-05  | 1.5E-05  | 2.0E-05  | 2.5E-05  | 3.0E-05  | 4.0E-05  |

| Nominal LSTP NMOS saturation drive current, $I_{d,sat}$ (at $V_{dd}$ , at 25°C) ( $\mu$ A/ $\mu$ m) [9] | 410      | 440      | 470      | 510      | 510      | 670      | 700      |

| Required "mobility/transconductance improvement" factor [10]                                            | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.3      | 1.3      |

| Sub-threshold slope adjustment factor (full depletion/multiple-gate effects) (0–1) [11]                 | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      |

| Effective saturation carrier velocity enhancement factor (due to quasi-ballistic transport) [12]        | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      |

| Parasitic source/drain series resistance (R <sub>sd</sub> ) (Ohm-μm) [13]                               | 180      | 180      | 180      | 180      | 180      | 180      | 180      |

| Ideal NMOS device gate capacitance (F/µm) [14]                                                          | 8.63E-16 | 7.74E-16 | 6.54E-16 | 5.98E-16 | 5.55E-16 | 5.82E-16 | 5.37E-16 |

| Parasitic fringe/overlap capacitance (F/µm) [15]                                                        | 2.40E-16 |

| LSTP NMOS intrinsic delay, $\tau = C_{gate} * V_{dd} / I_{d,sat}$ (ps) [16]                             | 3.23     | 2.77     | 2.28     | 1.97     | 1.72     | 1.35     | 1.22     |

| Relative NMOS intrinsic switching speed, 1/τ, normalized to 2003 [17]                                   | 1.00     | 1.17     | 1.42     | 1.64     | 1.88     | 2.39     | 2.64     |

| Nominal logic gate delay (NAND Gate) (ps) [18]                                                          | 81.4     | 69.7     | 57.5     | 49.7     | 43.2     | 34.0     | 30.8     |

| NMOSFET power-delay product (J/µm) [19]                                                                 | 1.6E-15  | 1.5E-15  | 1.3E-15  | 1.2E-15  | 9.6E-16  | 9.9E-16  | 9.4E-16  |

| NMOSFET static power dissipation due to drain and gate leakage (W/μm) [20]                              | 2.4E-11  | 2.4E-11  | 3.6E-11  | 4.8E-11  | 5.5E-11  | 6.6E-11  | 8.8E-11  |

表 48d Low Standby Power (LSTP) Technology Requirements—Long-term

| Year of Production                                                                                      | 2010     | 2012     | 2013     | 2015     | 2016     | 2018     |

|---------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|

| Technology Node                                                                                         | hp45     |          | hp32     |          | hp22     |          |

| DRAM ½ Pitch (nm)                                                                                       | 45       | 35       | 32       | 25       | 22       | 18       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                      | 54       | 42       | 38       | 30       | 27       | 21       |

| MPU/ASIC ½ Pitch (nm)                                                                                   | 45       | 35       | 32       | 25       | 22       | 18       |

| MPU Printed Gate Length (nm)                                                                            | 25       | 20       | 18       | 14       | 13       | 10       |

| MPU Physical Gate Length (nm)                                                                           | 18       | 14       | 13       | 10       | 9        | 7        |

| Physical gate length low standby power (LSTP) (nm) [1]                                                  | 25       | 20       | 18       | 14       | 13       | 10       |

| EOT: equivalent oxide thickness (physical) for LSTP (nm) [2]                                            | 1.3      | 1.2      | 1.1      | 1.1      | 1.0      | 0.9      |

| Electrical thickness adjustment for gate depletion and inversion layer effects (nm) [3]                 | 0.4      | 0.4      | 0.4      | 0.4      | 0.4      | 0.4      |

| Equivalent electrical oxide thickness in inversion (nm) [4]                                             | 1.7      | 1.6      | 1.5      | 1.5      | 1.4      | 1.3      |

| Nominal gate leakage current density limit (at 25°C) (A/cm²) [5]                                        | 8.00E-02 | 1.00E-01 | 1.48E-01 | 1.90E-01 | 2.56E-01 | 3.33E-01 |

| Nominal LSTP power supply voltage (V <sub>dd</sub> ) (V) [6]                                            | 1.0      | 1.0      | 0.9      | 0.9      | 0.8      | 0.8      |

| Saturation threshold voltage (V) [7]                                                                    | 0.39     | 0.43     | 0.34     | 0.38     | 0.36     | 0.40     |

| Nominal LSTP NMOS sub-threshold leakage current, $I_{sd,leak}$ (at 25°C) ( $\mu$ A/ $\mu$ m) [8]        | 6.0E-05  | 6.0E-05  | 8.0E-05  | 8.0E-05  | 1.0E-04  | 1.0E-04  |

| Nominal LSTP NMOS saturation drive current, $I_{d,sat}$ (at $V_{dd}$ , at 25°C) ( $\mu$ A/ $\mu$ m) [9] | 760      | 790      | 880      | 870      | 860      | 990      |

| Required "mobility/transconductance improvement" factor [10]                                            | 1.3      | 1.3      | 1.3      | 1.3      | 2.0      | 2.0      |

| Sub-threshold slope adjustment factor (full depletion/multiple-gate effects) (0–1) [11]                 | 0.8      | 0.8      | 0.5      | 0.5      | 0.5      | 0.5      |

| Effective saturation carrier velocity enhancement factor (due to quasi-ballistic transport) [12]        | 1.0      | 1.0      | 1.0      | 1.0      | 1.1      | 1.3      |

| Parasitic source/drain series resistance (R <sub>sd</sub> ) (Ohm-µm) [13]                               | 180      | 144      | 135      | 116      | 107      | 88       |

| Ideal NMOS device gate capacitance (F/µm) [14]                                                          | 5.08E-16 | 4.32E-16 | 4.14E-16 | 3.22E-16 | 3.21E-16 | 2.66E-16 |

| Parasitic fringe/overlap capacitance (F/μm) [15]                                                        | 2.40E-16 | 1.90E-16 | 1.70E-16 | 1.50E-16 | 1.40E-16 | 1.20E-16 |

| LSTP NMOS intrinsic delay, $\tau = C_{gate} * V_{dd} / I_{d,sat}$ (ps) [16]                             | 0.98     | 0.79     | 0.60     | 0.49     | 0.43     | 0.31     |

| Relative NMOS intrinsic switching speed, 1/7, normalized to 2003 [17]                                   | 3.28     | 4.10     | 5.40     | 6.61     | 7.54     | 10.36    |

| Nominal logic gate delay (NAND gate) (ps) [18]                                                          | 24.80    | 19.83    | 15.06    | 12.31    | 10.80    | 7.85     |

| NMOSFET power-delay product (J/µm) [19]                                                                 | 7.48E-16 | 6.22E-16 | 4.73E-16 | 3.83E-16 | 2.95E-16 | 2.47E-16 |

| NMOSFET static power dissipation due to drain and gate leakage (W/µm) [20]                              | 1.20E-10 | 1.20E-10 | 1.44E-10 | 1.44E-10 | 1.60E-10 | 1.60E-10 |

#### 表 48a から 48d の注

リンクした Microsoft Excel file は,モデルに基づいたスケーリングに関する詳細な項目が記載されたワークシートを含んでおり,MOSFET モデルで用いた式を取り込んでいる。LOPと LSTP Logic 技術要求表 48a-48d の全項目は,そのワークシートから選択されている。表に関する詳細な質問は,リンクされた Excel file を参照してください。

表に記載された数値のスケーリングは、以下の特定のスケーリング・シナリオを反映しており、それは低電力ロジックの目標を達成するために最適化してスケーリングするように試みたものである。ただし、目標を達成するために必要

とされるいくつかの主な技術革新の実現が先に伸びると、遅れることがある。主な技術革新とは、金属ゲート電極、高誘電率ゲート絶縁膜およびソース / ドレインの寄生抵抗値を低減するための新規な不純物ドーピング技術と熱処理技術である。表中のサブスレッショルド・リーク電流(注[8]参照)の目標を満足するように最終設定されている。しかしながら、変更可能なあるいはトレードオフ関係の多くパラメータ(EOT,  $V_{dd}$ ,  $I_{sd,leak}$ , Rsd 他)があるために、これらのパラメータのスケーリングに関して他の異なったスケーリング・シナリオを選択することも可能である。(この観点に関しての詳細は、本文を参照)

- [1] エッチング後のゲート電極底部の最終寸法.ここに示された値は,高性能ロジックに対するゲート長の値から LOPで 2 年,LSTP で 3 年遅れたものである(詳細な議論は本文参照)。ゲート電極の寸法制御は,Lithography と FEP Etchの ITWGs で決定されており,3 で  $\pm$  10%  $\times$  Lg と推察される。この 10%の要求を満足することは,スケーリングされるとともにますます困難になるであろうと考えられる(Lithography 章と FEP 章を参照)。駆動デバイス・パラメータの変動に対して,ゲート長の変動は主要な要因であると考えられる。

- [2] ゲート絶縁膜厚  $T_d$  と比誘電率  $\kappa$  に関して, $EOT=T_d/(\kappa/3.9)$  と定義され、ここで 3.9 とは熱二酸化シリコン膜の比誘電率である。ゲート絶縁膜厚  $T_d$  の MOSFET に関して,単位面積当たりの理想的なゲート容量は,熱酸化で形成された膜厚 EOT のゲート絶縁膜を有する MOSFET と同じ値である。LOP と LSTP との両方に関して,2006 年以降の赤色は,酸窒化ゲート絶縁膜がゲートリーク電流密度の制限を満たす能力がないことに起因する(注[5]参照,詳細は図 23 と図 24 とともに本文参照)。高誘電率ゲート絶縁膜の利用は,一つの解決策候補である。

- [3] ゲート電極の空乏化および量子効果を含む反転層効果に(近似的に)相当する値。反転層効果による電気的な膜厚の調整分を 0.4nm 一定と仮定した。多結晶シリコンゲート電極に対して,ゲート電極の空乏化による電気的な膜厚の調整分は,多結晶シリコンへのドーピングに依存する。2008 年以降の赤色は,ゲート空乏化による膜厚の調整分の要求値を満足するような適切な多結晶シリコンへのドーピングが不可能であることを反映している。金属ゲート電極の導入は一つの解決策候補であり,ゲート空乏化効果をゼロへ減少する。

- [4] EOT と電気的な膜厚調整値の合計 (上記注[2],[3]参照)。MOSFET の反転では、単位面積当たりの理想的なゲート容量 (注[14]参照) は, $\epsilon_{ox}$  / (電気的シリコン酸化膜換算膜厚)であり, $\epsilon_{ox}$  とは熱二酸化シリコンの誘電率である。反転における電気的シリコン酸化膜換算膜厚は,CV/I 本質的遅延(注[16]参照) および  $CV^2$  動的スイッチング・エネルギ(注[19]参照)の計算に用いられる。赤色 / 黄色は,EOT 項および電気的電気的膜厚調整 (上記注[2],[3]参照) に従う。

- [5] 25 における許容ゲートリークの最大値であり、チャネル幅  $1\mu m$  当たりのサブスレッショルド・リーク電流  $I_{sd,leak}$  と 関係する(下記注[8]参照)。許容ゲートリーク電流密度 =  $[I_{sd,leak}$  /(物理的ゲート長)]  $\times$  [温度係数 / 積層オーバラップ係数]。"温度係数" = 1 とは、LOP と LSTP のロジックが室温付近で動作すると思われ、温度係数は高温動作に対して調整したものである。"積層・オーバーラップ係数" = 3 とは、 $I_{sd,leak}$  とロジック・ゲートにおける積層トランジスタのゲートリーク電流との異なった効果およびトランジスタのゲート・オーバラップを調整したものである。温度係数と積層オーバーラップ係数の両方の値は、桁の見積もり程度の大まかなものである。黄色と赤色は、EOT(上記注[2]参照)に従う。

- [6] 電源電圧は、許容される回路スイッチング・ノイズ・マージン(しきいち電圧の約 2.3 倍)を維持するのに十分な最小値が選択されている。実際の IC における電源電圧の目標値は、この表に示された値から  $\pm$  10%と考えられ、特定の回路設計用途もしくは技術最適値に依存する。様々なシステム応用によって、LOP と LSTP ロジックの電源電圧の値は最適化され、またそれぞれ独立に設定される。 $V_{dd}^2$  に比例する動作時電力消費を最小限になるように、特に LOP の  $V_{dd}$  値は可能な限り最小限の値とした。システム全体としての電力消費は、様々な回路ブロックごとに"off"または"省電力"する回路 / システム技術の利用が必要となることに注意(この点に関する詳細な議論は本文参照)。もう一点は、必要とされる飽和駆動電流値を満たすための十分なゲート過駆動[ $V_{dd}$  飽和しきい値電圧(注[9]参照)]を維持することである。

[7]  $V_{dd}$  と等しい電圧をドレインに印加したときの最小ゲート長のトランジスタに対する計算されたしきい値電圧(注[6] 参照)。しきい値電圧値は、必要とされるサブスレッショルド・リーク電流値(注[8]参照)を満たすために選択されている。縮小された MOSFET に対する短チャネル効果の制御は、ここでは主な課題であるために、黄色 / 赤色はサブスレッショルド傾き調整係数(下記注[11]参照)にしたがう。

[8] サブスレッショルド・リーク電流値は NMOSFET のチャネル幅1 $\mu$ m 当たりの $\underline{V}$ ース電流によって定義され,25 ,ドレイン印加電圧を  $V_{dd}$ (注[6]参照)とし,ゲートとソースと基板の印加電圧を OV とした条件である。MOSFET デバイスの全寸法は,基準値 / 目標値と仮定した。NMOS の全オフ状態電流は,25 におけるチャネル幅1 $\mu$ m 当たりのNMOSFET のドレイン電流であり,NMOS のサブスレッショルド・リーク電流とゲートリーク電流と接合リーク電流の 3 要素の合計である。25 あるいは高温において,サブスレッショルド・リーク電流は接合リーク電流よりも大きいと仮定した。ただし, $I_{sd,leak}$  とゲート・リーク電流密度の関係は注[5]を参照。LOP ロジックと特に LSTP ロジックのサブスレッショルド・リーク電流は高性能ロジックの値よりかなり小さく,サブスレッショルド・リーク電流を低い値にする要求を達成することが LOP と LSTP のスケーリングでは最終目標である。黄色と赤色は,サブスレッショルド傾き調整係数にしたがい,その係数は極薄膜基板,完全空乏 MOSFET,多重ゲート MOSFET といった進歩したデバイスを用いることを考慮した(下記注[11]参照)。上記サブスレッショルド・リーク電流,ゲートリーク電流,接合リーク電流のスケーリング・シナリオは,PMOS デバイスにも適用される。ここでのサブスレッショルド・リーク電流値は,最高速 MOSFET だけに適用されることに注意。現在および将来のチップが高リークおよび低リークの両デバイスの混載により構成されるならば,ここでのサブスレッショルド・リーク電流値は,低速 / 低リーク MOSFET にも適用される (詳細は本文参照)。

[9] 飽和電流駆動  $I_{d,sat}$  は NMOSFET のチャネル幅  $1\mu m$  当たりのドレイン電流によって定義され,25 ,ゲートとドレインの印加電圧を  $V_{dd}$ (注[6]参照)とし,ソースと基板の電圧印加を 0V とした条件である。MOSFET デバイスの全寸法は,標準 / 目標値と仮定した。PMOS の飽和電流駆動値は,NMOS の飽和電流駆動値の(40-50)%と仮定した。 黄色 / 赤色は,以下の 2 つの項目にしたがう。寄生ソース / ドレイン直列抵抗  $R_{sd}$ (下記注[13]参照),反転における電気的な酸化膜換算膜厚(注[4]参照)。ここでの飽和駆動電流値は,最高速 MOSFET だけに適用されることに注意。現在および将来のチップが高リークおよび低リークの両デバイスの混載により構成されるならば,ここでの飽和駆動電流値は,低飽和駆動電流 / 低リーク MOSFET にも適用される(詳細は本文参照)。

[10] 基礎的なデバイス移動度 / 相互コンダクタンスの改善(ひずみSiチャネルが現在実行可能な選択肢) は,キャリア移動度の倍数化によって可能である。そのような改善は,必要とされる飽和電流駆動値を満足するために 2008 年に目標設定されている(注[9]参照)。2008 年以降の黄色は,ひずみSiチャネル・デバイスの適用への目標の困難さを反映している.2012 年以降の(LOP)と 2016 以降の(LSTP)の赤色は,この移動度増加係数を 2.0 とするような最適化が困難であることを反映している。進歩した極薄膜基板デバイスに対する移動度増加は困難である。

[11] サブスレッショルド傾き調整係数は,以下の影響を考慮しており、それは,進歩した単一ゲート電極薄膜基板完全空乏SOI MOSFET, さらには高度に縮小されたトランジスタに対する短チャネル効果を制御することが必要な極薄膜基板多重ゲートMOSFETが適用されることである。特に,この値はサブスレッショルド傾きへの掛け算係数であり,60 mV/decade という最小理論値へと減少する。係数 1.0 は古典的な平面バルク MOSFET に対応し,係数範囲 0.7 から 0.8 は単一ゲート極薄膜基板 MOSFET に対応し,係数範囲 0.6 から 0.5 は極薄膜基板多重ゲート MOSFET に対応する。これらの数値は,それらの進歩したデバイスの影響をおおまかに見積もったものである(極薄膜基板 MOSFET に対する議論は Non-Classical CMOS tables in Emerging Research Devices 章を参照)。黄色は 2010 年に単一ゲート極薄膜基板 MOSFET の導入目標を反映しており,赤色は 2013 年(LSTP)および 2016 年(LOP)に多重ゲートMOSFETの導入目標を反映している。

[12] この値はキャリア飽和速度に対する掛け算係数であり,高度に縮小された極薄膜基板MOSFET,とりわけ多重ゲートMOSFETにおける準パリスティック輸送を反映している。2013年以降の LOP および 2016年以降の LSTP の赤色は,必要とされる飽和電流駆動値を満足するために飽和速度の増加の目標を反映している(注[9]参照)

- [13]  $R_{sd}$  は、チャネル幅1 $\mu$ m 当たりの<u>最大許容</u>寄生直列ソースおよびドレイン抵抗である。これらの値は、必要とされる飽和電流駆動値(注[9]参照)を満足するように縮小される。黄色 / 赤色は、FET TWG の目標としたコンタクト抵抗、サリサイド・シート抵抗およびドレイン・エクステンションの縮小を反映している。

- [14]  $C_{g,ideal}$ , チャネル幅 1 $\mu$ m 当たりの理想的なゲート容量。 $C_{g,ideal}$ =[ $\epsilon_{ox}$  / (EOT $_{inv}$ )] ×  $L_g$  , ここで $\epsilon_{ox}$  とは熱二酸化シリコンの誘電率 , EOT $_{inv}$  とは反転における電気的酸化膜換算膜厚(注[4]参照) ,  $L_g$  とは物理的なゲート長(注[1]参照)。 黄色 / 赤色は , EOT $_{inv}$ にしたがう(注[4]参照)。

- [15] チャネル幅1 $\mu$ m 当たりの寄生ゲート・オーバーラップ / フリンジ容量。[3 x Miller 効果を含む片側オーバーラップ / フリンジ容量] これらの値は、バイアス条件に依存しないと仮定した。

- [16] でとは、25 におけるNMOSデバイスの本質的なトランジスタ遅延。 $\tau = (C_{gate} \times V_{dd} / I_{d,sat}, \text{ ここで } C_{gate}$ とは、チャネル幅1 $\mu m$  当たりの理想的なデバイス・ゲート容量(注[14]参照)とチャネル幅1 $\mu m$  当たりの寄生ゲート・オーバーラップ / フリンジ容量(注[15]参照)との合計。PMOSFET の $\tau$  も同様にスケーリングされると仮定した。ただし、PMOS  $I_{d,sat} \sim (0.4 \sim 0.5) \times (\text{NMOS } I_{d,sat})$ (注[9]参照)。 $\tau$  はデバイスの本質的なスイッチング遅延時間に対する良い尺度であり、 $1/\tau$  はデバイスの本質的なスイッチング速度に対する良い尺度である。赤色 / 黄色は、飽和駆動電流(注[9]参照)および理想的なゲート容量(注[14]参照)の両方にしたがう。