# 新探究素子 (ERD, EMERGING RESEARCH DEVICES)

---

## スコープ

半導体産業は、今後数年にわたって情報技術の指数関数的な成長を維持する準備が整っている。それに 22nm 世代を超えて CMOS を微細化するという前例のない技術を成功させ続けることになる。極限的に微細化された CMOS を超えて情報技術の成長を続けるには、短期的な視野に立つと、CMOS プラットフォームに異種の新技术を集積する必要がある。これはいわゆる「CMOS の延長」である。一方、長期的には、半導体産業は根本的に全く新しい情報処理の方法を発明するという困難に直面することになる。これに要求されることは、新しい材料、プロセス、デバイス、ナノアーキテクチャ、およびシステム革新による情報の物理的表現、処理、記憶、伝達の新しい方法を発明しそれを利用するであろう。

この章の主な目標は、「極限微細化 CMOS」を本質的に超えて情報処理の機能を拡張する新概念の発明および研究を促進することである。この目標を達成するには、上で示した 2 つの技術領域を扱わなければならない - 新技術の異種集積による CMOS の延長と、その後の新技術とナノアーキテクチャ概念の開発である。目的は 2 つに分けられる。1 つ目は、「大きな網を投げ」て、CMOS を超えてロードマップを延長するようなメモリ、ロジック、情報処理ナノアーキテクチャの代替概念を一箇所に集めることである。このようにして、ここでの議論は新技術候補に対する入口を提供する。2 つ目は、これらの情報処理の新デバイス技術に対して評価を与えることである。この点に関しては、新たに節を追加し、極限微細化 CMOS で達成可能な情報処理を本質的に超えるような情報処理を支配する根本的な原理を提案することとした。これにより、この章は半導体産業に新探究デバイス技術に関する見通しを提供するとともに、パルレク CMOS と CMOS を超えるマイクロエレクトロニクス領域の架け橋となる。

2003 年版でこの章のスコープに含まれていたのは、新情報処理技術を可能とする新探究メモリ、ロジック、ナノアーキテクチャの新しい取り組みであった。この 2005 年版では、スコープが拡大され、新しく重要な節として新探究材料を新設した。この節は、新探究メモリやロジックデバイスを実現するのに必要な新材料の本質的な特性を紹介する。さらに、この新材料の節には、これら必要な材料を開発するための合成技術、計測、評価、モデリング、シミュレーションツール等も記述されている。現在の CMOS 技術で利用される従来材料やプロセスは、(新探究デバイス実現のためにも用いられるかも知れないが)、フロントエンドプロセス(FEP)の章で扱う。また、ノンクラシカル CMOS の節は、2003 年版ではこの ERD の章に含まれていたが、2005 年版ではプロセスインテグレーション(PIDS)と FEP の章に移管された。このようにスコープを広げたことによって、この章は、材料、デバイスからデバイスレベルのナノアーキテクチャまで、新情報技術のパラダイムに関わるすべての技術を扱うことになった。

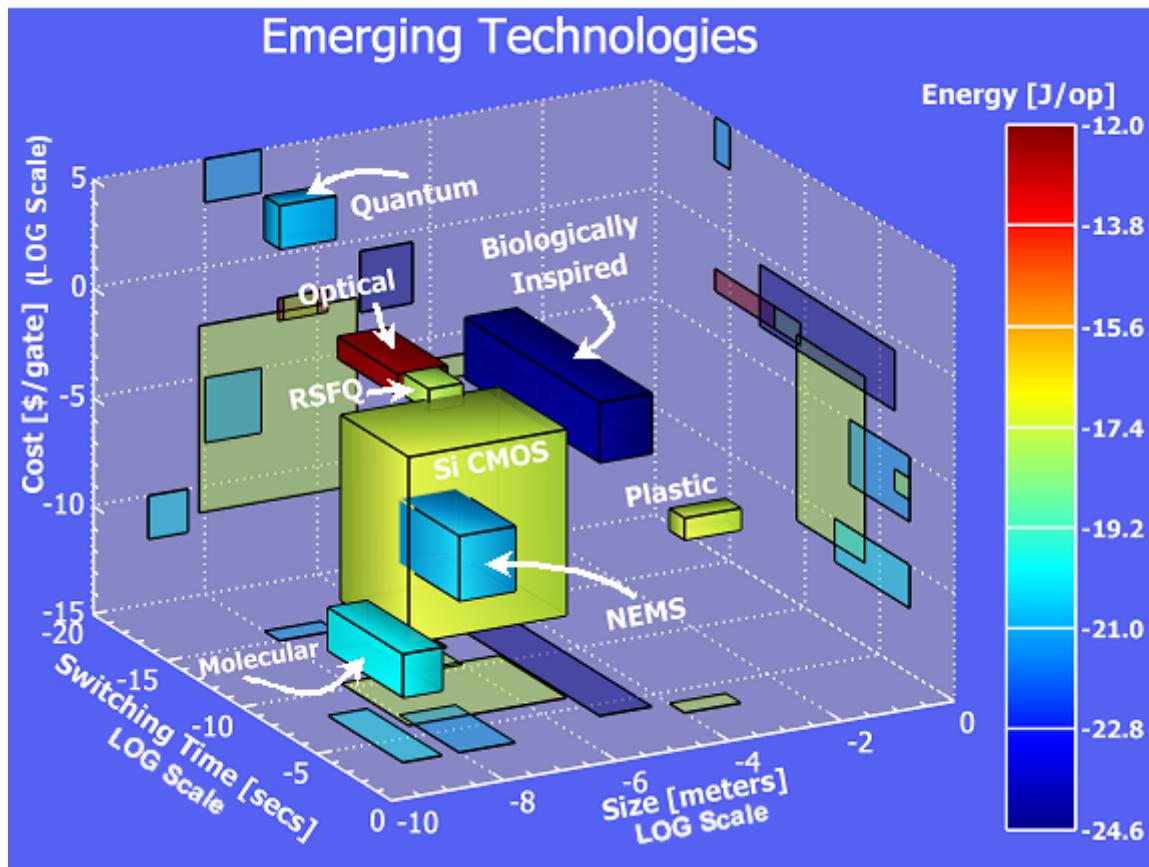

この章の議論は次の 4 つに分類される: 1) 材料、2) メモリデバイス、3) ロジックデバイス、4) 情報処理ナノアーキテクチャ。議論される内容は、それらの動作原理、利点、課題、成熟度、現在および将来の性能等に関する詳細である。さらに、いくつかの情報処理の新手法に関して、それらの性能予測とコスト等についての予備的ではあるが興味深い比較も行った。この比較で明らかになったことは、新探究デバイス、材料、アーキテクチャが成功裏に開発されたとすると、これらは CMOS と同じ領域で CMOS と直接競争するというより、CMOS では達成できないマイクロエレクトロニクスの新領域のアプリケーションを広げるということである。

最後に、この章では、紹介した新概念を支持したり推奨したりするものではない。

Table 52 Difficult Challenges—Emerging Research Device Technologies

| Difficult Challenges $\geq 32\text{ nm}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Summary of Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Development and implementation into manufacturing of a non-volatile memory technology, scalable beyond 32 nm, combining the best performance features of both volatile and non-volatile memory technologies for both stand-alone and embedded applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <p>Identification of the most promising technical approach(es) to obtain electrically accessible, high-speed, high-density, low-power, non-volatile RAM</p> <p>Development of a manufacturable, cost-effective fabrication technology integrable with the process flow for CMOS logic providing for seamless integration onto a CMOS platform</p>                                                                                                                                                                                                                                                                                                                                                                  |

| Difficult Challenges $< 32\text{ nm}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <p>Toward the maturation of CMOS scaling or beyond, discovery, reduction to practice, and implementation into manufacturing of novel, non-CMOS devices and architectures integrable (monolithically, mechanically, or functionally) with a CMOS platform technology.</p> <ul style="list-style-type: none"> <li>● 1D to extend charge based devices.</li> <li>● Articulate the fundamental physical principles needed to develop new device technologies.</li> <li>● Find a new information processing technology that addresses these fundamental principles (see the section entitled “Fundamental Guiding Principles”).</li> <li>● Make emerging logic and memory devices compatible. (A new logic technology may require a new compatible memory technology.)</li> <li>● Integrate the materials, device and architectural communities to interact and collaborate in discovering a new information processing technology.</li> </ul> | <p>No current approaches support the information processing technology required for “Beyond CMOS” satisfying the need for additional decades of functional scaling.</p> <p>Discovery and reduction to practice of new, low-cost methods of manufacturing novel information processing technologies.</p> <p>Any new technology for information processing must be compatible with the new memory technology discussed above; i.e., the logic technology must also provide the access function in a new memory technology.</p> <p>A knowledge gap exists between materials behaviors and device functions.</p> <p>Current metrologies examine fixed material states, but do not probe the state change dynamics.</p> |

## 困難な技術課題 (Difficult Challenges)

### 序章

マイクロエレクトロニクス産業は、CMOS 微細化の成熟を超えて集積回路技術を発展させるに際して、2種の困難な技術課題に直面している。1つは、CMOS 固有の集積度と機能を超えて CMOS を延長することであり、例えば、CMOS プラットフォームに新しい高速、高集積で、不揮発性メモリを含む技術を集積することにより CMOS を延長させることである。もう1種の課題は、CMOS で達成可能な情報処理を本質的に超えて情報処理技術を発展させることであり、これは情報を表現し、処理し、伝達し、記憶する新しい材料、デバイス、アーキテクチャの方法を革新的に組み合わせることにより達成される。これらの困難な技術課題は、この後デバイスと材料に分けて議論することとする。

### デバイス技術

新探究デバイスの困難な技術課題は、さらに、メモリ技術に関する課題とロジックデバイスに関する課題に分けられる。課題の一つは、現在の揮発性と不揮発性メモリの最良の特徴を併せ持ち、しかも CMOS プロセスと互換性のある新メモリ技術が必要なことである。このような技術は、スタンドアローンと混載メモリの双方に必要なメモリデバイス作製プロセスを提供することになるであろう。マイクロプロセッサユニット(MPU)がプログラムを実行する性能は、プロセッサとメモリの相互作用によって制限されており、微細化ではこの問題は解決できない。現在の解決策は、MPU のキャッシュメモリの容量を増やすことであり、その結果、MPU チップ上の SRAM の占有面積が増えている。このトレンドにより、正味の情報処理スループットが実際には下がってしまう。加えて、MPU 上の半導体メモリは不揮発性でないので、(ハードディスクや光 CD などの) アクセスの遅い外部記憶メディアが必要となっている。したがって、電気的にアクセス可能で不揮発性のメモリ、しかも高速で高集積のメモリの開発が、コンピュータアーキテクチャに革命をもたらすことになるかも知れない。このようなメモリの開発は、従来の微細化の恩恵がナノスケール CMOS で完全に実現されたとしても、さらなる情報処理スループットの著しい増大をもたらすことになるであろう。

情報処理の長期的な課題、すなわちロジックデバイスの課題は、「CMOS を超える」アプリケーションに対応する新しくしかも製造可能な情報処理技術の発明と実用である。この課題の解決策は、現状の新情報処理の機能を拡張することにより CMOS 微細化の終焉を超えるナノエレクトロニクスの可能性を拓くことになる。

*Table 53 Difficult Challenges—Emerging Research Materials Technologies*

| <i>Difficult Challenges <math>\geq 32\text{ nm}</math></i>                                    | <i>Summary of Issues</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1D Charge State                                                                               | Nanotube and nanowire properties, bandgap energy and carrier type, and mobility vary greatly at growth and are controlled by variations in composition, diameter and nanometer scale structure.<br>Nanotubes and nanowires grow in random locations and orientations, which is incompatible with high density memory and logic applications.                                                                                                                                                                                                                                                                                        |

| <i>Difficult Challenges <math>&lt; 32\text{ nm}</math></i>                                    | <i>Summary of Issues</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Molecular State: Molecules with Controllable, Reproducible Switching Mechanisms               | Molecular switching is often highly variable between device lots fabricated with the same chemicals and materials.<br>Contact formation and bond structure may require atomic level control. While groups have been able to fabricate devices that exhibited charge storage, complex interactions have been observed with contact materials and redox reactions, but it is often difficult to determine whether switching and transport are through molecular transport or other mechanisms.<br>No metrology tools are available to measure atomic structure details in carbon-based molecules embedded between two contact layers. |

| Spin State: Materials that Enable Spin Gain at Room Temperature and Dissipationless Transport | Ferromagnetic (FM) semiconductors only work at low temperatures $< 200\text{ K}$ ; need a room temperature FM semiconductor.<br>New materials are needed that can enable spin amplification (gain).                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Strongly Correlated Electron State                                                            | Materials with strongly correlated electron states have unique complex interactions between electric and magnetic properties, with complex ferromagnetic, anti-ferromagnetic phase transitions that may support spontaneous spin precipitation. The challenge is to determine whether these properties can be used to enable new devices at the nanometer scale.                                                                                                                                                                                                                                                                    |

| Nanometer Scale Contact and Interface Formation                                               | Materials and processes for establishing interfaces, such as contacts, passivation, etc., must produce interfaces that do not detrimentally affect the state variable or carrier of the state variable, and meet the functional requirements for the device, such as carrier transport.<br>At the nanometer scale, interface materials must have good adhesion, which requires bonding, without detrimentally changing the properties of the device material.                                                                                                                                                                       |

| Assembly of Nano-structured Materials                                                         | Nanostructure materials such as carbon nanotubes (CNTs) or molecules must be assembled in defined locations with controlled orientation and reproducible properties. (CNTs grow in random locations with random orientations.)<br>Molecules only self-organize on a small number of material surfaces and require thiol functionalization for assembly on Au and defect formation is not understood.                                                                                                                                                                                                                                |

## 材料技術

新探求材料の最も困難な課題は、ナノメートルスケールで高集積の新探求デバイスの動作を可能とする制御された特性を有する材料を提供することである。高集積デバイスの材料特性の制御性を向上させるためには、材料の合成法を新計測法やモデリングと結びつける必要がある。デバイス動作に欠かせない制御され再生可能な特性を有する材料を生み出すには、材料の組成とナノ構造の合成をガイドする技術が必要があり、計測法とモデリングのシンポが必須である。

材料に関する困難な技術課題は、いずれも技術の発展のためには欠かせないものである。異なるデバイス構造において性能の潜在能力を解析し、その極限性能を引き出すためには、合成、評価、モデリングの間の協力が必要である。材料の改良と最適化のためには、合成条件とその結果得られた組成と構造、および材料の機能特性との関係を理解する必要がある。したがって、組成、構造、機能特性との関係を確立するには評価を行わなければならず、モデルの確立は材料の機能特性の最適化を加速するのに役立つ。これらの材料に基づくデバイスを探索すると、特性のモデル化とシミュレーションにより新しいデバイスコンセプトが生まれるかも知れない。デバイスが作製されると、それらを機能化させるために異なる材料の最適化が必要になるかも知れない。したがって、構造や組成と機能特性を関係づけるモデルが材料改良を加速するかも知れない。うまく実験から結果が導かれると、デバイス開発、現象モデル、およびナノスケール構造材料の第一原理モデルを加速することは知識ベースを確立するのに非常に重要である。場合によっては、必要な計測法が必ずしも使えないこともあるので、計測ツールと実験を組み合わせることは課題の一つである。

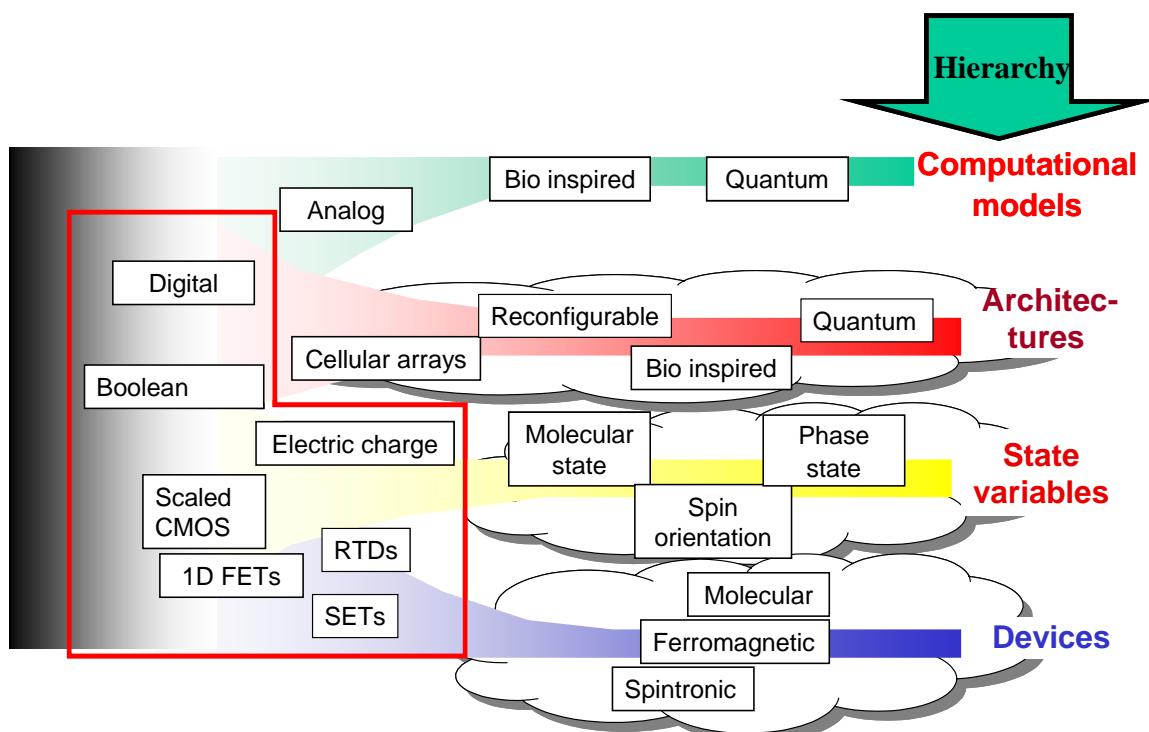

Figure 51 A Taxonomy for Nano Information Processing

## ナノ情報処理の分類

一般に、ある特定のシステム機能を実現する情報処理は、相互に関係する数種の異なる技術の階層を必要とする。これらの階層で最初に挙げるべきものは、必要なアプリケーションやシステム機能であり、システムアーキテクチャ、マイクロまたはナノアーキテクチャ、回路、デバイスと続き、最後は材料であろう。Figure 51 は、この階層を少し異なる方法で表現した。デバイスに代表される最も下の物理レイヤーで始まり、コンピューテーションモデルに代表される最も高いレイヤーで終わる。このより模式的な表現では、一般的な情報処理に焦点を当てており、情報の基本単位(例えばビット)は、計算の状態変数で表現される。たとえば、古いそろばんではビーズの位置、CMOS ロジックではノード容量の電荷すなわち電圧状態である。2 つかそれ以上の許された状態の中から、計算の状態を表現したり操作したりする物理的手段を与えるものがデバイスである。デバイスは、多くの材料の集合からなる物理構造であり、必要な情報処理を行い、多くのプロセスを経て作製される。この階層構造には示されていない重要な階層は、デバイス作製に必要な材料とプロセスである。アーキテクチャ(この例ではナノアーキテクチャ)は、計算モデルを行うデバイスが構成する高次の機能を実行する物理的手段のこ

とである。計算モデルは、情報が処理される手段のことであり、例えばロジック、計算、メモリ、セルラノンリニアネットワーク(CNN)、生体を模した神経機能は、ディジタル、アナログ、または生体を模した方法を利用している。

赤枠で囲んだ部分は、現在の CMOS か、あるいは計算の状態変数として電荷を用いプール代数を使ってディジタル計算を行うアーキテクチャを示している。赤枠の右に示した技術候補は 4 つのグループに分かれて表示されており、新しい状態変数による新ナノアーキテクチャや計算モデルを可能とするデバイスをまとめている。新しい情報処理技術は、それぞれの階層で新しい要素技術の革新的な組み合わせを必要とするであろう。

## メモリデバイス

### 序論

以下に示すメモリ技術は、公開されている研究成果(およそ 2003-2005)の一例であり、現在のメモリの代替技術となりうるアプローチである。歴史的には、実用に耐えるメモリデバイスの研究例は極めて少なく、この表に載っていても技術的にほとんど支持されていないあるいは保証されていない技術もある。反対に、この節を取り上げられていなくても、そのアプローチが全く支持されていない訳ではない。この表から分かるように、現在さまざまなデータ記憶メカニズムが基礎的に探究されている。データ記憶メカニズムの例としては、たとえば絶縁膜に囲まれて分離された電荷、強誘電体ゲート絶縁膜中の残留分極、あるいは様々な現象によって引き起こされた抵抗変化などがあげられる。Table54 には、既存メモリ技術と新探求メモリ技術を 4 つのカテゴリーに分類している。ここで重要な課題は、これらのメモリ候補それぞれを CMOS 技術のプラットフォームにうまく融合させることである。その作製プロセスは、標準 CMOS 技術に対し、若干の変更か追加程度でなければならない。最終目標は、これらのメモリを、あらゆる面で成熟したシリコンメモリチップとして機能するデバイスとしてエンドユーザに提示することである。

これらの新しいメモリは現状のメモリ技術の性能に匹敵するかあるいはそれ以上であることを目指すものである。キーとなる動作パラメータの値を、既存の標準的メモリ技術とプロトタイプのメモリ技術に対して Table55 に示してある。これらのパラメータの値は、それぞれの新探求メモリ技術の現在あるいは将来の性能を比較する上でのベンチマークとなりうるものである。

ロードマップの最新版における新探求メモリ技術の候補は、いくつかの点で、2003 年版のそれとは異なっている。技術候補からはずれたり追加されたりした技術候補の変動が、新探求メモリデバイスの遷移 Table (Table56) に示されている。今回の変化は、1) 相変化メモリをはずす 2) 基板浮遊 DRAM をはずす 3) 単一電子メモリをはずす 4) 強誘電体 FET メモリを候補に加える 4) ポリマーメモリを加える。こうした変化の理由と動機が、Table56 に示されている。

本節では、Table57 の各行の最初に示されている 6 つの技術候補を中心に構成されている。これらの技術候補は、世界的にみて最も活発に研究されている分野を決めるために、文献を系統的にサーベイすることで決定された。議論を簡単にするため、各技術候補は、関連の深いデバイス同士で、分類されている。各技術に関わる、キーとなるパラメータが、表に示されている。各パラメータに対して、以下の 3 種類の数値が示されている。1) 実用化される上で満たすべき最低限の値、2) 計算結果あるいは初期的実験結果に基づき理論的に予測された値、3) 引用した文献で報告された最新の実験値である。

Table57 の最後の列には、過去 2 年間に発表された当該デバイス技術に関する論文の数が示されている。この数値は、研究機関において現在行われている研究の活発さを示す尺度の意味があり、この表に各候補デバイスを含めるかどうかを決める上での、主な指標としている。表には多くの脚注がつけられており、詳細は引用されている文献に示されている可能性がある。表に付随して、各デバイスの動作原理の簡単な要約や表には書かれていません重要事項が文章で書かれている。

## メモリの分類

Table54 では、最も簡単な形でのメモリ技術の分類を行っている。ここでは、メモリセルを構成する機能要素として等価なものを分類している。例えば、アクセストランジスタと記憶蓄積ノードとなるキャパシタからなるおなじみのダイナミック RAM(DRAM)セルは、1トランジスタ-1キャパシタ(1T1C)技術として分類されている。データを磁性材料中のスピン状態として記憶している1トランジスタ-マグネティック RAM(MRAM)のようなセルは、1トランジスタ-1レジスタ(1T1R)技術として表現されている。ここでの抵抗”R”とは、セルの読み出しを、セルを流れる電流をセンスすることで行うということを意味している。このような分類から、等価の要素部品の数を最小にしてセルを単純化する(即ち、セル面積を縮小する)方向性を見て取ることができる。即ち、技術の開発初期では、マルチ・トランジスタ マルチ  $\times$  セル( $\times$  はキャパシタあるいは抵抗)となるのが一般的である。技術が成熟するにつれて、構造は生産性の高い1T1 $\times$ 型に単純化される。最も理想に近い構成は、1T セルのように、データ記憶部をトランジスタ中に埋め込むことである。超高集積ナノエレクトロニクス・メモリアレイでは、トランジスタ ”T”的代わりに、ダイオードのような2端子の非線形素子を、抵抗型メモリ素子とともに用いることができるかもしれない。そのような構造は、1ダイオード - 1レジスタ(1D1R)技術と表される。

新技術を差別化する重要な特性は、電源なしでもデータを保持することができるかどうか、である。不揮発性メモリは、根本的に有用性の高いものであり、不揮発性がどの程度保持されるかは、データを保持できる時間で表すことができる。揮発性メモリもまた、それぞれ特徴的なメモリ保持時間を持っており、その値は、ミリ秒から(実用性から)電源が保持される時間まで、様々である。

Table 54 Memory Taxonomy

| Cell Element     | Type                               | Non-volatility | Retention Time |

|------------------|------------------------------------|----------------|----------------|

| 1T1R or 1D1R [A] | MRAM                               | Non-volatile   | > 10 years     |

|                  | Phase Change Memory                | Non-volatile   | > 10 years     |

|                  | Polymer Memory                     | Non-volatile   | > 10 years     |

|                  | Molecular memory                   | Non-Volatile   | > years        |

|                  | Insulator Resistance Change Memory | Non-Volatile   | > years        |

| 1T1C [A]         | DRAM                               | Volatile       | ~ seconds      |

|                  | FeRAM                              | Non-volatile   | > 10 years     |

| 1T [A]           | FB DRAM                            | Volatile       | < seconds      |

|                  | Flash Memory                       | Non-volatile   | > 10 years     |

|                  | SONOS                              | Non-volatile   | > 10 years     |

|                  | Nano Floating Gate Memory          | Non-volatile   | > 10 years     |

|                  | Engineered Tunnel Barrier Memory   | Non-volatile   | > 10 years     |

|                  | FeFET Memory                       | Non-volatile   | > years        |

| Multiple T [A]   | SRAM                               | Volatile       | large          |

|                  | STTM [B]                           | Volatile       | small          |

Notes for Table 54:

[A] 1T1R 1トランジスタ 1 抵抗 1DIR—1ダイオード 1 抵抗 1T1C 1トランジスタ 1 キャパシタ IT 1 トランジスタ FB DRAM 浮遊基板DRAM FeFET—強誘電体 FET Multiple T 複数トランジスタ SONOS—シリコン/酸化膜/窒化膜/酸化膜/シリコン

[B] STTM—微細化可能な2トランジスタメモリ—Yi, J. H., W. S. Kim, S. Song, Y. Khang, H.-J. Kim, J. H. Choi, H. H. Lim, N. I. Lee, K. Fujihara, H.-K. Kang, J. T. Moon, and M. Y. Lee. “Scalable Two-transistor Memory (STTM),” IEDM. (2001) 36.1.1-4.

Table 55 Current Baseline and Prototypical Memory Technologies

|                                    |      | Baseline Technologies |                  |                                  |                         | Prototypical Technologies |                          |                                                    |                                                                                    |                                                      |

|------------------------------------|------|-----------------------|------------------|----------------------------------|-------------------------|---------------------------|--------------------------|----------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------|

|                                    |      | DRAM                  |                  | SRAM<br>[A]                      | Floating Gate<br>[B]    |                           | SONOS                    | FeRAM                                              | MRAM                                                                               | PCM                                                  |

|                                    |      | Stand-alone           | Embed-<br>ded    |                                  | NOR                     | NAND                      |                          |                                                    |                                                                                    |                                                      |

| <i>Storage Mechanism</i>           |      | Charge on a capacitor |                  | Interlocked state of logic gates | Charge on floating gate |                           | Charge in gate insulator | Remanent polarization on a ferroelectric capacitor | Magnetization of ferroelectric contacts                                            | Reversibly changing amorphous and crystalline phases |

| <i>Cell Elements</i>               |      | 1T1C                  |                  | 6T                               | 1T                      |                           | 1T                       | 1T1C                                               | 1T1R                                                                               | 1T1R                                                 |

| <i>Feature size F, nm</i>          | 2005 | 80                    | 130              | 90                               | 130                     | 130                       | 100                      | 130                                                | 180                                                                                | 90                                                   |

|                                    | 2018 | 18                    | 25               | 18                               | 25                      | 25                        | 20                       | 25                                                 | 22                                                                                 | 18                                                   |

| <i>Cell Area</i>                   | 2005 | 7.5F <sup>2</sup>     | 12F <sup>2</sup> | 140 F <sup>2</sup>               | 10 F <sup>2</sup>       | 5 F <sup>2</sup>          | 7F <sup>2</sup>          | 34F <sup>2</sup>                                   | 25F <sup>2</sup>                                                                   | 7.2F <sup>2</sup>                                    |

|                                    | 2018 | 5F <sup>2</sup>       | 12F <sup>2</sup> | 140 F <sup>2</sup>               | 10 F <sup>2</sup>       | 5 F <sup>2</sup>          | 5.5F <sup>2</sup>        | 16F <sup>2</sup>                                   | 16F <sup>2</sup>                                                                   | 4.7F <sup>2</sup>                                    |

| <i>Read Time</i>                   | 2005 | <15 ns                | 1 ns             | 0.4 ns                           | 14 ns                   | 70 ns                     | 14 ns                    | 80 ns [D]                                          | <25 ns [G]                                                                         | 60 ns [I]                                            |

|                                    | 2018 | <15 ns                | <1 ns            | 70 ps                            | 2.5 ns                  | 12 ns                     | 2.5 ns                   | <20 ns [E]                                         | <0.5 ns                                                                            | <60 ns                                               |

| <i>W/E time</i>                    | 2005 | <15 ns                | 1 ns             | 0.4 ns                           | 1 □s/<br>10 ms          | 1 ms/<br>0.1 ms           | 20 □s/20ms [J]           | 15 ns [F]                                          | <25 ns [G]                                                                         | 50/120 ns [I]                                        |

|                                    | 2018 | <15 ns                | 0.2 ns           | <0.1 ns                          | 1 □s/<br>10 ms          | 1 ms/<br>0.1 ms           | ~10 □s/10ms              | 1 ns                                               | <0.5 ns [H]                                                                        | Not known                                            |

| <i>Retention Time</i>              | 2005 | 64 ms                 | 64 ms            | [C]                              | >10 y                   | >10 y                     | >10 y                    | >10 y                                              | >10 y                                                                              | >10 y                                                |

|                                    | 2018 | 64 ms                 | 64 ms            | [C]                              | >10 y                   | >10 y                     | >10 y                    | >10 y                                              | >10 y                                                                              | >10 y                                                |

| <i>Write Cycles</i>                | 2005 | >3E16                 | >3E16            | >3E16                            | >1E5                    | >1E5                      | 1E7                      | 1E13                                               | >1E15                                                                              | 1E12                                                 |

|                                    | 2018 | >3E16                 | >3E16            | >3E16                            | >1E5                    | >1E5                      | 1E9                      | >1E16                                              | >1E15                                                                              | 1E15                                                 |

| <i>Write operating voltage (V)</i> | 2005 | 2.5                   | 2.5              | 1.2                              | 12                      | 15                        | 5-6                      | 0.9-3.3                                            | 1.8[G]                                                                             | 3[I]                                                 |

|                                    | 2018 | 1.5                   | 1.5              | 0.7                              | 12                      | 15                        | 4.0-4.5                  | 0.7 - 1                                            | <1.8                                                                               | <3                                                   |

| <i>Read operating voltage (V)</i>  | 2005 | 2.5                   | 2.5              | 1.2                              | 2.5                     | 2.5                       | 2.5                      | 0.9-3.3                                            | 1.8[G]                                                                             | 3                                                    |

|                                    | 2018 | 1.5                   | 1.5              | 0.8                              | 1.2                     | 1.2                       | 2.5                      | 0.7-1                                              | <1.8                                                                               | <3                                                   |

| <i>Write energy (J/bit)</i>        | 2005 | 1E-16                 | 1E-16            | 7E-16                            | 8E-15                   | 8E-15                     | 2E-15                    | 2E-14                                              | 1E-10                                                                              | 1E-10                                                |

|                                    | 2018 | 4E-17                 | 4E-17            | 2E-17                            | 3E-15                   | 3E-15                     | 3E-16                    | 4E-15                                              | 2E-11                                                                              | Not known                                            |

| <i>Comments</i>                    |      |                       |                  |                                  |                         |                           |                          | Destructive read-out                               | Spin-polarized Write has a potential to lower Write current density and energy [K] |                                                      |

Notes for Table 55:

[A] 高性能混載 SRAM (システムドライバの章の混載メモリへの要求の表を参照)

[B] 混載応用 (システムドライバの章の混載メモリへの要求の表を参照)

[C] SRAM の記憶状態は電源電圧が印加されている間は保持される

[D] Kim, K. and Y. J. Song. "Current and future high density FRAM technology," Integr. Ferroelectrics. 61 (2004) 3-15.

[E] Nanoelectronics and Information Technology, Ed. Rainer Waser, Wiley-VCH, 2003, 568-569.

[F] Moise, T., et al. IEDM 2002, session 21 (2002).

[G] Andre, T. W., J. J. Nahas, C. K. Subramanian, B. J. Garni, H. S. Lin, A. Omair, and W. L. Martino. "A 4-Mb 0.18-□m 1T1MTJ toggle MRAM with balanced three input sensing scheme and locally mirrored unidirectional write drivers."

[H] Schumacher, H. W. "Ballistic bit addressing in a magnetic memory cell array," Appl. Phys. Lett. 87.4 (2005) 42504.

[I] Cho, W. Y., B-H Cho, B-G Choi, H-R Oh, S. Kang, K-S. Kim, K-H. Kim, D-E. Kim, C-K. Kwak, H-G. Byun, Y. Hwang, S. J. Ahn, G-H. Koh, G. Jeong, H. Jeong, and K. Kim. "A 0.18-μm 3.0-V 64-Mb nonvolatile phase-transition random access memory (PRAM)," IEEE J. Solid-State Circuits. 40.1 (2005) 291-300.

[J] Seo, M-K., S-H Sim, M-H Oh, H-S Lee, S-W. Kim, I-W. Cho, G-H. Kim, and M-G. Kim. "A 130-nm 0.9-V 66-Mhz 8-Mb (256 x 32) local SONOS embedded flash EEPROM," IEEE J. Sol.-State Circ. 40.4 (2005) 877-883.

[K] Jiang, Y., T. Nozaki, S. Abe, T. Ochiai, A. Hirohata, N. Tezuka, K. Inomata. "Substantial reduction of critical current for magnetization switching in an exchange-biased spin valve", Nature Materials. 3 (2004) 361-364.

Table 56 Transition Table for Emerging Memory Devices

|                                 | <i>IN/OUT (Table 64)</i> | <i>Reason for IN/OUT</i>                                                                       | <i>Comment</i>                                                                                     |

|---------------------------------|--------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| <i>Ferroelectric FET Memory</i> | <b>IN</b>                | <b>Based on physics of operation, this memory has potential not realized in existing FeRAM</b> | <b>Some features of Nano-Ferroelectric memory: Nanoscale FE capacitor, non-destructive readout</b> |

| <i>Polymer Memory</i>           | <b>IN</b>                | <b>New materials structure, promising characteristics, several recent publications</b>         | <b>PM is different from MIM memory: it consist of MIMIM structure</b>                              |

| <i>Single-electron memory</i>   | <b>OUT</b>               | <b>It does not fit any of the application categories</b>                                       | <b>Small retention time, slow write, high soft error rate (SER)</b>                                |

| <i>Floating body DRAM</i>       | <b>OUT</b>               | <b>It became a mature prototypical technology</b>                                              | <b>Not presented in PIDS chapter in 2005 ITRS</b>                                                  |

| <i>PCM</i>                      | <b>OUT</b>               | <b>It became a mature prototypical technology</b>                                              | <b>Presented in the 2005 <i>PIDS chapter</i></b>                                                   |

Table 57 Emerging Research Memory Devices—Demonstrated and Projected Parameters

|                                    |                  | Nano-floating Gate Memory [A]                   | Engineered Tunnel Barrier Memory | Ferroelectric FET Memory                                 | Insulator Resistance Change Memory                                                   | Polymer Memory        | Molecular Memories    |

|------------------------------------|------------------|-------------------------------------------------|----------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------|-----------------------|

| <i>Storage Mechanism</i>           |                  | Charge on floating gate                         | Charge on floating gate          | Remanent polarization on a ferroelectric gate dielectric | Multiple mechanisms                                                                  | Not known             | Not known             |

| <i>Cell Elements</i>               |                  | 1T                                              | 1T                               | 1T                                                       | 1T1R or 1R                                                                           | 1T1R or 1R            | 1T1R or 1R            |

| <i>Device Types</i>                |                  | 1 Nanocrystal<br>2 Direct tunneling             | Graded insulator                 | FET with FE gate insulator                               | 1 M-I-M<br>2 Solid Electrolyte<br>3 FE tunneling<br>4 FE Schottky diode<br>5 FE-I-FE | M-I-M (nc)-I-M        | Bi-stable switch      |

| <i>Feature size F</i>              | Minimum required | <65 nm                                          | <65 nm                           | <65 nm                                                   | <65 nm                                                                               | <65 nm                | <65 nm                |

|                                    | Best projected   | 25 nm                                           | 10 nm [H]                        | 22 nm [K]                                                | 5–10 nm [O]                                                                          | 5–10 nm               | 5–10 nm [AA]          |

|                                    | Demonstrated     | 90 nm [A]                                       | 180 nm [I]                       | ~10 µm [L]                                               | 100 nm [P]                                                                           | 200 µm [W]            | 30 nm [AB]            |

| <i>Cell Area</i>                   | Minimum required | 10F <sup>2</sup>                                | 10 F <sup>2</sup>                | 8F <sup>2</sup>                                          | 10 F <sup>2</sup>                                                                    | 10 F <sup>2</sup>     | 10 F <sup>2</sup>     |

|                                    | Best projected   | 8–10F <sup>2</sup>                              | 8F <sup>2</sup> [H]              | 8F <sup>2</sup>                                          | 8/5F <sup>2</sup> [Q]                                                                | 8/5F <sup>2</sup>     | 5F <sup>2</sup>       |

|                                    | Demonstrated     | 16F <sup>2</sup> [A]                            | Data not available               | Data not available                                       | Data not available                                                                   | Data not available    | Data not available    |

| <i>Read Time</i>                   | Minimum required | <15 ns                                          | <15 ns                           | <15 ns                                                   | <15 ns                                                                               | <15 ns                | <15 ns                |

|                                    | Best projected   | 2.5 ns                                          | 2.5 ns                           | 2.5 ns                                                   | <10 ns                                                                               | <10 ns                | <10 ns [AA]           |

|                                    | Demonstrated     | 20 ns [B]                                       | 20 ns [B]                        | 20 ns [B]                                                | 2 ms [R]                                                                             | ~10 ns [X]            | Data not available    |

| <i>W/E time</i>                    | Minimum required | 1 µs/10 ms                                      | 1 µs/10 ms                       | Application dependent                                    | Application dependent                                                                | Application dependent | Application dependent |

|                                    | Best projected   | 1 µs/10 ms                                      | 1 ns at 9V[H]                    | 2.5 ns [B]                                               | <20 ns [P]                                                                           | Not known             | <40 ns [AA]           |

|                                    | Demonstrated     | W: 1–10 µs [C]<br>E: 10–100 ms [D]              | E: ~10 ms [I]                    | 500 ns [L]                                               | 25 ns [P]                                                                            | <10 ns [X]            | ~sec [AC]             |

| <i>Retention Time</i>              | Minimum required | >10 y                                           | >10 y                            | >10 y                                                    | >10 y                                                                                | >10 y                 | >10 y                 |

|                                    | Best projected   | >10 y                                           | >10 y                            | >1y                                                      | >10 y                                                                                | Not known             | Not known             |

|                                    | Demonstrated     | >200 hours [E]                                  | >10 y [I]                        | 30 days [M]                                              | 1 y [S]                                                                              | 6 month [Y]           | 2 months [AC]         |

| <i>Write Cycles</i>                | Minimum required | >1E5                                            | >1E5                             | >1E5                                                     | >1E5                                                                                 | >1E5                  | >1E5                  |

|                                    | Best projected   | >1E5                                            | >3E16                            | >3E16                                                    | >3E16                                                                                | >3E16                 | >3E16                 |

|                                    | Demonstrated     | >1E4 [A]                                        | 5E4 [J]                          | 1E12 [O]                                                 | 1E5 [T]                                                                              | >1E6 [X]              | >2E3 [AD]             |

| <i>Write Operating Voltage (V)</i> | Minimum required | Application dependent                           | Application dependent            | Application dependent                                    | Application dependent                                                                | Application dependent | Application dependent |

|                                    | Best projected   | >3 V [F]                                        | >3 V [F]                         | <0.9 V [K]                                               | <0.5 V [U]                                                                           | Not known             | 2 V [AE]              |

|                                    | Demonstrated     | ±6 [A]                                          | 6.5 [I]                          | ±6 [O]                                                   | 0.24 V [P]                                                                           | ~±2 [X]               | ~±1.5 V [AB]          |

| <i>Read Operating Voltage (V)</i>  | Min. required    | 2.5                                             | 2.5                              | 2.5                                                      | 2.5                                                                                  | 2.5                   | 2.5                   |

|                                    | Best projected   | 0.7                                             | 0.7                              | 0.7                                                      | <0.2 V [U]                                                                           | 0.7                   | 0.3 [AA]              |

|                                    | Demonstrated     | 2.5 [B]                                         | 2.5 [B]                          | 2.5 [B]                                                  | ~0.2 V[P]                                                                            | ~1 [X]                | 0.5 [AB]              |

| <i>Write Energy (J/bit)</i>        | Min. required    | Application dependent                           | Application dependent            | Application dependent                                    | Application dependent                                                                | Application dependent | Application dependent |

|                                    | Best projected   | 5E-16 [G]                                       | 5E-16 [G]                        | 2E-15 [N]                                                | 1E-15 [V]                                                                            | Not known             | 2E-14 [AA]            |

|                                    | Demonstrated     | 2E-15 [G]                                       | Data not available               | Data not available                                       | 5E-14 [P]                                                                            | 1E-13 [Z]             | Data not available    |

| <i>Comments</i>                    |                  | A natural evolution of the floating gate memory |                                  | Potential for non-destructive readout                    | Low read voltage presents a problem                                                  |                       |                       |

| <i>Research activity [AE]</i>      |                  | 123                                             | 12                               | 74                                                       | 39                                                                                   | 25                    | 68                    |

- [A] 記述の一貫性のため、浮遊ゲートメモリに関する全ての数値は、一つの文献と一種類のメモリを参照したものである： Freescale ナノクリスタルメモリ、NOR 構成—Muralidhar, R., et al., “A 6V Embedded Silicon Nanocrystal Nonvolatile Memory for the 90 nm Technology Node,” IEDM Digest. (2003).

- [B] 浮遊ゲートとSONOSのデータに基づく（Table 55 参照）。全ての1T メモリデバイスの読み出し電圧と読み出し時間は同程度であると考えられる。

- [C] ホットエレクトロン注入—Muralidhar, R., et al. “A 6V Embedded Silicon Nanocrystal Nonvolatile Memory for the 90 nm Technology Node,” IEDM Digest. (2003).

- [D] Fowler-Nordheim 注入—Muralidhar, R., et al. “A 6V Embedded Silicon Nanocrystal Nonvolatile Memory for the 90 nm Technology Node,” IEDM Digest. (2003).

- [E] 実験的には >200 h のデータ保持時間が観測された。表の数値は、実験データと第一原理モデリングの下に予測されたもの—Muralidhar, R., et al. “A 6V Embedded Silicon Nanocrystal Nonvolatile Memory for the 90 nm Technology Node,” IEDM Digest. (2003).

- [F] 不揮発電荷保持特性のための最小パリア高さ1.5 eV に基づいたもの

- [G] 計算は、最大プログラム電圧と配線キャパシタンスに基づいている—（システムドライバの章の混載メモリへの要求の表の脚注 [6] 参照）。

- [H] Likharev, K. K., “Riding the crest of a new wave in memory,” IEEE Circ. and Dev. 16.4 (2000) 16–21.

- [I] Blomme, P.; B. Govoreanu, M. Rosmeulen, A. Akheyar, L. Haspeslagh, J. DeVos, M. Lorenzini, J. Van Houdt, and K. DeMeyer. “High-k materials for tunnel barrier engineering in floating-gate flash memories,” 208th Electrochemical Society Meeting. ECS, 2005. (2005) 16–21.

- [J] Blomme, P., B. Govoreanu, M. Rosmeulen, J. Van Houdt, and K. DeMeyer. “Multilayer tunneling barriers for nonvolatile memory application,” in: 60th Device Research Conference. (2002) 153–154.

- [K] Fitzilis, M., Y. Mustafa, and R. Waser. “Scaling the ferroelectric field effect transistor,” Integrated Ferroelectrics. 70 (2005) 29–44.

- [L] Sakai, S., and R. Ilangoan, “Metal-Ferroelectric-Insulator-Semiconductor memory FET with long retention and high endurance,” IEEE Electron Dev. Lett. 25.6 (2004) 369–371.

- [M] Takahashi, K., B.-E. Park, K. Aizawa, and H. Ishiwara. “30-day-long Data Retention in Ferroelectric-gate FETs with HfO<sub>2</sub> Buffer Layers,” SSDM 2004, Tokyo. Paper No. D-1-2 (2004).

- [N] 文献[K] に示されている微細FE キャパシタのパラメータに基づいた計算

- [O] 見積もりは、導電パッドサイズ(10 kOhms の最大 ON 抵抗)と隣接セル間の絶縁距離に基づいて行われた。

- [P] Kozicki, M. N., M. Mitkova, M. Park, M. Balakrishnan, and C. Gopalan. “Information storage using nanoscale electrodeposition of metal in solid electrolytes,” Superlat. and Microstr. 34 (2003) 459–465.

- [Q] 1TIR に対しては 8F<sup>2</sup>、1R セルに対しては 5F<sup>2</sup>

- [R] Beck, A., J. G. Bednorz, C. Gerber, C. Rossel, and D. Widmer. “Reproducible Switching Effect in Thin Oxide Films for Memory Applications,” Appl. Phys. Lett. 77 (2000) 139.

- [S] Watanabe, Y., J. G. Bednorz, A. Bietsch, Ch. Gerber, D. Widmer, A. Beck, S. J. Wind, “Current-driven Insulator-conductor Transition and Non-volatile Memory in Chromium-doped SrTiO<sub>3</sub> Single Crystals,” Appl. Phys. Lett. 78 (2001) 3738.

- [T] Seo, S., M. J. Lee, D. H. Seo, S. K. Choi, D.-S. Suh, Y. S. Joung, I. K. Yoo, I. S. Byun, I. R. Hwang, S. H. Kim, and B. H. Park. “Conductivity switching characteristics and reset currents in NiO dilms,” Appl. Phys. Lett. 86 (2005) 093509.

- [U] 電気化学的セルポテンシャルが書き込み電圧を制御する。適切な組み合わせの下では、0.5 V でいくらかの安全マージンが残るであろう。読み出し電圧は非常に小さくなるであろう。

- [V]  $V=0.2 \text{ Volts}$ ,  $R_{ON}=2E5 \text{ Ohm}$ ,  $t_w=10 \text{ ns}$  の下で、 $E \sim 0.5 * V^2 / R_{ON} * t_w$  として見積もった

- [W] Ouyang, J., C. W. Chu, C. R. Szmanda, L. P. Ma, and Y. Yang. “Programmable polymer thin film and non-volatile memory device”, Nature Materials. 3.12 (2004) 918–922.

- [X] Ma, L. P., J. Liu, and Y. Yang. “Organic electrical bistable devices and rewritable memory cells,” Appl. Phys. Lett. 80.16 (2002) 2997–2999.

- [Y] Ma, L. P., Q. Xu, and Y. Yang. “Organic non-volatile memory by controlling the dynamic copper-ion concentration within organic layer”, Appl. Phys. Lett. 84.24 (2004) 4908–4910.

- [Z] 文献[AB] で報告されている以下の実験データに基づいて見積もられた:  $E \sim 0.5 * V^2 * I_{ON} * t_w$  for  $V_{ON}=2 \text{ Volts}$ ,  $I_{ON}=10 \text{ mA}$ ,  $t_w=10 \text{ ns}$ .

- [AA] DeHon, A., S. C. Goldstein, P. J. Kuekes, P. Lincoln. “Nonphotolithographic nanoscale memory density prospects,” IEEE Trans. Nanotechnology. 4.2 (2005) 215–228.

- [AB] Wu, W., G-Y. Jung, D. L. Olynick, J. Straznicky, Z. Li, X. Li, D. A. A. Ohlberg, Y. Chen, S-Y. Wang, J. A. Liddle, W. M. Tong, and R. S. Williams. “One-kilobit cross-bar molecular memory circuits at 30-nm half-pitch fabricated by nanoimprint lithography,” Appl. Phys. A. 80 (2005) 1173–1178.

- [AC] Chen Y., D. A. A. Ohlberg, X. M. Li, D. R. Stewart, R. S. Williams, J. O. Jeppesen, K. A. Nielsen, J. F. Stoddart, D. L. Olynick, E. Anderson, “Nanoscale Molecular-switch Devices Fabricated by Imprint Lithography,” Appl. Phys. Lett 82 (2003) 1610.

- [AD] Wu, W., G-Y. Jung, D. L. Olynick, J. Straznicky, Z. Li, X. Li, D. A. A. Ohlberg, Y. Chen, S-Y. Wang, J. A. Liddle, W. M. Tong, and R. S. Williams. “One-kilobit cross-bar molecular memory circuits at 30-nm half-pitch fabricated by nanoimprint lithography,” Appl. Phys. A. 80 (2005) 1173–1178

- [AE] 7/1/2003–7/1/2005 の間の Science Citation Index database に現れた、技術論文中での引用文献数

## メモリデバイス - 表掲載技術の定義と議論 -

ナノ浮遊ゲートメモリ(NFGM) —NFGMは、従来の浮遊ゲートメモリとSONOSメモリを進化させたものである。浮遊ゲートメモリの特性を向上させるために2つのアプローチが提案されている。1) ホットキャリア注入とFowler-Nordheim (F-N)トンネリング<sup>1</sup>による孤立トラップ蓄積ノードへの電荷注入、2) 直接トンネリングによる孤立トラップ蓄積ノードへの電荷注入<sup>2</sup>。ナノクリスタルメモリデバイスでは、電気的に絶縁されたナノクリスタルに電荷を蓄積することにより、電荷蓄積層から下地酸化膜への電荷ロスが緩和できる。35Åよりも薄いトンネル酸化膜では、プログラム書き込みや消去は、量子力学的直接トンネリングによって行われるかもしれない。通常不揮発用途で必要な、より厚い酸化膜に対しては、電荷はホットエレクトロン注入によって書き込まれ、Fowler-Nordheimトンネリングによって消去されるかもしれない。このデバイスの研究の殆どは、シリコン・ナノクリスタルを用いて行われているが、適切な伝導帯端の不連続量をもつように材料を選択したナノクリスタルを用いることで、デバイス特性を最適化できる。

孤立トラップ蓄積ノードをもつNFGMでは、浮遊ゲートは、多重のナノクリタル・ドットが絶縁膜中の電荷トラップ欠陥<sup>3</sup>からなる。多重浮遊ドットはそれぞれ分離していて独立であるので、電子は異なった経路でドットに注入される。この孤立トラップメモリによって、電荷保持時間を改善することができる。ナノ浮遊ゲートデバイスはトンネル酸化膜の局所的な欠陥による電荷ロスを緩和できるので、トンネル酸化膜を通常の浮遊ゲート技術のおよそ10nmから、およそ5nmまでスケーリングすることができる。これにより、動作電源電圧はおよそ9Vからおよそ6Vまでスケーリングすることができる<sup>4</sup>。

NFGMは、これまでの浮遊ゲートメモリの自然の進化であり、動作パラメータの改善は限定的である(Table55と57参照)。そのスピードや電圧をロジックデバイスに匹敵させることは不可能かもしれない。

トンネル障壁エンジニアリングメモリとしては、傾斜(例えば、「鶏冠状」)バリア浮遊ゲートメモリ<sup>5, 6</sup>や酸化膜厚可変浮遊ゲートメモリ(VARIOT)<sup>7</sup>が含まれる。傾斜バリアの考え方では、絶縁膜の積層構造を使って、蓄積ノードからの実効的トンネリングや蓄積ノードへの実効的トンネリングを可能にする特有のバリア形状を作り出す。傾斜バリアをもつ浮遊ゲートの考え方には、非常に魅力的であるが、積層絶縁膜によるトンネルバリアを実現することは非常に難しい。実現のためには、バンドギャップや誘電率に傾斜をもつ新しい絶縁膜材料が必要である。傾斜絶縁膜電子材料という考え方には、傾斜III-Vヘテロ構造と類似したものである。傾斜Al<sub>x</sub>Ga<sub>1-x</sub>As/GaAs構造が、傾斜電荷注入バリアを形成するために使われてあり<sup>8</sup>、上記の傾斜注入バリアメモリの考え方のさきがけとして実験的に実証されていることは注目に値する。鶏冠状トンネルバリア積層構造Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>が実験的に調べられ、NVM特性が改善することが報告されている<sup>9</sup>。また、最近の研究では、AlO<sub>x</sub>やHfO<sub>2</sub><sup>10, 11</sup>層が、傾斜トンネルバリアのための候補材料系の一つとして検討されている。

VARIOTメモリでは、誘電率の異なる2層の積層絶縁膜が使われる。この構造により、良好なデータ保持特性を保ったまま、比較的低い印加電圧の下で高いトンネル電流が得られる。トンネルバリアを工夫することにより、メモリセルへの書き込みや消去に必要な電圧を低下させることが可能である。SiO<sub>2</sub>とHfO<sub>2</sub>あるいはAl<sub>2</sub>O<sub>3</sub>からなる積層構造が実験的に検討されており、すでにトンネリングによるプログラム電圧の低下と10年のデータ保持特性が得られることが示されている。

**強誘電体FETメモリ** — 従来の1T1C強誘電体RAM(FeRAM)では、DRAMセルキャパシタに蓄積される電荷量と同じオーダーのスイッチング可能な分極電荷が必要である。この結果、3-D立体型強誘電体キャパシタが必要になり、このキャパシタ面積の要求により、微細化限界をもつ。これに対し、強誘電体キャパシタをFETのゲットスタック構造に組み込むならば、強誘電性分極がチャネルのキャリアに直接影響を与えることで、FET入力特性のシフトがもたらされる。この1Tメモリを強誘電体FET(FeFET)<sup>12</sup>と呼ぶ。チャネルとの界面での低い界面準位を保証するために、高品質の絶縁膜が必要である。このため、実際のデバイスでは、金属-強誘電体-絶縁膜-半導体(MFIS)のゲットスタック構造となる。場合によっては、もう一つの金属層を強誘電体層と絶縁層の間に形成する(MFMIS)こともある。FeFET素子は、MOSFETと同様にスケーリングできる。しかしながら、ス

ケーリングできるのは 22nmノード辺りまでであると考えられている。これは、絶縁層が非常に薄くなり、抗電界の膜厚依存性の観点から、強誘電体の特性を維持するためには、この世代の膜厚よりも薄くすることができないことによる<sup>13</sup>。この 10 年間、FeFETを用いた不揮発性メモリを作製する試みが、数多く行われてきた。その結果として、最大の課題はデータ保持時間が短い点にあることが明らかとなった。これは、強誘電体の分極電荷を、リークによる電荷が遮蔽することによって引き起こされる。最近、データ保持時間の大変な改善が報告された<sup>14, 15</sup>。疲労やインプリントのような他の信頼性上の課題については、まだ十分に研究されておらず、理解されていない。

**絶縁体抵抗変化メモリ** — 一群の金属-絶縁体-金属(MIM)系は電気パルスによる抵抗変化効果を示す。この効果の背景となるメカニズムを、次のカテゴリーに分類することができる。

- 1) 電極材料あるいは絶縁体あるいはその両方に含まれる酸化還元反応。ここで絶縁体はイオン性伝導をもつことが必要である。材料系としては、酸化物、高次のカルコゲナイト(非晶質を含む)、半導体、更にポリマーを含む有機化合物である。ここでの変化量は、陽イオンの輸送、電極還元反応、金属フィラメントの成長である。主にAgやCuを含む材料系を用いて、セル動作の実証に成功している<sup>16, 17</sup>。このとき、対抗電極間に繋ぐフィラメントが形成されると低抵抗状態になる。一方、酸化によりフィラメントが分解すると高抵抗状態に戻る。他には、絶縁体それ自身の中での電気伝導を誘起する酸化還元反応に起因するものもある<sup>18, 19, 20</sup>。多くの場合、双安定スイッチを起こす前に、何らかの形成過程が必要である。この電気伝導の多くは、極めて局所的である。この効果が制御できれば、双安定スイッチング過程に基づいたメモリは、極めて小さなサイズまで微細化できる。この現象のスイッチング速度は、イオンの輸送によって制限される。双安定スイッチングを制御している酸化還元反応に関わる実際の距離が小さければ(< 10 nmの領域)、スイッチング時間は数ナノ秒程度に短くすることが可能である。しかしながら、報告されている現象のメカニズムの詳細がまだ分かっていないため、スイッチング時間を正確に予測することは可能ではない。

- 2) 強誘電体分極効果。強誘電性分極が超薄絶縁膜のトンネル特性や隣接している半導体層のショットキー型空間電荷層を変調していることが考えられる<sup>21, 22</sup>。いくつかの研究成果が文献に報告されている。このメモリの基本的な構成要素は、リーク電流に再現性のあるヒステリシスを示すCrをドープした (Ba, Sr)TiO<sub>3</sub> や SrZrO<sub>3</sub> のような絶縁体を使った金属-絶縁体-金属(MIM)構造<sup>23, 24, 25, 26</sup>である。書き込み動作は、このMIM構造に電圧を印加して、低抵抗状態と高抵抗状態を可逆的にスイッチさせることにより行われる。この構造で、多値のスイッチングも実現できる。データの読み出しは、書き込み電圧よりも低い電圧(典型的読み出し電圧は 0.5V 以下)をMIM構造に印加して、その抵抗を測定することによって行われる。このようなMIM構造のデータ保持時間は、極めて長いものがあり、1 年のデータ保持時間という結果が実験的に示されている。安定で再現性のあるヒステリシスがMIM構造で報告されている一方で、センス用トランジスタと集積化した実用的セルはまだ実証されていない。また、現段階では、観測されている可逆的スイッチング現象の起源が強誘電性であるかどうかは十分確認されている訳ではない。ある場合では、可逆的導電フィラメントの生成と消滅が起こっていることが報告されている<sup>27</sup>。

**ポリマーメモリ** — このメモリの構成要素は、2つの電極間に形成された薄膜の有機膜/金属/有機膜からなる3層構造である。有機材料の一例は、2-amino-4, 5-imidazoledicarbonitrileである<sup>28, 29, 30, 31, 32</sup>。ポリマーメモリでは、このような3層構造の電気的双安定性を利用している。この構造は、同じ印加電圧の下で、2つの異なる導電率をもつ状態を示す。書き込み動作は、電圧パルスをこの構造に印加し、低抵抗状態と高抵抗状態の間の可逆的なスイッチングを引き起こすことによって行われる。2 状態間での導電率の比として、およそ  $10^4$ という値が報告されている。状態遷移が起こったあとでは、電源を切っても、この 2 状態のうちのどちらかを取ったまま保持される。消去動作は、逆方向の電圧パルスを印加することによって行われる。スイッチング時間は、10 nsであることが報告されている。

このポリマーメモリと、絶縁体抵抗変化メモリや分子メモリのようなほかの電気的双安定抵抗メモリとの主な相違点は、ポリマーメモリには、その構造の中に、埋め込まれた金属層が存在するという点にある。実験結果によれば、この埋め込まれた金属層が、ポリマーメモリの双安定L-V特性に重大な役割を果たしている<sup>28</sup>。後に、この埋め込み金属層は、電気的に連続膜ではない、即ち孤立した金属ナノ微粒子であることが見出された。ポリマーメモリの動作原理は、まだ不明である。絶縁体抵抗変化メモリや分子メモリの場合のように、導電フィラメントの形成が関与しているとは思われない。抵抗変化が孤立した金属ナノ微粒子中の電荷のトラップに起因していることから、双安定性のメカニズムは、Simmons-Verderberの理論<sup>34</sup>によって説明できるとしている研究者もいる<sup>33</sup>。最近、単層のポリマーによるM-I-M構造でも同様な振る舞いを示すことが報告された<sup>35</sup>。

**分子メモリ** — 分子メモリとは意味の広い言葉であり、原子または分子のスペースに 1 ビットの情報を記憶するメモリセルとして個々の分子を利用するさまざまな提案の総称である。すでに実験的に実証されている方法としては、2 つの電極間に接続された分子のコンダクタンスがゲート電圧によって可逆的に急速に変化する現象に基づくものがある<sup>36, 37, 38, 39</sup>。この分子メモリでは、分子に 2 つの伝導状態が存在し、外部から電圧を印加して、その伝導状態を遷移させることによりデータを記憶する。データ読み出しは分子セルの抵抗変化を検出することにより行う。分子の特性と、DRAM<sup>40</sup>や浮遊ゲートメモリなどの現在のメモリ技術を組み合わせる考え方もある。分子の導電率がスイッチする機構は完全には理解されていない。分子間の電気伝導に関して過去に報告されている実験結果のいくつかは、2 つの金属電極間に形成された分子に沿ってできた金属フィラメントの形成によるものであることが分かっている<sup>41</sup>。分子エレクトロニクスの基礎的知識ベースの構築には、更なる研究が必要といえる。

## ロジックデバイス

### 序論

今日良く知られている CMOS デバイス・プロセスの微細化は、産業が 2019 年あたりで 16nm (物理ゲート長 6nm) に近づくに頃には、ますます困難になり、ついには終局に向かうであろう。このような CMOS の従来型スケーリングが終わった後は、シリコンプラットフォーム上に異なる電子デバイスを集積化することで機能的にスケーリングを継続することが可能になるかもしれない。このような電子デバイスとしては、1D 構造(CNT や化合物半導体ナノワイヤなど)、RTD、SET、分子やスピンドバイスなどがあり、いずれについてもこの章で議論を行う。おそらく、これらの選択肢は、新しい適切なナノアーキテクチャと結びつけなければ、その可能性を充分に開花することはできないであろう(ナノアーキテクチャの定義については、[アーキテクチャ](#)の節を参照のこと)。

しかし、これらのコンセプトは、まだ電荷ベースのロジックを表しており、そのスケーリングは基本的にバイナリー動作(binary operation)あたりの最小スイッチングエネルギーに伴う熱力学限界で制限される。この限界を超えるためには、電荷以外の何かに基づく新しい技術 - 情報処理技術のスケーリングを数世代延長し、性能を数桁向上させるような技術 - を、1 つあるいは複数、創案し開発するという大きな技術課題が存在する。このような代替技術としては、この節で議論する強磁性ロジック(ferromagnetic logic)やスピングain(spin gain)デバイスなどに加えて、まだ他にもこれから見つかるものもあるであろう。この点については、以降の [CMOS を越える技術](#)の節内の [新探素子技術 - 評価](#) の節で更に議論を行う。

確かに、CMOS デバイスを延長するための技術革新・発明の余地はまだ存在し、CMOS の極限的微細化は大規模な研究開発活動の焦点となっている。このような極限 CMOS デバイスは、新規で生産的な方法によって、代替の電子デバイスと融合されるかもしれない。しかし、このような高度な電子技術は、まだ発見されていない新しいスケーラブルなアプローチへの橋渡しとなる過渡的な技術として考えるべきである。

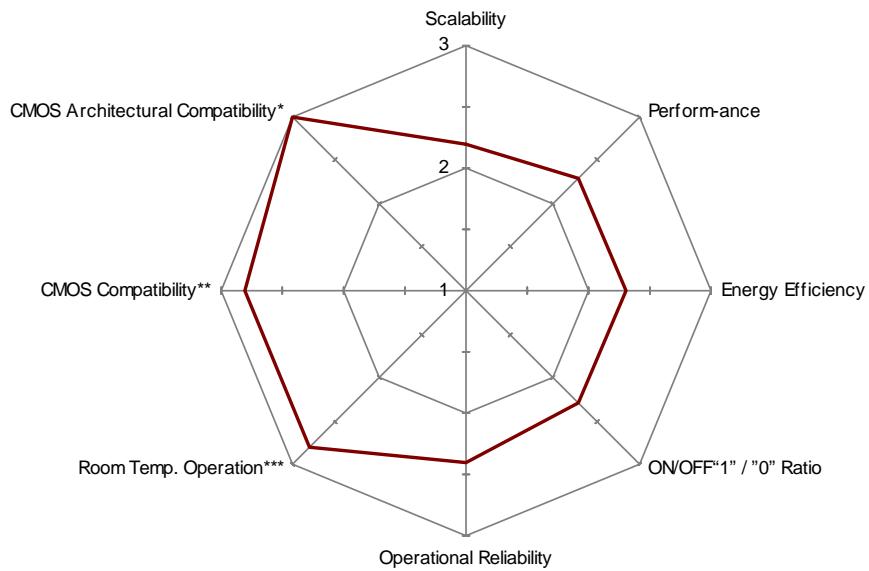

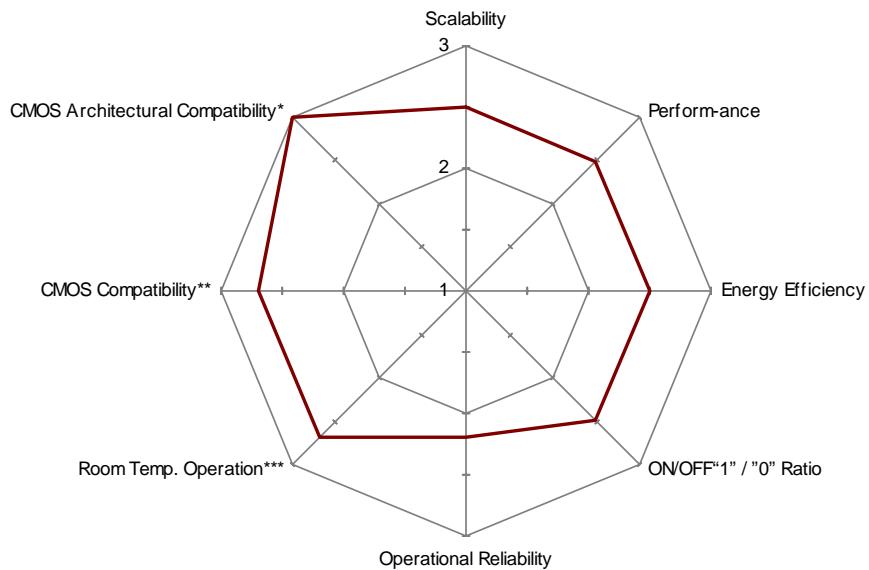

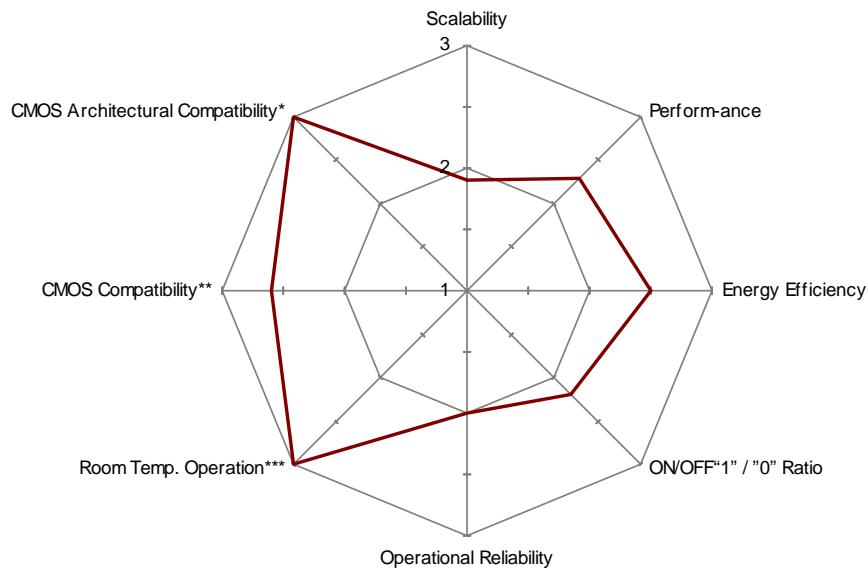

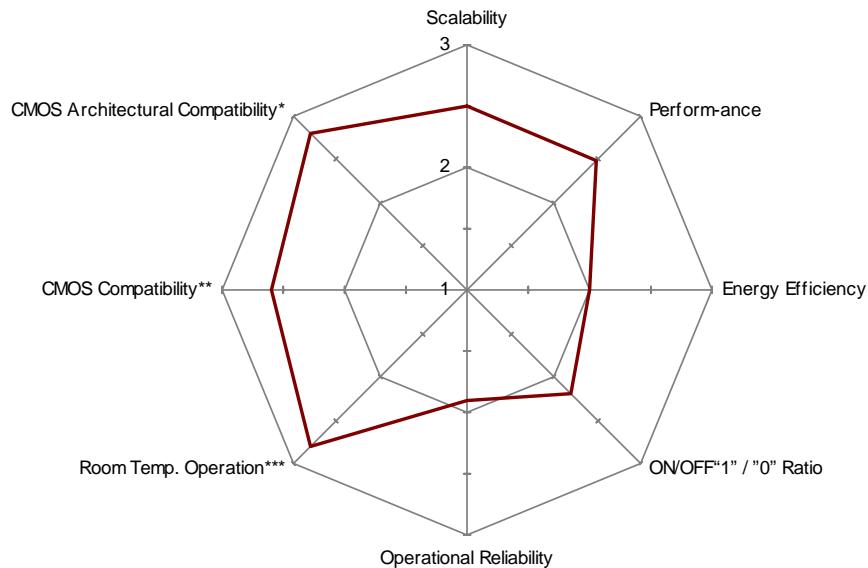

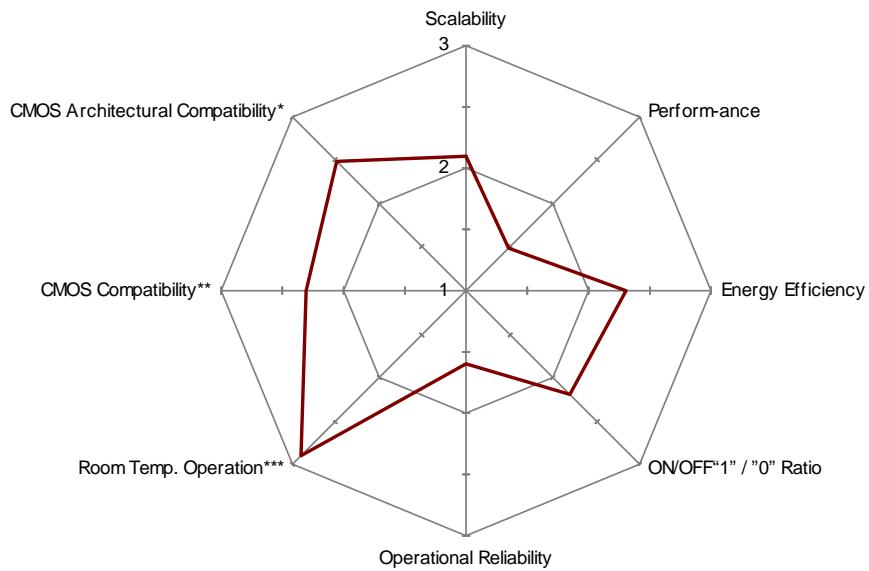

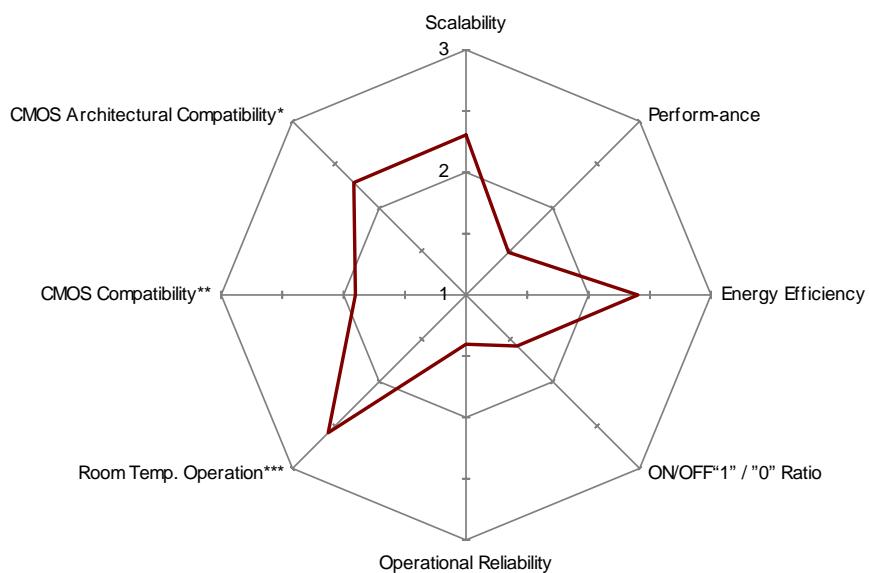

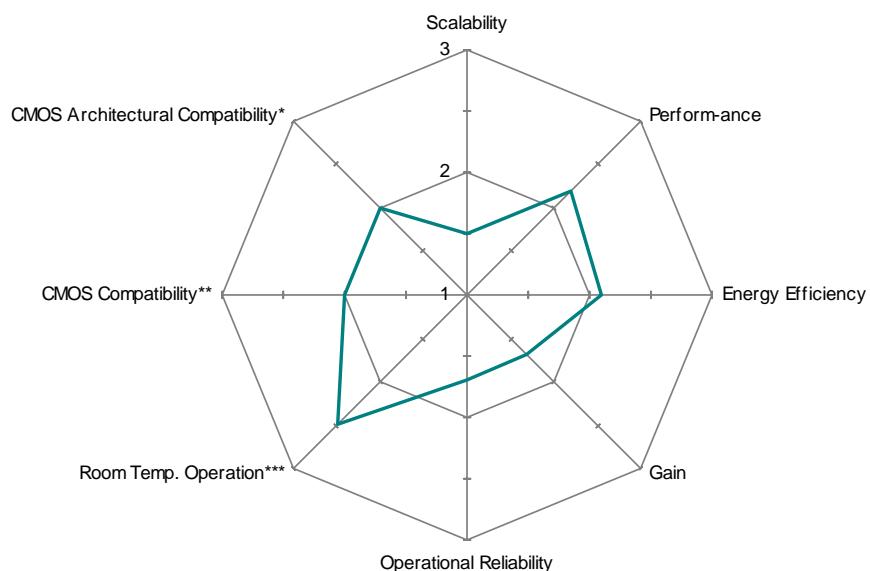

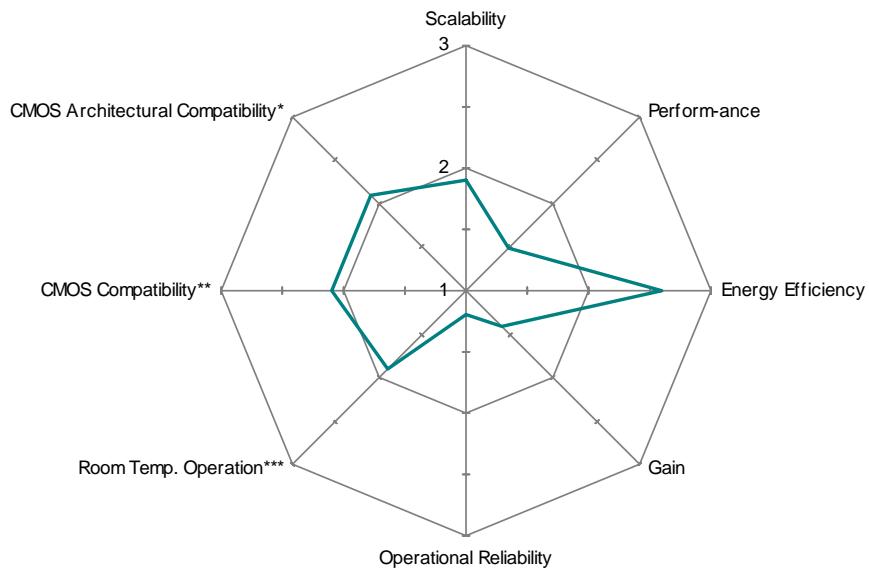

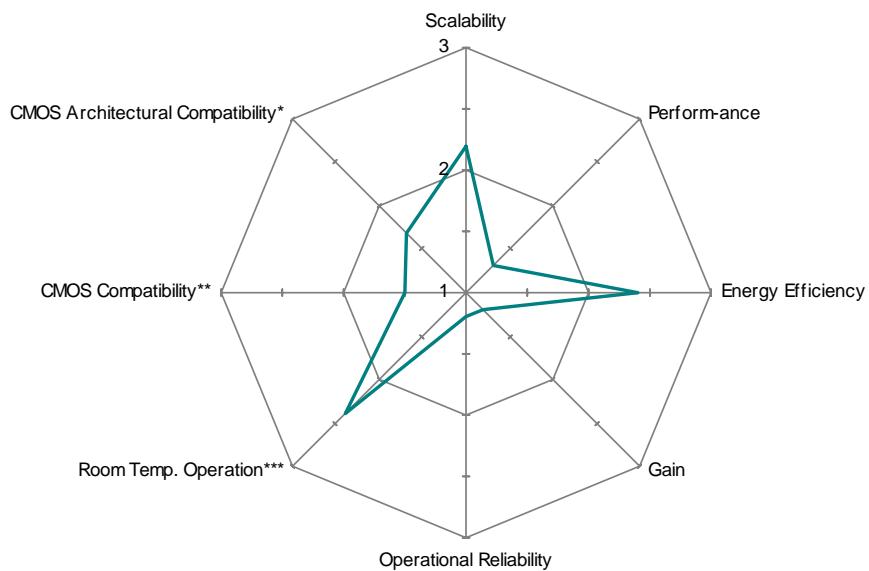

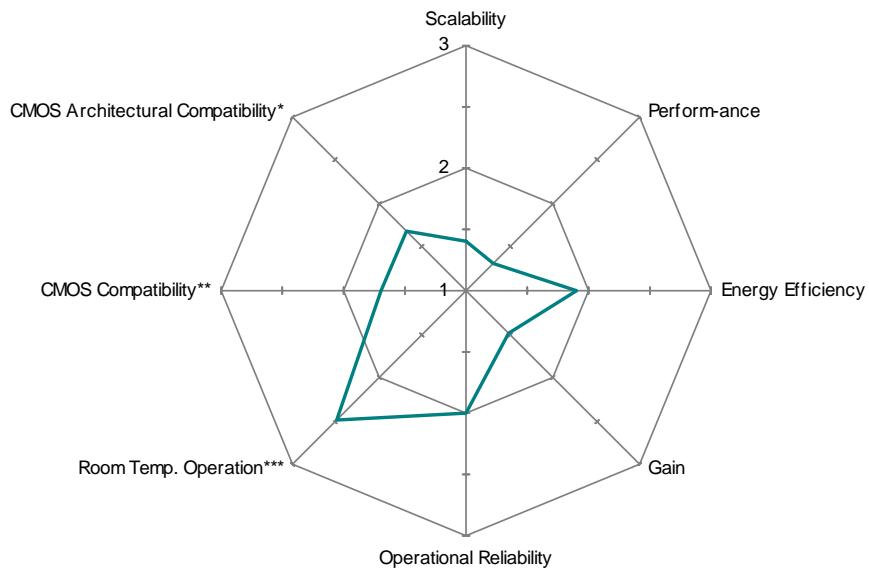

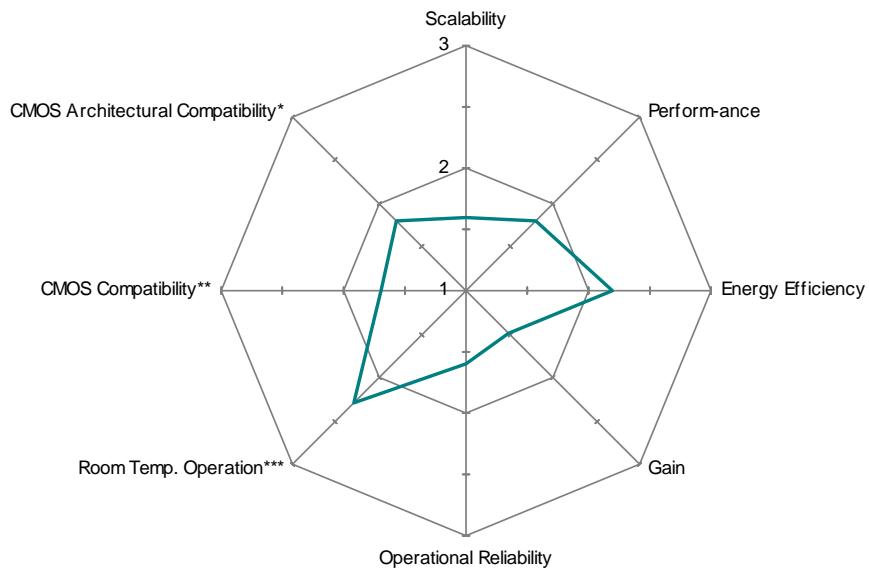

このような新技术は、新しいインフラストラクチャを造り上げるために必要な大がかりな投資を正当化するために、一定の動作条件を満たし、しかも説得力のある特性を備えていなければならない。まず第一に、新しい

情報処理技術は以下の要件を満たさなければならない。

1. CMOS の性能を数桁越えてマイクロエレクトロニクスを発展させ、しかも CMOS プラットフォームと円滑に連結できること。これを満たすには、さらに以下の要件が必要である

- CMOS より数桁以上機能的にスケーラブルなこと

- 高速な情報・信号処理速度とスループット

- 機能命令ごとに必要なエネルギーが CMOS より十分小さいこと

- 機能ごとのコストがスケーラブルで極めて小さいこと

## 2. 室温動作

3. 定常状態での動作を維持するためのエネルギー回復機能を持っていること(たとえば従来のデバイスでは、ゲインのメカニズムを持っていること)

直前の節“[基本的な指導原理](#)”において、情報処理に対する CMOS を越える新技術の開拓を考える際の一連の原則を提案した。

この版のロードマップにおける技術候補は、2003 年版と比べていくつかの点で異なっている。これらの変更は新探求ロジックデバイスに対する推移 Table(Table58)にまとめられている。変更点は、1)RSFQ がこの節から抜けた点、2)強磁性ロジックが候補として加えられた点、3)E:QCA がこの節から抜けた点、である。これらの変更に対する理由と意図するところは表に述べられている。

この節は Table59 の見出しの列に示した 6 つの技術候補を中心に構成されている。これらの候補は、系統的な文献調査によって、世界的に最も重要な研究活動領域を見つけだすことにより決定された。リストアップされたそれぞれの技術候補は、いくつかのデバイスのサブカテゴリを持つが、議論を簡単にするためにグループ化してある。表は、これらの技術に対して鍵となるパラメータを一覧にしている。各々のパラメータに対して、現在測定されている実験値と、理論的に予測されている値の 2 つの数字を記載している。

Table59 の最後の列には、各デバイス技術についての過去 2 年間に掲載された論文の数が示されている。これは、各研究コミュニティにおいて現在進行している研究活動の高さの目安、と捉えることができ、これらの表に、各候補デバイスを含めるかどうかを決める主な評価量ともなっている。これらの表には多くの脚注があり、その詳細は示された文献中に書かれている可能性がある。表に関連したテキストには、各デバイスの動作原理の簡単なまとめと共に、表には書ききれていない重要な課題が述べられている。

Table58 Transition Table for Emerging Logic Devices

|                     | IN/OUT | Reason for IN/OUT                                                                                              | Comment                                                                                                                                                  |

|---------------------|--------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ferromagnetic logic | IN     | Proposed ferromagnetic logic devices offer some new opportunities such as nonvolatility and re-configurability |                                                                                                                                                          |

| RSFQ                | OUT    | RSFQ is in production                                                                                          | Current assessment is that RSFQ will address several important specific applications that are beyond the scope of ITRS.                                  |

| E: QCA              | OUT    | E:QCA does not fit any of the application categories                                                           | Slow operation, low temperatures are needed, M:QCA are addressed in <i>ferromagnetic logic</i> , molecular QCA are addressed in <i>molecular logic</i> . |

Table 59 Emerging Research Logic Devices—Demonstrated Projected Parameters

| Device                                     |              |              |                                                                                            |                            |                                                          |                                                         |                               |                                  |

|--------------------------------------------|--------------|--------------|--------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------|---------------------------------------------------------|-------------------------------|----------------------------------|

|                                            |              | FET [B]      | 1D structures                                                                              | Resonant Tunneling Devices | SET                                                      | Molecular                                               | Ferromagnetic logic           | Spin transistor                  |

| Types                                      |              | Si CMOS      | CNT FET<br>NW FET<br>NW hetero-structures<br>Crossbar nanostructure                        | RTD-FET<br>RTT             | SET                                                      | Crossbar latch<br>Molecular transistor<br>Molecular QCA | Moving domain wall<br>M: QCA  | Spin transistor                  |

| Supported Architectures                    |              | Conventional | Conventional and Cross-bar                                                                 | Conventional and CNN       | CNN                                                      | Cross-bar and QCA                                       | CNN Reconfigure logic and QCA | Conventional                     |

| Cell Size (spatial pitch)                  | Projected    | 100 nm       | 100 nm [C]                                                                                 | 100 nm [C]                 | 40 nm [L]                                                | 10 nm [Q]                                               | 140 nm [U]                    | 100 nm [C]                       |

|                                            | Demonstrated | 590 nm       | ~1.5 μm [D]                                                                                | 3μm [H]                    | ~700 nm [M]                                              | ~2μm [R]                                                | 250 nm [V, W]                 | 100 μm [X]                       |

| Density (device/cm <sup>2</sup> )          | Projected    | 1E10         | 4.5E9                                                                                      | 4.5E9                      | 6E10                                                     | 1E12                                                    | 5E9                           | 4.5E9                            |

|                                            | Demonstrated | 2.8E8        | 4E7                                                                                        | 1E7                        | 2E8                                                      | 2E7                                                     | 1.6E9                         | 1E4                              |

| Switch Speed                               | Projected    | 12 THz       | 6.3 THz [E]                                                                                | 16 THz [I]                 | 10 THz [M]                                               | 1 THz [S]                                               | 1 GHz [U]                     | 40 GHz [Y]                       |

|                                            | Demonstrated | 1 THz        | 200 MHz [F]                                                                                | 700 GHz [J]                | 2 THz [N]                                                | 100 Hz [R]                                              | 30 Hz [V, W]                  | Not known                        |

| Circuit Speed                              | Projected    | 61 GHz       | 61 GHz [C]                                                                                 | 61 GHz [C]                 | 1 GHz [L]                                                | 1 GHz [Q]                                               | 10 MHz [U]                    | Not known                        |

|                                            | Demonstrated | 5.6 GHz      | 220 Hz [G]                                                                                 | 10 GHz [Z]                 | 1 MHz [F]                                                | 100 Hz [R]                                              | 30 Hz [V]                     | Not known                        |

| Switching Energy, J                        | Projected    | 3E-18        | 3E-18                                                                                      | >3E-18                     | 1×10 <sup>-18</sup> [L]<br>[>1.5×10 <sup>-17</sup> ] [O] | 5E-17 [T]                                               | ~1E-17 [V]                    | 3E-18                            |

|                                            | Demonstrated | 1E-16        | 1E-11 [G]                                                                                  | 1E-13 [K]                  | 8×10 <sup>-17</sup> [P]<br>[>1.3×10 <sup>-14</sup> ] [O] | 3E-7 [R]                                                | 6E-18 [W]                     | Not known                        |

| Binary Throughput, GBit/ns/cm <sup>2</sup> | Projected    | 238          | 238 [C]                                                                                    | 238 [C]                    | 10                                                       | 1000                                                    | 5E-2                          | Not known                        |

|                                            | Demonstrated | 1.6          | 1E-8                                                                                       | 0.1                        | 2E-4                                                     | 2E-9                                                    | 5E-8                          | Not known                        |

| Operational Temperature                    |              | RT           | RT                                                                                         | 4.2 – 300 K                | 20 K [L]                                                 | RT                                                      | RT                            | RT                               |

| Materials System                           |              | Si           | CNT,<br>Si, Ge, III-V,<br>In <sub>2</sub> O <sub>3</sub> , ZnO,<br>TiO <sub>2</sub> , SiC, | III-V<br>Si-Ge             | III-V<br>Si                                              | Organic molecules                                       | Ferromagnetic alloys          | Si, III-V, complex metals oxides |

| Research activity [A]                      |              |              | 171                                                                                        | 88                         | 65                                                       | 204                                                     | 25                            | 102                              |

Table 59 の注釈:

[A] 論文誌に掲載された論文数は2003年7月–2005年7月の期間に対して, the Science Citation Index databaseにおいて得られた数値。

[B] Si CMOS に対しては高性能 MPU のパラメータを使用: “予測値”(2020) と “実験値”(2005)。

[C] これらの構造の寸法と回路スピードに関するスケーリングは, MOSFET のスケーリングと同じである。

[D] Appenzeller, J., Y.-M. Lin, J. Knob, and P. Avouris. “Band-to-band tunneling in Carbon Nanotube Field-Effect Transistors,” Phys. Rev. Lett. 93.19 (2003) 196805.

[E] Burke, P. J. “AC performance of nanoelectronics: towards a ballistic THz nanotube transistor,” Solid-State Electron. 48 (2004) 1981–1986.

[F] Singh, D.V., K. A. Jenkins, and J. Appenzelle. “Direct measurements of frequency response of carbon nanotube field effect transistors,” Electronics Letters. 41.5 (2005) 280–282.

[G] Javey, A., Q. Wang, A. Ural, Y. M. Li, and H. J. Dai. “Carbon Nanotube Transistor Arrays for Multistage Complementary Logic and Ring Oscillators,” Nano Lett. 2.9 (2002) 929–932.

[H] Fay, P., L. Jiang, Y. Xu, G. H. Bernstein, D. H. Chow, J. N. Schulman, H. L. Dunlap, and H. J. De Los Santos. “Fabrication of Monolithically-integrated InAlAs/InGaAs/InP HEMTs and InAs/AlSb/GaSb Resonant Interband Tunneling Diodes,” IEEE Trans. Electron Dev. 48 (2001) 1282.

[I] Dragoman, D. “Terahertz oscillations in semiconducting carbon nanotube resonant-tunneling devices,” Physica E 24 (2004) 282–289.

[J] Brown, E. R. and C. D. Parker. “Resonant tunnel diodes as submillimetre-wave sources,” Phil. Trans. Roy. Soc. A 354 (1996) 2365.

[K] Auer, U., W. Prost, M. Agethen, F. J. Tegude, R. Duschl, and K. Eberl. “Low-voltage MOBILE logic module based on Si/SiGe interband tunneling devices,” IEEE Electron Dev. Lett. 22 (2001) 215.

[L] SET ロジック回路については、デバイス寸法／集積度、回路スピード、スイッチングエネルギーおよび動作温度は独立である。表中の値は、1 GHz で動作する複雑な回路について求められたものである: Chen, R. H., A. N. Korotkov, and K. K. Likharev. "Single-electron transistor logic," *Appl. Phys. Lett.* 68.14 (1996) 1954.

[M] Park, K-S., et al., "SOI single-electron transistor with low RC delay for logic cells and SET/FET Hybrid ICs," *IEEE Trans. Nanotechnology*. 4.2 (2005) 242.

[N] 参考文献 [M]において、SET に対して実験的に報告された“intrinsic な速度”は容量測定から求められたものであり、時間依存の特性測定からではない。

[O] [ ]の中の値は、冷却エネルギーを含む値である。もし理想的なカルノー冷却器が動作温度 $T_c$ までの冷却に使われた場合、全体のスイッチングエネルギーは  $E_{sw} > E_c \cdot \frac{300}{T_c}$  となる。ここで、 $E_c$  は冷却エネルギーを考慮しない場合のスイッチングエネルギー全体である。

[P] Tsukagoshi, K., B. W. Alphenaar, and K. Nakazato. "Operation of Logic Function in a Coulomb Blockade Device," *Appl. Phys. Lett.* 73 (1998) 2515.

[Q] DeHon, A. and M. J. Wilson. "Nanowire-Based Sublithographic Programmable Logic Arrays, Proc. Intern. Sym. on Field-Program. Gate Arrays (FPGA2004, Feb. 22–24, 2004).

[R] Kuekes, P. J., D. R. Stewart, and R. S. Williams, "The crossbar latch: Logic value storage, restoration and inversion in crossbar circuits," *Journal of Applied Physics*. 93 (2005) 034301.

[S] Seminario J. M., P. A. Derosa, L. E. Cordov et al. "A molecular device operating at terahertz frequencies: Theoretical simulations," *IEEE Transactions On Nanotechnology*. 3.1 (2004) 215–218.

[T] DeHon, A. "Array-Based Architecture for FET-Based Nanoscale Electronics," *IEEE Trans. Nanotechnol.* 2.1 (2003) 23.

[U] Parish, M. C. B. and M. Forshaw. "Physical constraints on magnetic quantum cellular automata," *Appl. Phys. Lett.* 83.10 (2003) 2046–2047

[V] Cowburn and M. E. Welland. "Room Temperature Magnetic Quantum Cellular Automata," *Science*. 287.5457 (2000) 1466.

[W] Allwood, D. A., et al. "Submicrometer Ferromagnetic NOT Gate and Shift Register," *Science*. 296 (2002) 2003.

[X] Hirose, T., Y. Fujiwara, M. Jimbo, T. Kobayashi, and S. Shiomi. "Magneto-current of magnetic tunnel transistors employing various Schottky junctions," *J. Magnetism and Magnet. Materials*. 286 (2005) 124–127.

[Y] Nikonorov, D.E. and Bourianoff G.I., "Spin gain transistor in ferromagnetic semiconductors - The semiconductor Bloch-equations approach," *IEEE Transactions On Nanotechnology*. 4.2 (2005) 206–214.

[Z] Tanaka T., Y. Ohno, S. Kishimoto, et al. "Experimental demonstration of capacitor-coupled resonant tunneling logic gates for ultra-short gate-delay operation," *Japanese Journal of Applied Physics*. Pt 1. 42.11 (2003) 6766–6771.

## ロジックデバイス - 表掲載技術の定義と議論 -

**1D構造(カーボンナノチューブとナノワイヤ)** — 2003年版ITRS EDSチャプタは全ての技術候補を調査し、大量生産に採用されるための困難はまだ非常に大きいものの、1D構造が、他のどの候補よりも、微細化の進むナノエレクトロニクスに対して大きなインパクトを与えることを見出した。その後、この分野における研究活動は、1D構造の持つ重要な問題点を見極める段階にまで進展した。研究活動は4つの主要な目的に集中された：1)コヒーレント輸送(coherent transport)を含む量子閉じ込め状態(quantum-confined)での輸送における基礎的な物理メカニズムの解明、2)予測・制御可能な特性を持つナノチューブとナノワイヤの作製、3)位置制御、電極コンタクト、ドーピング、絶縁膜とゲート材料の集積化など、デバイス作製に関わる問題解決、そして最後に、4)輸送効率(transport efficiency)、サブスレッショルド係数(subthreshold slope)、アンビポーラ伝導(ambipolar conduction)、RF応答、 $I_{ON}/I_{OFF}$ 比、その他のデバイス課題の評価、である。MOSFETに1D構造を適用する際の重要な課題の一つは、複数の負荷ゲート(multiple load gates)の容量をドライブするのに充分なドレン電流を得るために、一つのデバイス内にそのような構造を何本か平行に配置する必要があることである。この節は、これまでに理解されていることを手短にまとめ、4つのエリアそれぞれにおける最近の研究を指示し、応用上の障害となっている残りの問題を議論することを目的としている。また、本章の新探求材料の節では、1D構造に関する材料面での問題についても議論をする。

量子閉じ込め状態での電子輸送の物理に関する最近の研究は2つの領域に注力されている。1点目は、現実的な温度と電圧条件において、量子閉じ込め効果が電子の移動度に与える影響を理解することであり、2点目は、高効率のコヒーレント干渉(coherent interference)ロジックデバイスの可能性を評価することである。状態密度(density of states)の減少に伴って移動度が向上するという初期の期待<sup>42</sup>に対して、より最近の計算は逆の結論を報告している<sup>43</sup>。現実的な界面を考慮して、更に注意深く行われた室温でのマルチバンド計算では、電子とフォノンの波動関数の重なりが増大するために移動度は低下することが示唆されている。決定的な実験はまだ行われていない。1Dデバイスにおけるコヒーレント電子輸送は、原理的には、テラヘルツ(THz)の領域で動作可能である<sup>44</sup>。しかし、そのようなデバイスは、極端なリソグラフィの精度が必要であること、動作温度が低温であること、更に、電子がフェルミオンの性質(Fermionic nature)を持つため量子閉じ込め構造(quantum confined structures)においてトータルの電流が制限されること、などの理由から、かなり非現実的であると思われる<sup>45</sup>。

特性を制御したナノチューブの作製に関しては、プラズマ化学気相堆積(plasma enhanced chemical vapor deposition; PECVD)法の利用によって大きな進歩が遂げられた。現在では、90%以上が半導体的性質を持つようなナノチューブを信頼性良く作製することが可能となっている。これは、大量生産の環境における純度の要求からは、まだ程遠い段階ではあるが、大きな前進を表している。繰り返しになるが、この点については、本章の材料の節で更に議論を行う。

CNT FETの作製上の課題の一つは、リソグラフィによって決められた位置に、ナノチューブを確実に配置したり、成長させることである。最近の報告では、触媒を使った成長によって2 nmの正確さで配置できることが実証されている<sup>46</sup>。この手法では、最先端の電子線リソグラフィと、粒径の揃った触媒粒子を斜め蒸着する技術を組み合わせることで、高い正確度を達成した。その後、触媒粒子の位置にCNTを成長させることで90%を越える被覆率を実現している。CNT FETの作製上のもう一つの課題は、信頼性の高い、その場(*in situ*)ドーピング(特にP型ドーピング)である。2重ゲートを配置して、化学的なドーピングと静電的なドーピングを組み合わせる新しい手法では、静電的な制御によりP-FETとN-FETのどちらでも動作させることが可能になる<sup>47</sup>。高誘電体ゲート絶縁膜とゲート材料に関する進展に関しては、本章の最後にある参考文献(Endnotes)で挙げたもの<sup>48</sup>を含め、いくつかの文献を参照されたい。CNTの品質は、測定された音響フォノンによる平均自由行程(acoustic phonon mean free path)が約300 nm、光学フォノンによる平均自由行程(optical phonon mean free path)が15 nm<sup>49</sup>、という点にまで向上されている。

CNT FETのオン電流は1 μA領域と小さいため、50 負荷を用いて従来の技術でそのAC応答を直接測定することは困難であった。最近では、広帯域の測定技術により200 MHzまでの直接測定が可能になったことが

報告されている<sup>50</sup>。ショットキー障壁CNT FETにおけるアンビポーラ伝導は、 $I_{ON}$ 対 $I_{OFF}$ 比を容認できないほど低い値に制限してしまうため、通常の方法で用いる上で大きな障害となっている。

**共鳴トンネル素子 (Resonant tunnel devices)<sup>51, 52</sup>** — ロジック応用のための共鳴トンネル素子には、共鳴トンネルトランジスタ(RTT)や共鳴トンネルダイオードを一つあるいはそれ以上のFETと組み合わせた混成デバイス(RTD-FET)がある。RTDは、本質的に極めて速いスイッチング速度をもち、そのI-V特性に負性微分抵抗領域をもつ2端子デバイスである。この2つの特性のために、RTDは、高速のスイッチングが可能な素子として魅力的とのものである。2つのRTDが直列に接続された場合には、2つの安定動作点が存在し、ゲートとして働く第3電極が形成されれば、この2つの安定動作点の間を高速でスイッチすることが可能である。しかしながら、RTDを流れるピーク電流は、トンネル障壁膜厚に指数関数的に依存するので、ゲート電極によってピーク電流値を制御できるようにしないと、再現性のあるデバイス動作を得ることは、本質的に難しい。ピーク電流の制御は、通常共通基板上にトランジスタと直列に接続された2重RTDを集積することによって行われる<sup>53</sup>。この方法では、極めて良い膜厚制御性を得るために、エピタキシャル成長を用いた複雑な構造が必要となる。

トランジスタを一对のRTDと集積化した場合、本質的に高速な双安定スイッチングのための時間に加えて、トランジスタのゲート・スタックにおける容量の充放電に関わる遅延時間が必要になる。このため、集積化された素子の動作速度は、RTDそれ自身の真性のスイッチング時間に対して、数桁遅くなる可能性がある。他の技術課題としては、CMOSのデジタル回路設計者が求める10<sup>5</sup>台の $I_{ON}/I_{OFF}$ 比と比べ、このデバイスの $I_{ON}/I_{OFF}$ 比は10程度であること、また集積化された構造が本質的に複雑であること、がある。後者は、デバイスサイズのスケーリングに対する限界となる。混成デバイスの複雑さのために、そのサイズは大きくなり、実験的には、3μmのオーダーの空間ピッチのものが報告されている。別の課題は、高いピーク・パレイ比をもつSiあるいはSiGeトンネルダイオードを実現することである。

RTDに制御電極を付加することによって、様々な応用に対する有用性が広がる。この考え方には、共鳴トンネルトランジスタ(RTT)<sup>54</sup>を実現する際に使われた。RTTは負性相互コンダクタンスをもち、種々の論理回路に使うことが出来る。例えば、一つのトランジスタでXORゲートを実現することができる<sup>55</sup>。

伝統的にRTDはIII-V材料系を用いて作製されてきたが、このことがRTDの適用範囲を制限していた。最近、いくつかの論文において、Siと適合する材料でIV族デバイスを作製したことが報告されている。これらの中には、SiGeを用いた3値ロジックデバイス<sup>56</sup>や、Siベースの電界誘起型バンド間トンネリングトランジスタ(band-to-band tunneling transistor)<sup>57</sup>などがある。これらのデバイスは、いずれも先に述べた課題を依然として有しているが、Siと適合性の良い材料構造で作製されたということで、集積化に関する課題を大幅に軽減している。