## ITRS の歴史

n kermal lona

### ITRS10年周年記念!

http://www.itrs.net

1991 Micro Tech 2000 Workshop Report

**Europe**

Japan

Korea

**Taiwan**

**USA**

**1998ITRS Update**

**1999ITRS**

**2000ITRS Update**

**2001ITRS**

**2002ITRS Update**

**2003ITRS**

**2004ITRS Update**

**2005ITRS**

**2006ITRS Update**

**2007ITRS**

ITRS Press Conference 2007 Makuhari, Japan

## ITRS 2007年版の概要

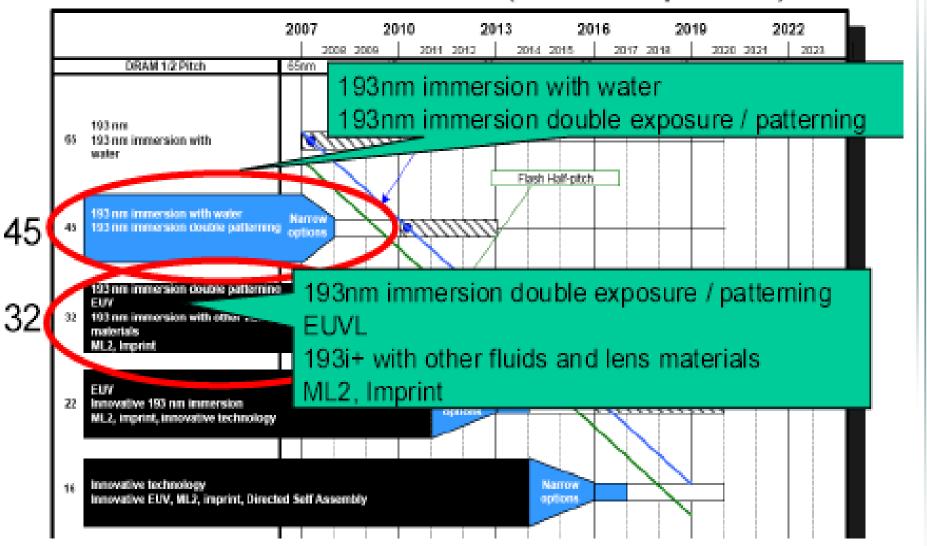

## リソグラフィ

m kermal loma

### Potential Solutions (2007 Update)

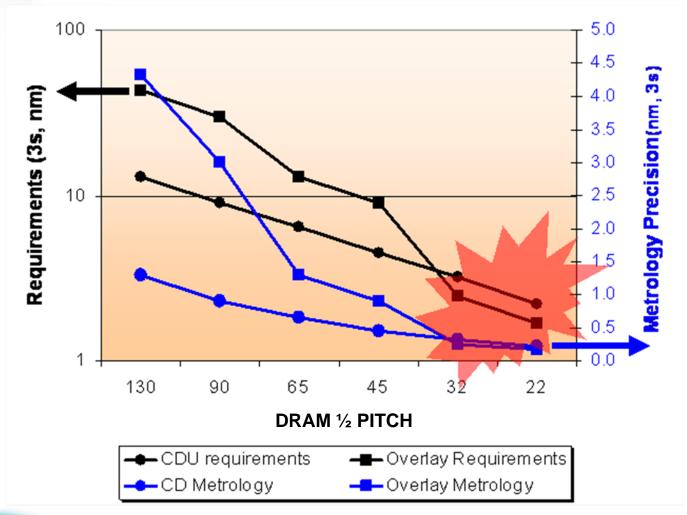

### リソ計測のニーズ

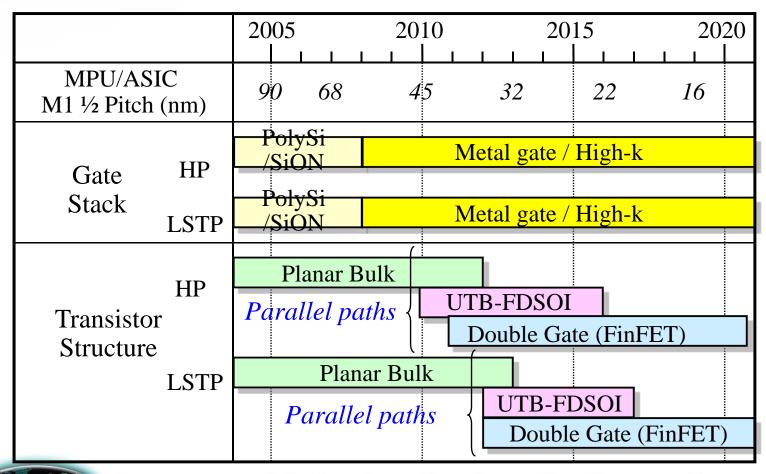

### 最新製品技術動向

- DRAM: 2007 version compared to 2005 version

- ハーフピッチ: 2007と同じ

- DRAM 製品: 1年後ろ倒し

- セル寸法係数: 6F^2は 2006開始 (2年前倒し)

- キャパシター技術: 2010年まで変わらない

- キャパシター 構造: 2012年までシリンダー(スタック型)とペデスタル(トレンチ型)

#### NVM

сетно ощ

- NAND フラッシュ・ハーフピッチ: ITRS2005と比較して2年前倒しが予想される

- 4bit/セル技術: ITRS2005で予測されたが、3bit/セル技術が2bit/セルと4bit/セルの中間技術として登場するだろう

- NANDフラッシュ・セル構造:セル構造は浮遊ゲート技術から、電荷トラップを利用する技術に 2010年には移行するでしょう。2013以降は3次元構造が必要になるでしょう。

- 表は電荷による素子(フラッシュ)と電荷によらない素子(相変化メモリー、MRAM、 FeRAM)で分かれて記述されている

### 次の数年に必要となる技術革新

fi=1/[CV/I]で表されるスケーリングを維持するためには、 新材料と新素子構造による革新必要である

### 3次元配線

● 配線計測

n kennalional

- 3次元配線計測は2007年版に加えられた

- アセンブリーとパッケージ

- SiP, 3次元実装, TSV等に対する共同設計ツール

- 発熱密度が増加している(特に3次元実装)

- 進歩はロードマップの予測をはるかに超えている

- 3次元実装: 3次元実装の技術は豊富にある

#### 環境問題

#### 効率的な資源の利用

- 2007年は資源管理に注力する

- 薬品

- 利用エネルギー削減

- 利用ウェーハの削減

### 工場自動化 2007 Updates

- ■異なるビジネスモデルに対応するため小ロット(12 wafer)の指標を追加

- ■プロセス制御と高速・大容量のデータの必要性を述べた

- ■装置省エネモードとグリーン工場の必要性を述べた

THE CHILD THE PARTY OF THE PART

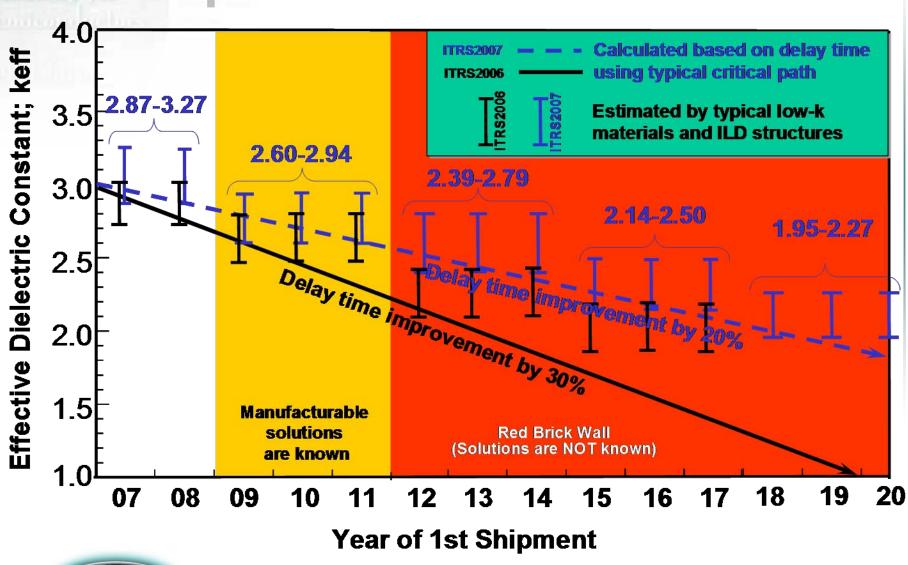

### 配線 2007 改訂

- Low-κ 減速

- 製造にとって現実的な材料でモデルを作った

- ・ 新技術の導入

- Cu配線のALDバリヤープロセスと金属キャップは導入が 遅れている

- 消費電力指標

- 単位長さ当たりの容量は誘電定数の減少に伴い減少

- しかし、配線層の増加とチップの大型化のために、消費 電力は増加が予想される

### Low-k update

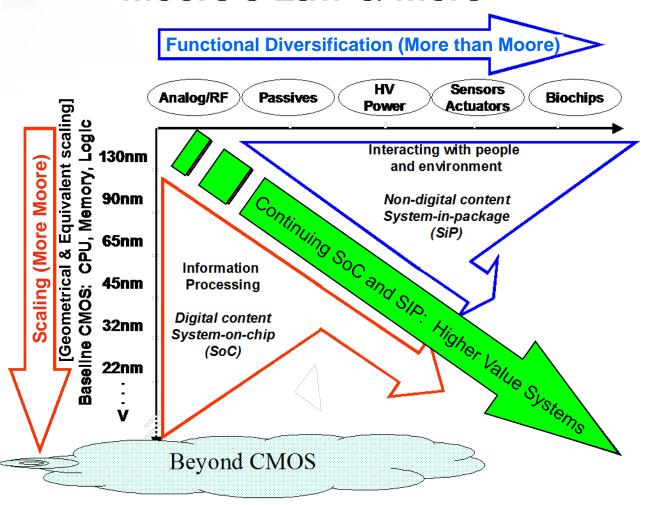

"More Moore" & "More than Moore"

#### 2007 ITRS Executive Summary

#### Moore's Law & More

# 2007 ITRS 定義提案: "More Moore(更にムーア)" and "More than Moore(ムーアを超えて)"

#### 1. スケーリングによる ("More Moore更にムーア")

n terminations

- a. (場を一定にした)継続的な幾何学的スケーリングとはチップ上のロジック及び記憶容量の横方向、縦方向の物理的寸法を縮め、素子密度を上げ(機能当たりのコストを下げ)て、性能(速さ、消費電力)と信頼性を向上させて、応用製品と最終顧客に価値を届けることである。

- b. 等価的スケーリングとは、継続的な幾何学的スケーリングと共に生まれ、またこれを可能にしてきたものだが、3次元デバイス構造("設計係数")による改善と、他の、チップの電気的性能に影響を及ぼす幾何学によらないプロセス技術や新材料を使うことである

#### 2. 機能の多様化 ("More than Mooreムーアを超えて")

機能の多様化とは必ずしもムーアの法則に従ってスケーリングしない機能をデバイスに取り入れ、最終顧客に様々な面で付加価値を与えることである。"More-than-Moore ムーアの法則を超えた"アプローチでデジタルではない機能(即ち、RF通信、電力制御、受動素子、センサー、アクチュエータ)がシステムのボード上から、特別のパッケージ (SiP)へ、そしてチップ(SoC)へ搭載されることである