# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS

2009年版

メトロロジ

THE ITRS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

# 訳者まえがき

この文書は International Technology Roadmap for Semiconductors 2009 Edition(国際半導体技術ロードマップ 2009 年版) 本文の全訳である。

国際半導体技術ロードマップ(以下 ITRSと表記)は、米国、日本、欧州、韓国、台湾の世界5極の専門家によって編集・作成されている。日本では、半導体技術ロードマップ専門委員会(STRJ)が電子情報技術産業協会(JEITA)内に組織され、日本国内で半導体技術ロードマップについての調査活動を行うとともに、ITRSの編集・作成に貢献している。STRJ内には14のワーキンググループ(WG: Working Group)が組織され、半導体集積回路メーカ、半導体製造装置メーカ、材料メーカ、大学、独立行政法人、コンソーシアなどから専門家が集まり、それぞれの専門分野の調査活動を行っている。

ITRS は改版を重ねるごとにページ数が増え、2009年版は英文で約1000ページの文書となった。このような大部の文書を原文で読み通すことは専門家でも多大な労力を要するし、専門家であっても技術分野が少し異なるとITRSを理解することは必ずしも容易でない。STRJの専門委員がその専門分野に応じてITRSを訳出することで、ITRSをより親しみやすいものにすることができるのではないかと考えている。

なお、ITRS 2005年版(英語の原書)までは、ウェブ公開とともに、印刷された本としても出版していたが、ITRS 2007年版以降、は印刷コストが大きくなってきたこと、ウェブ上で無料公開されている文書の出版版を本の形で有償頒布しても需要が限られることなどのため、印刷物の形での出版を断念し、ウェブ公開のみとなった。ITRS の読者の皆様にはご不便をおかけするが、ご理解願いたい。ITRS 2009年版の作成にあたっては、当初から電子媒体でITRS を公開することを前提に編集を進めた。ITRS の表は原則として、Microsoft Excel のファイルとして作成し、そのまま公開することにした。

ITRS は英語で書かれている。日本語訳の作成は、STRJ 委員が分担してこれにあたり、JEITAの STRJ 担当事務局が全体の取りまとめを行った。訳語については、できる限り統一するように努めたが、なお、統一が取れていないところもある。また、訳者によって、文体が異なるところもある。ITRS の原文自体も多くの専門家による分担執筆であり、そもそも原文の文体も一定していないことも、ご理解いただきたい。誤訳、誤字、脱字などが無いよう、細心の注意をしているが、短期間のうちに訳文を作成しているため、なお間違いが含まれていると思う。また、翻訳の過程で原文のニュアンスが変化してしまうこともある。訳文についてお気づきの点や、ITRS についてのご批判、ご意見などを事務局まで連絡いただけれますよう、お願い申し上げます。

今回の訳出にあたっては、ITRSの本文の部分のみとし、ITRS内の図や表の内部の英文は訳さないでそのまま掲載することとした。Executive Summaryの冒頭の謝辞(Acknowledgments)に、ITRSの編集にかかわった方々の氏名が書かれているが、ここも訳出せず、原文のままの表記とした。原文中の略語については、できるかぎり、初出の際に、「ITRS(International Technology Roadmap for Semiconductors)」のように()内に原義を示すようにした。英文の略号をそのまま使わないで技術用語を訳出する際、原語を引用したほうが適切と考えられる場合には、「国際半導体技術ロードマップ (ITRS: International Technology Roadmap for Semiconductors、以下 ITRSと表記)」「国際半導体技術ロードマップ (International Technology Roadmap for Semiconductors)」のように和訳の後に()内に原語やそれに対応する略語を表示した。Executive Summaryの用語集(Glossary)も参照されたい。原文の括弧()があってそれを訳するために括弧を使った場合もあるが、前後の文脈の関係で判別できると思う。また訳注は「【訳者注:この部分は訳者の注釈であることを示す】」のように【】内に表記した。また□内の部分は、訳者が原文にない言葉をおぎなった部分であることを示す】」のように【】内に表記した。また□内の部分は、訳者が原文にない言葉をおぎなった部分であることを示している。訳文は厳密な逐語訳ではなく、日本語として読んで意味が通りやすいように意訳している。ITRSのウェブ版ではいイパーリンクが埋め込まれているが、今回の日本語版ではハイパーリンクは原則として削除した。読者の皆様には不便をおかけするが、ご理解いただけば幸いである。

今回の日本語訳全体の編集は全体のページ数が膨大であるため、大変な作業となってしまいました。編集作業を担当いただいた、JEITA内 STRJ 事務局の古川昇さん、関口美奈さんに大変お世話になりました。厚くお礼申し上げます。

より多くの方に ITRS をご活用いただきたいとの思いから、今回の翻訳作業を進めました。 今後とも ITRS と STRJ へのご理解とご支援をよろしくお願い申し上げます。

2010年5月

訳者一同を代表して

電子情報技術産業協会(JEITA)半導体部会 半導体技術ロードマップ専門委員会(STRJ) 委員長 石内 秀美 (株式会社 東芝)

# 版権について

# ORIGINAL (ENGLISH VERSION) COPYRIGHT © 2009 SEMICONDUCTOR INDUSTRY ASSOCIATION

All rights reserved

ITRS • 2706 Montopolis Drive • Austin, Texas 78741 • 512.356.7687 • http://public.itrs.net

Japanese translation by the JEITA, Japan Electronics and Information Technology Industries Association under the license of

the Semiconductor Industry Association

#### -引用する場合の注意-

原文(英語版)から引用する場合: ITRS 2009 Edition page XX, Figure (Table) YY この日本語訳から引用する場合: ITRS 2009 Edition (JEITA 訳) XX 頁,図(表) YY と明記してください。

問合せ先:

社団法人 電子情報技術産業協会 半導体技術ロードマップ専門委員会 事務局 Tel: 03-5218-1068 mailto: roadmap@jeita.or.jp

### TABLE OF CONTENTS

| 汁測( <b>Metrology</b> )                        |    |

|-----------------------------------------------|----|

| 概要                                            |    |

| 産業基盤の必要性(Infrastructure needs)                |    |

| 計測で考慮すべきこと(Critical Metrology Considerations) |    |

| 精密さと不確かさ(Precision and Uncertainty)           |    |

| サンプリングの要件(Sampling Requirement)               |    |

| 困難な技術課題                                       | 6  |

| 顕微鏡観察(Microscopy)                             | 7  |

| リソグラフィにおける計測(Lithography Metrology)           | (  |

| ラインラフネス(Line Roughness)                       | 12 |

| 計測の不確かさ(Measurement Uncertainty)              | 13 |

| Table MET3、MET4 における不確かさの説明                   | 15 |

| FEPにおける計測(Front End Processes Metrology)      | 24 |

| 配線における計測 (Interconnect Metrology)             | 33 |

| Cu-Low-x膜のメッキ配線問題と計測技術への要求                    | 34 |

| <b>Cu</b> メッキ配線の問題                            |    |

| <b>Cu</b> メッキ配線の計測                            | 3£ |

| 低誘電率(Low-ĸ)膜の課題と計測要求                          | 37 |

| 低誘電率(Lowx)膜の課題                                | 37 |

| 低誘電率(Lowx)膜の計測                                | 38 |

| 材料と汚染の評価·解析                                   | 30 |

| <b>標準計測システム</b>                               | 4  |

| 標準試料標準物質                                      | 4  |

| 統合計測と先端プロセス制御( <b>APC</b> )                   | 46 |

| 新探求材料とデバイスの為の計測                               | 49 |

| 3 次元原子イメージングと分光法                              | 50 |

| 走査プローブ顕微鏡を含む他の顕微鏡の必要性                         | 5  |

| ナノ物質の光学特性                                     | 52 |

| 新材料とデバイスの為の電気的特性評価                            | 53 |

| 参照文献                                          | 54 |

#### LIST OF FIGURES

| Figure MET1    | Relations of Time, Tool and Sample Dependent                                  |    |

|----------------|-------------------------------------------------------------------------------|----|

|                | Components of Uncertainty and Bias                                            | 5  |

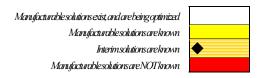

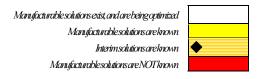

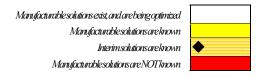

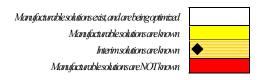

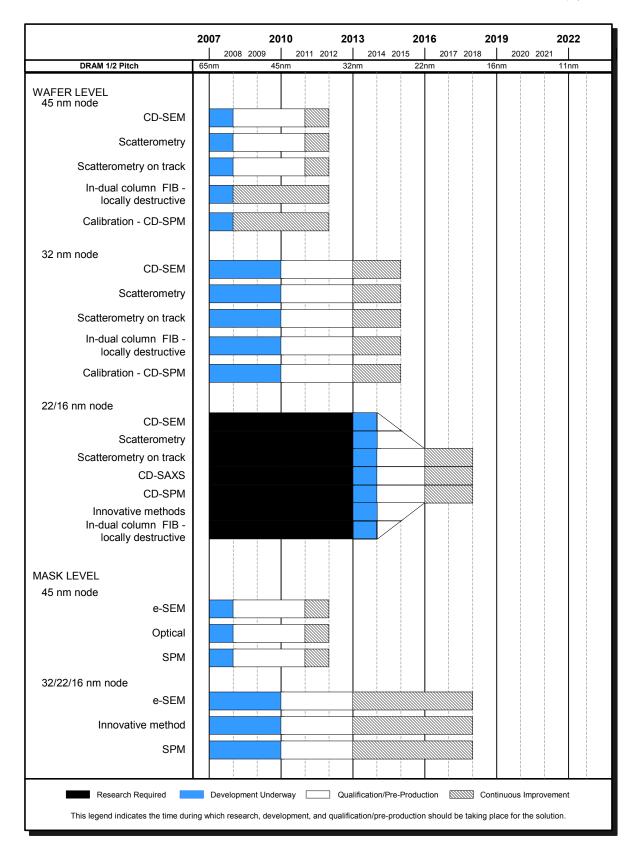

| Figure MET2a   | Lithography Metrology Potential Solutions: CD                                 | 23 |

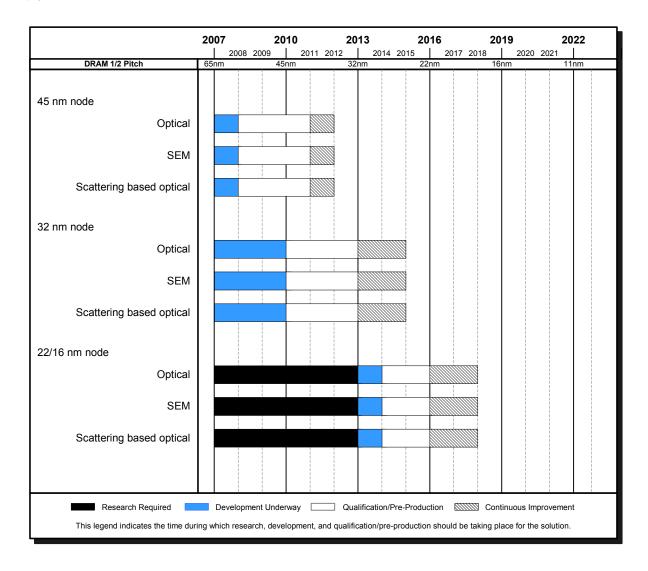

| Figure MET2b   | Lithography Metrology Potential Solutions: Overlay                            | 24 |

| Figure MET3    | Review of Stress/Strain Measurement Methods                                   | 31 |

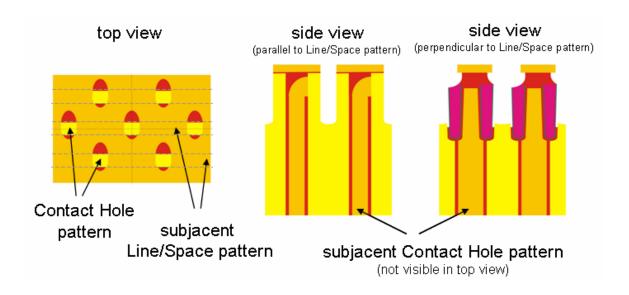

| Figure MET4    | 3D Metrology Requirements                                                     | 32 |

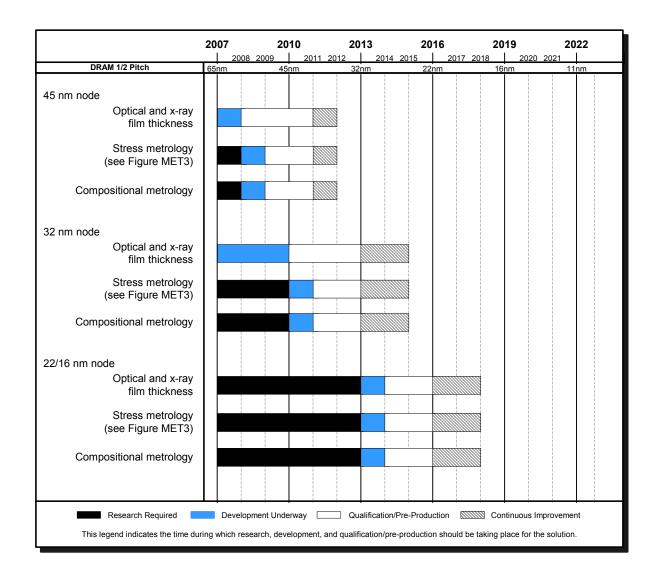

| Figure MET5    | FEP Metrology Potential Solutions                                             | 33 |

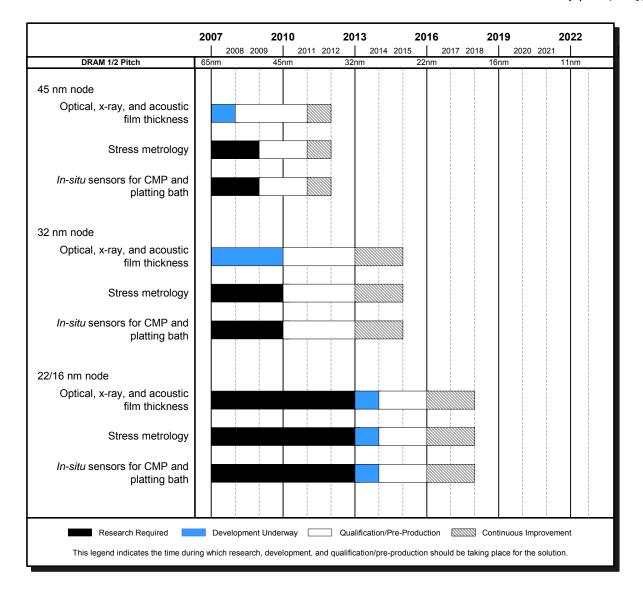

| Figure MET6    | Interconnect Metrology Potential Solutions                                    | 39 |

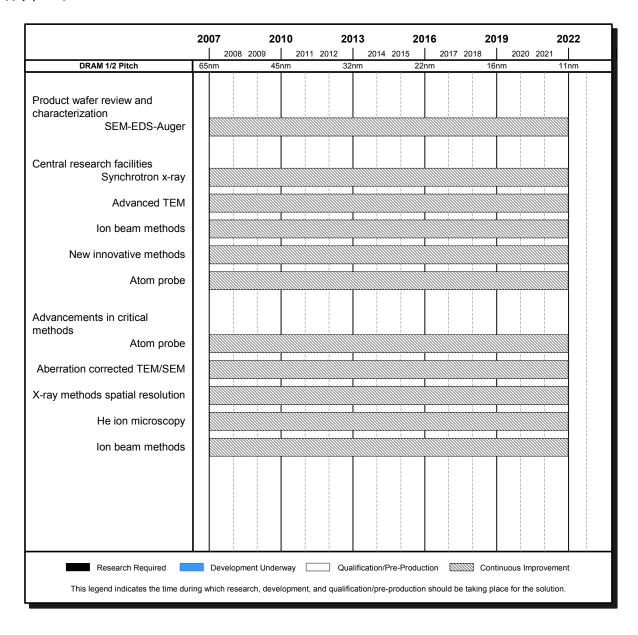

| Figure MET7    | Materials and Contamination Potential Solutions                               | 44 |

|                |                                                                               |    |

| LIST OF TABLES |                                                                               |    |

| Table MET1     | Metrology Difficult Challenges                                                | 6  |

| Table MET2     | Metrology Technology Requirements                                             | 7  |

| Table MET3a    | Lithography Metrology (Wafer) Technology Requirements—Near-term Years         | 17 |

| Table MET3b    | Patterning Metrology (Wafer) Technology Requirements—Long-term Years          | 18 |

| Table MET4a    | Lithography Metrology (Mask) Technology Requirements: Optical—Near-term Years | 19 |

| Table MET4b    | Patterning Metrology (Mask) Technology Requirements: Optical—Long-term Years  | 19 |

| Table MET4c    | Lithography Metrology (Mask) Technology Requirements: EUV—Near-term Years     | 21 |

| Table MET4d    | Patterning Metrology (Mask) Technology Requirements: EUV—Long-term Years      | 22 |

| Table MET5a    | Front End Processes Metrology Technology Requirements—Near-term Years         | 26 |

| Table MET5b    | Front End Processes Metrology Technology Requirements—Long-term Years         | 27 |

| Table MET6     | Interconnect Metrology Technology Requirements                                | 37 |

## 計測(METROLOGY)

計測は測定の科学と定義される。ITRSでは、計測ロードマップが"CMOSを延命させたり CMOS代替デバイスの実用化を加速させたりするために必要とされる計測"の研究・開発方向を示している。計測は半導体技術において日常的にナノエレクトロニクスの領域を扱うようになった最初の分野である。ITRSの活動によって進歩が促された結果、CMOSを延命させるためのプロセスの開発や計測の開発が加速されている。CMOS以降に向けた材料やデバイスの最新研究から、課題を解決するための新しい戦力が生まれつつある。計測方法は、原子程度の大きさを測ることが当たり前のことになる。収差補正透過電子顕微鏡観察のような材料解析の手法を用いれば単層グラフェンの像を形成することはできるが、ナノメータ程度の精密さでパターン寸法を測ることは難しい。精密さを考える際の手引きとしては、これまでと同じような考え方を用いることができる。たとえば、形状が名目寸法値の1/10ばらつくと、デバイス特性に重大な変動をもたらすことがある。物質の性質の中には原子程度の特定領域に集中していないものがあると云う事実は注目に価する。原子レベルの測定では、ナノスケールの物性や測定に係わる物理を完全に理解していることが必要になる。工場における計測の基本的な課題は、大量生産に適した方法で原子程度の大きさの測定・制御が行えることであろう。

CMOS 以降に向けた計測の中ではグラフェンの像形成と特性解析についての取り組みが目をひく。シリコン上に形成された厚さ30mmの二酸化シリコンの上に置かれたグラフェン層を観る手段として光学顕微鏡観察法が重要な地位を占め続けている。高分解能の収差補正 TEMを用いることで初めてカーボン原子層の像を形成することができるようになった。収差補正(訳者注:球面収差の補正)に加えて、電子ビーム損傷を軽くするための低ビームエネルギー(80keV) および色収差を減らすためのモノクロメータと高輝度電子源が採用された;これらの手段を全て使ったとしても、データの解釈には注意深い解析やシミュレーション像との比較が要る。さらに、グラフェンの原子像を観るために原子レベルの解像度を得ようとすると念入りに試料の準備をしなければならない、またデバイスに組み込まれたグラフェン層では原子像を見ることができないかもしれない。ラーマン分光法や低エネルギー電子顕微鏡観察法(LEEM)を用いると多層試料の中のグラフェン層を特定することができる。単電子トランジスタの原理に基づけば走査プローブ顕微鏡を使って電子正孔パドルのような新しい現象を像として観ることができる。低エネルギー電子線回折や電子回折 TEM を用いることでグラフェン層のうねりの情報が得られるようになりつつある。ホール測定の結果、驚くほど高いキャリヤ移動度が示され半古典的量子力学的輸送理論へのベリー位相補正が観察された。次世代デバイスを開発するために緊急に必要とされると云うことで その他の物質についての計測も進歩している。しかし、孤立した薄膜あるいは表面層を対象とした計測が多く、機能デバイスに組み込まれた物質の計測に使うことができないかもしれない。

計測のお陰で IC の研究・開発・製造が続けられる。測定能力に係る課題は、パターン寸法縮小の速さと新材料や新構造の導入に応えることである。現行の方法で多世代に対応し得る場合もあるし、不十分な装置で測定せざるを得ない場合もあるう。重ね合わせ測定法や寸法測定法の開発が不完全なままでスペーサー工重露光のような新し、リソグラフィプロセスが製造に使われだした。デバイス設計の先の見通しがはっきりしないことが、上記の課題に加わる。ナノデバイスに向けての長期の研究は、新しい測定方法を提供してくれるうえに、計測にとって絶好の試走車になってくれる。引き続きその場計測やプロセス装置に一体化された計測が製造に導入されて行く。全ての計測は工場規模の自動化システムに接続されており、その自動化システムにはデータベースがあってデータ処理された情報が蓄えられている。オフラインの材料解析も工場規模の自動化システムに接続される方向へと進んでいる。先行的な顕微鏡観察法やプローブ技術は、使い方や得られたデータの解釈について理解ができていない部分はあるにしても、市販品として速やかに手に入れられるようになってきている。新しい材料解析法を上手く使えるか否かは、迅速な前処理法の開発にかかっている。全ての材料解析法が材料開発やプロセス開発にとって欠かせないものである、しかし製造時に必要となる計測を予測することはできない。プロセスの課題がプロセス改良に因って解決しても、"信頼性を保証するために、"製造時に何を測るべきか"という問題が未解決のまま残されている。

基板表面に応力層を設けたりチャネルにプロセス誘起応力を加えたりして移動度を高くすることのようなトランジスタ

#### 2 メトロロジ

特性を制御することの多くが、困難な課題のまま残っている。表面に形成された歪シリコン層の応力や歪みを測定することはできる。しかし、小さなゲートのチャネルのような"ナノサイズかつ埋め込まれた層に加わる応力や歪み"を直接測ることは、もっと難しい仕事になる。透過型電子顕微鏡を用いた破壊測定は断面試料を必要とするし、その断面試料の応力が構造全体の応力を代表しているとは限らない。大抵は、表面にある薄膜あるいは構造の性質を測った結果から、モデルを使って内部の層の性質を決めなければならない。ウェーハ表面での形状測定とモデル化とを組み合わせて計測することが今後の動向になる。

計測ロードマップでは、"先行的研究・開発と装置メーカの財政的基盤を固めることの必要性"を何年にもわたり繰り返し述べてきた。計測とプロセス技術開発との関係を根本から再構築しなければならない。かつての課題は、対象とするプロセス技術に先行して計測を開発することであった。今日の問題は、"材料が全く新しくなり デバイス設計が劇的に変わると言うのに、何が選ばれるかを予測できない"という予測の困難さである。"計測データおよび情報"と"最適フィードバック、フィードフォワードプロセス制御および実時間プロセス制御"との相互関係を理解することが、計測とプロセス技術との関係を再構築する際に重要となる。"スピントロニクスや分子エレクトロニクスのような根本的変化をもたらす新技術に必要とされる計測"の節が、新しく計測ロードマップに書き加えられた。

新しい計測技術は勿論、革新的な計測技術も、"3 年計画で導入される新しい技術世代"に歩調を合わせて研究・開発されなければならない。パターン寸法縮小のロードマップが、新しい材料、プロセスおよび構造に係わる計測の解決予定表を引き延ばしている。SOI や歪みシリコンのような基板材料は、測定をより複雑にする。計測は、これらのことを踏まえて開発されなければならない。計測は、装置開発、試作ラインや新しい生産ラインの垂直立上げ、および生産ラインでの歩留り向上を可能にする。計測は、プロセス装置やプロセスをより正確に評価できることから、"製造コストの削減"や"新製品を市場に投入するまでの時間の短縮"を可能にしてくれる。チップ種類の多様化が進むことは、課題の範囲をさらに広げることになり、すでに限界にある計測研究・開発のリソースを分散させることになろう。装置メーカ、半導体メーカ、コンソーシアムおよび研究機関の計測に携わっている人達は、ITRSで示された要求期限に間に合わせるために、協力して研究・開発および装置試作を行わなければならない。開発された最先端の計測技術は、時宜にかなったやり方で製品化されねばならない。パターン寸法と材料は 2003 年 ITRS 以来プロセスおよび材料開発用計測にとっての大きな課題である。

計測の短期的な課題は、"トランジスタ・配線用の新材料・プロセス・構造"および"寸法の比例縮小を制御すること"に係る要求が中心となる。16mm 世代およびそれ以降の技術が確定していないことは、計測技術の開発に大きな影響を与えている。FINFET および その他の新しい構造は、側壁薄膜などのような非常に難しい形状の測定を必要としている。技術世代毎に、数多くの材料が使用候補として考えられており、材料を開発し処理する過程で必要とされる評価や制御を行うために、これら材料の特性を評価することが必須になる。さらに、或る技術世代についてみると、"半導体メーカに依っては異なった材料が使われる"ということも十分考えられ、異なった計測が必要とされることも有り得る。highkとlowk 誘電体膜の電気計測および物理計測を今までと同じように短期間で進歩させなければならない。FEP ロードマップで議論されている最も確からしい情報に拠ると、極薄かっ恐らくは絶縁膜上歪シリコンの上に形成されたデバイスの測定技術が必要になる。新しい計測ニーズとして、スクライブライン上のテスト構造の代わりにアクティブエリア上の構造を測定したいとの要求が増えている。16mm 以下の技術世代を対象とする長期的な課題は、デバイス設計や配線技術の動向が明確でないことから、今述べることは難しい。Cu配線に代る技術の選択は、研究課題のまま残されている。材料評価や現行インライン計測の幾つかは新しいデバイスや配線の構造に使えるけれども、生産に適用可能な計測を開発するためには"材料、デバイスおよび配線構造についての或る程度以上の知識"が必要である。

3次元配線の計測は新規の緊急課題になっている。ウェーハアライメントおよびボンディングや その他の欠陥の観察には空間分解能の向上が必要である。シリコン貫通ビア(TSV)ではエッチや充填の欠陥を調べなければならない。

あらゆる分野の測定技術(特に"歩留り向上の章"に記載されている測定技術)が、情報に基づいたプロセス制御を

行うために、コンピュータ統合製造(CIM; computer integrated manufacturing)やデータ管理システムと組み合わされつつある。 組込み計測は、未だ普遍的な定義が成されていないけれども、"オフラインからインライン および その場測定への漸進的な移行"を表わす用語である。オフライン、インラインおよびその場測定を適当に組み合わせて用いることに依り、"最新のプロセス制御(APC)"および"歩留りの垂直立上げ"が可能になる。

計測装置の開発を成功させるためには、"新材料や新構造の計測に使えるようにすること"が必要である。実用化するためには、"必要とされる標準試料の製作"および"生産に先立つ計測方法の開発"に最新の技術・設備を活用できるようにしなければならない。活用するためには、計測技術開発とプロセス開発との連係をより緊密にするための注意が要る。計測がプロセス装置およびプロセスに上手く適合していれば、試作ラインや生産ラインの立上げ期間が短縮される。妥当な CoO(Cost Of Ownership)を維持しながら最大の生産性を得るためには、上手く設計・製作された装置と適切な計測を適当に組み合わせることが必要になる。

#### 概要

2009 年の計測ロードマップに記載されている項目は、顕微鏡観察;パターン寸法(CD; Critical Dimension)と重ね合わせ;膜厚とプロファイル;材料と汚染解析;ドーパントプロファイル;プロセス制御に用いる その場計測用センサとクラスタツール用計測ステーション;標準試料/標準物質(訳者注:寸法・形状に係わる Reference Materials を標準試料、その他の Reference Materials を標準物質とした);物理測定と電気測定との相関;そしてパッケージング(封止技術)である。これらの話題はこの章の以下の節で述べられる:顕微鏡観察法;リソグラフィ計測;FEP 計測;統計限界に直面しているプロセスおよび原子サイズに近づきつつある物理構造の計測;配線における計測;材料および汚染の評価・解析;組込み計測;基準測定システム(RMS; Reference Measurement Systems)、標準試料/標準物質;および新材料・デバイスの評価・解析と計測。

新しい計測技術および標準(訳者注:国家的あるいは国際的な規格および標準試料/物質)の開発には、国際的な 協力が必要になるであろう。計測およびプロセスの研究・開発機関は、装置メーカおよびICメーカなどの産業界と共同し て動かなければならない。ICメーカと計測装置メーカが早い時期から協力することで、"測定装置を最も効果的に使用 できるような技術ロードマップ"が作られるであろう。 計測・プロセスおよび標準の研究機関、標準の推進組織、計測装置 メーカ、および大学で計測に携わる人々は、計測方法の標準化・改善および標準試料/標準物質の製作に関し、引き 続き協力して行かねばならない。尺度に関する標準化された定義と手順があるにも拘らず、測定の精密さ対プロセス許 容度比(P/T比: Measurement Precision to Tolerance Ratio)のように、尺度を個々に用いることが普通である。P/T比は、統計的 プロセス制御(SPC; Statistical Process Control)に不可欠な自動測定能力を評価するためのものであり、測定ばらつきすな わち測定の精密さを製造ばらつきと関連付けるものである。測定装置の測定ばらつきは、当該製品あるいは当該プロセ スとは無関係の標準試料/標準物質を用いて求められることが多い。したがって、公称測定精度は製品ウェーハを測 定する際の装置起因測定ばらつきを反映していないかも知れない。装置感度が不十分なため、"小さいけれども許容 することができないプロセス変動"を見逃すことも有り得る。計測装置の分解能を統計的プロセス制御に使用するために は、分解能を正確に表わす尺度が必要である。"測定の精密さ対プロセスの変動し易さの比"の逆数は、信号対雑音比 (SN比) あるいは弁別比と云われることもある。しかしながら、何の分解能かは対象プロセスに依るので(厚さや幅の測 定には空間分解能、表面汚染金属のレベル測定には原子パーセントの違いを弁別するための分解能が要ることなど)、 分解能の尺度を測定項目毎に定めることが必要になるかも知れない。新しいニーズとして、"計測装置が連続的なデー タではなく離散的なデータを出力する場合の測定精度の決め方"を標準化することが挙げられる。このようなことは、例 えば、有意差が装置分解能よりも小さい時に起こる。

組込み計測の考え方は、スタンドアローン計測および"センサに基づいた計測(Sensor Based Metrology)"自体にも適用

<sup>&</sup>lt;sup>1</sup> For example, refer to SEMI E89-0999 "Guide For Measurement System Capability Analysis."

#### 4 メトロロジ

される。雰囲気温度や湿度の僅かな変動のように装置校正および測定精度に影響を与える要因は、監視され、計測装置の性能ひいては統計的なプロセス制御を改善するために用いられる。

ウェーハメーカ、プロセス装置メーカ、試作ライン、および新しく立ち上げる生産ラインの夫々で、測定への要求内容 および必要時期が異なる。試作ラインでは、より短い期間で立ち上げることが必要であり、試作開始前にプロセス装置 やプロセスを十分に評価・把握できるようにしなければならない。しかし、プロセスの完成度が高くなるにつれて、計測の 必要性は減小するはずである。デバイス寸法が縮小して行くにつれて、物理計測の課題は重要な電気特性データを 与えてくれるインラインでの電気テストと歩調を合わせて行くことになろう。

#### 産業基盤の必要性(Infrastructureneeds)

メーカが計測装置、センサ、制御装置、および標準試料/標準物質を合理的な価格で提供しようとするならば、健全な産業基盤が必要となる。MEMS (Micro-Electro-Mechanical Systems)を用いた計測やナノテクノロジのような芽をR&Dから製品にまで育て上げようとするならば、新規の研究や開発が必要となるであろう。多くの計測装置メーカは、小さな企業であり、先端的な用途向けに新しい装置を開発するための費用を負担できない。計測装置が当初に売れるのは、装置開発用やプロセス開発用だけである。開発した計測装置が半導体メーカに数多く・継続して売れるようになるまで、数年間を待たねばならない。装置メーカが新しい技術を設計概念の証明から装置試作・製品化を経て数多く売れるようにするまでの投資金額に見合う資金助成が必要である。

#### 計測で考慮すべきこと(CRITICAL METROLOGY CONSIDERATIONS)

#### 精密さと不確かさ(PRECISION AND UNCERTAINTY)

ロードマップ中の数値と測定結果を比較する場合に留意すべき点が幾つかある。比較の妥当性は比較がどのようになされたかに強く依存する。ITRSに記載されている精密さは、従来どおりの解釈でをすると、3σで表わされた単に一台の装置での再現性である。しかしながら2、よく調べると、"精密さ"という用語は恐らく"不確かさ"すなわち"話し言葉で誤差範囲と云われる測定誤差"のような広義の用語に置き換えた方が良いように思われる。Figure MET1に示すように、測定誤差は時間(再現性)、装置(装置間差)および試料(試料間のバイアス変化)の複雑な関数である。したがって、測定の不確かさは測定間・装置間そして試料間の変動成分を含んだ合計のバイアス変化として定義される。これらの成分は装置や使い方に依って重みが変わるかも知れない。これら成分についてのより厳密な定義と吟味は別の書を参考にできる。

バイアスは試料に依存しているので、正確さを標準試料/標準物質を使って正当に評価することはできない:標準試料/標準物質は対象とする製品やプロセスを代表するものではない。詳細については、後述する"標準試料/標準物質"および"標準測定システム"の節を参照されたい。

$Special \it attentions hould paid to insure that optimized sampling plans are used to align test and the \it reference data (see "Sampling Error" section below).$

Figure MET1 Relations of Time, Tool, and Sample Dependent Components of Uncertainty and Bias

#### サンプリングの要件(SAMPLING REQUIREMENT)

製造やリソグラフィに係る測定では、測定点数が不十分なことに因って誤差を生じることもある。良い例として、先行的プロセス制御(APC)を考えてみよう;フィードバックループは、入力データがそのプロセスの正しい統計的な平均値であることを必要とする。異なるパターンを一つずつ測定することは、平均値を高い確度で見積もるのに十分でないかもしれない。逆に、或る場合には、プロセス平均値が非常に重要であるばかりでなく、プロセス変動の情報も必要になる。これらの影響に因る誤差が"標本誤差"である。<sup>2</sup>

変わり易さということでは、ナノ領域の観察において真に完全な試料というものはない。集積回路には多くのパターンが含まれており、これらパターンの名目寸法は設計ルール上ぎりぎりの値に決められている;しかし現実には僅かと云えども必ず寸法ばらつきがある。これらパターンを一つずつ測定するCD-SEM或いは周期的(格子状)パターンを測定するスキャトロメータ、これ等の装置は夫々の試料を測定した結果数値の上で同じ精密さ或いは同じ不確かさを示すかも知れない、しかし試料を変えた時 CD-SEMの測定値はスキャトロメータの測定値よりも大きく変化するであろう:CD-SEMはスキャトロメータよりもラフネスに対する感度が高いからである。一方の測定装置が他の測定装置よりも不正確だと云うことではない、試料の採り方が違うのである:しばしば、測定限度。の違いと云われる。CD-SEMは形成したラインパターン像の一部を利用してパターン両端の距離を測る、一方スキャトロメータは格子パターンの広い照射領域から散乱光を集めてそのモデル解から平均寸法を求める。簡単に書けば、装置はプローブサイズが異なることによって異なった物を測ることになる:このことは精密さのみでは量れない。これら試料に因る違いのもう一つの考え方は、試料がラフネス周期の関数でありCD変動が、ラフネス周期のフーリェ・パワースペクトル。のように連続体になることである。計測装置が異なるとこのスペクトルに対する感度範囲が異なる;そして、観測される測定変動は装置の感度範囲でパワースペクトルを積分した値になる。スキャトロメトリは非常に大きな周期に比較的敏感であり、CD-SEMは小さな周期および局所的な変

#### 6 사ロロジ

動に対して感度が高い。しかし、注意すべきは、CD-SEMがスキャトロメータを真似られることである:大きな試料を測るために、一組の大量なデータを平均化することになる。CD-SEMでMFM (Multiple Feature Measurement)を使えば、CDデータを得るための像を大きくできるので、実際のプロセス変動に対する感度を維持しながらより大きなラフネス周期やライン幅変動を測ることができ、得られたプロセス平均値の信頼度が高くなる。4

APC を実行する時の手法が異なるとプロセス平均値を見積もる際の誤差が違うために異なった結果が得られる。もし 測定点数が十分で無かったとしたら、測定値の変動が大きくなり(すなわちサンプリングノイズが大きくなり)、APC が上手 く機能しないかも知れない。与えられたサンプリング計画で如何に測定結果を定量化するかが将来の調査テーマにな ろう。答えは問題の与え方に大きく依存するであろう。測定目的(相関/校正、SPC、プロセス評価)、どの程度の変動が見 込まれているか、そしてプロセスの変動およびあるいは平均値についての知識が如何に重要であるかのように、適用の 必要性を理解することが非常に重要となるであろう。より深い議論は別の書を参照されたい。

#### 困難な技術課題

以下に挙げられている"計測に関する短期的課題"の多くは、16nm 技術世代以降も課題として残るであろう。2016 年以降の計測ニーズは、これから明らかとなるであろう新材料および新プロセスの在り方に応じて変わるであろう。従って、将来の計測ニーズの全てを明らかにすることは難しい。パターン寸法を縮小すること、しきい値電圧やリーク電流のようなデバイスパラメータをより厳しく制御すること、そして 3 次元配線のような新しい配線技術は、物理計測技術に大きな挑戦的課題を与えることになるであろう。所望のデバイス・スケーリングを成し遂げるために、計測装置は原子スケールでの特性測定ができなければならない。Table MET1 に、計測の 10 大課題を示す。

Table MET1 Metrology Difficult Challenges

|                                                                                                                                                             | T                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 困難な技術課題 ≥ 16nmノード                                                                                                                                           | 問題の内容                                                                                                                                                |

| 実時間その場計測装置、組み込み計測装置、およびインライン計測装置の計測データを工場および会社規模で統合すること;頑丈なセンサ(robust sensors、訳者注:測定精度に余裕があり、環境の変動などに強いセンサ)およびプロセスコントローラの開発;センサの追加が可能なデータ管理。                | プロセスコントローラおよびデータ管理の標準規格が必要である。大量な生データを半導体製造の歩留り向上に役立つ情報に転換することが必要である。トレンチエッチング時の終点、およびイオン注入時のイオン種/エネルギー/ドーズ量(電流)を検出するために、より良いセンサの開発が必要である。           |

| SOI のような新しい基板が導入されると、シリコンウェーハの計測や製造での計測が影響を受ける。必要とされる感度でのシリコンウェーハの不純物検出(特に微粒子)およびウェーハ周辺部の検査不能領域の削減。薄い SOI の光学的性質および電子ビームやイオンビームによる帯電は、CD、膜厚、および欠陥検出に影響を及ぼす。 | 現在の計測能力では、ロードマップの目標レベルを達成することができない。極微小粒子を検出してサイズ分類しなければならない。SOI ウェーハの計測性能を向上しなければならない。課題は、SOI 構造からの余分な光散乱と表面の品質に因るものである。                             |

| 二度露光のような新しいプロセス技術、メモリ素子の容量やコンタクト穴のように複雑な3次元構造、および3次元配線の制御は、素早く立ち上げるための準備ができていない。                                                                            | 二度露光に対する重ね合わせ測定は、より厳し、制御を要求される。重ね合わせが CDを決める。3 次元配線には多くの実現方法がある。新しいプロセスを制御するために必要とされることが明確になっていない。たとえば、容量・デバイス・コンタクトを含めてトレンチ構造には3次元(CDと深さ)測定が必要であろう。 |

| 複雑な積層材料の測定、および界面における物理的性質や電気的性質の計測。                              | 制御された薄膜と界面層を含む新 highk ゲート/容量誘電膜、配線バリアのような薄膜と lowk 誘電膜、およびその他のプロセスニーズに対応する標準試料/標準物質と標準測定方法。ゲートや容量誘電膜の光学的測定結果は広い領域の平均であり、界面層の評価・解析が別に必要になる。歪 Si や SOI 基板あるいはバリア層の測定で積層構造に対するキャリア移動度評価が必要になるだろう。メタルゲートの仕事関数の評価は、もう一つの大きなニーズである。 |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 測定用のテスト構造と標準試料/物質。                                               | 特にスクライブラインでテスト構造に割当てられる面積が縮小している。スクライブライン上に置かれたテスト構造ではチップ内の特性変化と相関が取れないという懸念がある。重ね合わせその他のテスト構造はプロセス変化に敏感であり、テスト構造はスクライブライン上とチップ内の対応が取れるように設計を改善する必要がある。標準化機関は最先端の開発・製造ラインを使って標準物質を作ることができるように早急に働きかけることが必要である。               |

| 困難な技術課題<16nm                                                     | 問題の内容                                                                                                                                                                                                                        |

| ウェーハおよびマスクに関する 3 次元構造の寸法測定/重ね合わせ精度測定/欠陥検出/解析に使用する非破壊の生産用顕微鏡観察技術。 | 表面帯電およびコンタミネーションは SEM 像形成時の障害となる。 寸法測定ではパターン側壁の形状を考慮しなければならない。 ダマシンプロセスにおけるトレンチ構造の寸法測定が必要である。 ステッパの焦点と露光量、エッチバイアス(エッチ後寸法とレジスト寸法の差)などのプロセス制御は高精度化と3次元対応が必要である。                                                                |

| チップ内特性を測ることでチップ間やウェハ間ばらつきを反映できるような新し、計測法を考える必要がある。               | デバイス縮小に伴って、テスト構造を変えた場合の特性とチップ内の特性との相関を取るのが難しくなっている。測定試料の択び方を最適化することが、これ等の問題を解く鍵である。                                                                                                                                          |

| 統計変動が顕在化する32nmノード以降でのプロセス制御。                                     | 自然現象としてのゆらぎが計測を制限する領域では、プロセスを制御することが困難となろう。たとえば、低ドーズのイオン注入、薄いゲート絶縁膜、および極微細構造でのエッジラフネスである。                                                                                                                                    |

| デバイススケールでの構造や組成の解析、および CMOS 以降<br>のデバイスの測定。                      | 界面層制御、ドーパント位置、欠陥、元素濃度に関して、デバイススケールとの対応が取れるような材料評価や計測方法が必要。一例は、3 次元のドーパントプロファイル測定。自己組織化プロセスの測定も必要である。                                                                                                                         |

| デバイス構造と配線技術が明確にならない段階で製造における<br>計測を決める必要がある。                     | 現在のトランジスタに代る新デバイス構造や Cu 配線に代る材料が検討されている。                                                                                                                                                                                     |

Table MET2 Metrology Technology Requirements

#### 顕微鏡観察(MICROSCOPY)

顕微鏡観察は、"2 次元分布"すなわち"集積回路(IC)パターンの形状や外観を示すデジタル画像"が重要な情報を与えてくれるので、核となるプロセス技術の多くに用いられている。通常、"先ず画像形成ありき"ではあるが、画像形成は多くの場合 "それを観察し、測り、そして制御することができる"という一連の過程の第1段階に過ぎない。顕微鏡は、一般的には光、電子ビーム、あるいは走査プローブを用いる。"画像形成した後に測り制御する"というオンラインの応用には、欠陥や微粒子の検出・レビュー・自動分類に加えて、パターン寸法(CD)や重ね合わせ精度の測定がある。ウェーハが高価かつ多量に要ることから、高速、非破壊、インラインでの画像形成・測定の要求が増えつつある。IC パターンのアスペクト比が大きくなりつつあることから、これまでの横方向のパターン寸法(例えば線幅)の測定に加えて、3 次元形状を詳細測定することの重要性が増しており、インラインで使えるようにすべきである。"先進的なデジタル画像処理・解析技術、遠隔存在(Telepresence; 訳者注:ここに居るのに、其処に居るように感じさせること)およびネットワークで結んだ測定装置"を活用する新しい計測方法は、近い将来の IC 技術ニーズに合わせて開発することが必要であろう。これらの技術を用いた顕微鏡観察の技術や測定は、技術者がプロセスをより自動的なやり方で管理できるように、詳細

かつ十分なプロセス情報を逸早く提供するように機能しなければならない。

あらゆる種類の顕微鏡観察法およびそれらに基づく計測では、装置の性能を監視するために、信頼できて操作が容易な方法を開発・提供することが益々重要になってきている。集積回路の構造が小さいためこれらの装置は 最高性能で動作しなければならない、それを達成・維持することは容易でない。現在、十分な性能を保証するためには原始的な方法に頼らざるを得ない。像や測定の分解能以上に、装置に依存するパラメータも定期的に監視・最適化されることが必要である。これらの重要パラメータは結果に重大な影響を与え、測定不確かさの要因に含めなければならない。

電子顕微鏡観察 - "電子ビームを試料に照射し画像を形成する原理の顕微鏡観察"には、様々な方式がある。 走査電子顕微鏡観察、透過電子顕微鏡観察、走査型透過電子顕微鏡観察、電子線ホログラフィ、および低エネルギー電子顕微鏡観察などである。走査電子顕微鏡観察および電子線ホログラフィについては以下に述べる。透過電子顕微鏡観察、走査型透過電子顕微鏡観察、および低エネルギー電子顕微鏡観察については、"材料および汚染の評価・解析"の節で議論する。

走査電子顕微鏡観察(SEM; Scanning Electron Microscopy) - 断面加工試料の評価・解析、微粒子および欠陥の解析、 欠陥像のインライン観察(欠陥レビュー)および CD 測定のために、オフライン(at-line: 訳者注:米国では工場内でのオ フライン計測を at-lineと云い、ウェーハを工場外に持ち出して行うオフライン計測を offlineと云うが、この場合は前者の意 味で使用されている)およびインラインの像形成法として使用され続ける。45mm 世代以降も CD 測定および欠陥レビュ ー(および試作ラインでの欠陥検出)を効果的に行って行くためには、改良が必要である。十分な分解能を保ちながら "試料表面の帯電、コンタミネーション、および照射損傷に起因した像質の劣化"を防ぐためには、超低エネルギー電子 ビーム(<250 eV)や高エネルギーSEM(10keV~200keV)を用いるなどの 新しいインライン SEM 技術が、必要となるかも 知れない。球面収差を低減して分解能を上げようとすると、実用にならないほど焦点深度が浅くなってしまうので、"幾つ かの焦点位置で取られた信号を重畳して像形成すること" およびあるいは "ビーム形状を考慮したアルゴリズムを使用 すること"が必要になるかも知れない。SEM の分解能を大幅に上げるために、透過電子顕微鏡で用いられていた収差 補正レンズ技術が、SEM に転用されるようになった。ナノチップの使用や電子線ホログラフィのような非従来型の像形成 技術を開発することが価値のあることとして証明された場合には、その開発を進めなければならない。圧力下すなわち 雰囲気制御下での顕微鏡観察は、"高加速電圧での高分解能な像形成および計測"への可能性を開いてくれるもの で、新しい代替手法の一つとなり得る。バイナリマスクおよび位相シフトマスクが、この方式の高分解能走査電子顕微鏡 で上手く観測された。試料をガス雰囲気中に置くことは、表面帯電やコンタミネーションを低減することが分った。この方 法は、ウェーハの検査、像形成、および計測にも高い可能性を持っている。

測定の物理に従いかつ 収集された全ての情報を用いるようなデータ解析法は、独自の方法に比べて優れていることが実証された。 "測定された像とモデル化された像" および "速くて正確な比較技術"は、SEMの寸法計測において、重要性を増しつつあるように見える。

CD 測定精度を向上するために、"試料物質と得られたラインプロファイルとの関係について理解を深めること"が望まれる。試料物質の直接電離とゲート構造の帯電に起因した試料損傷が、荷電粒子ビームを用いる全ての顕微鏡の根本的使用限界を決めることになるかも知れない。

90nm 以下のコンタクト/ビアホール、トランジスタのゲート、配線ラインあるいはダマシンの溝と言った構造の実際の 3 次元形状を測るためには、現行の顕微鏡観察および試料作成法を引続いて進歩させることが必要であろう。完全に自動化された FIB (Focused Ion Beam:収束イオンビーム)による断面加工 および TEM (Transmission Electron Microscope:透過電子顕微鏡)あるいは STEM (Scanning Transmission Electron Microscope: 走査型透過電子顕微鏡)で像観察するための半自動化されたリフトアウト(訳者注: FIB を用いてウェーハから切り出した試料を顕微鏡の試料台に装填すること)は、効果的であることが実証された。

He イオン顕微鏡観察(HIM) — "細く絞られた電子ビームと試料の相互作用に関連して実効的なプローブサイズが拡がること"に係る問題を克服するための手段として提案された。この技術は CD 測定、欠陥レビュー、およびナノテクノロジーに応用できる可能性を持っている。HIM で lmm以下の分解能が達成された、しかし試料との相互作用については未だ疑問のままである。

走査プローブ顕微鏡観察(SPM;Scanning Probe Microscopy) — CD-SEM(Critical Dimension Measurement Scanning Electron Microscope)の測定結果の校正に使用されるかも知れない。原子間力顕微鏡(AFM)のように尖鋭なプローブを用いた SPM は、"被測定試料の材質に影響され難い 3 次元測定"を可能にする。プローブが細過ぎると、プローブ先端のチップ先端部が曲げられて測定精度が悪くなる。したがって、プローブ材質と走査時に受ける力を考慮して、チップ先端部の形状とアスペクト比を妥当な値に設定しなければならない。短いカーボンナノチューブ(訳者注:炭素原子で構成された径が nm 程度の筒)のような非常に硬いプローブ材料が、この問題を多少とも解消してくれるかも知れない。

遠視野顕微鏡観察(Far-field Optical Microscopy) - 訳者注:回折光を利用した通常の顕微鏡での観察) - 分解能は光の波長に依って決められる。波長による限界を打破するため、遠紫外光源を用いた顕微鏡および近接場光学顕微鏡(Near-field Microscopy; 訳者注:光が波としての性質を発揮できない極微小な領域の光、すなわち近接場光あるいはエバネッセント光を利用する顕微鏡での観察)の開発が進んでいる。自動欠陥分類ソフトの改良が必要である。光学顕微鏡は、今後も引続いて、マルチチップモジュールのハンダバンプのような大きなパターンの検査に使われて行くであろう。

欠陥検出技術 — 各技術が極限的問題を抱えている。欠陥は"歩留りを低下させる恐れがある全ての物理的、電気的あるいはパラメータ的な異常"として定義される。現行の SEM や SPM の欠陥検出速度は、光学顕微鏡に取って代わるには余りにも遅すぎる。アレー型 SPM(訳者注:複数の SPMを配列した SPM)を用いることで高速走査の可能なことが実証されてきた(SEM よりは速いかも知れない)、しかしプローブチップ先端部の寿命、均一性、特性、および摩滅に係わる問題が処理されねばならない。アレー型 SPM の技術は、並べる SPM の数を増やすことと多様な操作モードを開発することに力を注ぐべきである。アレー型マイクロカラム SEM(訳者注:複数の超小型鏡筒を配列した SEM)が SEMのスループットを上げるための手法として提案され、単鏡筒のマイクロカラム SEM ではその動作が実証された。静電レンズおよび磁界レンズの設計限界に挑む研究が必要である。

#### リングラフィにおける計測(LITHOGRAPHY METROLOGY)

パターン加工技術の急速な進歩は、リソグラフィ用計測に対して、相変わらず困難な課題を課し続けている。トランジスタのゲート長における変動を正確に制御する取り組みは、マスク計測から始まることになる。マスク上の全ての図形は、露光装置の投影倍率の関係上、ウェーハ上に投影されたレジスト図形の4倍の大きさであるが、位相シフトや光近接効果補正のための補助パターンの大きさは、投影されたレジストパターンサイズの半分程度の大きさである。マスクエラーファクター(MEF)が大きければ、マスクプロセスでもタイトなプロセス制御をしなければならないだろう。したがってより正確な計測技術が開発されなければならない。マスク計測には、光の位相が正確に転写したかどうか観察できる計測が含まれる。ウェーハ上に形成されたパターンのCDと重ね合わせ精度の測定もまた、次第に困難な領域に入ってきている。トランジスタのゲート長のCD制御は、クロックスピードが早くなっているIC製造においては、依然として重要な要素になっている。プロセス制御と製品の処置判定のための計測技術の必要性が、"計測の不確かさ"(measurement uncertainty)の改善の原動力になり続けてゆく。将来の技術世代のために使用可能な計測技術を提供しようとするならば、CDと重ね合わせズレ計測に対する研究・開発活動を加速することが不可欠である。これら全ての課題に対して、"測定能力の評価方法"を発展させる必要がある。(リソグラフィの章を参照)

#### 10 メトロロジ

従来の顕微鏡ベースのCD計測システムをプロセス制御に応用し、製品上のモニターから、実効的な露光量、フォーカスを計測するに至っている。同様のシステムによって、リソグラフィプロセスのモニター同様にCDや重ね合わせ計測情報を出力することができる。そういった計測のプロセス制御能力と効率は進歩している。そういった新しい応用を支援する社会基盤も概ね出来上がっている(装置や機能が市販化されている、あるいは機能の改良が可能な状況にある)。例えば、重ね合わせ計測で使用されている従来の光計測システムでも計測できるように、リソグラフィプロセス制御のための実効露光量、フォーカスモニターもまた開発されてきている。同様の能力を有する計測手法としてCD計測に加えて、サイドウォール、高さ計測がスキャトロメリーで行われようとしている。全てのケースにおいて、プロセス制御のためにCD計測を行うというより、あらゆるパターン(図形)のCDは露光とフォーカスの複雑な関数であり、これらのシステムは、露光量誤差が1%(3g)、フォーカス誤差が10mm(3g)程度の計測誤差を持つプロセスパラメータそのものを出力することができる。今日のプロセスモニターの能力は、15%の露光量、200mmのフォーカスのプロセス裕度に対して、P/T (precision to tolerance) = 0.1 といった高いレベットにあり、これが大量生産におけるkiファクタの更なる縮小を可能にし、光リソグラフィを延命している。計測システムの安定化とマッチング精度に対する要求が増大する傾向がある。一方、この領域における活動として、より厳密な制御とマッチング精度を高める開発を目的とした取り組みが始まっている。これらの活動は正確なCD計測の前提であり、単なるプロセス制御の応用や、専用のプロセスモニターに特化したものでは無い。

計測能力が高く、効率的な直接プロセスモニター方式のリソグラフィプロセス制御においては、従来の CD 計測の技術限界を克服する能力を持っている。現在リソグラフィプロセス制御の手法は変化しているが、この変化を加速するためには、企業間の協力によって、直接プロセス制御の要求項目を明確にし、その制御効果を実証し、新しい計測技術の応用と応用環境の標準化をすることが重要である。こういった変化の結果、優れた CD 計測メーカによって高性能で効率的なプロセス制御の手法が提供され、差別化が行われ、リソグラフィの計測に恩恵をもたらすだろう。しかしながら、特に、校正や先端マスクデザインルール(例:OPC(光近接効果補正)、RET(超解像技)や様々な露光条件においての 1、2、3 次元のスルーピッチ計測あるいは各種レイアウト計測を通して検証される)が遵守されているかどうかを検証するための CD 計測の領域において、次世代技術の計測要求を満たすには、"絶対的な正確さ"(absolute accuracy)の新たな基準が必要である。

現状必要とされる全ての情報を提供できる単一の計測技術は存在しない。それゆえに様々な次元の計測装置や計測方法に対して、意味のある比較が出来るようにするためには、"繰り返し精度"(repeatability)や"精密さ"(precision)を超えた変数が求められる。それぞれの計測を適用するにあたって、相対精度(CD変動に対する感度と2次的な特徴の変化に対する非敏感度)、絶対精度(絶対基準長を辿ることができること)、LER やサンプリング、計測における破壊の性質を考慮することが必要である。

全ての計測装置に対して、計測の不確かさを、その主要な要因の発生を含めて、正確に特徴付けることができれば 理想的であろう。計測の不確かさを記述するにあたっては、国際的に認可されている手法の使用が推奨される。こういった知識は、全ての計測機を最大限に活用するのに役立つ。また、計測した結果が必要とされる情報を含んでいない といった状況を回避できる。最後に、一旦計測誤差の主要因が判明すれば、より良い計測装置がすばやく開発される 状況が生まれる。そこで、様々な次元の計測機について、計測の不確かさを国際的に認可された方法に従って記述し、 その主要因を特定あるいは定量化することを強く推奨したい。

しばしば、製造工程において、特殊なテスト構造を用いたCD計測が行われている。このような場合においては、実素子の寸法は計測されない。CD-SEMは、今後もウェーハあるいはマスク上のラインパターンやビア/コンタクトパターンを計測するのに用いられる。193 nmの露光パに用いられるフォトレジストの電子ビーム照射ダメージを克服するために、かなりの努力が注がれてきた。そして、EUVLといった代替リソグラフィ技術が導入される際も同様のことが行われるだろう。積層構造材、表面状態、ラインパターン形状、あるいはラインパターン近傍のレイアウトでさえCD-SEMの2次電子信号波形や、ひいてはその信号波形から抽出されるラインパターンのCDに影響を及ぼす。これらの効果が、正確にモデル化され補正されなければ、CD-SEMの"計測変動"(measurement variation)やトータルの不確かさが増加してしまう。分解能と

"精密さ"(precision)を向上させる電子ビーム光源の開発試験が続けられている。CD-SEMは、SEMを基本原理としたCD計測において、新たな手法が見出せない限り、浅い焦点深度の問題に直面することになるだろう。高加速電圧のCD-SEMや低損失検出器がCD-SEMの延命として提案されている。。

統計的に確かなSEM計測を実現するためには、適切な種類と量の情報を集めることが不可欠である。必要以上の情報を集めることはスループットの低下につながる。一方、情報が不十分であったり、間違った情報を収集した場合にはプロセス制御を損なってしまう。計測の妥当性を示すと共に、必要な情報を明らかにし、それを表現する計測手法を開発することが大切である。SEM分解能レベルのピクセルを用い、かつ、より広い視野(FOV: Field Of View)を用いることにより、多点計測(MFM: multiple feature measurement)の活用領域を大幅に広げることが出来、単位時間当たりの情報量を増やすことが出来る。これにより、スループット低下を招くことなくサンプリング量が増え、計測結果の有効性が高まる4。

CD-SEMとDBM (Design Based Metrology) アプリケーションでは、設計情報を利用した自動レシピ作成を行うことができる。このアプリケーションでは、2次元輪郭線情報の取得とGDSファイルとの比較を通して大規模な設計インテントの検証にSEMを用いることを可能とした。技術世代の進展と共に、リソグラフィでのOPC開発に必要な計測点数は指数関数的に増大すると考えられ、OPCの開発並びに検証のためにはDBMアプリケーションが非常に重要となってきている。また、ダブルパターニングのためのDBMアプリケーションも検討されている。これはDFM (Design For Manufacturing) の領域『とのインターフェースとして中心的な役割を担っている。4 また、レティクル上のCD情報を集めウェハ上のCD情報と比較することはいくつかの場合において重要なアプリケーションであり、輪郭線情報と共に用いることにより大きな効果を出すものと予測される。

しかしながら、まだ多くの解決すべき課題が残っている。それらは輪郭線の誤差要因のテスト方法、輪郭線のレファレンス計測、SEM輪郭線のモデリングなどである。12314 輪郭線の信用度は共通の技術課題であり、最新の改善によりこの産業に価値がもたらされる領域である。輪郭線の欠落部あるいは消失部は、試料あるいは計測装置のいずれにも関係する理由により発生し得る。これらは、エッジに平行な方向へ電子線(高速)走査を行った際の微弱な信号(訳者注:二次電子信号)、あるいはその切れ目、また、輪郭線に沿った信号コントラスト変動を主な要因として発生する。それらは下層構造の変動(例えば、側壁角度の変化、再進入(reentrance))や走査型電子顕微鏡(SEM)におけるエッジ近接効果のような装置特有の事由により発生する。

例えば、アクティブエリア上のポリシリコンゲート配線の場合のようないくつかのケースでは、輪郭線の切れ目が自然に発生してしまう。完全な輪郭線を得るというこの課題は、輪郭線の抽出精度と強い関係がある。輪郭線抽出アルゴリズムは2次元画像処理技術を用いるため、従来のラインスキャン方式による 1 次元の CD 値抽出アルゴリズムとはその機能が異なる。特に、エッジ検出と信号平均化の程度に大きな違いがあることが知られている。また、サンプリングも大きな影響を及ぼす。わずか5本の輪郭線を平均化した場合であっても、パターンの局所ラフネスの影響は平均化効果により除去されるため輪郭線抽出精度が向上する。これにより SEM 画像より抽出された輪郭線とシミュレーション((訳者注:リソグラフィシミュレーション)による輪郭線との一致度も改善される。

効果的な OPC のためには、SEM 輪郭線と設計データの位置合わせに関する要求事項にも注意を払っていく必要がある。SEM 輪郭線と設計データ間の回転ずれ、位置ずれオフセットを補正する機能、視野歪みを補正する機能がモデルに必要である。これは製造誤差に及ぼす計測精度といった問題に多少なりとも影響する。SEM 輪郭線と設計データをマッチングさせる際の計測誤差の許容範囲についてはまだ合意に至っていない。例えば、輪郭線を引き伸ばすことにより除去される一定の倍率誤差は SEM 視野内の非線形性ほど問題とはなっていない。

輪郭線計測精度の改善に有効な他の手段として、輪郭線抽出法とモデリングソフトウエアの高度化がある。例えば、 輪郭線抽出精度を明らかにするため 95%信頼区間を設定する方法がある。 最終的な輪郭線計測の指標は、このロード マップ中にもある従来の線幅計測の指標と矛盾しないものとすべきであることを明記しておきたい。 スキャトロメリーは製造現場に導入され、ラインパターンの形状計測に用いられるようになった。スキャトロメリーには、単一波長 一多入射角光散乱測定と、多波長 一単一入射角光散乱測定の2方式がある。最近の進歩としては、シミュレーションにより生成したライブラリーを使用しなくとも、CD やラインパターン形状を特定できる精度に到達している。スキャトロメリーはAPC における計測機として用いられることで、トランジスタの主要な電気的特性の分布を、非常にタイトに制御できることが示されている。次の段階は、コンタクトやビア構造に適用できるスキャトロメリーの開発である。スキャトロメトリーの計測モデルは、ラインパターンや下地の材質の光学的な性質が均一であるということを仮定している。表面異常や不均一なドーパント分布はスキャトロメトリーの計測結果に影響を及ぼす可能性がある。それゆえに、スキャトロメトリーのモデルでは、校正や定期的な検証が不可欠である。リソグラフィとエッチングのマイクロローディング効果はラインパターンのCDに顕著な影響を及ぼすだろう。スキャトロメトリーは特殊なテスト構造を用いて計測を行うため、SEM、AFM、あるいはTEMなどの他のCD計測技術を用いて、スキャトロメリー計測用テスト構造のCDと回路中のパターンのCDとの相関を取る必要性がある。スキャトロメトリーは、計測の"精密さ"(precision)を高めると同時に、小さなテスト構造でも計測できるようにする必要がある。ダブルパターニングの使用量が増えると、加工されたパーンの計測において様々な技術課題が発生する。2回に分けて露光されたパターンについて、CD、側壁角、ラフネス、ピッチ(合わせずれ)など、それぞれの分布を別個に計測し制御するが必要となる。いくつかの手法では、反射防止膜(ARC)を用いることによりUV光が下層に侵入するのを防ぐことが出来るかもしれない。

CD 計測に関して新たな計測方法の提案がなされており、その計測手法が製造ラインへ最初に導入される機会は22 mm DRAMハーフピッチの世代となる模様である。32 mmハーフピッチについては既にデバイス開発段階に入っており、 β版の計測装置は、あらゆるプロセス領域で使用できる状況にある。新たに有効な計測の解決策としては、He イオン顕微鏡(顕微鏡の章で議論されている)や小角X線散乱(CD-SAXS; Small Angle X-ray Scattering)が含まれている。CD-SAXS はグレーティング構造の試料にX線を照射し、その透過X線情報を計測することで、測定試料の平均CD、サイドウォールの角度およびラフネス、さらには、グレーティング構造における各ラインのCD線幅のバラツキも計測する能力を有することが示されている。

製品の性能を向上させるために、リソグラフィ計測におけるフィードフォワード制御の概念を広げ、少なくともレジストパターンやマスクパターンの測定データを用い、エッチング等の次工程のプロセス制御を行う仕組みが必要である。フィードバック制御の仕組みも、過去に取得した大量のデータから適切なプロセス制御パラメータを設定するために同様に必要である。CD制御に重ね合わせ精度測定装置を用いることも既に報告されている。この方法は、ラインパターンの幅の変化がフォトレジストラインパターンのラインパターンの長さにも影響をするといった事実に基づいており、このラインパターン長は、光学式の重ね合わせ精度測定装置を用いて測定することができる。この場合、ラインパターン配列とスペースパターン配列を含む特殊なテスト構造が必要である。

CD-AFM 計測はラインパターン形状や CD 計測、あるいは輪郭線計測の校正に用いることができる。もし、CD-AFM を 50 mm 以下の密ラインパターン計測に適用するのであれば、新規なプローブチップ技術と 3 次元傾斜可能なカンチレバーが必要である。フォーカスー露光量との相関の調査(特にコンタクト/ビアホールに対して)に関しては、ラインパターン形状との相関が直接観察できるデュアルカラムの FIB(SEM+FIB)は勿論のこと、前述した全ての方法で行うことが出来る。電子線ホログラフィーも長期的な CD 計測技術として提案されている。

#### ラインラフネス(Line Roughness)

ラインエッジラフネス(LER)はリソグラフィプロセスで制御すべき重要な項目であり、ライン幅ラフネス(LWR)はエッチングプロセスにおける重要な制御課題である。リソグラフィの技術ロードマップでは、LERとLWRの測定基準を示している。2001年のLWRに対する要求は、LERとして記載された。LWRはトランジスタの駆動電流との相関は無かったが、リーク電流の増加と相関があったため「5、2001年ITRSに記載された。「S LER、LWR計測方法については、SEMIスタンダードとして定義されている」。 以下に示すように、LERの計測精度"精密さ"の要求値は、CDのそれの数年先を行く値である

ことに留意しなければならない。CD-SEMやリソグラフィープロセスシミュレーションシステムは、LERを計算するソフトウェアを搭載しているが、まだ、すべてのシステムが、LER計測を規定した新しいSEMI標準を遵守しているわけではない。

LER/LWR は 2 つの方法によって評価される。スペクトル分析と LER/LWR の振幅程度(一般的に、平均位置あるいは 平均 CD に対する残存成分の 3σとして定義)である。LER/LWR のフーリエスペクトルは R&D では一般的になりつつある。しかしながら、実際のインラインパターン計測において、3σは依然非常に使い勝手の良い指標である。LER/LWR を 評価する際に、検査エッジの長さ(L)とエッジ検出のサンプリング間隔(Δy) は最も重要な計測パラメータである。というのは、3σは LとΔy に強く依存するからである。

推奨されている LER/LWR の測定基準は、現在 2-μmのラインパターンに沿って、残存成分の 3σとして定義されている。しかしながらトランジスタの性能は、将来的にゲート内のラフネスに非常に敏感になることも有り得る。そのような場合、ゲート内のラフネスに対して新しい指標(例えば、高周波成分の LWR)が追加定義されるべきであろう。LWR 起因のゲート CD変動を分離して評価するためには、低周波数成分の LWR の指標も同様に定義する必要がある。

画像処理を基にしたLWR/LERの計測におけるもう一つの重要な誤差要因は、エッジの検出におけるノイズである。このノイズは、ラフネス計測において十のバイアス(偏差)を発生させる影響をもたらす。これは、LWR<sub>mss</sub><sup>2</sup>=LWR<sub>attr</sub><sup>2</sup>+  $\sigma_{\epsilon}^2$ の式で表現される。LWR<sub>mss</sub>は計測値であり、LWR<sub>attr</sub>は、被測定パターンの実際のラフネスである。 $\sigma_{\epsilon}$ はノイズ項であり、所定の計測サンプル点に沿ってエッジ位置を特定するための計測再現性(reproducibility)として定義される。 $\sigma_{\epsilon}$ の大きさ 2.5 mm程度と計測されており、この値は、将来のテクノロジーノ世代において、実際のラフネスの計測値を覆い隠してしまう懸念がある。このノイズ項を除去するための方法論が示されており、これによってラフネスの普遍推定量が求められる。これを用いることは将来のラフネスの計測の"正確さ"(accuracy)を保証するために非常に重要であり、同時にリソグラフィ計測のコミュニティー内でデータの比較を許容するための重要な要素になるべきだと考えている。<sup>20</sup> 留意しなければならないこととして、計測装置の分解能がLWR計測要求値に近づくにつれLWR計測自体の課題が大きくなることがある。22mmノードでのLWR計測には 1.3mmの分解能を必要とする。この値は、現在のCD-SEMの分解能と同程度である。

#### 計測の不確かさ(MEASUREMENT UNCERTAINTY)

CD計測の性能は、個々の計測装置の計測再現精度(reproducibility)、計測装置間のマッチング精度、計測サンプル 間の計測バイアスの変動から生じる計測変動をすべて含んだ"精密さ"(precision)要求を満たしていない。SEMIでは"精 密さ"(precision)を計測再現精度(reproducibility)の倍数として定義している。序論で紹介したように、計測再現精度 (reproducibility)は、繰り返し精度(repeatability)、ウェーハの再ロードによる変動、長期のドリフトを含んでいる。実際問題、 計測再現精度(reproducibility)は、同一サンプル、測定個所を長期にわたって繰り返し計測することによって決定される。 ITRSにおけるCD計測の精度"精密さ"要求には、いつもラインパターン形状と材質の違いの影響が含まれていたが、同 一サンプルの繰り返し計測では、サンプル間のバイアスの違いに関連した計測の不確かさは判らない。それゆえに、現 状の方法論では、ラインパターン形状や材質、レイアウト、あるいは他の要因の違いに関連した計測の不確かさは"精 密さ"(precision)には含まれないことになる。通常CDプロセス制御に用いる標準試料は、それぞれのプロセスレベルで特 別に選別された最適なウェーハ、あるいは"golden"ウェーハである。そのようにして、企業での慣例においては、計測の "精密さ"がそれぞれのプロセスレベルの計測再現精度(reproducibility)と決められる。計測のバイアスを検知することはで きない。このやり方では、計測の不確かさの成分である計測のバイアスの変動成分を欠くことになる。これに照らして、総 合計測不確かさ(TMU)といった新しい計測基準を用いることが出来よう。12 総合計測不確かさは、テクノロジーを代表 する一組の試料を用いて決定される。そして、それらの試料はそれぞれの工程に関連した計測バイアスのバラツキを説 明できる必要がある。この考え方は、FMP(Fleet Matching Precision)24というもう一つの計測基準を用いて、製造ラインで複 数の計測装置を使用する場合にも拡張できる。これらの計測基準は、全ての計測装置の"正確さ"(accuracy)を網羅して いる。つまり、計測装置群が単一の計測装置に要求されると同様に振舞うことを想定している。また"正確さ"(accuracy)やマッチングに関して他の計測手法も有効であることも留意しておく必要がある。

インラインCD計測機の校正は、注意深く校正用計測機を取り扱うことが必要である。例えば、研究レベルで用いているTEMやCD-AFMは、インラインのCD計測機に相当するか、それ以上の"精密さ"(precision)が無くてはならず、頻繁に校正もしなければならない。製造中に用いられる標準試料は、実際のプロセス工程と構造を代表するものでなくてはならない。また、テスト時に計測装置で評価される値は、プロセス変動を適切に反映したものでなくてはならない。この手法に関する報告は既に行われている。

CD 計測は、ラインパターンの形状制御まで応用されるに至った。傾斜ビーム機構の CD-SEM、ゴールデンウェーハのラインスキャン 2 次電子波形との比較、スキャトロメリー、CD-AFM やデュアルビームの FIB/SEM(電子ビームとガリウムイオンビームの併用システム)、そしてトリプルビームの FIB/SEM(電子ビーム、ガリウムイオンビーム、及びアルゴンイオンビームの併用システム)が、ラインパターン形状計測に応用されてきた。サイドウォールの角度は、重要なプロセス変動要因として提起された。既にフォトレジストのラインパターンは、一枚の平面図形ではサイドウォールを上手く表現できない形状を有している。ラインパターンに沿った LERと LWR、垂直方向の LER、そして丸みを帯びたトップ形状は、プロセス制御において考慮すべき重要なポイントである。前述したように、"精密さ"(precision)の値は各々のプロセス工程毎に変化する。これによってエッチングバイアス(エッチング前後の CD 差)を求めるのが困難になっている。電気的なCD 計測によって、ゲートや配線のラインパターン線幅を観測することが出来るが、これはウェーハの再生処理が不可能な時点に限られ、リアルタイムのプロセスパラメータ補正用途には適用できない。電気的 CD 計測は、その適用性が導電性材料に限定される。

マスク計測は、現在の光技術では測れない領域に入っている。圧力/雰囲気制御走査電子顕微鏡観察法を用いてバイナリマスクおよび基板掘り込み型位相シフトマスクを調べることが行われ、良い結果が得られた。高分解能、高信号、大きな試料室および試料交換機能と組み合わせての電界放出技術を装備した雰囲気制御走査電子顕微鏡は、マスク CD 計測を行う半導体産業の分野で既に使われるに至っている。圧力制御 SEM の手法は、試料をガス雰囲気中に置くことで、電子ビーム照射に起因した帯電を軽減しようとするものである。この方法は、電荷を中和することに関しては非常に期待が持てるけれども、今まではホトマスク計測あるいはウェーハ計測に本格的に用いられることがなかった。これは、この分野へのこの技術の新規な応用であり、"ホトマスクの検査、像形成、および計測を帯電無く行うこと"への大きな期待を抱かせる。この手法は、"ウェーハ計測にも同じ様に適用できる可能性"を持っている。圧力制御 SEM の手法は、正確な計測を行うために帯電をモデル化することの必要性を、全く無くすことはできないにしても、最小にする道を示してくれる。

リソグラフィ計測は、位置ズレや CD 計測のみならず、プロセス制御や、リソグラフィプロセスに必要な材料、例えば、フォトレジスト、位相シフター、反射防止膜等の性質の評価・解析も含まれる。こういったリソグラフィ材料は複雑になって来ており、こういった材料の性質の評価・解析は困難を増している。更に、ウェーハ製造プロセスで使用されるリソグラフィ以外の材料(ゲート酸化膜、金属、Lowk 絶縁膜、SOI 基盤)は間接的にリソグラフィ工程に影響を及ぼしている。というのは、これらの光学的特性は露光波長の光の反射率に影響を及ぼすからである。SOI ウェーハの埋め込み酸化膜のように、通常リソグラフィプロセスに重大な影響を及ぼすとは考えられない層であっても、そのプロセス条件の僅かな変動が、その層の光学的性質に影響を与える場合は、レジスト像の寸法や形状が変化することがありえる。

最低限のこととして、全ての層の露光波長における複素屈折率(屈折率 n と消衰係数 k)を知ることが必要である。このような特性の文献データは、通常、利用できない。すなわち、時代遅れで信頼できないもの(Kramers-Kronig 変換を用いて、材質が確かでない材料を時代遅れな反射率測定法で測定した結果から求められたもの)である。理想的な場合には、露光波長での分光エリプソメトリを用い、インラインで n と k を測定することができる。特に、193nm 以下の場合には測定が非常に難しく、通常は技術要員が工場外で測定する。EUV の光学的性質は、特別な光源(シンクロトロンのよう

な光源や EUV 露光装置のための EUV 光源)を用いてのみ求められることができる。したがって、実際上は光学的性質を直接測ることができない場合に、材料組成を指標として用いることがある。しかし、同じ組成の物質でも、異なる光学特性を示すことが有り得る(例として、非晶質 Si と結晶 Si の場合が挙げられる)。

表面粗さ、界面層、複屈折すなわち光学的異方性(フォトレジストあるいは他の有機層が応力を受けた時にしばしば観られる)、あるいは"組成が深さに依存して変わること"に起因して、光学的性質を求めることが複雑になる。ウェーハプロセスラインで使われる幾つかの材料では、楕円偏向角から光学定数を求めるという逆問題を完全には解けないので、材料の光学的性質を求められない。それゆえに、物理的な性質、材料の特性および光学定数が全て相互に関係していることから、光学的性質を求めるには材料の物理的評価・解析をしなければならない。

重ね合わせ精度の測定では、位相シフトマスク(PSM)および光学的近接効果補正マスクが課題であり、異なった層で、異なった露光装置あるいは、露光技術を用いることが困難さを増大させている。画像コントラストが低いことに起因した問題に加えて、今後重ね合わせ精度測定の要求が厳しくなると、走査プローブ顕微鏡(SPM)と共に、新しい光学的な方法あるいは SEM を用いた方法の開発が必要になるであろう。"従来のターゲット構造では検出できない位相シフトマスクや光学的近接効果補正マスクのアライメント誤差に係わる問題"を解決するための手段として、新しいターゲット構造の必要性が示唆された。オンチップ配線の重ね合わせは、引続いての課題である。平坦化のために化学的機械研磨法(CMP; chemical mechanical polishing)を用いることが、ターゲット構造を劣化させている。したがって、重ね合わせをより厳しく制御しようとする要求に応えるため、配線のアライメントターゲットはラインエッジをでこぼこにしている。絶縁体として使用される Lowk 材料は、特に多孔質の Lowk 材が製造に使われるようになると、重ね合わせを更に難しくする。

DRAMやNVMの先端デバイス適用においては、デバイスのハーフピッチの20%ないし25%という劇的に厳しい重ね合わせ基準の制御が必要であり、高加速 SEMやスキャトロメトリー技術のような代替計測技術による解決が早期に求められている。しかしながら、これらの技術は、現在成熟とは程遠い状況であり、計測技術の集約の中で解決が必要かもしれない。

EUVリソグラフィに導入には、EUVマスク計測とEUV空間像計測システム(EUV AIMS: EUV Aerial Image Measurement System)の領域でのさらなる開発進展が必要である。

リソグラフィ計測の要求テーブルは、ウェーハ計測要求(MET3)とマスク計測要求(MET4a, 4b)とに分けられている。マスク計測技術に関する要求テーブル(MET4a, 4b)は、更に、光露光、EUV 露光、そして電子線投影露光といった露光技術毎に分けられている。

#### TABLEMET3、MET4における不確かさの説明

に述べた不確かさの概念については、パターニングの計測の"精密さ"(precision)を考慮して以下に要約されている。 "精密さ"(precision)の定義は、その用途に強く依存する。用途と計測機器が与えられた場合、サンプリング方法を定義する必要がある。 "精密さ"(precision)の規格は、その用途、計測機器、サンプリング方法に照らして解釈がなされる。用途によって、"正確さ"(accuracy)、単一計測装置の"精密さ"(precision)、マッチングの要求値が定義されることになる。幾つかの用途においては、相対的な"正確さ"(accuracy)や、単一計測装置の"精密さ"(precision)が最優先される。また、ある用途においては、計測装置間のマッチングや単一計測装置の"精密さ"(precision)が最優先される。また他の用途においては、単一の計測結果だけでは必要とされる計測情報を提供するには不十分である。むしろ、複数の計測結果の平均は、計測として重要な意味を持つ。この場合、"精密さ"(precision)は、平均値の不確かさの要求値として解釈されるべきである。表中の"精密さ"(precision)の値は、不確かさの値として変更した。"精密さ"(precision)と"不確かさ"(uncertainty(の))の関係は式(1)に与えられている。

$$\frac{P}{T} = \frac{6 \cdot \sigma}{UL - LL}$$

1)

$$\sigma = \sqrt{\sigma_p^2 + \sigma_M^2 + \sigma_S^2 + \sigma_{other}^2}$$

2)

不確かさ ( $\sigma$ ) は次の成分を含んでいる :  $\sigma_P$  (Precision),  $\sigma_M$  (Matching),  $\sigma_S$  (Sampling) と  $\sigma_{other}$  (inaccuracy and other effects)。 それぞれの成分は、独立な正規分布であると仮定する。

Lithography Metrology (Wafer) Technology Requirements—Near-term Years Table MET3a

| DAM//-Pichem/(context)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Year of Production                                                                                                                       | 2007  | 2008  | 2009  | 2010  | 2011  | 2012  | 2013  | 2014  | 2015  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| #### #################################                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,                                                                                                                                        |       |       |       |       |       |       |       |       |       |

| Flesh   Fles | ( ) (                                                                                                                                    |       |       |       |       |       |       |       | -     |       |

| ### April                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                          |       |       |       |       |       |       |       | -     |       |

| Waitrocetay.orintol(mr)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 // 2/                                                                                                                                  |       |       |       |       |       |       |       |       |       |

| Water Orders youth threstology uncertainty (im) 3 of PT=1         11         1         0.9         0.8         0.71         0.64         0.57         0.51         0.45           Water Obmetokey to durectainty (im)*         0.40         0.36         0.32         0.28         0.26         0.22         0.20         0.18         0.16           Gae         Image: Committed and production of the interpretability of the interpretabilit                                                                                                                                                                                                                                                     | , , ,                                                                                                                                    |       |       | -     |       |       |       |       |       |       |

| Waifor Obmethology to characteristry (mm)*   0.40   0.36   0.32   0.28   0.26   0.22   0.20   0.18   0.16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | , , ,                                                                                                                                    |       |       |       |       |       | -     |       |       |       |

| OAU   0.36   0.32   0.28   0.28   0.22   0.21   0.18   0.16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 1 & 3( ) /                                                                                                                             | 1.1   | 1     | 0.9   | 8.0   | 0.71  | 0.64  | 0.57  | 0.51  | 0.45  |

| Printed gate CD control (mn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | WaferCDmetrology/tooluncertainty/(nm)* (P/T=2)forLWR**                                                                                   | 0.40  | 0.36  | 0.32  | 0.28  | 0.26  | 0.22  | 0.20  | 0.18  | 0.16  |

| Uniformity (variance) is 12% of CD Allowed lithography variance=34 total variance of physical gate length*  Wafer CD metrology tool uncertainty (nm)* 3 stat PT=02 for isolated printed and physical lines [A] Exhad Gate Line With Roughness (nm, 3 style="length: 150;"> 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Gate                                                                                                                                     |       |       |       |       |       |       |       |       |       |

| Display   Disp | Printed gate CD control (nm) Uniformity (variance) is 12% of CD Allowed lithography variance=3/4 total variance of physical gate length* | 2.6   | 23    | 2.1   | 1.9   | 1.7   | 1.5   | 1.4   | 1.2   | _1_   |

| Derse Line   Waferderse line CD control (mm)*   Uniformity is 135% of CD   S66   S53   4.7   3.7   3.7   3.3   2.6   2.6   2.4   2.4   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2.5   2 | WaferCDmetrology tool uncertainty (nm)*3\sigma at P/T=02 for isolated printed and physical lines [A]                                     | 0.52  | 0.46  | 0.42  | 0.37  | 0.33  | 0.29  | 0.27  | 0.23  | 0.21  |

| Waferdense line CD control (nm)*   Uniformity is 135% of CD   Allowed lithography variance = 3/4 total variance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Etched Gate Line Width Roughness (nm, 3 o) < 8% of CD**                                                                                  | 2     | 1.8   | 1.6   | 1.4   | 1.3   | 1.1   | 1     | 0.9   | 0.8   |

| Uniformity is 135% of CD Allowed lithography variance=34 total variance  Wafer CD metrology tool uncertainty (nm)* (PT=2 for dense lines**)  126 1.19 1.05 0.84 0.84 0.75 0.58 0.58 0.58 0.54  Contacts  Wafer minimum contact hole (nm, post etch) from lithography tables 64 57 51 45 40 36 32 28 25  Wafer contact CD control (nm)* Uniformity is 15% of CD = minimum contact hole size Allowed lithography variance=2/3 total variance  Wafer CD metrology tool uncertainty (nm)* (PT=2 for contacts)***  1.57 1.4 1.25 1.1 0.98 0.88 0.88 0.88 0.88 0.88 0.88 0.88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DenseLine                                                                                                                                |       |       |       |       |       |       |       |       |       |

| 1.19   1.05   0.84   0.84   0.75   0.58   0.58   0.54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | WaferdenselineCDcontrol(nm)* Uniformity is 13.5% of CD Allowed lithography variance=3/4 total variance                                   | 5.6   | 5.3   | 4.7   | 3.7   | 3.7   | 3.3   | 2.6   | 26    | 24    |

| Wafer minimum contact hole (nm. postech) from lithography tables         64         57         51         45         40         36         32         28         25           Wafer contact CD control (nm)* Uniformity is 15% of CD = minimum contact hole size Allowed lithography variance = 23 total variance         7.8         7         6.2         5.5         4.9         4.4         3.9         3.4         3.1           Wafer CD metrology tool uncertainty (nm)* (P/T=2 for contacts)****         1.57         1.4         1.25         1.1         0.98         0.88         0.88         0.88           Aspect Ratio Capability for Tiench Structure CD Metrology         15:01         15:01         15:01         15:01         15:01         15:01         15:01         20:01         20:01         20:01           Double Patterning Overlay Metrology ******         9:19         8.06         7.07         6.36         5.66         5.09         4.53         3.96         3.54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WaferCDmetrology tool uncertainty (nm)* (P/T=2 forderse lines**)                                                                         | 1.26  | 1.19  | 1.05  | 0.84  | 0.84  | 0.75  | 0.58  | 0.58  | 0.54  |

| Wafer contact CD control (nm)*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Contacts                                                                                                                                 |       |       |       |       |       |       |       |       |       |

| Uniformity is 15% of CD=minimum contact hole size         7.8         7         6.2         5.5         4.9         4.4         3.9         3.4         3.1           Allowed lifthography variance = 23 total variance         1.57         1.4         1.25         1.1         0.98         0.88         0.88         0.88           Wafer CD metrology tool uncertainty (nm)* (PT=2 for contacts)****         1.57         1.4         1.25         1.1         0.98         0.88         0.88         0.88           Aspect Ratio Capability for Tiench Structure CD Metrology         15:01         15:01         15:01         15:01         15:01         20:01         20:01         20:01           Double Patterning Overlay Metrology *****         9.19         8.06         7.07         6.36         5.66         5.09         4.53         3.96         3.54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Waferminimum contact hole (nm, postetch) from lithography tables                                                                         | 64    | 57    | 51    | 45    | 40    | 36    | 32    | 28    | 25    |