# INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTOR

2011 EDITION

SYSTEM DRIVERS

The ITRS is devised and intended for technology assessment only and is without regard to any commercial considerations pertaining to individual products or equipment.

## 訳者まえがき

この文書は International Technology Roadmap for Semiconductors 2011 Edition(国際半導体技術ロードマップ 2011 年版)本文の日本語訳である。

国際半導体技術ロードマップ(以下 ITRS と表記)は、米国、日本、欧州、韓国、台湾の世界5極の専門家によって編集・作成されている。日本では、半導体技術ロードマップ専門委員会(STRJ)が電子情報技術産業協会(JEITA)内に組織され、日本国内で半導体技術ロードマップについての調査活動を行うとともに、ITRSの編集・作成に貢献している。STRJ内には15のワーキンググループ(WG: Working Group)が組織され、半導体集積回路メーカ、半導体製造装置メーカ、材料メーカ、大学、独立行政法人、コンソーシアムなどから専門家が集まり、それぞれの専門分野の調査活動を行っている。

ITRS は改版を重ねるごとにページ数が増え、2011年版は英文で 1000 ページを越えるの文書となった。 このような大部の文書を原文で読み通すことは専門家でも多大な労力を要するし、専門家であっても技術分野が少し異なると ITRS を理解することは必ずしも容易でない。STRJ の専門委員がその専門分野に応じてITRS を訳出することで、ITRS をより親しみやすいものにすることができるのではないかと考えている。

なお、ITRS 2005 年版(英語の原書)までは、ウェブ公開とともに、印刷された本としても出版していたが、ITRS 2007 年版以降、は印刷コストが大きくなってきたこと、ウェブ上で無料公開されている文書の出版版を本の形で有償頒布しても需要が限られることなどのため、印刷物の形での出版を断念し、ウェブ公開のみとなった。ITRS の読者の皆様にはご不便をおかけするが、ご理解願いたい。ITRS 2009 年版以降、電子媒体でITRS を公開することを前提に編集を進め、ITRS の表は原則として、Microsoft Excel のファイルとして作成し、そのまま公開することにした。

ITRS は英語で書かれている。日本語訳の作成は、STRJ 委員が分担してこれにあたり、JEITA の STRJ 担当事務局が全体の取りまとめを行った。訳語については、できる限り統一するように努めたが、なお、統一が取れていないところもある。また、訳者によって、文体が異なるところもある。ITRS の原文自体も多くの専門家による分担執筆であり、そもそも原文の文体も一定していないことも、ご理解いただきたい。誤訳、誤字、脱字などが無いよう、細心の注意をしているが、短期間のうちに訳文を作成しているため、なお間違いが含まれていると思う。また、翻訳の過程で原文のニュアンスが変化してしまうこともある。訳文についてお気づきの点や、ITRS についてのご批判、ご意見などを事務局まで連絡いただけますよう、お願い申し上げます。

今回の訳出にあたっては、ITRS の本文の部分のみとし、ITRS 内の図や表の内部の英文は訳さないでそのまま掲載することとした。Executive Summary の冒頭の謝辞(Acknowledgments)に、ITRS の編集にかかわった方々の氏名が書かれているが、ここも訳出していない。

原文中の略語については、できるかぎり、初出の際に、「ITRS(International Technology Roadmap for Semiconductors)」のように()内に原義を示すようにした。英文の略号をそのまま使わないで技術用語を訳出する際、原語を引用したほうが適切と考えられる場合には、「国際半導体技術ロードマップ (ITRS: International Technology Roadmap for Semiconductors、以下 ITRSと表記)」「国際半導体技術ロードマップ (International Technology Roadmap for Semiconductors)」のように和訳の後に()内に原語やそれに対応する略語を表示した。Executive Summary の用語集(Glossary)も参照されたい。原文の括弧()があってそれを訳するために括弧を使った場合もあるが、前後の文脈の関係で判別できると思う。また訳注は「【訳者注:この部分は訳者の注釈であることを示す】」のように【】内に表記した。また[〕内の部分は、訳者が原文にない言葉をおぎなった部分であることを示している。訳文は厳密な逐語訳ではなく、日本語として読んで意味が通りやすいように意訳している。ITRSのウェブ版ではハイパーリンクが埋め込まれているが、今回の日本語版ではハイパーリンクは原則として削除した。読者の皆様には不便をおかけするが、ご理解いただけば幸いである。

今回の日本語訳全体の編集は全体のページ数が膨大であるため、大変な作業となってしまいました。編集作業を担当いただいた、JEITA内SRTJ事務局の進藤淳二さん、関口美奈さんに大変お世話になりました。厚くお礼申し上げます。

より多くの方にITRSをご活用いただきたいとの思いから、今回の翻訳作業を進めました。今後ともITRSと STRJへのご理解とご支援をよろしくお願い申し上げます。

> 2012年 5月 訳者一同を代表して

電子情報技術産業協会(JEITA)半導体部会 半導体技術ロードマップ専門委員会(STRJ) 委員長 石内 秀美 (株式会社 東芝)

# 版権について

# **ORIGINAL (ENGLISH VERSION) COPYRIGHT © 2011 SEMICONDUCTOR** INDUSTRY ASSOCIATION

#### All rights reserved

ITRS •SEMATECH, Inc., 257 Fuller Road, Albany, NY 12203 • http://www.itrs.net Japanese translation by the JEITA, Japan Electronics and Information Technology Industries Association under the license of the Semiconductor Industry Association

#### -引用する場合の注意-

原文(英語版)から引用する場合: ITRS 2011 Edition page XX, Figure(Table) YY この日本語訳から引用する場合: ITRS 2011 Edition (JEITA 訳) XX 頁.図(表)YY と明記してください。

#### 問合せ先:

一般社団法人 電子情報技術産業協会 半導体技術ロードマップ専門委員会 事務局

電話: 03-5218-1068 電子メール: roadmap@jeita.or.jp

#### TABLE OF CONTENTS

| 概要              |                                                            | 1  |

|-----------------|------------------------------------------------------------|----|

|                 | バ                                                          |    |

| システム・オン・チ       | ップ・ドライバ                                                    | 3  |

| ネットワークSOCド      | ライバ                                                        | 5  |

|                 | ₹                                                          |    |

|                 | べの設計生産性の動向                                                 |    |

|                 | 可けSOC (SOC-CP) ドライバ                                        |    |

|                 | h向けSOC(SOC-CS)ドライバ                                         |    |

|                 | MPU)ドライバ<br>ル・ドライバ                                         |    |

|                 | バ                                                          |    |

|                 | ロードマップに向けて;SOC-CPの消費電力試案                                   |    |

| LIST OF FIGURES | <b>S</b>                                                   |    |

| Figure SYSD1    | SOC Networking Driver Architecture Template                | 6  |

| Figure SYSD2    | SOC Networking Driver MC/AE Platform Performance           | 6  |

| Figure SYSD3    | Several Trends for SOC Consumer Portable Driver            | 8  |

| Figure SYSD4    | SOC Consumer Portable Driver Architecture Template         | 9  |

| Figure SYSD5    | SOC Consumer Portable Design Complexity Trends             | 9  |

| Figure SYSD6    | SOC Consumer Portable Power Consumption Trends             | 10 |

| Figure SYSD7    | SOC Consumer Portable Processing Performance Trends        | 11 |

| Figure SYSD8    | SOC Consumer Stationary Driver Architecture Template       | 12 |

| Figure SYSD9    | SOC Consumer Stationary Design Complexity Trends           | 13 |

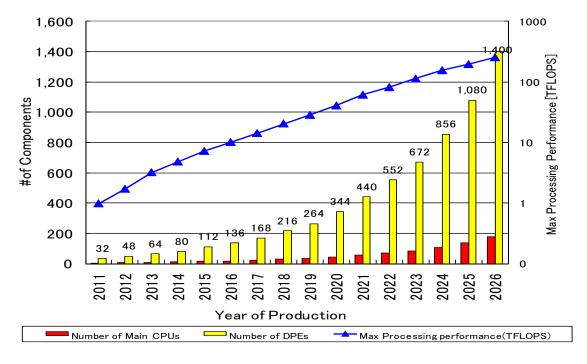

| Figure SYSD10   | SOC Consumer Stationary Performance Trends                 | 13 |

| Figure SYSD11   | SOC Consumer Stationary Power Consumption Trends           | 14 |

| Figure SYSD12   | VCO Performance for Mm-Wave Circuits                       | 24 |

| Figure SYSD13   | Recent ADC Performance Needs for Important Product Classes | 28 |

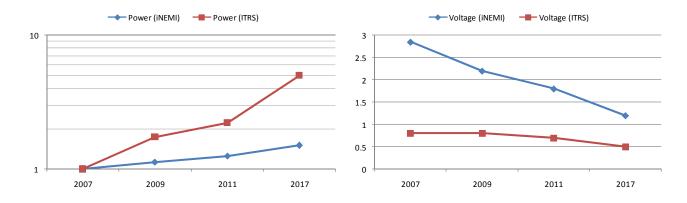

| Figure SYSD14   | ITRS-iNEMI System-to-Chip Power Comparison Trends          | 34 |

| LIST OF TABLES  |                                                            |    |

| Table SYSD 1    | Major Product Market Segments and Impact on System Drivers | 2  |

| Table SYSD 2    | SOC Consumer Driver Design Productivity Trends             | 7  |

| Table SYSD 3a E | Embedded Memory Requirements—Near-term                     | 31 |

| Table SYSD 3b E | Embedded Memory Requirements—Long-term                     | 32 |

### システム・ドライバ

#### 概要

将来の半導体の生産能力および設計技術は、世界の半導体産業を牽引するドライバ商品からの要求に応 じて開発されている。ITRS は、そのビジネスおよび機械設備の改善を行うサイクルが半導体領域をドライブす る製品分野のための技術的要求がどのように発生するかを把握する必要がある。かつては、技術進歩が一部 のキーとなる製品分野の詳細を含む、全ての半導体製品に対して展開されているという暗黙の仮定があった が、このような仮定はもはや成り立たない。今日、新しい技術導入はますます応用製品がドライブする傾向にあ る。 つまり、 アプリケーションが技術発展の動因となっている。 計算機用マイクロプロセサに加え、ミックスド・シ グナル・システム、電池駆動の携帯型機器、据置き型民生機器、そして通信機器もこのようなドライバとなって いる。組織内だけで行われてきたチップ設計は、マルチソースからのビルディングブロック方式の設計スタイル によるシステム・オン・チップ(SOC)やシステム・イン・パッケージ(SIP)の設計によって取って代わられている。

2011 年版ITRSシステムドライバ章の目的は、既存のITRSのシステムドライバを更新することと、新たなシス テムトライバを追加していき、ますます広がりをみせる半導体産業の趨勢をとらえることにある。総括ロードマッ プ技術指標(Overall Roadmap Technology Characteristics)と共に、システムドライバ章は、ITRSの各技術領域に おける技術的要求のための首尾一貫したフレームワークおよび動機づけを提供する。この章は、定量的で内 部に自己矛盾がなく、将来の技術進歩にも対応可能なシステムドライバのモデルから構成されている。私たち は次の4つのシステムドライバに注目する:システム・オン・チップ(これには頻出するシステム・イン・パッケー ジ技術への言及も含む)、マイクロプロセサ(MPU)、アナログ・ミックスド・シグナル(AMS)、および、混載メモリで ある。システム・オン・チップ・ドライバについては、以下の4つの重要な市場にもとづいて定義をおこなう: 民 生用据置き機器、民生用携帯機器、通信機器。はじめに、半導体製品の主要なマーケット・ドライバについて 概観する。読者はInternational Electronics Manufacturing (iNEMI) roadmap ( http://www.inemi.org) も参照い ただきたい。

#### マーケット・ドライバ

Table SYSD1 では、製造規模、ダイサイズ、異種技術集積の度合い、システムの複雑さ、タイム・トゥ・マーケ ットのような要因によって半導体製品市場を対比している。この表で、各分野におけるSOC、AMS、MPUへの 影響が示されている。

<sup>1</sup> マーケット・ドライバは、コスト、タイム・トゥ・マーケット、生産量により極めて明確に区分されている。システムコストは製造 原価+デザインコストである。製造原価はさらに再生しないエンジニアリング(non-recurring engineering (NRE))コスト(マス ク、設備など)とシリコンコスト(未処理のウエハ+処理+テスト)に分割される。 全体のシステムは機能やI/Oの数やパッケー ジコスト、電力やスピードに依存する。種々の領域の要求(生産量、タイム等マーケット、システム複雑さ)はFPGA. Structured-ASIC, SOC implementation fabricsによって提供され、シングルダイやシステム・イン・パッケージなどで提供さ れる。この分割については絶えず進化している。

Table SYSD 1 Major Product Market Segments and Impact on System Drivers

| Market Drivers                       | SOC                                  | Analog/MS                          | MPU                            |

|--------------------------------------|--------------------------------------|------------------------------------|--------------------------------|

| I. Portable/consumer                 |                                      |                                    |                                |

| 1. Size/weight ratio: peak in 2004   | Low power paramount                  | Migrating on-chip for voice        | Specialized cores to optimize  |

| 2. Battery life                      |                                      | processing, A/D sampling, and even | processing per microwatt       |

| 3. Function: 2×/2 years              | Need SOC integration (DSP, MPU,      | for some RF transceiver function   |                                |

| 4. Time-to-market: ASAP              | I/O cores, etc.)                     |                                    |                                |

| II. Medical                          |                                      |                                    |                                |

| Cost: slight downward pressure       | High-end products only.              | Absolutely necessary for physical  | Often used for programmability |

| (~1/2 every 5 years)                 | Reprogrammability possible. Mainly   | measurement and response but may   | especially when real-time      |

| 2. Time-to-market: >12 months        | ASSP, especially for patient data    | not be integrated on chip          | performance is not important   |

| 3. Function: new on-chip functions   | storage and telemedicine; more SOC   |                                    |                                |

| 4. Form factor often not important   | for high-end digital with cores for  |                                    | Recent advances in multicore   |

| 5. Durability/safety                 | imaging, real-time diagnostics, etc. |                                    | processors have made           |

| 6. Conservation/ ecology             |                                      |                                    | programmability and real-time  |

|                                      |                                      |                                    | performance possible           |

| III. Networking and communications   | ,                                    | '                                  | 1                              |

| 1. Bandwidth: 4×/3–4 years           | Large gate counts                    | Migrating on-chip for MUX/DEMUX    | MPU cores, FPGA cores and some |

| 2. Reliability                       | High reliability                     | circuitry                          | specialized functions          |

| 3. Time-to-market: ASAP              | More reprogrammability to            |                                    |                                |

| 4. Power: W/m <sup>3</sup> of system | accommodate custom functions         | MEMS for optical switching.        |                                |

Table SYSD1 Major Product Market Segments and Impact on System Drivers (continued)

| IV. Defense                         |                                        |                                       |                                    |

|-------------------------------------|----------------------------------------|---------------------------------------|------------------------------------|

| 1. Cost: not prime concern          | Most case leverage existing processors | Absolutely necessary for physical     | Often used for programmability     |

| 2. Time-to-market: >12 months       | but some requirements may drive        | measurement and response but may      | especially when real-time          |

| 3. Function: mostly on SW to ride   | towards single-chip designs with       | not be integrated on chip             | performance is not important       |

| technology curve                    | programmability                        |                                       |                                    |

| 4. Form factor may be important     |                                        |                                       | Recent advances in multicore       |

| 5. High durability/safety           |                                        |                                       | processors have made               |

|                                     |                                        |                                       | programmability and real-time      |

|                                     |                                        |                                       | performance possible               |

| V. Office                           | •                                      |                                       |                                    |

| 1. Speed: 2×/2 years                | Large gate counts; high speed          | Minimal on-chip analog; simple A/D    | MPU cores and some specialized     |

| 2. Memory density: 2×/2 years       |                                        | and D/A                               | functions                          |

| 3. Power: flat to decreasing,       | Drives demand for digital              |                                       |                                    |

| driven by cost and W/m <sup>3</sup> | functionality                          | Video i/f for automated camera        | Increased industry partnerships on |

| 4. Form factor: shrinking size      |                                        | monitoring, video conferencing        | common designs to reduce           |

| 5. Reliability                      | Primarily SOC integration of custom    |                                       | development costs (requires data   |

|                                     | off-the-shelf MPU and I/O cores        | Integrated high-speed A/D, D/A for    | sharing and reuse across multiple  |

|                                     |                                        | monitoring, instrumentation, and      | design systems)                    |

|                                     |                                        | range-speed-position resolution       |                                    |

| VI. Automotive                      |                                        |                                       |                                    |

| 1. Functionality                    | Mainly entertainment systems           | Cost-driven on-chip A/D and D/A for   |                                    |

| 2. Ruggedness (external             |                                        | sensor and actuators                  |                                    |

| environment, noise)                 | Mainly ASSP, but increasing SOC for    |                                       |                                    |

| 3. Reliability and safety           | high end using standard HW             | Signal processing shifting to DSP for |                                    |

| 4. Cost                             | platforms with RTOS kernel,            | voice, visual                         |                                    |

|                                     | embedded software                      |                                       |                                    |

|                                     |                                        | Physical measurement                  |                                    |

|                                     |                                        | ("communicating sensors" for          |                                    |

|                                     |                                        | proximity, motion, positioning);      |                                    |

|                                     |                                        | MEMS for sensors                      |                                    |

A/D—analog to digital ASSP—application-specific standard product D/A—digital to analog DEMUX—demultiplexer DSP—digital signal processing FPGA—field programmable gate array i/f—interface I/O—input/output HW—hardware MEMS—microelectromechanical systems MUX—multiplexer *RTOS*—real-time operating system

#### システム・オン・チップ・ドライバ

SOCは製品分野であり、他のシステムドライバ分野(MPU、混載メモリ、AMS、そして、プログラマブル・ロジッ ク)からの技術や設計要素を統合した設計スタイルであり、さまざまな高度に複雑で高付加価値の半導体製品 を生み出している。SOCの生産および設計技術は、一般的に出荷量の多い専用製品向けとして元々開発され たものである。SOCドライバは以前の版のITRSで取り上げていたASICから発展したものであり、低設計コストお よび高レベルのシステム・インテグレーションがその主要なゴールである<sup>2</sup>。SOC設計では、そのゴールは既存

<sup>2 &</sup>quot;ASIC"はビジネスモデル (特定の「ハンドオフ」を伴いデザインチームから ASIC 製造工場まで)と設計手法(チップデ ザイナーが主に機能的なレベルで、 Verilog / VHDL (非常に高速の集積回路ハードウェア記述言語)あるいはさらに抽 象度の高い記述言語を用いて設計し、スタンダードセルを用いた自動論理合成と配置配線を実行する)の両方を意味す る。経済的理由で、カスタム機能はめったに作られない;デザインコストとデザインリスクを減らすことが重要である。ASIC

ブロックあるいは「コア」の再利用率を最大にするということであり、新規に設計されるチップの量を最小限にすることである。SOC中の再利用されるブロックは、アナログおよび既に量産されている専用コアばかりではなく、ソフトウエア・ブロックも含んでいる。そのキー・チャレンジは、再利用可能なブロックあるいはコアを企画、作成しメンテナンスし、SOC設計者が利用できるようにすることである<sup>3</sup>。

SOCは、いくつかの意味でこれまでの製品分野を統合したものといえる。上に述べたように、SOCは他のシステムドライバ分野からのブロックを集積したものである。フルカスタムおよびASIC/SOC間の品質ギャップは着実に低減してきた。すなわち、(1) 2001 年版ITRS以降、ASICおよびMPUのロジック密度は等しいとしてモデル化された。(2)そして、「ASICのスケジュールでカスタム設計並みの性能」は進歩した物理合成とチューニングベースのスタンダードセル設計手法によってどんどん達成されてきている。そして、MPUはSOCになってきている。すなわち、(1) MPUはますます、SOCに使われるコアとして設計されるようになっている。(2)その再利用性と設計生産性を改善するためにMPUそれ自身もSOCとして設計されている(後で議論されるようにITRSのMPUモデルは複数の演算処理コアを持っており、構成はSOCに似ているが、加えて言えば、いくつかの市場分野、とりわけ通信機器やゲーム機器といった分野では、性能仕様がますます高水準になっている。ときには、要求性能指標一例えばダイあたりの毎秒の浮動小数点演算数とかダイあたりの入出力バンド幅一がMPUなど既存のドライバのそれを超えることすらある。このような仕様が存在している状況で、主たる設計要求や解決策に対するドライバとなったのは、先述の機器の分野におけるSOC設計である。重要な指標一ダイあたりのコア数、コアあたりの最大周波数、ピンあたりの入出力バンド幅など一の伸びは、ますますこれらのドライバがリードするようになっている。

先に述べたとおり、最も基本的な SOC の挑戦はインプリメンテーションの生産性および製造原価である。そ れはプラットフォームに基づいた設計、シリコン・インプリメンテーションの規則性あるいは他の斬新な回路およ びシステム・アーキテクチャ・パラダイムばかりではなく、より大規模な再利用も必要とする。 第二の基本的な挑 戦は、多数のインプリメンテーション*要素*(たとえば、リプログラマブル・ロジック、メモリ、アナログ、無線周波 (RF)、MEMS、ソフトウェア)からの異種なコンポーネントのインテグレーションである。SOC ドライバ分野は、設 計生産性を改善する知的資産(IP)の多くの再利用と、低コストと高集積のための異種技術のシステム・インテグ レーションとによって特徴づけられる。コスト的要因は、ローパワー・プロセスとローコスト・パッケージング・ソリュ ーション、およびターンアラウンドタイムの短い設計方法論の採用を促す。後者の結果として、IP 記述、IP テス ト(内蔵自己テスト(BIST)および自己修復を含む)、ブロック・インタフェース合成等の新しい規格および方法論 が必要となる。集積化の側面は、チップとパッケージの同時最適化の必要性のみならず、特定のシステム・コン ポーネント(メモリ、センサ等)を実現させる多種多様の技術(フラッシュ、DRAM、アナログ、RF、MEMS、強誘 電体RAM (FeRAM)、磁気抵抗RAM (MRAM)、化学センサ等)への要求を加速させる。このように、SOCは同 ーシステム・パッケージだけでなく、同一製造プロセス上で複数の技術の集積を促すドライバである。本章は、 いくつかの形態に関してSOCの性質および発展を議論するものである。各形態をドライブするのは、複合技術 集積(multi-technology integration、MT)、高性能(HP) 一特に(a) 通信機器と(b)民生用据置き機器―、およ びローパワー・低コスト(LP) 一特に民生用携帯機器一である。

#### SOC/SIP 複合技術

異種システムを単一チップ上に構築する必要性は、構造的な要因や、コネクションの負荷とスピードの関係、

設計は比較的保守的な設計手法と設計ゴールに特徴を持つが(前回の版のITRSでのMPUとASICの間のクロック周期とレイアウト密度の相違、参照)、しかしスケーリング技術に移行してからの積極的な技術の使用は設計リスクほとんどなしでよりよい結果を生み出す安価な方法である(前回の版のITRSでのMPUとASICの集合、参照)。1990年代の後半から、ASIC はその内容、プロセス技術、デザイン手法に関して SOC と共通化してきた。

<sup>&</sup>lt;sup>3</sup> 例えば、再利用可能なコアは、通常指定されないノイズや電力の特質("フィールドオブユース"や"設計における仮定")について、特徴を明らかにすることが要求されるかも知れない。他の人に再利用させるICデザインの創出は、1回限りの使用目的のそれと比べていっそう困難(推定で2倍から5倍)である。

<sup>4</sup> 類似のASICとストラクチャド・カスタム・MPUの設計手法もまた共通の階層ASIC/SOC設計手法として一本化される。これは ASIC 側で、顧客所有のツールで工夫されるビジネスモデルによって、そして両方の手法が直面するツール限界によって速められる。

或いは信頼性等のコスト意識によってもたらされる。そのためプロセス技術者は、MEMS やその他のセンサと CMOS の融合を模索して来た。単一チップ上に複数の技術を集積することは、より複雑なプロセスを要求し、この複雑度が複合技術 SOC の主なコスト要因と成る。将来の新材料やプロセスの複合に関して、総合的なコスト予測をすることは困難である。しかしながら、コスト制約によってある SOC に集積できる技術の数は制限される。標準低消費電力ロジックプロセスにフラッシュメモリが混載されるように、プロセスのモジュール化が進んだとしても、一般的にはモジュールは"積重ね"可能ではない。他の技術と集積する必然性や大量生産の必然性が無くとも、標準 CMOS プロセスと各々の技術を集積することには、今後も発展する可能性が有るであろう。最近の(電気・光、電気・生物)技術と CMOS の集積は、単に技術的優位性だけではなく、複数チップによるシステム・イン・パッケージの代案よりもコスト効率が優位でなければならない。今日、幾つかの技術(MEMS、GaAs)では、各々の製品(Flash や DRAM)の面積やピン数の制約に依存して、同一モジュール内でフリップして重ね合わせるか、シリコン上に隣り合わせに集積することでコスト効率が向上出来ている。特にセンサの単一ダイへの集積の必要性は、システムの物理的大きさ(耳と口:例えば自動車内でのスピーカとマイクの分離)等に影響されている。

#### ネットワーク SOC ドライバ

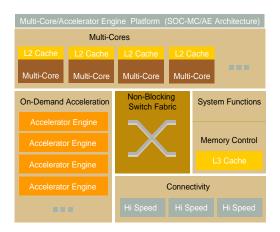

ハイパフォーマンス SOC の例としては、ハイエンド・ゲーム用プロセサ(以下の民生用据置き機器向け SOC(SOC-CS)ドライバ)やネットワーク機器が挙げられる。高速通信用 SOC は、チップ外への入出力信号に対する要求を生み出す(それはテストやアセンブリ、パッケージング、設計への重要なチャレンジを生み出す)。歴史的に見ても、チップの入出力速度(ピン当たりのバンド幅)は、チップ内部のクロック周波数に比べ、スケーリングが遅れて来た。この十年では、長距離通信用に開発された高速リンク技術が、他の応用にも適用されて来た。この高速入出力は、基板の信号安定化時間の問題を、1対1接続と配線を伝送線路として扱うことで回避して来た。今日では、これら最新技術のシリアル・リンクで10Gbit/秒、さらには40Gbit/秒から100Gbit/秒の動作へと進化している。将来のネットワークは、贅沢なマルチメディアコンテンツを配信し、進化した IP ベースのアプリケーションやサービス(家庭内ネットワークと境目無く移動しながら楽しむ)をサポートするスケーラブルで電力制約を満たし、コスト有利なSOCを要求する。メモリやI/Oのアクセス遅延とコアスピードの根本的な差異から、ネットワーク SOC のアーキテクチャはスイッチ機構や L3 キャッシュを内蔵し、必要に応じて専用エンジンを持つマルチコア構成に向かっている。ここで私たちは、ネットワーク機構を内蔵するマルチコア SOC アーキテクチャとして、ネットワーク SOCドライバを定義する事としたい。

シングルコアアーキテクチャでの動作周波数向上では、これ以上ネットワークで必要な性能の達成が望めないため、ネットワーク SOC では更なる性能向上を図るためマルチコア・アーキテクチャが用いられる。それでも、放熱問題と組込み用途での厳しい電力制約(例えば 20W 或いは 40W)から、マルチコア化だけで必要な性能向上を達成できるわけではない。従って、専用エンジンやチップ内のスイッチ機構、オンボードキャッシュメモリの階層化を実装する事も、漸進的な性能向上の実現に応用される。これらの進展はデザイン等価スケーリングの例である(定義についてエグセクティブ・サマリーを参照)。SOC プラットフォームの観点からは、シリコンでの達成可能な性能・電力限界を拡張する挑戦は、メモリと内部バスバンド幅の競合や、スケーラビリティの問題、プログラムの見通しの悪さから生じる非実行サイクルの問題を包含する。ハードウェア自体の能力を引出すには、更なる投資として、ソフトウェアを用意し且つそれをシミュレーションする環境を準備する必要がある。これが Figure SYSD1 に示したネットワーク SOCドライバのアーキテクチャの動機で、それはマルチコアと専用エンジン(MC/AE)から成り、ネットワーク機構を必要とする。

この MC/AE アーキテクチャは、単に高性能化や電力高効率化をもたらすだけではなく、エコシステムを可能にする相補的なソフトウェアへの明確な投資を通して、製造業のマルチコアプロセサ化への遷移を容易にする。

Figure SYSD1 SOC Networking Driver Architecture Template

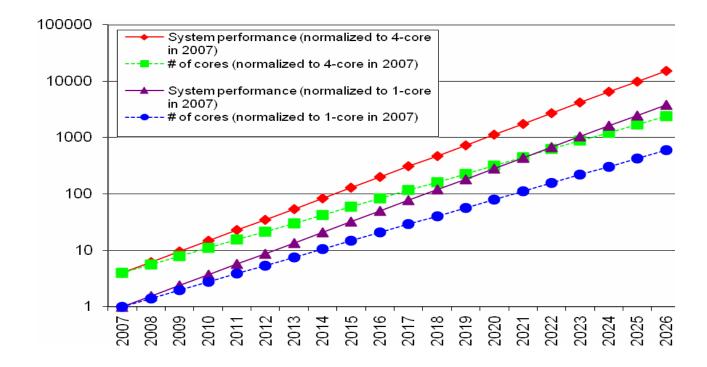

Figure SYSD2 はネットワーク SOC ドライバの期待される性能向上とコアの数を示しており、合計 30W と仮定した電力で中規模のスイッチング/ルーティングを行う組込みネットワーク機構を想定している。モデルは以下の仮定を含んでいる。

- ダイサイズは一定。

- コアの数は年率 1.4 倍で増加する。

- コアの動作周波数は年率 1.05 倍で上昇する。

- ・ 専用エンジンの動作周波数は年率 1.05 倍で上昇する。

- ・ ロジックやメモリ(階層キャッシュ)、チップ内スイッチ機構、システム間結合の構造はコア数を増加させて も矛盾無くスケーリングする。

図はシステム性能が 1000 倍に向上する所を示しており、コアの数と動作周波数、専用エンジンの周波数の掛算になっている。このシナリオによると、2009年の45nmで8コア実装を行ったシステムの性能を基準として、予想した22nmでのシステム性能は(80コアで)20倍超になる。

Figure SYSD2 SOC Networking Driver MC/AE Platform Performance

#### 民生用 SOC ドライバ

民生用 SOC ドライバは、民生用電子機器の広い多様性を反映した典型的な SOC の分野を包含する。民生 製品における短い製品寿命や機能と性能への急速な成長要求から、民生用 SOC ドライバの要件は高い性能 と機能、短時間での商品化が鍵となる。民生用SOCドライバは二種類に分類され、携帯電話を典型例とする民 生用携帯機器と高性能ゲーム機を典型例とする民生用据置き機器がある。二つのカテゴリは主に消費電力の 要求で区別され、民生用携帯機器ドライバは機器のバッテリーを持たせるために消費電力を最小化する必要 があり、一方民生用据置き機器ドライバは高性能であることが重要な特徴である。

#### 民生用 SOC ドライバの設計生産性の動向

Table SYSD2 は民生用携帯機器向け SOC、民生用据置き機器向け SOC 両ドライバの設計生産性の動向を 示している。基になるモデルは以下の仮定を行っている。必要な設計労力は一定であることを仮定する。設計 労力はロジック回路の規模に比例すると仮定する。ロジック回路の再利用設計労力は同規模の新規ロジック設 計に必要な労力の半分と仮定する、これは再利用に労力が掛からない訳ではなく、機能修正や実装、最終的 な物理検証の労力が必要であるからである。メモリや純粋なアナログ回路のような非ロジック回路に関しては、 再利用設計労力は掛からない。再利用の比率は、2011年を54%、2026年を98%として線形に補間して決めて いる。これらの仮定の下に SOC 設計労力を一定に保てば、2019 年までの 10 年間で新規ロジック設計の生産 性を 10 倍に改善する必要がある事になる。この生産性への挑戦には、幾つかの手法を混合する必要がある。 第一に設計の抽象度を高める必要がある。第二に、設計の検証と実装の自動化の度合いを増加させる必要が ある。最後は、設計再利用に掛かるオーバヘッドの労力を削減しつつ、再利用の比率を高める必要がある。

| Years                                                                                         | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 | 2021  | 2022  | 2023  | 2024  | 2025  | 2026  |

|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|-------|-------|-------|-------|-------|-------|

| SoC-CP Total Logic Size                                                                       | 1.00 | 1.32 | 1.79 | 2.32 | 2.96 | 3.77 | 4.70 | 5.85 | 7.45 | 9.70 | 11.65 | 15.50 | 19.56 | 24.40 | 31.23 | 38.10 |

| Required % of reused design                                                                   | 54%  | 58%  | 62%  | 66%  | 70%  | 74%  | 78%  | 82%  | 86%  | 90%  | 92%   | 94%   | 95%   | 96%   | 97%   | 98%   |

| Required Productivity for new designs (Normalized to 2011)                                    | 1.00 | 1.22 | 1.60 | 2.02 | 2.50 | 3.08 | 3.72 | 4.48 | 5.51 | 6.93 | 8.17  | 10.67 | 13.34 | 16.48 | 20.89 | 16.48 |

| Required Productivity for reused designs (Normalized to productivity for new designs at 2011) | 1.00 | 1.22 | 1.60 | 2.02 | 2.50 | 3.08 | 3.72 | 4.48 | 5.51 | 6.93 | 8.17  | 10.67 | 13.34 | 16.48 | 20.89 | 25.24 |

Table SYSD 2 SOC Consumer Driver Design Productivity Trends

#### 民生用携帯機器向け SOC (SOC-CP) ドライバ

(前回の版の ITRS で、「電力効率」のための SOC-PE として知られている) SOC 民生用携帯機器 (SOC-CP)ドライバはますます SOC の進展を象徴している。それは高性能コンピュータや企業向けアプリ ケーションのような他の処理目的のチップだけでなく、スマートメディアフォン、タブレット、デジタルカメラの ようなポータブルやワイヤレスのアプリケーションにまで及ぶ。SOC-CP ドライバは Japan Semiconductor Technology Roadmap Design Working Group によって作成されたモデルに基づいている。

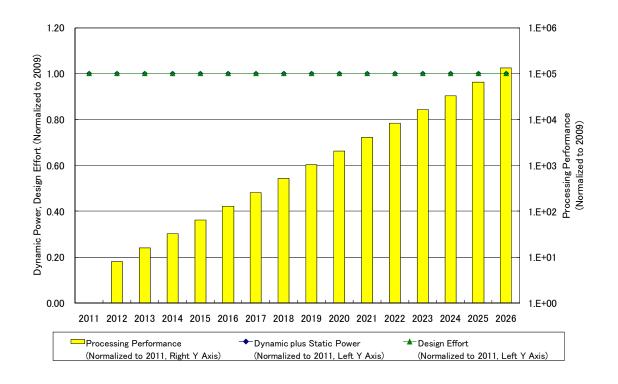

Figure SYSD3 は、一般消費者に扱われるおそらくマルチメディアを処理する能力を持ったワイヤレスデ バイスの電力効率の必須な特質を表している。

- 典型的なアプリケーションエリアは"ポータブル/モバイル民生機器プラットフォーム"に分類される電 子機器である。このアプリケーションエリアが近い将来において半導体のどの技術世代でも、急速に 発展するであろう。

- この種の SOC "ポータブル/モバイル民生機器プラットフォーム"の典型的な要求項目はバッテリー 寿命を維持する電力制約を上限とするにもかかわらず、処理能力の急速な増加を余儀なくされるこ とにある。 ダイナミックな電力消費量は際立って変化しないにもかかわらず、処理能力は今後 10 年 間で1000倍に増加する。

- "ポータブル/モバイル民生機器プラットフォーム"製品の寿命は短く、今後においても短いままだろう。 したがって、設計効率の向上は難しく、近い将来に関しては現在のレベルに留めなくてはならない。

Figure SYSD3 Several Trends for SOC Consumer Portable Driver

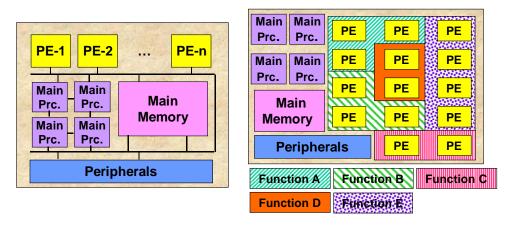

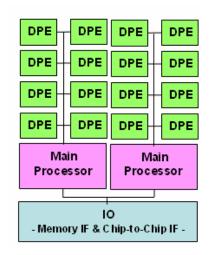

Figure SYSD4 に SOC 民生用携帯機器ドライバのためのアーキテクチャテンプレートを示す。 SOC はメインプロセサ、複数の PE (処理エンジン)、周辺機能、メモリで構成される高度に並列化されたアーキテクチャを持つ。 ここでいう、PE は特定の機能のためにカスタマイズされたプロセサである。 大規模で、非常に複雑な構造を持つ機能は、PE のセットとして実装されるであろう。 このアーキテクチャテンプレートは並列処理と特定機能をもったハードウェアの実現によって、高い処理パフォーマンスと低消費電力の両立を可能にする。提示されたアーキテクチャは、特別なプロセサ配列構造や対称プロセサを必要としない。その本質的な特徴は必要とされる機能を実装するために SOC 内に多数の PE を埋め込んだことである。

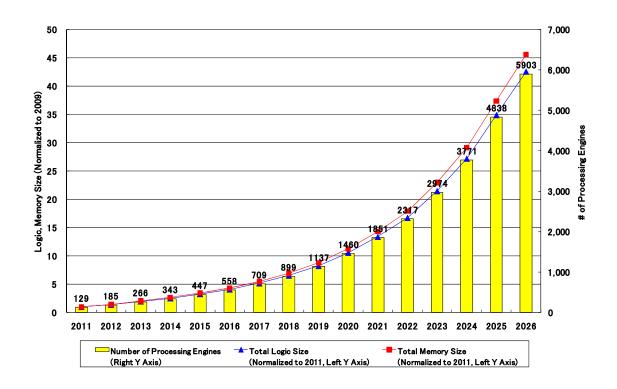

このアーキテクチャテンプレートに基づいて、SOC 民生用携帯機器ドライバの定量化された設計の複雑さの動向を Figure SYSD5 に示す。基礎となるモデルの仮定は次の通りである。1) およそ一定の複雑さを持った 2~4 個のメインプロセサがあり、将来その数は引き続き増加するだろう。2) 周辺機能も同じく一定の複雑さを持続するだろう。3) PE に関しては、回路の複雑さの平均は一定で保たれ、かつ PE の数は、49mm2 から 44mm2 付近に次第に減少するダイサイズを限度としながら、増え続けるだろう。 それ故、PE の数は今後急速に増大する。4) メインメモリの容量は、PE の数に比例して増加するだろう。

Figure SYSD4 SOC Consumer Portable Driver Architecture Template

Figure SYSD5 SOC Consumer Portable Design Complexity Trends

#### 民生用携帯機器向けSOC の消費電力の動向

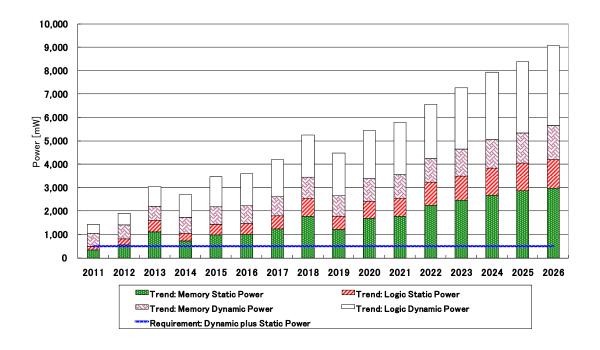

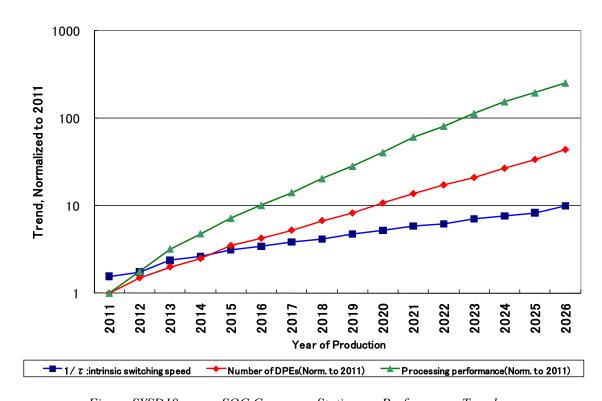

設計の複雑さが重要な動向である一方で、消費電力もまた、民生用携帯機器向け SOC チップの設計に対して重大な要素と言える。Figure SYSD6 は、PID 章の LOP トランジスタ性能パラメータと、配線章の "Interconnect Technology Requirements"のインターコネクト性能パラメータと、Table SYSD2 にある回路の複雑性パラメータを使用し、総合的なチップ消費電力の動向を表している。我々は次のことに気付く。

- ・ ここで適用されるモデルは、単純に現在の最高水準の技術と ITRS 内のコンポーネント技術のロードマップから推定している。この結果の消費電力は、2011 の PIDS 章の電源電圧が長期年次で、2009 の LOP デバイスの電源電圧に戻ったにもかかわらず、電力効率の要求水準をかなり上回る。我々は、競争的な民生用携帯機器における電力効率の要求や、世界的なより"green"で、エネルギー効率がいい電子機器への要請が、将来の ITRS の電力考慮のデバイスのロードマップ作成を牽引することを期待する。

- ・ 可能性のある解決策は、デザイン章の中で議論される。SOC 民生用携帯機器の具体的な解決策は、設

計の高位段階における消費電力解析に基づくアーキテクチャ最適化や、カスタマイズされた PE の実現を含んでいる。

- 0.5W というトータル消費電力の要求値は ITRS2009 で記載された。ただし、例外が存在することを示しておく。例えば、最新のタブレット製品の中の民生機器向けのプロセッサは物理的な製品の特性や進んだパワーマネージメント技術により、2W まで電力消費が可能である。

- ・ 供給電圧が、将来不連続に推移するため、論理回路のスイッチング(すなわち、ダイナミック)電力とメモリのスタティック電力は、2013 年から 2014 年、2018 年から 2019 年、2020 年から 2021 年に単調でない動きをする。

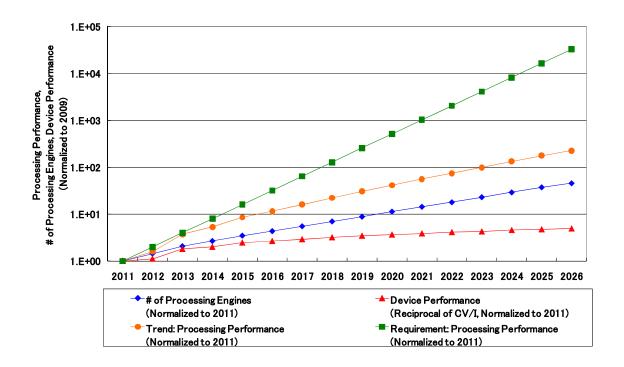

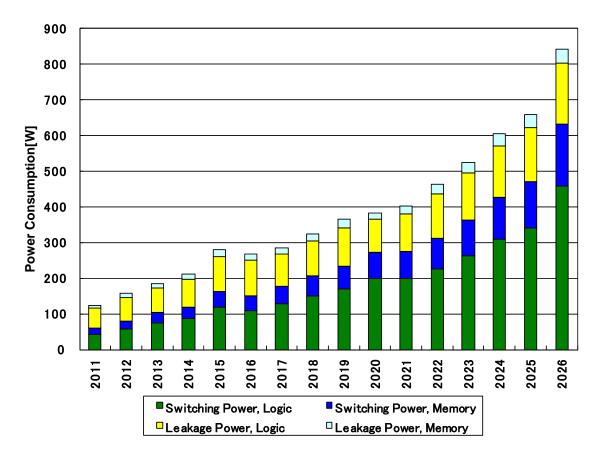

#### 民生用携帯機器向けSOC の処理性能の動向

民生用携帯機器向けSOCドライバの処理能力は、SOC上のPEの数とデバイスの性能の積に比例すると推測される。Figure SYSD7は、処理能力に対する要求と実現可能な処理能力との線形の傾向を超えて拡大するギャップが残ったままであることを示す。このギャップは、電力と設計に制約を受けるPEの数を増やすことによって、潜在的に解決される。

可能性のある解決策は、デザイン章の中で議論される。高位設計段階での最適なハードウェアとソフトウェア分割が含まれており、ハイレベルデザインのステージからインプリメンテーションのステージへの自動化されたインタフェース技術(例えば、高位合成)も同様に含まれている。

Figure SYSD6 SOC Consumer Portable Power Consumption Trends

Figure SYSD7 SOC Consumer Portable Processing Performance Trends

#### 民生用据置き機器向け SOC (SOC-CS) ドライバ

民生用据置き機器向け SOC (SOC-CS) ドライバの節では、ハイエンド・ゲームなど、通常は携帯用途では なく、AC 電源線に接続されて使われるような幅広い民生用デジタル機器に使用されるような SOC の設計につ いて説明する。この SOC モデルの主たる特徴は以下である。

- 処理能力が最も重要な差別化要因である。Figure SYSD9に示すように、2022年に必要とされる処理能 力は 70TFlops を超える。

- 機能は主としてソフトウェアにより実現され実行される。したがって、高い処理能力が要求され、SOC は 多数のデータ処理エンジン(DPE: Data Processing Engine)から成るようになる。

- 民生用携帯機器向け SOC ドライバと比較して、このドライバの電力対性能比は良くないが、機能を追加 したり、機能を改善したりといった柔軟性に優れている。

- 機能を追加したり、機能を改善したりといったことが容易なため、民生用据置き機器向け SOC の種類の 設計物のライフサイクルは比較的長く、またその結果、応用分野が広い。

Figure SYSD8には、民生用据置き機器向け SOCドライバの典型的なアーキテクチャの雛形を示す。この SOC は、多くのメインプロセサ、多くのデータ処理エンジン(DPE)、メモリやチップ・チップのインタフェースのための I/Oから成る高度な並列アーキテクチャを特徴とする。ここで、データ処理エンジン DPE は、データ処理に特化 したプロセサであり、汎用的な目的のための機能を取り除くことによって高い処理能力を達成している。メイン プロセサは、汎用プロセサであり、データ処理エンジン DPE に対して作業の割り振りをしたり処理をスケジュー ルしたりする。1つのメインプロセサといくつかのデータ処理エンジン DPE とが一緒になって、基本的なアーキ テクチャを構成する。データ処理エンジン DPE の個数は、必要とされる処理能力とチップサイズから決まる。目 標とする要求性能を達成するために、この章においてモデルとして記載される全ての SOC の中で、SOC-PEド ライバが最も多くのデータ処理エンジン DPE を有する可能性がある。

Figure SYSD8

SOC Consumer Stationary Driver Architecture Template

#### 民生用据置き機器向けSOC の設計複雑さの動向

SOC-CS のアーキテクチャの雛形に基づいて、定量的に設計複雑度の動向を示したものが Figure SYSD9 である。最も興味深い動向が、データ処理エンジン DPE の数の急激な増加である。モデルにおける基本的な仮定は以下のようなものである。

- ・ SOCのチップサイズは、最近のゲーム向けプロセサの製品として発表されている数値から、220mm<sup>2</sup>で 一定である。

- ・ メインプロセサとデータ処理エンジンDPEの両方について、回路の複雑度は一定である。このことにより、 各々のレイアウト面積は、M1 ピッチの平方に比例して縮小する。

- ・ メインプロセサは、最大で8つまでのデータ処理エンジンDPEを制御できると仮定する。

#### 民生用据置き機器向けSOC の処理性能の動向

民生用据置き機器向け SOC ドライバの処理性能は、デバイスの性能と SOC 上の DPE の数の積に比例すると想定することができる。民生用据置き機器向け SOC の処理能力の動向を Figure SYSD10 に示す。要求される処理能力は、今後 15 年で約 250 倍の急激な増加をする。このような性能要求を達成する主要な解決策には、種々の設計技術(特に、論理設計、回路設計、物理設計の段階の設計技術)を使って回路の性能を最大化することが含まれる。もちろん、高位合成といった自動化の手法も重要である。

Figure SYSD9 SOC Consumer Stationary Design Complexity Trends

SOC Consumer Stationary Performance Trends Figure SYSD10

#### 民生用据置き機器向けSOC の消費電力の動向

消費電力の爆発が、将来の民生用据置き機器向け SOC の LSI チップの設計において、最も深刻に考慮さ れるべきものとなるであろう。Figure SYSD11は、チップの消費電力をロジック部分とメモリ部分について、スイッ チング電力とリーク電力に分けて、動向を示したものである。解析は、PIDS 章のトランジスタ性能のパラメータ やインターコネクト章の配線性能のパラメータと、上に示した設計複雑度の動向を元にして行った。2011 年に おける消費電力は、最近のゲームプロセサ製品について公表済のデータから取得したものである。注として下 記のものをあげておく。

- ・ 民生用据置き機器向け SOC においては、民生用携帯機器向け SOC とは違い、一般に電池寿命の問題からは開放される。しかしながら、急激な消費電力の増加は、チップのパッケージや冷却において深刻な問題となる。

- ・ リーク電力は、プロセスばらつきや温度の効果により Figure SYSD11 に示す計算結果よりも大きくなる。

- ・ データ処理エンジン DPE 1 個当たりの消費電力は、電源電圧の低下や層間膜の低誘電率化により減少する。しかしながら、チップあたりのデータ処理エンジン DPE の数が増加することにより、チップ電力にとっては重大な影響を及ぼす。

Figure SYSD11 SOC Consumer Stationary Power Consumption Trends

・明らかなのは、受入れ可能な消費電力の限度を超えないようにするためには、PIDS 章や配線章の技術ロードマップに既に組み込まれている解決策を超えた新しい解決策の早急な開発を SYSD11 で示す消費電力動向が強く表現していることである。

#### マイクロプロセサ(MPU)ドライバ

ハイボリューム向けのカスタム設計では、パフォーマンスと製造原価の問題が、設計や他の開発コスト (NRE)の問題より重要である。なぜなら、これらのチップは売上個数の結果で大きな利益を生む可能性を持っているからである。カスタム設計スタイルや、特別なプロセスエンジニアリング、設備などを正当化するためには、大量というだけでは、必要条件でもなく、十分条件でもない。NREや製造装置への投資を合わせて、期待される収益がプラスになることが重要である。ハイボリューム向けの分野における、3 つの大きなクラスは、今では、MPU、メモリ<sup>5</sup>、そしてリプログラマブルロジック(例えばFPGA)である。MPU製品クラスは、最も積極的な設計スタイルおよび製造技術を使用するため、半導体製品にとって重要なシステムドライバである。これらの大量製品のおかげで、製造フローの変更、新しい設計スタイルおよび支援ツールの作成(大きな収入は新しいツー

The International Technology Roadmap for Semiconductors: 2011

<sup>&</sup>lt;sup>5</sup> メモリは基本記憶素子とその回路が非常に高い再利用率となる特殊なハイボリューム・カスタム設計品である。これらの記憶素子は、チップ上で数百万回も複製され、また数百万チップが製造されるので、この部分のカスタム設計は並外れた適応回数と成る。この点から、正常動作を保障するためDRAMの製造ラインは独立したものとなっている。

ル生成の代価を払うことができる)、(設計者によって取られたすべてのリスクが出てくるとは限らないが)微妙な 回路問題まで洗い出される。実際、MPUは、集積度および設計の複雑さ、電力-速度性能曲線、大規模チーム の設計工程の効率、テストおよび検証、電力制御、パッケージシステム・コストに関して半導体産業をドライブし ている。MPU(一般的にはハイボリューム・カスタム設計品)の生産は、非常に労働者に集約されているにもか かわらず、全産業によっててこ入れされる新技術およびオートメーション方法(設計および組立ての両方)を作り 出す。

ITRS の MPU ドライバは、汎用の命令セットアーキテクチャ(ISA)に基づいて設計され、デスクトップとサーバシステムにおけるスタンドアロンでの使用、または、SOC アプリケーションでのコアとして組み込まれたりする。 MPUシステムドライバは、常に市場のけん引役で、歴史的に以下の特徴がある。1)標準アーキテクチャ・プラットフォームが出現したのち、それが複数世代にわたって供給され続ける、2)市場からの影響による激しい価格変動、3)非常に高い生産量および製造原価意識。MPUドライバ・モデルの重要な要素は、以下のとおりである。 (本章の調査内容は GTX ツールで検証できる。 MPU に関する内容は、電子版でリンクされた研究で提供される。)

1. 3つのタイプのMPU — これまでの歴史をみると、3つのタイプのMPUがあった。1)「デスクトップ」向けのコストパフォーマンス(CP)タイプ、2)「サーバ」向けの高性能(HP)タイプ、3)「モバイルハンドへルドデバイス」向けの電力・ネット接続・コスト(PCC:power-connectivity-cost)タイプである。2001年ITRSで予測したように、(ワイヤレス接続を備えた)電池駆動の携帯機器の市場増加は、MPUの新しいPCCカテゴリを生んだ。同時に、伝統的に「デスクトップ」向けであった CPの分野は、低額で廉価な従来型「サーバ」から、「モバイルのデスクトップ」(主としてACモードで使用されるラップトップ)および「ブレード」サーバまで、価格性能トレードオフ・カーブの広範囲に拡大しつつある。結果として、CPとHPのカテゴリ間でのパフォーマンスのギャップは小さくなっている。しかしながら、大規模なマージンのため生産量に不釣り合いな設計努力を施した本当に高額のサーバの市場は残るであろう。以前に予測されたように、新しいPCCカテゴリは、電池寿命の増加およびワイヤレス接続による便利性に後押しされ、また、グラフィックス、不揮発性メモリや高速IOといったコンポーネントを加えて、高機能と低消費電力SOC設計の特性を持ち始める。しかしながら、PCC設計のより大きなマージンと生産量は、従来のSOCと比較して、はるかに大きな設計努力を正当化するであろう。

2. ダイサイズ一定 — ダイサイズ (CPでは 140mm²、HPでは 260mm²、PCCでは 70–100mm²) はロードマップ上一定であり、一般にロジック、メモリおよび集積のオーバヘッドにブレークダウンされる。集積のオーバヘッドとは、ブロック間チャネル、無駄な領域を持つフロアプラン、および設計所要時間に伸ばせるレイアウト密度とのトレードオフによる。以前のITRSモデルと異なり、電力とコスト・配線遅延がダイサイズの強い制約になる。追加ロジックは、パッケージ・パワーの制限から効果的に利用できないかもしれないし、また、追加メモリ(たとえばより大きなキャッシュ、より高次なメモリ・ハイアラーキ・レベルのオンチップ・メモリ)も、ある点から先はコスト効率が良くないことが考えられる6。さらに、(実際のプロセスとデバイスのスケーリングの結果)配線のパイプライン段数が増加するとともに、正確なアーキテクチャの性能シミュレーションが困難になり、これもダイサイズの増加を制限するであろう。

3. マルチコア構成 — MPUのロジック規模は、主にHPおよびハイエンドCPカテゴリで、130nm世代でスタートしたマルチプロセッシングユニットのオンチップ化を反映する。これは、以下のいくつかの事実を含んでいる。: 1)最近および今後計画されている商用MPU製品の構成(サーバおよびデスクトップの両方); 2)標準の命令セットアーキテクチャと同様に検証と論理設計を再使用する必要性の増加; 3)世代ごとに逐次「増大」していく命令セットアーキテクチャ(例えば、暗号化、グラフィックス、マルチメディア等を継ぎ足した、x86、multi-media

\_

<sup>&</sup>lt;sup>6</sup> マルチコア構成やそれに伴う電力効率は、ダイサイズの微増を可能にするかもしれないが、ここでは、それでもダイサイ ズは増えることは無いと言っている。

instructions (MMX)およびexplicitly parallel instruction computing (EPIC)); 4)電力の観点ではそれほど効率的ではない汎用のプロセサ・コアに、効率的な専用「補助エンジン」<sup>7</sup>をSOCのように集積することによって、アーキテクチャ、operating system (OS)およびアプリケーションレベルでの電力の柔軟な管理を可能にする必要性; 5) プロセサ・コアのトランジスタ複雑度の増加<sup>8</sup> (プロセサ・コア毎のロジックトランジスタ数は、テクノロジ世代毎に1.4倍以下の増加); 6) 設計生産性の必要からのSOCとMPUの設計手法の融合。より複雑になる単一のコア設計がさらに数年間継続する一方、それらは、特にHPおよびハイエンドCPカテゴリで、等価なマルチコア設計と競争するようになる。2007年に4コアに再設定されたMPUモデルにおけるマルチコア設計のコア数は、テクノロジ世代毎に1.4倍の割合で増える。利用可能な平行性を活用するための"パワーの壁"と現在の制限された性能は、コアのスケーリングを制限する;最近のトレンドは4年毎に2倍の増加を示唆している。ITRSのMPUモデルでは、コア毎のトランジスタ数増加と合わせて、トランジスタ総数はテクノロジ世代毎に2倍とする。

- **4. 内蔵メモリ規模** MPUに搭載されるメモリ規模は、SRAMで 2007 年に、CP用で 4M バイト(4 x 1,048,576 x 9 ビット)、HP用で 16Mバイトに再設定された。メモリ規模は、ロジック規模と同じく、絶対時間間隔 (例えば 18 か月ごと) で増加するわけではないが、テクノロジ世代ごとに 2 倍になるとした<sup>9 10</sup>。

- 5. レイアウト密度 そのシステムの複雑さと生産ボリュームの高さから、MPUはレイアウト密度を改善するドライバである<sup>11</sup>。したがって、MPUドライバによってレイアウト密度が設定され、よって総括ロードマップ技術指標(Overall Roadmap Technology Characteristics)で規定されているトランジスタ数とチップサイズを設定する。ロジックとSRAMのレイアウト密度は、DRAMの「Aファクタ」と類似して、最近のMPU製品で数値合わせをしている。Fがそれぞれのテクノロジ世代のロジックのM1 ハーフピッチである場合、ロジック・レイアウト密度は、ほぼ175F²のスタンダードセルでの平均ゲート・レイアウトを反映しており、6トランジスタでビットセルが構成されるSRAMのレイアウト密度は、ほぼ60F²である¹²(N.B.:8トランジスタのビットセルはおおよそ84F²を要求する)。レイアウト密度は、接続されるM1ピッチのため、0.7のスケーリング係数に従って、テクノロジ世代毎に2倍とする。SRAMレイアウト密度は、周辺回路のために60%面積オーバヘッドを持ち、MPU内では(F²を単位としたビットセルあたりの面積の式を通じて)6トランジスタ・ビットセルの使用を反映している。

#### 6. **最大オンチップ (グローバル) クロック周波数** — MPUは、総括ロードマップ技術指標(Roadmap

<sup>&</sup>lt;sup>7</sup>「補助エンジン」は、画像処理や暗号化、信号処理など用のプロセサ・コア。傾向としては、汎用性に乏しく、より専用ロジックを持つアーキテクチャに向かっている。

<sup>&</sup>lt;sup>8</sup> 2007 年版でCPコアは4 千万トランジスタ、HPコアは5 千万トランジスタで構成されると再設定された。その差は、より先進 的な(トレースキャッシングや種々の予測機構などの)マイクロアーキテクチャや、補助的なエンジン(暗号化、画像処理な ど)の導入を可能にしている。

<sup>&</sup>lt;sup>9</sup> テクノロジ世代毎にロジックとメモリの量が倍になるのは、18~24ヶ月周期で進むと言うより、ITRSの他の部分と同じように、本質的にはロジックとSRAMのレイアウト密度の進歩によっている。ITRSではプレーナCMOSセントリックも残す一方で、UTB FD SOI とマルチゲートFETへの進化も進行中である。この様な新たなデバイスアーキテクチャを採用することで、単なるスケーリングを凌ぐレイアウト密度の向上が達成される。

<sup>10</sup> eDRAMを採用する事と、L3 キャッシュを搭載することは、各々チップ上のメモリを高密度化し、メモリトランジスタ数は従来の約3 倍に成る。このことはトランジスタ数の著しい増加をもたらすが、チップサイズや消費電力のロードマップには極端な影響を与えない。

<sup>11 1999</sup> ITRSから、ASIC/SOCとMPUのシステムドライバ製品は、同類のプロセスを前提に予想が行われてきた。この結果、SOCもMPUも同じ(SRAM、ロジック)レイアウト密度の製造手段を持つ純製造業が出現した。しかし、MPUは高集積、高性能をドライブし、一方SOCは高集約、低コスト、低電力をドライブする。

$<sup>^{12}</sup>$  ロードマップを通して、2 入力NANDは8×3 グリッドを仮定し、縦方向の単位はコンタクトしたローカルメタル(Metal 2)の ピッチ( $P_{M2}$  = 2.5×F)、横方向の単位はコンタクトしたポリのピッチ( $P_{poly}$  = 3×F)。6トランジスタSRAMのビットセルは2×5 グリッドでレイアウトされると仮定する、縦方向の単位はコンタクトしたポリのピッチ( $P_{poly}$  = 3×F)、横方向の単位はコンタクトしたポリのピッチ( $P_{poly}$  = 3×F)、横方向の単位はコンタクトしたローカルメタル1 のピッチ( $P_{MI}$  = 2×F)。言換えると、平均ゲートは(8×2.5F)×(3×3F) = 180 $P^2$  の面積を占め、平均 SRAMビットセルは(2×3F)×(5×2F) = 60  $P^2$  の面積を占める。製造ライブラリのデータを適用して、ロジックのAファクタを175とした。セミカスタム(ASIC/SOC)とフルカスタム(MPU)設計手法のどちらも、ロジックは100%のオーバヘッドを、SRAMは60%を仮定している。ロジックのAファクタ175 は、これまでのITRSで用いられていた320から大幅に削減され、同様に (SRAM)60 も以前に比べて大幅に削減された。このことがITRS2009でMPUドライバのダイサイズが削減された主な背景要因である。

Technology Characteristics)の中で最大オンチップ・クロック周波数もドライブしている。これは、翻って、配線、 PIDS (Process Integration, Devices, and Structures)、フロントエンドプロエス、および テストとテスト装置のロー ドマップの様々な局面をドライブする。2000年のITRSでは、MPU最大オンチップ・クロック周波数は、世代毎に 2 倍の増加するようにモデル化した。このうち、ほぼ 1.4 倍は、デバイススケーリング則(CV/Lメトリックで 17 %/年 の向上)による。残りの 1.4 倍は (例えば 180nmにおける 32 のファンアウト4 のインバーター(FO4 INV)の遅延 $^{13}$ に相当し、130nmでは 24~26 のFO4 INV遅延となる) パイプラインのロジック段数の削減からきている。2001 年のITRSで指摘したように、この歴史的なトレンドが継続しないいくつかの理由がある。1)良質のクロックパル スは 6~8 より少ないFO4 INV遅延では生成することができない。2)パイプラインの中でオーバヘッド(効果の低 減)が増加する(17)ップ・フロップあたり  $2\sim3$  段のFO4 INV遅延、パルスモードラッチあたり  $1\sim1.5$  段のFO4INV遅延)。3)手頃なパッケージングによって課された熱特性が非常に深いパイプラインを抑止する。4)アーキ テクチャと回路の革新は、周波数改善に直接寄与するものよりも、(デバイスに相関する)配線RCの悪化への 影響をさらに繰り延べる。最新のITRS では、最大オンチップ・グローバルクロック周波数が、(歴史上のMPU クロック周期データのプロットが提供されている) 90nmで、クロック周期は 12 のFO4 INV遅延でフラットになって おり、斬新な回路およびアーキテクチャのアプローチがない状態では、デバイス性能のみでクロック周波数が 増加する。2007 年には、許容できる最大消費電力からの制約を追加した。最近のMPUプラットフォームは、パ ッケージコストや信頼性、冷却コストの問題ため、最大消費電力が約 120Wで一定となってきた。一定の電力要 求のもとで、更新されたMPUのクロック周波数モデルは、2007 年に 4.7GHzと再設定され、積極的な低消費電 力設計の開発と適用にもかかわらず、テクノロジ世代毎に多くても 1.25 倍の割合で増加することになった<sup>14</sup>。

#### MPU の進化

最近の「セントラライズド・プロセッシング」の状況は、1)従来の MPU 群(ここで想定しているドライバ)からなるハイ・パフォーマンスな演算機能を持つ中央処理装置(サーバ)、および 2) 例えばワイヤレス携帯端末マルチメディア・プラットフォーム(Figure SYSD4 の SOC Consumer Portable モデル参照)を構成する、RF、アナログドックスド・シグナルおよびデジタル回路を集積した SOC からなる、パワー効率を狙った演算処理を行う「インターフェイスリメデリアル・プロセサ」【訳者注:データ量の多い演算処理を、ネットワークを介したサーバなどで処理させることを意図した、インタフェース救済型プロセサと解釈した】を統合したものである。従来型 MPU の将来に向けた進化に対するキーとなる課題は、設計生産力、パワーマネージメント、マルチコア化、I/O 帯域幅、回路およびプロセス技術に関するものである。

**設計生産性** — MPU 製品の設計および検証の複雑さやコストは、1 つの設計あたりのエンジニアが年間数千人単位(設計チームで数何百チーム)で急速に増加しているのもかかわらず、いまだに数百のバグを抱えたプロセサが市場に投入されている。この局面は、激しいカスタム化やエキゾチックな回路トポロジー使用を減少させ、論理合成および自動的な回路チューニングのような設計自動化ツールの使用を増加させた。その結果生じる生産力の増加は、プロセサ開発スケジュールおよびチーム規模を一定にすることを可能にした。タイミング、雑音や電力の解析ツール、および、物理的や電気的な設計ルールをチェックするツールの改良は、安定した設計の高品質化にも貢献した。

<sup>13</sup> FO4 INV遅延は、インバータが自身の入力負荷容量(ローカルなインターコネクトが無い状態) ×4 をドライブしたときの遅延と定義された。この値はPIDS章でデバイスのパフォーマンスを規定したCV/Iの約 14 倍に等しい。2007ITRSで更新されたFO4 INV遅延のモデルの説明は、ITRS2007 のオンラインエディションにリンクされている。

<sup>14</sup>新しい"消費電力一定"のMPUモデルは、ダイナミック電力とリーク電力の両方を併せて削減し、テクノロジ世代毎に1.25 倍に増加するクロック周波数を補償する"設計ファクタ"に依存している。設計ファクタの内、テクノロジ世代毎にダイナミック電力の15%を削減するのは、単位面積当たりのスイッチング活性化率で、設計進歩と機能/構造分割最適化、ピン交換やゲートサイジング、階層的クロックゲーティング等の既存低消費電力化技術を厳しく適用することで達成される。動的電圧周波数スケーリングは、ダイナミック電力とリーク電力の両方の設計ファクタに寄与する。これらの設計ファクタは実際には保守的で、見積もり動作周波数と実動最大周波数の間の'slack'は、論理の自由度と物理設計の最適化によって得られる更なるチップ電力削減を可能にする。設計ファクタによる電力削減がより早く製造に反映されれば、今後の低消費電力化とクロックの高周波数化の均衡を図ることが可能となる。

パワーマネージメント — パッケージの消費電力上限は(ITRSタイムフレームの最後までに 200W/cm²に達すると推測されるにもかかわらず)、高い供給電圧(世代あたりの理想値 0.7xに対して経験値換算 0.85x)および周波数(世代あたりの理想値 1.25xに対し経験値換算 2x)をコスト的に継続維持し続けることはできない<sup>15</sup>。PIDS章で述べられているように、MPUシステムドライバにおける過去のクロック周波数トレンドは、大きなオフ電流および非常に薄いゲート酸化物に導かれる将来のCMOSデバイス性能(スイッチング速度)を必要条件として説明されてきた。そのようなデバイスが与えられた場合、単に既存の回路やアーキテクチャ技術を継続するMPUは、商業的には存立できなく成るであろう。もしくは、MPUロジック搭載量および(または)ロジック動作率は、パッケージ制約を守るために減少する必要がある。ポータブルでローパワーな組込み仕様のものは、厳密にパワー制限が行われており、このような障害(課題)に早い段階で遭遇するであろう。最近のパワー効率(たとえば、GOPS/mW)は、汎用MPUに対して専用ハードウェア(組込み型ハードウェア)の方が4桁向上しており、この傾向がより大きくなっている。結果として、従来型の演算コアは、次世代のSOCライクなMPU領域において、特定用途向け、または、リコンフィギュアラブルなプロセサ・エンジンとの競争に直面することになるであろう。

マルチコア構成 — 1 つダイの中にマルチコアを持つMPUにおいて、コアは(1)グローバル配線スケーリング 則に逆らって、小さく速く、(2)多数のアプリケーションおよび構成に横断的に再利用されるため最適化すること ができる。マルチコア・アーキテクチャは、工場の歩留りを達成するため冗長性を利用するのと同じように、消 費電力削減を可能にする<sup>16</sup>。またMPUモデルは、チップ上にメモリ階層の規模を増やすことを可能とする。(メ モリ混載プロセサ、または、大規模オンチップeDRAM L3 キャッシュ)。より大きなメモリ容量がある方が(論理 回路よりも電力密度が低いため)リークやトータルの消費電力をうまく制御することが可能になる。概して、発展 的なマイクロアーキテクチャの進化(スーパーパイプライン、スーパースカラー、および予測技術)は、推進する 原動力が衰えてきているように見える。(「*ポラックの法則*」では、ある一定のプロセス技術において、新しいマイ クロアーキテクチャは古い(前の世代の)マイクロアーキテクチャを使用した場合に比べ面積が2~3倍になり、 その一方で性能は1.4倍~1.6倍しか改善されないとしている。) そのようなことから、最近は並列処理によるマ ルチスレッド化の傾向が大きくなっている。同様にネットワークやグラフィックス、セキュリティ等も、より複雑な専 用ハード、および(または)専用エンジンが充てられる傾向にある。柔軟性のある効率のトレードオフ・ポイント が、汎用的なプロセサから遠ざけ、伝統的な大規模コアとより低消費電力な小規模コアの異種混在という形態 を一般的なものとしていく。確かに、最近の発表では、このような小規模コアがMPUのスケーリングを支配して いることを示している。大規模コアが2013年以降は4年で2倍以下のレートでスケールされる一方、小規模コ アはテクノロジノード毎に2倍でスケールされる。L1やL2キャッシュを含んだMPUコアロジックはダイエリアの 約 30%占めると予想される一方、最後のL3 キャッシュがダイエリアの別の 30%を占めると予想される。

I/O 帯域幅 — MPU システムにおける I/O ピンは、主として、高機能キャッシュメモリやメインシステムメモリに使われている。プロセサのパフォーマンスが増加するに従い、I/O 帯域幅の要求は強くなってきている。最も高い帯域幅のポートは、伝統的に L2、L3 キャッシュに使われてきたが、最近の設計は、メモリの「待ち時間(レーテンシ)」を減らすために、プロセサにメモリコントローラを内蔵し始めている。これらのダイレクトメモリインタフェースはキャッシュインタフェース以上に I/O 帯域幅を要求する。メモリインタフェースに加えて、多くの設計がシステムバスを高速なポイント・ツー・ポイント・インタフェースに置き換えている。これらのインタフェースは、Gbit/s

<sup>&</sup>lt;sup>15</sup>合理的なパッケージコストを維持するために、ピン数とフリップチップのバンプピッチは、チップの集積密度の進化よりも低速でなければならない(AssemblyとPackaging章を参照)。大きな起動・動作電流と電源のIRドロップの問題は、設計技術で管理する必要が増加し、この電力管理問題は、アーキテクチャ、OS、アプリケーションレベルのシステム設計へと波及している

<sup>16</sup> コアを複製することで、処理能力を維持したまま周波数とV<sub>dd</sub>を低下して、省電力化が可能である(例えば、2 個のコアが 半分の周波数で電源電圧も半分で動作するならば、CV<sup>2</sup>fで表される動的負荷電力は等価なシングルコアに比べて4 倍電 力を節約できる)。(将来は、コアの複製によるチップサイズ増加が許容されるかもしれない) 更に言えば、リソースを時間 多重して利用するオーバヘッドを廃し、アーキテクチャと設計の主眼がメモリ以上に面積利用効率化へ向けられるかもし れない。例えば、個の機能コアの内k-1 個が動作すれば良いとする、冗長原理による歩留まり改善が実現するかもしれない。

のレートを実行するのに高速な I/O 設計を必要としている。シリアル・リンクは、このレートに到達しており、その一方で、単独チップ上の I/O の大規模集積化は、いまだ設計(各々の回路が超低消費電力を必要とする)、テスト(この速さを実行できるテスタを必要とする)、および、パッケージ(パッケージがチップとボードの接続を含め、バランスのとれた伝送ラインの配線を必要とする)に関してチャレンジ途上にある。PCIe のような I/O インターフェイスさえも搭載され、スループットとレイテンシを改善するために、より多くの I/O ピンや増加するパッケージコストを牽引している。メモリーコントローラ、インターコネクトのための要素、I/O コントローラや他の I/O ブロックがダイエリアの約 30%を占めている。

回路技術とプロセス技術 — 薄く信頼できないゲート酸化物・積極的なレチクル改良が必要なサブ波長の光学リソグラフィ・原子規模のプロセス変動(例えば注入プロセス)における増加する脆弱性を含む特徴サイズやデバイス構造のロードマップ、すなわちリソグラフィ章と PIDS 章、に暗黙的に記載されるプロセス変動によって、歩留りパラメータ(ウェハテスト後のウェハ価格/枚)は脅かされている。これにより、回路やアーキテクチャ設計のレベルで制約がかけられるであろう。ダイナミック回路の使用は、より低周波か、クロックゲート制御された分野での性能には魅力的であるが、雑音マージンおよび消費電力によって制限されているかもしれない。パス・ゲート・ロジックは基板効果により使用されなくなるであろう。歩留まりのロスを補うために冗長やリコンフィギュラブルの使用と同様に、ロジック中の single event upset(SEU)用エラー訂正が増加するであろう。設計と解析中のプロセス変動、およびパラメトリック歩留まりの変動(ウェハテスト後)への影響が考慮できるように、設計技術はさらに発展するであろう。パワーマネージメントの必要性は、下記を含むいくつかの要素技術の組合せを求めるであろう。

- ・ 並列処理やヘテロジニアスコア考慮のタスクスケジューリング、それから、プロセス・オペレーティングコンディション・経年劣化に適応性のある電圧および周波数スケーリングを含むアプリケーションレベル・OS レベル・コンパイラーレベル・アーキテクチャレベルの最適化

- 絶縁膜上のシリコン(SOI)使用の増加を含むプロセスの革新

- ・ マルチ Vth・マルチ Vdd・スループット制約のもとでの消費電力最小化・マルチドメインクロックのゲーティングとスケジューリングの同時使用を含む回路設計技術

- リーク電流を減少させる斬新なデバイス

#### MPU のチャレンジ

MPUドライバは、デバイス (オフ電流)・リソグラフィ/FEP/配線(変動性)・パッケージング(消費消費および電流分配)と同様に、設計とテスト技術(分散型/協調設計プロセス、検証、アットスピードテスト、ツール・キャパシティー、電力管理)に強く影響する。最も大きなチャレンジは、以下の項目である。

- 設計および検証の生産性 (例えば、総設計コスト、バグを大幅に減らすこと)(デザイン)

- ・ パワーマネージメントおよび電源供給 (例えば giga operations per second (GOPS)/mW) (デザイン、PIDS、アッセンブリ&パッケージング)

- ・ 量産時のパラメタリック歩留り (リソグラフィ、PIDS、フロントエンドプロセス、デザイン)

- MPU スケーリング。投資に対する十分なリターンがコアのスケーリングで獲得されなければならない。 すなわち、アプリケーションレベル・オペレーティングシステムレベル・コンパイラーレベル・アーキテク チャレベルの改善を、スループットを最大化し、アイドルパワーを最小化するために、リソースの最大利 用をして実現する必要がある。

#### ミックスド・シグナル・ドライバ

RF/ミリ波/アナログ/ミックスド・シグナルチップは、少なくとも精度の高さが重要である入力信号を扱う部分を含むチップである。それは RF、ミリ波、アナログ、AD コンバータ、 DA コンバータを含み多岐にわたる。

また最近では、高精度で信号を計測する必要のある回路をその一部として有する多くのミックスド・シグナルチップが該当する。これらのチップはデジタル回路に必要な設計やプロセス技術とは異なる技術を必要とする。技術スケーリングはデジタル回路に対しては、省電力、省面積、遅延減少の観点から常に好ましいものであるが、アナログ回路にとっては必ずしも好ましいものではない。何故なら、電源電圧スケーリングにともなって、精度要求を満たすことや決められた電圧範囲の信号を取り扱うことが困難となるためである。したがって新技術へのアナログ回路のスケーリングは困難な技術課題である。一般に AMS 回路(例えばミリ波や RF、それにアナログ設計手法)とプロセス技術(例えば、III V 族化合物半導体、シリコン・ゲルマニウム、内蔵の受動素子)は低コストの CMOS 集積化に対しては困難な技術課題を提起することになる。しかし、高精度のアナログ/RF/ミリ波回路のデジタル技術による補正や、アナログ/RF/ミリ波回路の自己試験機能のように、RF/ミリ波/アナログとデジタルをうまく組み合わせると高機能化ばかりではなく、デジタル回路と同じようなコストスケーリングも可能となる。ナノスケール CMOS でアナログ回路の設計を行うと、精度の低下が生じ、精度の低下はしばしば速度特性との引き換えになることが多いが、このようなプロセスノードでは、速度についてはほとんど問題にならない。それでも、32nmCMOSプロセスにおける厚い酸化膜による180nmトランジスタの性能は、180nmノードの 180nmトランジスタに比べアナログ特性が優位に改善していることが強調されるべきであろう。

高精度性が必要であることは、明らかにアナログ設計のためのツールへの要求内容に対して影響を及ぼす。デジタル回路設計では、論理ゲートが正しく作用する仕組みが作られている。これらの仕組みに従う限り、正確な信号値の計算は必要でなくなる。一方、RF、ミリ波、アナログ設計者は要求精度を満たすために多くの「二次効果」を考慮しなければならない。関連する技術課題としては、相互結合(信号や電源供給インテグリティに影響をあたえる静電容量、インダクタンス、抵抗および基板)や非対称性(局部的なイオン注入、位置合わせ、エッチングなどすべての製造工程の局所的な揺らぎは電気的特性に影響を与える)がある。これらの効果を解析するツールはあるが、専門家の手を必要とし、また、それらツールの精度は低消費電力アナログ回路、ミックストングナル回路、RF、ミリ波設計においては未だ不十分である。合成ツールは、アナログや RF/ミリ波に固有のレイアウト合成に集中すべきであり、現時点ではアナログ回路設計において必要となる高精度なマッチングや電磁場といったものを考慮することはできていない。AMS 回路に対する製造テストはまだまだ性能向上が必要であるが、SOC へ向けた取り組みとしてアナログ、RF、ミリ波のビルトイン・セルフ・テスト(BIST)の可能性がある。最後に、より微細化の進んだ集積回路で構成要素を再利用することは検証の自動化が十分で無いことや、ナノスケール CMOS ノードにおける圧倒的な配線系の寄生素子のため簡単ではない。アナログ設計のためには、パラメータの適合範囲を検証するなどの方法によりリグレッション手法が改善されるべきである。

今日の大規模なアプリケーションにおけるアナログ回路ならびに RF 回路は SOC のほんの一部分である。このトレンドは、現在ミリ波領域に広がりつつある。主流となる製品のビジネスは非常に競争的である一それらは大量生産品であるため、ミックスド・シグナル技術を推進させる多額の研究開発費投資が必要である。移動体通信用分野はミックスド・シグナルを必要とするもっとも大きな製造規模をもつ分野である。アナログとミックスド・シグナル (AMS) のロードマップをまとめる時、多種多様の回路形式と形状が存在するので簡略化が必要となる。2001 年版の ITRS から、本セクションでは 4 つの基本的なアナログ回路と RF について議論してきた。これらは最も重要な回路要素というだけではなく、それら回路の要求性能は RF、ミリ波、SOC のアナログ部にとって、代表的かつ重要であるためである。加えて 2011 年版では、5 つ目の基礎的要素を導入し、アンプへの要求内容についてブロードバンドアプリケーションを包含するように拡張した。

- 1. ロー・ノイズ・アンプ (LNA, Low-noise amplifier)

- 2. 電圧制御発振器(VCO, Voltage-controlled oscillator)

- 3. 電力増幅器 (PA, Power amplifier)

- 4. アナログデジタル変換器 (ADC, Analog-to-digital converter)

- 5. 並直列変換器、直並列変換器(Serializer-desirializer)

これらの基本的な RF、アナログ、ミックスド・シグナル、それに高速デジタル回路を作るために利用される設計およびプロセス技術は、他の多くのミックスド・シグナル回路の性能をも決定する。従って、これら 5 つの回路の性能を性能指標 (FoM) によって評価する。これらはミックスド・シグナル回路ロードマップの良い指針となる。(将来のロードマップにおいては、電力管理に関する要求を追加することになりそうである。これらについては現時点でも考慮すべき重要な項目ではある。)

以下、これらの性能指標について詳細に議論する。パラメータ(たとえば、利得G、雑音指数 NF)は、すべてデシベル・スケールではなく絶対値として与える。与えられた設計課題に対しての特定の解決策への偏見を避けるものとする。予想もしない解決策によって技術障壁が克服されることが度々あるので、むしろ異なるタイプの解決策を推奨するためである。(たとえば、代替解決策間の競争は、技術ロードマッピングに関係するすべてのタイプの進歩のためによい推進力となる。)。 回路性能については、その目的によってそれぞれの異なる要求性能がある。つまり、ある性能指数は異なる応用には矛盾している可能性がある「7。そのような状況を回避するために、移動通信プラットフォームに必要とされるアナログ回路およびRF回路の性能指数を議論する。最後に、本セクションでは、デバイスパラメータによる性能指標の依存性を評価する。その結果、回路設計上の要求からデバイスおよびプロセス技術仕様を導くことができるようになる。アナログ、RF、ミリ波回路性能の大きな進歩ならびに現実的で実現可能な技術進歩につながるような外挿手法を提案する。これらのパラメータは、RFおよびアナログ、ミックスド・シグナル技術の章に記載されている。

#### ロー・ノイズ・アンプ (LNA)

デジタル処理システムは、アナログ処理部分へのインタフェースを必要とする。これらのインタフェースの 典型的な例は有線あるいは無線通信での伝送媒体である。ロー・ノイズ・アンプ(LNA)は、次段の信号処理が雑音に影響を受けないようなレベルにまで入力信号を増幅する。ロー・ノイズ・アンプの重要な性能指標は、次段の信号処理段に雑音を付加することなく、かつ歪なく増幅された信号を伝えることである。

ロー・ノイズ・アンプの応用(Long Term Evolution (LTE), wideband code division multiple access (W-CDMA), wireless local area network (WLAN), global positioning system (GPS), Bluetooth, automotive radar, passive imaging 等)は多くの周波数帯に関連している。動作周波数、および時にロー・ノイズ・アンプの周波数帯域幅が達成可能な性能に影響を与える。非線形性は多くのアプリケーションに適合するように考慮する必要がある。これらのパラメータは性能指標に含まれる必要がある。他方で、異なるシステムは多くの場合、直接に比較することが不可能であり、異なる必要条件を持つ。例えば、有線アプリケーションには非常に広い帯域幅が必要である。しかし、これは消費電力を増加させる。低消費電力性は、狭帯域の無線通信アプリケーションの重要な設計項目である。広帯域幅のシステムについては、ロー・ノイズ・アンプの性能を議論する際に帯域幅の方が線形性よりも重要となることがある。

ロー・ノイズ・アンプの線形性は、第 3 次インターセプトポイントの出力によって記述することができる ( $OIP3=G \times IIP3$ 、ここでGは利得、IIP3 は第 3 次インターセプトポイントの入力)。 ロー・ノイズ・アンプ によって正確に増幅される最小の信号を決定するパラメータは、アンプの雑音指数/雑音因子Fによって直接与えられる。しかしながら、雑音が重畳されたアンプの影響度を考えるためには、 (F-I)の方が、増幅器の雑音 $N_{amplifier}$ (あるいは等価雑音温度)と入力信号に含まれる雑音 $N_{input}$ (あるいは基準温度)の比率を示すので、増幅器のノイズをよりよく表す。これらの 2 つの性能指標は消費電力Pと関連させることが可能である。その性能指標は、調整された狭帯域のアンプのダイナミックレンジと必要なDC電力の関係と考えられる。ロードマッピングのためには、それら性能指標は周波数とは無関係、すなわち特定のアプリケーションと無関係であることが望ましい。これは、ロー・ノイズ・アンプが一段増幅によって構成されると仮定することで達

17 ある種の応用については簡単化のために削除されている。考察は特定のケースに特化して行う。というのは、CMOSが技術を進化させる主要な技術であることと、多くの場合において最も重要な技術であるためである。代替技術(特に他のデバイスファミリー)や関連性についても、述べる場合がある。

The International Technology Roadmap for Semiconductors: 2011

成することが可能である。その結果、(F-I)は動作周波数fで直線的に増加する。うまく設計されたロー・ノイズ・アンプにおいて、 $OIP3 = G \times IIP3$  は、電源電圧により制約され、周波数の関数であるべきでは無い。これらの近似と仮定のもとで調整されたロー・ノイズ・アンプの性能指標  $(FoM_{LNA})$  は次のように定義される。

$$FoM_{LNA} = \frac{G \cdot IIP3 \cdot f}{(F-1) \cdot P}$$

[1]

さらに単純化させる仮定を作り、出力の 3 次のコンプレッションポイントが  $V_{DD} \times I_{DC} = P$ により制約を受け、かつ「設計のノウハウ」を無視することで、技術スケーリングに沿った性能指標 $FoM_{LNA}$ の外挿ができる。周波数fにおけるトランジスタの $F_{MIN}$ からロー・ノイズ・アンプの性能指数の物理上限( $FoM_{LNA}$ -UL) は以下のように得ることができる。

$$FoM_{LNA-UL} = \frac{f}{(F_{MIN} - 1)}$$

[2]

トランジスタの最小雑音指数/雑音係数  $F_{MIN}$ 、最大発振周波数 $f_{max}$ 、インダクタの性能、およびRF供給電圧などを含むロー・ノイズ・アンプ設計のためのデバイスパラメータのトレンドについては、RFおよびアナログ、ミックスド・シグナル技術章に記述されている。長期的に、特に線形性に関する問題は、今後ますます、デジタル校正手法を利用して解決されてゆくであろう。

ある応用分野においては、アンプの帯域幅が、線形性よりも重要視される。そのような場合において、修正版の性能指数 (FoM) というものを、式[1]を補う形で相対的な帯域幅 $BW_R$ を用いて表すことができる。

$$FoM_{LNA-pi} = \frac{G \cdot IIP3 \cdot f \cdot BW_R}{(F-1) \cdot P}$$

[3]

ここで、アンプの帯域において計測される最悪ケースでの雑音指数が使われるべきである。 パッシブなイメジング用ロー・ノイズ・アンプにおいては、線形性の性能指数は不適切であり完全に排除される。

最後に、光通信システムや将来のLSIチップ間の接続において、低ノイズ広帯域のトランスインピーダンスアンプ (TIA)は、ワイヤレスシステムにおける良く調整されたロー・ノイズ・アンプと同様の役割を担う。トランスインピーダンスアンプの性能を測る基準は、トランスインピーダンスゲイン  $Z[\Omega]$ 、消費電力 P[mW]、式[1]におけるfを置き換えるものとして最大ビットレート  $R_B[Gb/s]$ 、通常のエラーレートで動作する際の最大入力電流  $I_{MAX}[mA]$ 、それに入力換算のRMS (二乗平均平方根) 雑音電流  $i^{rms}_n[\mu A]$  である。

$$FoM_{TIA} = \frac{Z \cdot I_{MAX} \cdot R_B}{i^{rms} \cdot P}$$

[4]

ロードマップに取り上げられるよく調整されたロー・ノイズ・アンプについて、入力換算雑音電流はトランジスタの最小雑音指数と関連付けることができるが、同様に $I_{MAX}$ は電源電圧とトランジスタの破壊電圧により制約される。またトランスインピーダンスゲインとデータレートの積は、トランジスタの遮断周波数  $f_T$  に関連する。

#### 電圧制御発振器 (VCO)

電圧制御発振器(VCO)は、位相同期ループ(PLL、Phase-Locked Loop)の重要構成要素である。位相同期ループは、外部の広帯域幅で高動作周波数アプリケーションと集積回路との間での信号のやりとりにおいて同期を取るのに使われる。VCOの一番目に重要な設計上の目標は、位相雑音を最小化すること(これは生成する波形のタイミングジッタを最小化することと等価)であり、二番目には、位相雑音の最小化の目標を達成しつつ消費電力を最小化することである。これらのパラメータにより、 $\mathbf{W}^{-1}$ で測定される性能指標( $FoM_{VCO}$ )は次のように定義される:

$$FoM_{VCO} = \left(\frac{f_0}{\Delta f}\right)^2 \frac{1}{L\{\Delta f\} \cdot P}$$

[5]

ここで、 $f_0$ は発振周波数、 $L\{\Delta f\}$  は $f_0$ からオフセット $\Delta f$ 離調した周波数において測定した位相雑音の電力スペクトル密度であり、搬送波電力に対する相対値である。PはVCOコアの消費電力である。 $FOM_{VCO}$ は、しばしば、1mWを基準にdB値として表記される。

全ての測定は正確なVCOの性能比較のために室温(25℃)で実施されなければならない。FoMvcoは、通常、最小の位相雑音に達するところよりも、もっと低い電流密度のところでピーク値を取るため、FoMはVCOの位相雑音が最良となるような電流密度において計算されるべきである。

この定義から、トランジスタのテクノロジが決まり、ある特定の周波数オフセット Af において、VCOの位相雑音と出力パワーは、周波数の2乗で減少するということがわかる。また定義ではVCOのチューニング範囲を無視している。チューニング範囲という観点からは、FoMvcoは位相雑音が最大になる周波数で評価すべきである。

位相雑音の主要因は、発振の振幅、LCタンク回路の良さの指数、VCOに使われる能動部品および受動部品の雑音、キャリア周波数への近接度、およびVCO中の能動部品の 1/f雑音の影響を受けるオフセット周波数の値である。FoM $_{VCO}$ はVCOの能動部品において最大で許容できる電圧振幅におおよそ比例し、V $_{dd}$ 電源電圧に反比例し、LCタンク回路の性能指数の二乗に比例する。選択されたバイアス電流密度の値は、1/f雑音や雑音指数の最小化と発振振幅を十分大きく取ることの両者の妥協点となる。このように $FoM_{VCO}$ は技術進歩とリンクし、主には、 $f_{MAX}$ 、破壊電圧、最小の雑音指数と関連する。

周波数が高くなるにしたがって、レイアウト上の寄生素子の影響がより大きくなり、VCOのチューニング範囲を拡げることは、より困難になってくる。指標 $FoM_{VCO-T}$  [W<sup>-1</sup>]は、VCO性能をキャリア周波数、キャリアオフセット、DC電力、周波数チューニング範囲といったもので正規化したものとして定義される。

$$FoM_{VCO-T} = \left(\frac{f_0}{\Delta f}\right)^2 \left(\frac{FTR}{10}\right)^2 \frac{1}{L\{\Delta f\} \cdot P}$$

[6]

ここでFTRは、規格化したVCOの周波数チューニング範囲をパーセント表記したものであり、200  $(F_{max}-F_{min})/(F_{max}+F_{min})$  に相当する。ここで $F_{max}$ と $F_{min}$ は、VCOの発振周波数の最大と最小に対応している。以前のFoMの定義と同様に、測定は室温  $(25^{\circ}C)$  で実施しなければならず、FoMは最良のVCOの位相雑音を測定したのと同じ電流密度において計算されなければならない。FoM $_{VCO-T}$ は、参考文献[1]に紹介されている拡張されたLeessonのモデルから導くことができる。VCOゲインのために位相雑音が悪化することが考慮され、RFシステムにおいて通常要求される 10%の周波数チューニング範囲で規格化されている。FoM $_{VCO-T}$ は、しばしば 1mWを基準にdB表記される。そしてVCOの性能が良くなれば、FoM $_{VCO-T}$ は正の数であるが、増加する。

ミリ波のVCOにおいて、出力パワー $P_{out}$ がしばしば分子に追記されることに注目すべきである。これは、トランジスタの $f_{MAX}$ に近い周波数において、パワーを発生することの困難さを反映するために行われている。これは、自動車搭載のレーダーシステム応用において、特に重要である。このような状況において適用されるVCOの $F_{OM}$ の第三の式は、これらの状況を考慮して次のように表記できる。

$$FoM_{VCO-PA} = \left(\frac{f_0}{\Delta f}\right)^2 \frac{P_{OUT}}{L\{\Delta f\} \cdot P}$$

[7]

ここまでのFoMと同様に、測定は室温(25℃)において行われ、VCOの位相雑音が最良となる電流密度

において計算されなければならない。CMOSのクロスカップルタイプのVCOは、FoM<sub>VCO</sub>において良い特性を示す傾向にあるが、コルピッツ型やバイポーラVCOはFoM<sub>VCO-PA</sub>において最高の位置を占める。

技術スケーリングトレンドに加えて、デジタル制御発振器やデジタルPLLに向けた設計関連の技術トレンドについても見ておくべきである。そのようなタイプの VCO は若干悪い性能を示すが、柔軟性とコストにおいて良い特性を示す。したがって、このような回路は1つのチップ上に異なる複数の無線回路が集積されているような分野で特に好んで使われる。

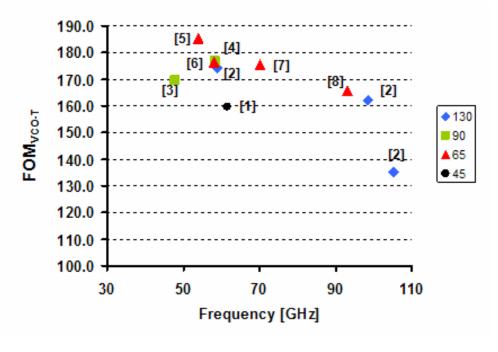

Figure SYSD12 は、130nmから 45nmノードにかけてCMOSテクノロジ構成され集積されたミリ波のVCOのFoM<sub>VCO-T</sub>の改善を示している。周波数に対する全般的な傾向として、オクターブあたり 20dBよりも少し大きな傾きを持っている。このことは、ミリ波におけるVCO設計では、良好なチューニング範囲を達成するということが課題であることを示しており、また 45nmCMOSにおけるデータが十分では無いということも言える。FoM<sub>VCO-T</sub>に関して言うと、45nmから 130nmで、どのテクノロジが優れているかを明確に見ることはできない。

Figure SYSD12 VCO Performance for Mm-Wave Circuits

#### パワーアンプ (PA)

パワーアンプ (PA) は有線あるいは無線のコミュニケーションシステムの伝送パスにおける重要なコンポーネントである。パワーアンプは、隣接したチャネルへの漏洩を最小化するために高い線形性を備えつつ、情報をオフチップへ送信するのに必要な送信電力を供給する。特に電池動作の応用においては、所望の出力電力を最小の DC 電力で実現することが要求される。

CMOS パワーアンプは、低い破壊電圧や低い Q 値の受動素子といった技術的理由により比較的小さな送信電力が必要とされる応用分野に限定される。個別部品で構成されるパワーアンプ(それらは SIP 技術のなかで集積化されるであろう)については、バイポーラや化合物半導体テクノロジが強みを持っている (RF およびアナログ、ミックスド・シグナル技術の章を参照)。

性能の指標を議論するためには、いくつかの重要なパラメータを考慮する必要がある。これらのパラメータとは、飽和出力電力 $P_{out}$ 、電力利得G、キャリア周波数f、線形性(出力の 1dBコンプレッションポイント OP1dB)、および電力付加効率(PAE)である。不幸にも、線形性はアンプの動作の級(クラス)に強く依存す

る。このため、異なる動作の級のアンプを比較することが困難となっている。さらに線形性に関する課題は、 将来的にはデジタル校正手法や完全デジタルのパワーアンプにより解決され得ると思われる。したがって、 設計アプローチ手法やアプリケーション毎の固有の仕様といったものと無関係にするために、この線形性 のパラメータを性能指数からは省略することにする。パワーアンプのトランジスタのRF利得の20dB/デケード のロールオフを補償するためf<sup>2</sup>のファクタを含めている。これらから性能指標(FoM)は次のように表すことが できる。

$$FOM_{PA} = P_{out} \cdot G \cdot PAE \cdot f^2$$

[8]

最後に、パワーアンプのアークテクチャとして最も単純な飽和型のパワーアンプアーキテクチャとして高効率な (B級やF級)もので、CMOSあるいはSiGeパワーアンプにおいて 50%のPAEを想定して単純化を行うことで、FOMとデバイスパラメータとの関係を与えることが可能となる。ここで、デバイスパラメータというのは、SiGe HBTやMOSFETで通常得られる最大飽和電力時のピーク $f_T$ の電流密度や $I_{ON}/2$  といったパラメータや、デバイスの破壊電圧や、 $f_{MAX}$ である。

$$FOM_{PA\_HBT} = \frac{J_{pfT}}{2} \min \left\{ V_{DD}, \frac{BV_{CEO}}{2} \right\} \cdot \min \left\{ MSG, \frac{f_{MAX}^2}{f^2} \right\} \cdot 0.5 \cdot f^2$$

[9]

$$FOM_{PA\_MOS} = \frac{I_{ON}}{4} \min \left\{ V_{DD}, \frac{BV_{GD}}{2} \right\} \cdot \min \left\{ MSG, \frac{f_{MAX}^2}{f^2} \right\} \cdot 0.5 \cdot f^2$$

[10]

これらの性能指数は[GHz²W/mm]で示される。この他の技術上重要なパラメータは、受動整合用の素子の質に関するものであり、上の[9][10]の式では、無限大を仮定している。将来の微細化したテクノロジ世代に向けて(詳細は、RFおよびアナログ、ミックスド・シグナル技術の章を参照)、将来のパワーアンプのFoM値を予想することができる。クラス最高のCMOSパワーアンプの性能指標(FoM)は近年向上してきているが、これは、能動デバイスと受動素子パラメータの改善に強く依存するものであるとともに、飽和パワーモードで使うデジタルによる調整機能付きのCMOSパワーアンプ(デジタルPA)の導入によるものである。しかしながら、多くの携帯電話や無線LANのパワーアンプ、現実的には全てのミリ波用パワーアンプは、引き続きSiGe HBTやIII V族化合物半導体技術により製造されるであろう。

#### アナログ-デジタル変換器 (ADC)

デジタル処理システムはアナログの世界とのインタフェースを有している。それは、オーディオやビデオのインタフェース、磁気的あるいは光学的な記憶メディアへのインタフェース、さらに有線あるいは無線の伝送媒体へのインタフェースといったものである。アナログの世界は、アナログ・デジタル変換器(ADC)を介してデジタル信号処理の世界につながる。すなわち、ADC は、時間的にも信号振幅も連続的なアナログ信号を時間的に離散的(サンプリング)かつ信号振幅も離散的(量子化された)な量に変換する。したがってADC は、システム・インテグレーションの観点から、将来のテクノロジの有効性や限界を明らかにする上で有効な性能指標になる。また、ADC は今日の集積化ミックスド・シグナル回路設計において、最も重要かつ広く用いられているミックスド・シグナル回路である。

ADCの主要な仕様値は、サンプリングと量子化に関係している。変換における分解能、つまり量子化されたレベルの数は  $2^n$ となる。ここで、nは変換器における「bit数」に対応する。このパラメータは、最大の信号対雑音のレベルSNRを決定し、これは  $SNR = n \cdot 6.02 + 1.76$  [dB] で与えられる。変換器におけるサンプリングレート、つまり単位時間に量子化されるn幅のサンプル数は、変換に要求される帯域幅とこのような性能に到達するために必要な消費電力に関係している。シャノン/ナイキストの基準は、サンプリングレートが変換される信号の帯域幅の 2 倍を超えていれば、すなわち $f_{sample}$   $> 2 \times BW$ であるときに元の信号を再合成できると述べている。

将来の技術世代の可能性を見込むために、ADCの性能指数 (FoM) は、ダイナミックレンジ、サンプルレート  $f_{\text{sample}}$  それに消費電力Pを考慮したものであるべきである。しかしながら、これらの名目的なパラメータは、変換器の実効的性能への見通しを与えるものではない。より正しい基準は、測定データから抽出される実効的な性能である。ダイナミックレンジは、低周波における信号対雑音および歪 (SINAD<sub>0</sub>) の測定値から量子化誤差 (これらの値は両方ともdB単位) を引くことで得られる。SINAD<sub>0</sub>より"実効的なbit数"は $ENOB_0 = (SINAD_0 - 1.76)/6.02$  で導くことができる。そして、ナイキスト基準とのリンクを保つために、次のことが行われる。つまり、実効的な帯域幅の倍の値 ( $2 \times ERBW$ )が、もしより小さい値である場合には、サンプルレートの値が、この値で置き換えられる。

$$FoM_{ADC} = \frac{2^{ENOB_0} \cdot \min\{f_{sample}, (2 \cdot ERBW)\}}{P}$$

[11]

ADCに関して、性能指数FoMとテクノロジパラメータの関係は、変換器のアーキテクチャや回路形式に強く依存する。ADCの複雑さと多様性は、性能指数とテクノロジパラメータの直接的な関連付けをほぼ不可能にする。RF回路においては、この関連付けはある程度可能であった。にもかかわらず、性能指数に入れ込むパラメータに関する一般的な考察が行われている18。場合によっては、重要なサブ回路の性能要求から、設計の性能要求を決めることができる。異なるADCの設計に関連するデバイスパラメータについては、RFおよびアナログ、ミックスド・シグナル技術にまとめられている。近年の傾向として、ADCの性能指数は3年ごとにおおよそ2倍改善している。設計上の知見が向上していることを考慮に入れると、過去の性能向上はアナログ素子のデバイスパラメータの改善とよく一致している。スタンドアロンのCMOS/バイポーラCMOS(BiCMOS)の場合、2011年時点の最高クラスであるADCの性能は2100[ギガ変換/(秒・ワット)]であり、エンベディドCMOSの場合で800[ギガ変換/(秒・ワット]]である。電源電圧や信号電圧振幅が減少する中で、ADCの性能向上をはかるために設計上の技術進歩が強く要求される。長期的には、基本的な物理的制約(例えば熱雑音)が、ADCの性能指数のさらなる改善の障害になるかもしれない。

#### 直並列変換器、並直列変換器

直並列変換器、並直列変換器(SerDes)は、有線通信や光ファイバー通信システムにおいて最も重要な部品であり、近年CMOSによって実現されるケースが増えている。直並列変換器、並直列変換器には、N:P多重化回路(マルチプレクサ)、P:N逆多重化回路(デマルチプレクサ、ここでN>PでありPは通常 1 や 4 である)、クロックやデータの再生回路(CDR)、クロックの逓倍回路(CMU)といったものが含まれる。シングルチップの直並列変換器や並直列変換器において、最も高速なものでは、直列データのデータレートが 56Gbsに達しており、複数チップや並列レーンによる方式であれば、100Gbsを超えている。近年の傾向として、複数ビットの高速デジタル・アナログ変換器を集積し、並直列変換器の出力に接続することで、16QAMといった高度な変調方式が実現できるようになってきている。性能指数FoM<sub>SerDes</sub> [Gbs/mW]を、この種の回路に対して定義することができるが、ある多重化-逆多重化の比において、消費電力を最小化しつつデータレート R<sub>B</sub> を最大化するという性能上の目標として定義される。

$$FoM_{SerDes} = \frac{R_B \cdot MuxDeMux_{ratio}}{P}$$

[12]

主要なデバイスパラメータは、 $f_T$ (通常 $f_T \ge 3 \times R_B$  となるようなデバイステクノロジが必要)、ピーク $f_T$ 電流密度(少ないのが良い)、スルーレート $S_{Li}$ 、CMU回路の遅延である。将来のテクノロジ世代におけるデバイスパラメータの改善予測(RFおよびアナログ、ミックスド・シグナル技術を参照のこと)から、将来の性能指数 $FoM_{SerDes}$ を推論することができる。

\_

<sup>&</sup>lt;sup>18</sup> R. Brederlow, S. Donnay, J. Sauerer, M. Vertregt, P. Wambacq and W. Weber, "A Mixed-signal Design Roadmap for the International Technology Roadmap for Semiconductors (ITRS)," IEEE Design and Test, December 2001.

#### ミックスド・シグナルの発展

*コストの見積り ―* ミックスド・シグナルのドライバの発展は、コストと性能の相互関係によって決定される。 コストと性能の両方は、技術トレンドが既存のアプリケーションに対して十分適応可能であるかを決定し、さ らに新しいアプリケーションへの発展性を有しているかも決定する。大量生産されるデジタル製品において は、そのコストはほとんどチップ面積で決まっている。ところが、ミックスド・シグナルの設計においては、面 積はいくつかのコスト要因の一つでしかない。SOCにおけるアナログ回路の占有面積は、通常、5~30%の 範囲にある。したがって、ミックスド・シグナルの領域の面積を縮小しようとする経済的な圧力は、論理回路 部分やメモリの部分に比べるとあまり強くない。しかしながら、この状況は次の 5~10 年程度の間で、複数の 無線回路をオンチップに搭載したり、フェーズドアレイといったものをオンチップに搭載したりといったものが 出現することで変化しそうである。以下のような考察をすることができる。

- アナログ部分の面積は、システムにおけるアナログ部分とデジタル部分の切り分けを変えることで時 として減らすことができる。(例えば ADC における自動校正機能やパワーアンプの線形性調整、デ ジタルパワーアンプ)

- 高性能のアナログ素子を導入するとプロセスが複雑化する。このような解決アプローチは、面積を削 減することには有効であるが、全体のコストを引き上げることになる。

- ・ 使用する半導体技術の選択は、設計コストに影響を与える場合がある。というのは、ハードウェア設 計を何度もやり直すというリスクにつながるからである。(テープアウトに至る設計の繰り返し)

- 製造コストは、パラメータの歩留りの感度によっても影響を受ける。

- テストコストがミリ波の周波数帯のデバイスの製造において支配的になる可能性がある。このようなア プリケーションにおいては、自己診断回路といったものを組み込むことにより、製造コスト全般につい てめざましい低減をすることが可能となる。

- 複数のダイ(例えば、ダイサイズが大きく安価なデジタルチップと、ダイサイズの小さい高性能のアナ ログチップの組合せ)を使うSIPのような解決法の方が、SOCよりも安価になることもありえる。

このような考察は、ミックスド・シグナルの設計におけるコスト見積りを大変困難にする。最初に、高性能用 途のみに議論を限定して、ミックスド・シグナルのコストを見積もることを試みる。というのは、このような用途 というのは、テクノロジへの要求をドライブするものであるからである。次に、無線やアナログの特性が高性 能の受動素子やアナログトランジスタにより実現され、それらの面積がほぼコスト<sup>19</sup>に反映されることを注記 しておく。システムのデジタル部分の回路密度を向上させるという要請によりトランジスタのスケーリングが推 進されてきており、アナログ向けのトランジスタもこれに従い、レイアウト密度を向上させてきていることにつ いては特に言及する必要は無い。今日の多くのアナログ・ミックスド・シグナル回路の設計において、チップ 面積は内蔵の受動素子の面積で決まっている。すなわち、これらの受動素子の面積がシステムのミックス ド・シグナル部分のコストを決定している。したがって、無線通信の章における表は、高性能のミックスド・シ グナル設計におけるコスト/性能比を向上させるのに必要なオンチップ搭載の受動素子のレイアウト密度の ロードマップを示している。これに並行して、受動素子をデジタル回路で置き換えるようなシステムアーキテ クチャの変革がまさに進行中である。

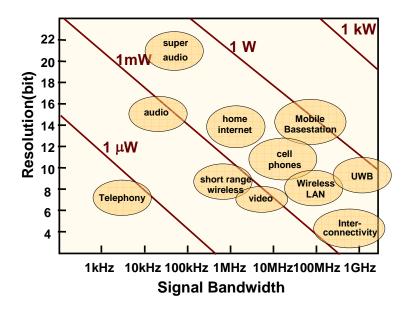

技術の充足度の見積り ― Figure SYSD13 は、電力と性能の関係の観点で最近の応用分野ごとに ADC への要求を記載している。一定の性能(分解能×帯域幅)という条件のもとでの一定消費電力特性が傾き-1 の直線で示されている。性能を向上するということは、よいテクノロジを使うか、回路設計を改善することで 達成されるが、これは一定電力消費の線を右上に移動することと等価である。データによると、ADC の技術

<sup>19</sup> アナログ設計においては、消費電力はしばしば回路面積に比例する-そして電力は4 つすべての性能係数に含まれ ていることから、面積とコストについては暗黙的に考察していることになる。それでもなお、面積に関する要求は、ロードマ ップにおいて明示的に表記されるべきである。

上の「バリア・ライン」は、1Wの電力消費で表されているが、これは10年間で一桁程度しか移動していないことがわかる。今日の多くのADCの技術(シリコン、SiGe、III-V族化合物半導体、それにこれらのハイブリッド)は、1Wのバリア・ラインの下にある。そして、このバリア・ラインをより急速に引き上げるための解決策は見つかっていないが、2010年の現状(2.13GHz/mW)では、変換機能としては許容できる消費電力で高速データ通信分野に十分適応可能な位置にある。

ADC の性能向上のペースはハンドセット(通信機)の用途に対しては十分であったが、GSM の基地局のデジタル線形化や、携帯応用における高データレートのデジタルビデオ用途に対しては、明らかに不足である。例えば、32 キャリアを扱うマルチキャリア GSM 基地局においては、80dB 以上のダイナミックレンジを必要とする。このような基地局において、25MHz の送信帯域幅でデジタル線形化を実現するためには、ADC に消費電力 1W 以下で 300MHz の標本化速度と 14bit の分解能が要求される。高性能パワーアンプを必要とするアプリケーションにおいては、SiGe ヘテロ接合バイポーラトランジスタ(HBTs)や III-V 化合物半導体をパワーアンプに利用し、他のアナログフロントエンド部には CMOS を利用する SIP による解決が時に最適解である。

新規製品分野の実現 — 通常の製品において、製品出荷を増やすために一般的に採られる戦略は、価格を下げて性能を上げることである。しかしながら、特にミックスド・シグナル部を含んでいる製品にとってこの戦略は半導体ビジネスにおける唯一の推進策ではない。このような戦略よりも、技術と設計の改善を行うことにより、新しい応用(近年の携帯電話のように)が生み出され、半導体産業は新しい市場に入ってゆくことができた。Figure SYSD13 に示されるミックスド・シグナルの設計に関する解析結果は、将来の製品や市場に向けた設計への要求や、設計の実現性を見積もることに使うことができる。性能を向上させることは、現時点の技術で実現されているものよりも高い性能や低い消費電力を必要とする新しい製品を開発できるということと等価であることがわかる。言い換えると、新しい製品の仕様がわかれば、これらの仕様を実現するために必要な半導体技術を見積もることができる。あるいは、半導体産業が妥当なコストと性能で製品を作ることができるようになるまでの時間を知ることができる。このように性能指数の概念は、新しいミックスド・シグナルの製品の市場の潜在性や実現可能性を評価することに使うことができる。高性能のミックスド・シグナルの回路を低コストで、また高い周波数や高いデータレートで実現する能力は、半導体産業が新しい製品や市場を開拓する原動力となる。

Figure SYSD13 Recent ADC Performance Needs for Important Product Classes

#### ミックスド・シグナルにおけるチャレンジ

ミリ波の設計やミリ波の設計ほどではないが、RFの設計については、アナログ設計からは分けて考えた ほうが良い。ミリ波のシステムは、CMOS、BiCMOSそれにIII-V族半導体のスケーリングの恩恵を大いに受 けている。回路を電圧ドメインでは無くMOSFETを0.2~0.4mA/μmあるいはそれ以上といった比較的大きな 電流となるようバイアスするような電流ドメインで設計することにより、トランジスタの高いfr、fmax、それに低い 雑音指数といった有利な特性を生かしつつ、ナノスケールCMOSによるRFやミリ波の回路を閾値電圧のば らつきやリーク電流に対して頑強にすることができる。

今日のミックスド・シグナルの設計のほとんど、3GHz以下で動作するような全てのPAにおいて(特に古典 的なアナログ設計において)は、処理対象の信号を、電圧の差として表すので、電源電圧が最大の信号振 幅を決定する。電源電圧の低下(定電界スケーリングの結果)は、最大の達成可能な信号レベルが下がる ことを意味する。このことは、SOC ソリューションのミックスド・シグナル製品の開発に対して大きな影響を与 える。デバイスパラメータによる回路動作の影響のシミュレーション精度は向上しているものの、最先端の CMOSプロセスノードにおける複雑さの進展に対しては追いついていない。したがって自由度を制約し、可 能な限り再利用すること等で固定的なレイアウトルールを適用することが必要とされる。アナログ、RFおよび ミリ波の設計において最初のシリコンで成功を収めるためには、以前よりも一層、より良いシミュレーションツ ールやモデルに依存するところとなっているが、新しいミックスド・シグナル部品の開発は、一般的にデジタ ルやメモリ部品よりも多くの開発時間がかかる。もし面積に関する制約が無くなるならば、理想的な設計プ ロセスは、既存のミックスド・シグナルの設計資産を再利用し、SOC と外部とのインタフェース仕様を整合す るようにパラメータ調整をすることである。しかしながら、このような再利用をおこなうためには、微細化にもか かわらず最大動作電圧がスケーリングもせずに、かつ同じ電気特性かより良い特性をもつ特別の MOSFET を必要とする。これは、PIDS 章でのミックスド・シグナルの CMOS トランジスタの特性として、高いアナログ供 給電圧と、この電圧が複数のデジタルテクノロジ世代にわたって向上してゆくことにつながる。このようなデ バイスをもってしても、アナログ回路ブロックを新しい技術ノードに適用するのは、特性の検証のための効 率的な手法が無いため、時間のかかるものとなる。さらにこのようなスケーリング手法は、スケーリングから得 られるコスト上の恩恵を少なくしてしまうことから、多量のアナログ回路を搭載するような設計においては好 ましくないものとなる。このような場合において、アーキテクチャの変更といったものを含む、最初から再設 計を行うというやり方が、いまだに多く見られる。要約すると、アナログ回路ブロックの電源電圧低下および アナログ回路ブロックの開発期間は、引き続きミックスド・シグナル機能の低価格化と効率的なスケーリング に対して主要な障害となる。最も困難なミックスド・シグナルにおけるチャレンジは以下のものであると言え る。

- *供給電圧の低下*: 電流モード回路を使うこと、電圧を上げるためのチャージポンプ回路を使うこと そして、スタンダード・セル回路において、電圧の最適化が必要 (PIDS、デザイン)

- ナノスケール CMOS において圧倒的に増大し続ける寄生素子の問題のせいで、レイアウトからの寄 生素子パラメータ抽出無しの回路図レベルの設計が役に立たないという状況になってきている(モ デリング&シミュレーション、デザイン)

- *相対的なパラメータのばらつきの増大*:能動的にパラメータのミスマッチを補償する機構の導入、 製品の仕様決定の際に速度と分解能のトレードオフを行うことが必要 (PIDS、フロントエンドプロセ ス、リソグラフィ、デザイン)

- チップあたりのアナログトランジスタ数の増加: ミックスド・モードのシミュレーションツールの更なる 高速処理、より正確なコンパクトモデル、および収束性の改善が必要 (モデリング&シミュレーショ ン、デザイン)

- *処理速度の向上(キャリア周波数およびクロック周波数)*: デバイスと配線、それに中間層の配線 における誘導効果を正確にモデリングすることに加えて、テスト能力、パッケージやシステムレベル のインテグレーションができることが必要 (テストとテスト装置、アセンブリ&パッケージング、モデリ

ング&シミュレーション)

- ・ SOC 集積に伴うクロストーク: 寄生効果のより正確なモデリング、RF とミリ波回路における完全差動回路の設計、これらに加えて PIDS 章に記載されている技術的な対処が必要 (PIDS、モデリング &シミュレーション、デザイン)

- ・ *設計スキルおよび生産性の不足*: トレーニングが欠如していること、また、自動化が進んでいないことに起因する。教育と基本的な設計ツールに関する研究が必要(デザイン)

- ・ アナログ回路に検証において、回路の再利用を目的とした特性のリグレッション試験を行うための一 連のしくみが欠如していること

#### 混載メモリ・ドライバ

SOC 設計において、混載される RAM や読み出し専用メモリ(ROM)、そしてレジスタ・ファイルメモリの数や 種類がますます増加している。インターコネクト、IO 帯域幅、設計生産性、そしてシステム電力限界は、すべて マイクロエレクトロニクス・システムにおける高いレベルのメモリ集積が継続するというトレンドを指し示している。 混載メモリ技術をドライブするアプリケーションは、再構成可能な応用(たとえば、自動車用)のコード・ストレー ジであり、スマートまたはメモリ・カードのデータ・ストレージであり、そしてゲーム用あるいは大容量記憶システムに見られる高性能ロジックと混在する大容量メモリである。

ロジックとメモリのバランスは、総システム・コスト、電力や IO 制約、ハードウェア・ソフトウェア構成、そして全体的なシステムとメモリの階層に影響を受ける。コストに関しては、デバイス性能とモノリシックなロジック・メモリ集積の追加マスク層が、チップ・積層・チップ、もしくは他のシステム・イン・パッケージ(SIP)集積の代案に対して釣り合う必要がある。ロジック・メモリ集積のレベルは、さらにコード・データ・バランス(たとえば、ソフトウェアはコードメモリに書かれ利用されるべきで、不揮発性やアプリケーションのデータはデータメモリに存在すべきである)だけでなく、ハードウェア・ソフトウェアの切り分けのトレードオフ(たとえば、ソフトウェアはより柔軟であるが、ブートしなければならず、より多くの面積を消費する)にも反映するであろう。IO ピン数と通信速度は、システム構成として、どのように帯域幅とストレージ構造をトレードオフするかを決定する。つまり、1) メモリアクセスは、より高いもしくはより低いバンク・グループでメモリを構成する際の周辺オーバへッドの代償によって速くすることができる。そして、2) アクセス速度はまた、ピンカウントと回路の複雑さを、高速で少ピンカウント接続なのかあるいは低速で多ピンカウント接続なのか、その間でどのようにバランスさせるかにも依存する。

メモリ階層では、プロセッサの速度要求にメモリアクセスの能力が一致していることが重要である。この事実は伝統的なプロセッサ・アーキテクチャー領域ではよく知られており、プロセッサ・コアの"メイン"メモリとフォアグラウンド・メモリ(たとえば、レジスタ・ファイル)の間で、数レイヤー(層)かのレベルのハードウェア制御されるキャッシュを導入することが行われている。各レイヤーでは、通常ひとつの物理キャッシュメモリが存在する。しかしながら、階層の選択は、さらに電力にとって強い意味合いを持つ。従来のアーキテクチャは、エネルギーの非効率的な制御オーバヘッドを代償に大きな性能向上を得ている。非効率な制御オーバヘッドの例として、高次の連想キャッシュの周囲回路にある予測/履歴メカニズムと余分なバッファがあげられる。システムの観点から、ポータブル機器で主要な内蔵のマルチメディアや通信のアプリケーションは、ソフトウェア制御された分散のメモリ階層からより恩恵を受けることができる。メモリ階層の異なるレイヤーは、さらに高度な異なるアクセス・モードと内部分割を必要とする。ページ/バースト/インターリーブといったモードの使用と、バンクの物理的な切り分け、サブアレイ、分割ワード/ビットラインは、一般にレイヤーごとに最適化されるに違いない。また、ますます支配的となるリーク電力制約は、現在よりもさらに異種のメモリからなる階層構成を採ることにつながってゆく。

スケーリングは混載メモリ構造に多くの課題を提示する。回路レベルでは、スタティック・ランダムアクセス・メモリ(SRAM)のセンス・アンプ・マージン、および DRAM での減少した Ion ドライブ電流は、2 つの明確な課題

である。より小さな形状は、たとえばデバイス当たりの少数のドーパントなど、ばらつきにより大きな影響を与える。ひとつの製品の中により多くのデバイスが集積されるので、ばらつきは、ノイズマージンとリークパワー(リーク電流は Vth の指数関数的な依存性がある)の両方に関して、より大きなパラメータ上の歩留まり損失に繋がる。将来の回路トポロジーと設計手法は、これらの問題に取り組む必要があるであろう。エラー耐性は、プロセス・スケーリングと積極的なレイアウト密度で深刻化するもう一つの課題である。混載メモリのソフト・エラー・レート(SER)は、形状の縮小につれ増加し、そして混載 SRAM および混載 DRAM の両方に影響する。これに関してはデザイン章で議論される。不揮発性メモリでもビットの書き換えのときは、ソフト・エラーの影響を受けるかもしれない。特に、自動車部門のような高度で信頼性のあるアプリケーションには、エラー訂正はいずれくる要求であり、アクセス・タイム、パワー、およびプロセス・インテグレーションに対する歩留まりと信頼性のトレードオフを引き起こすであろう。最後に、大規模と異種混合メモリ・アレイのためのコスト効率のよい製造テストおよびビルトイン・セルフテストは、SOC における重要な要求である。

メモリは繰り返し多数配置されることから、メモリのセルサイズとパフォーマンスは、コストおよび性能に大きく直接の影響を持つ。ここで議論されるメモリ以外の基本回路すべてと比較して、最適化のために費やされる技術的な作業の量は大変多くなる。 Table SYSD3a とSYSD3b は、3 つの現在主要なタイプの混載メモリ: CMOS 混載スタテック・ランダムアクセス・メモリ(SRAM)、混載不揮発性メモリ(NVM)、それに混載ダイナミック・ランダムアクセス・メモリ(DRAM)の技術要求を与えるものである。これらのパラメータは、回路設計考察と PIDS 章の中の logic requirement table(ロジック要求テーブル)によって与えられる技術境界条件のバランスに起因して決まる。 高性能と低電力を駆り立てるものとして CMOS SRAM の挑戦的なスケーリングは途切れること無く継続する。 高性能化としてノード当たり 0.7×のリード・サイクル・タイムのスケーリングを要求する。 電圧スケーリングは、たとえば保持時間と読み出し動作電圧の間の関係、あるいは 45 nm ノードで始まる PMOS デバイス要求上の電源電圧としきい値電圧スケーリングの影響、など多数の検討を伴う。発生期の強誘電体 RAM、磁気抵抗RAM、それに相変化メモリ技術については、新探求素材章で議論されている。

Table SYSD 3a Embedded Memory Requirements—Near-term

| Year of Production                                                                                       | 2007        | 2008              | 2009              | 2010        | 2013              |

|----------------------------------------------------------------------------------------------------------|-------------|-------------------|-------------------|-------------|-------------------|

| DRAM ½ Pitch (nm)                                                                                        | 65          | 55                | 50                | 45          | 35                |

| CMOS SRAM High-performance, low standby power (HP/LSTP) $DRAM \not\sim pitch \ (nm), \ Feature \ Size-F$ | 65          | 65                | 65                | 45          | 35                |

| 6T bit cell size $(F^2)$ [1]                                                                             | 140F²       | 140F <sup>2</sup> | 140F <sup>2</sup> | 140F²       | 140F <sup>2</sup> |

| Array efficiency [2]                                                                                     | 0.7         | 0.7               | 0.7               | 0.7         | 0.7               |

| Process overhead versus standard CMOS – #added mask layers                                               | 2           | 2                 | 2                 | 2           | 2                 |

| Operating voltage – V <sub>dd</sub> (V) [4]                                                              | 1.1         | 1/1.1             | 1/1.1             | 1           | 0.9/1             |

| Static power dissipation (mW/Cell) [5]                                                                   | 3E-4/1E-6   | 3E-4/1E-6         | 3E-4/1E-6         | 5E-4/1.2E-6 | 1E-3/1.5E-6       |

| Dynamic power consumption per cell (mW/MHz) [6]                                                          | 4.5E-7/7E-7 | 4E-7/6.5E-7       | 4E-7/6E-7         | 3E-7/5E-7   | 2.5E-7/4.5E-7     |

| Read cycle time (ns) [7]                                                                                 | 0.3/1.5     | 0.3/1.5           | 0.3/1.5           | 0.2/1.2     | 0.15/0.8          |

| Write cycle time (ns) [7]                                                                                | 0.3/1.5     | 0.3/1.5           | 0.3/1.5           | 0.2/1.2     | 0.15/0.8          |

| Percentage of MBU on total SER                                                                           | 16%         | 16%               | 16%               | 32%         | 64%               |

| Soft error rate (FIT/Mb) [8]                                                                             | 1150        | 1150              | 1150              | 1200        | 1250              |

| Embedded Non-Volatile Memory (code/data), DRAM ½ pitch (nm)    | 90               | 90               | 90               | 90               | 65               |

|----------------------------------------------------------------|------------------|------------------|------------------|------------------|------------------|

| Cell size $(F^2)$ – NOR FLOTOX [9]                             | 10F <sup>2</sup> |

| Array efficiency – NOR FLOTOX [10]                             | 0.6              | 0.6              | 0.6              | 0.6              | 0.6              |

| Process overhead versus standard CMOS – #added mask layers [3] | 6–8              | 6–8              | 6–8              | 6–8              | 6–8              |

| Read operating voltage (V)                                     | 2V               | 2V               | 2V               | 1.8V             | 1.5V             |

| Write (program/erase) on chip maximum voltage (V) – NOR [11]   | 10V              | 10V              | 10V              | 10V              | 10V              |

| Static power dissipation (mW/cell) [5]                         | 1.00E-06         | 1.00E-06         | 1.00E-06         | 1.00E-06         | 1.00E-06         |

| Dynamic power consumption per cell (mW/MHz) [6]                | 6.00E-09         | 6.00E-09         | 6.00E-09         | 6.00E-09         | 4.00E-09         |

| Read cycle time (ns) – NOR FLOTOX [7]                          | 15               | 15               | 15               | 15               | 15               |

| Program time per cell (μs) – NOR FLOTOX [12]                   | 1.0              | 1.0              | 1.0              | 1.0              | 1.0              |

| Erase time per cell (ms) – NOR FLOTOX [12]                     | 10.0             | 10.0             | 10.0             | 10.0             | 10.0             |

| Data retention requirement (years) [12]                        | 10               | 10               | 10               | 10               | 10               |

| Endurance requirement [12]                                     | 100000           | 100000           | 100000           | 100000           | 100000           |

| Embedded DRAM, ½ pitch (nm)                                    | 90               | 90               | 65               | 65               | 45               |

| 1T1C bit cell size (F <sup>2</sup> ) [13]                      | 12–30            | 12–30            | 12–30            | 12–30            | 12–30            |

| Array efficiency [2]                                           | 0.6              | 0.6              | 0.6              | 0.6              | 0.6              |

| Process overhead versus standard CMOS – #added mask layers [3] | 3–5              | 3–5              | 3–5              | 3–5              | 3–6              |

| Read operating voltage (V)                                     | 2                | 2                | 1.8              | 1.7              | 1.6              |

| Static power dissipation (mW/Cell) [5]                         | 1.00E-11         | 1.00E-11         | 1.00E-11         | 1.00E-11         | 1.00E-11         |

| Dynamic power consumption per cell (mW/MHz) [6]                | 1.00E-07         | 1.00E-07         | 1.00E-07         | 1.50E-07         | 1.60E-07         |

| DRAM retention time (ms) [12]                                  | 10               | 10               | 4                | 4                | 2                |

| Read/Write cycle time (ns) [7]                                 | 3                | 3                | 2                | 2                | 1.6              |

| Soft error rate (FIT/Mb) [8]                                   | 60               | 60               | 60               | 60               | 60               |

FIT—時間あたり故障率 (failures in time) 1FIT=1E-9/時間 FLOTOX—フローティングゲート・トンネル酸化膜 (floating gate tunnel oxide)

MBU—複数ビットのエラー (multiple bit upsets) NAND—"not AND"の論理演算 NOR—"not OR"の論理演算

*Table SYSD 3b* Embedded Memory Requirements—Long-term

| Year of Production                                                                                       | 2016              | 2019              | 2022              | 2024              | 2026      |

|----------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-----------|

| DRAM ½ Pitch (nm)                                                                                        | 25                | 18                | 13                | 10                |           |

| CMOS SRAM High-performance, low standby power (HP/LSTP) $DRAM \not\sim pitch \ (nm), \ Feature \ Size-F$ | 25                | 18                | 13                | 10                |           |

| 6T bit cell size $(F^2)$ [1]                                                                             | 140F <sup>2</sup> | 140F <sup>2</sup> | 140F <sup>2</sup> | 140F <sup>2</sup> |           |

| Array efficiency [2]                                                                                     | 0.7               | 0.7               | 0.7               | 0.7               |           |

| Process overhead versus standard CMOS – #added mask layers [3]                                           | 2                 | 2                 | 2                 | 2                 | Not       |

| Operating voltage – V <sub>dd</sub> (V) [4]                                                              | 0.8/0.9           | 0.7/0.8           | 0.7/0.8           | 0.7/0.8           | currently |

| Static power dissipation (mW/cell) [5]                                                                   | 2E-3/2E-6         | 3E-3/2.5E-6       | 5E-3/3E-6         | 6E-3/3.5E-6       | projected |

| Dynamic power consumption per cell (mW/MHz) [6]                                                          | 2E-7/4E-7         | 1.5E-7/3E-7       | 1E-7/2E-7         | 0.5E-7/1E-7       |           |

| Read cycle time (ns) [7]                                                                                 | 0.1/0.5           | 0.07/0.3          | 0.07/0.3          | 0.07/0.3          |           |

| Write cycle time (ns) [7]                                                                                | 0.1/0.5           | 0.07/0.3          | 0.07/0.3          | 0.07/0.3          |           |

| Percentage of MBU on total SER                                                                           | 100%              | 100%              | 100%              | 100%              |           |

| Soft error rate (FIT/Mb) [8]                                                                             | 1300              | 1350              | 1400              | 1450              |           |

| Embedded Non-Volatile Memory (code/data), DRAM ½ pitch (nm)    | 40               | 32               | 32               | 25               | 20                     |

|----------------------------------------------------------------|------------------|------------------|------------------|------------------|------------------------|

| Cell size (F <sup>2</sup> ) – NOR FLOTOX [9]                   | 10F <sup>2</sup> | 10F <sup>2</sup> | 10F <sup>2</sup> | 10F <sup>2</sup> | 10F2                   |

| Array efficiency – NOR FLOTOX [10]                             | 0.6              | 0.6              | 0.6              | 0.6              | 0.6                    |

| Process overhead versus standard CMOS – #added mask layers [3] | 6–8              | 6–8              | 6–8              | 6–8              | 6-8                    |

| Read operating voltage (V)                                     | 1.3V             | 1.2V             | 1.1V             | 1.0V             | 1.0V                   |

| Write (program/erase) on chip maximum voltage (V) – NOR [11]   | 9V               | 9V               | 9V               | 9V               | 9                      |

| Static power dissipation (mW/cell) [5]                         | 1.00E-06         | 1.00E-06         | 1.00E-06         | 1.00E-06         | 1.00E-06               |

| Dynamic power consumption per cell (mW/MHz) [6]                | 3.50E-09         | 3.00E-09         | 3.00E-09         | 3.00E-09         | 2.50E-09               |

| Read cycle time (ns) – NOR FLOTOX [7]                          | 12               | 10               | 10               | 8                | 7                      |

| Program time per cell (μs) – NOR FLOTOX [12]                   | 1                | 1                | 1                | 1                | 1                      |

| Erase time per cell (ms) – NOR FLOTOX [12]                     | 10               | 10               | 10               | 10               | 10                     |

| Data retention requirement (years) [12]                        | 10               | 10               | 10               | 10               | 10                     |

| Endurance requirement [12]                                     | 100000           | 100000           | 100000           | 100000           | 10000                  |

| Embedded DRAM, ½ pitch (nm)                                    | 35               | 25               | 25               | 20               |                        |

| 1T1C bit cell size (F <sup>2</sup> ) [13]                      | 12–50            | 12–50            | 12–50            | 12–50            |                        |

| Array efficiency [2]                                           | 0.6              | 0.6              | 0.6              | 0.6              |                        |

| Process overhead versus standard CMOS – #added mask layers [3] | 3–6              | 3–6              | 3–6              | 3–6              | <b></b> .              |

| Read operating voltage (V)                                     | 1.5              | 1.5              | 1.5              | 1.5              | Not                    |

| Static power dissipation (mW/cell) [5]                         | 1.00E-11         | 1.00E-11         | 1.00E-11         | 1.00E-11         | currently<br>projected |

| Dynamic power consumption per cell (mW/MHz) [6]                | 1.70E-07         | 1.70E-07         | 1.70E-07         | 1.70E-07         | projected              |

| DRAM retention time (ms) [12]                                  | 1                | 1                | 1                | 1                |                        |

| Read/Write cycle time (ns) [7]                                 | 1.3              | 1                | 1                | 1                |                        |

| Soft error rate (FIT/Mb) [8]                                   | 60               | 60               | 60               | 60               |                        |

FIT—時間あたり故障率 (failures in time) 1FIT=1E-9/時間

FLOTOX—フローティングゲート・トンネル酸化膜 (floating gate tunnel oxide)

MBU—複数ビットのエラー (multiple bit upsets) NAND—"not AND"の論理演算 NOR—"not OR"の論理演算

#### Tables SYSD3a and SYSD3h の用語の定義

- [1] 最小加工寸法の関数として表記した標準的な6トランジスタのCMOS SRAM セルのサイズ

- [2] (メモリのコア領域の面積/メモリ回路全体の面積) で定義される典型的なアレイ効率.