# 論理回路のソフトエラー

- 低電力LSIの新しい課題 -

STARC 設計技術開発部 低電力技術開発室 石橋 孝一郎

# 内容

- 背景

- 論理回路のソフトエラー

- ✓組み合わせ論理回路

- ✓フリップフロップ回路

- STARCでの取り組み

- ✓耐放射線ラッチ回路技術

- 結論

### 近年の半導体ソフトエラーの実例

#### Sun tries to cope with server flaw

For the past year, Sun Microsystems Inc. has struggled to solve a mysterious fault that can cause its high-end servers to crash unexpectedly, an embarrassing problem for a computer maker that routinely refers to its servers as "rock solid" reliable.

By David Hamilton The Wall Street Journal Online November 7, 2000, 4:00 PM PT

(http://zdnet.com.com/2100-11-525403.html?legacy=zdnn)

ソフトエラーによって月に一度、突然のサーバークラッシュが起こっていたSun Microsystemsの報告。

長時間にわたりシステムがダウン、さらにシステムの種類によっては人命に係わる事故に繋がる可能性もある。

ソフトエラー問題がわかる一例

STRJ WS: March 4, 2004

### ソフトエラー対応回路研究状況

- 1978 ·Intelによってソフトエラーメカニズムが明らかになる

- 1996 ·IBMが宇宙線中性子ソフトエラー研究結果を発表

- 1998 ·NASAが耐放射線ラッチ方式発表(NASA Symp.)

- **2000** ·Intelが耐放射線ラッチを発表(VLSI) ・サーバーの突然のクラッシュ問題が米国で浮上

- ・応用物理学会で国内発のシンポジウム開催

- 2001 ·JEDEC(Joint Electron Device Engineering Council)が中性子ソフトエラー標準試験法策定

- 2002 ·JEITA (Japan Electronics and Information Technology Industries Association)にSER委員会発足

- **2003** ·Intelが耐放射線ラッチを発表(CICC)

- 2004 ·STARCが耐放射線ラッチを発表(ISSCC)

# 背景

- ノイズ発生粒子とノイズ電荷

- ✓アルファ線 15fC/um

- ✓中性子線 150fC/um

- 論理回路の微細化と低電圧化

- ✓臨界電荷量の低減

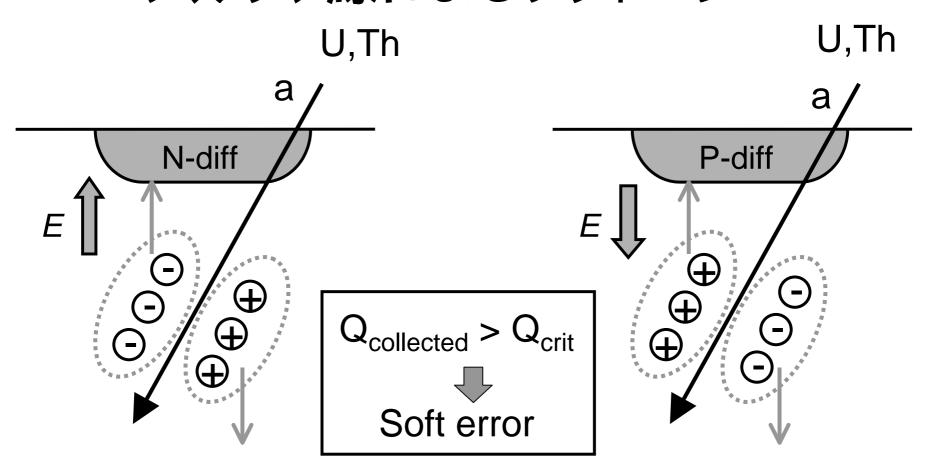

### アルファ線によるソフトエラー

- LSI構成材料中の不純物(Uranium, Thorium)から放射

- ノイズの極性は接合の極性に依存

- ノイズ電荷発生量 15fC/um

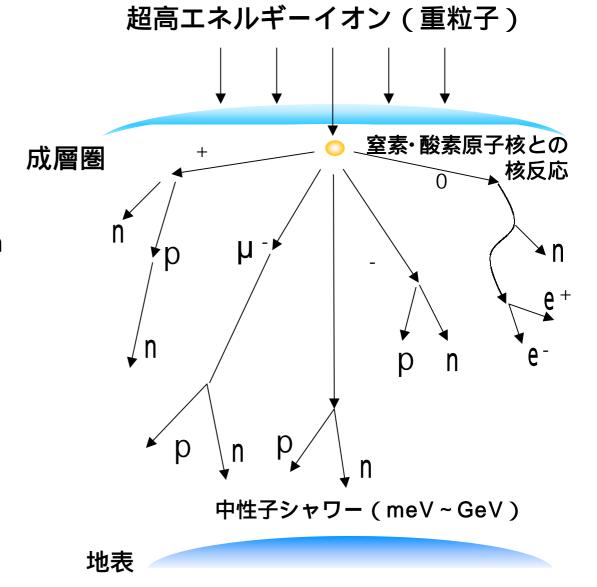

# 中性子の発生

大気圏外: 0.1 particles/cm<sup>2</sup>/s

飛行高度(9000m): 7200 neutrons/cm<sup>2</sup>/h

海面レベル(0m): 20 neutrons/cm<sup>2</sup>/h

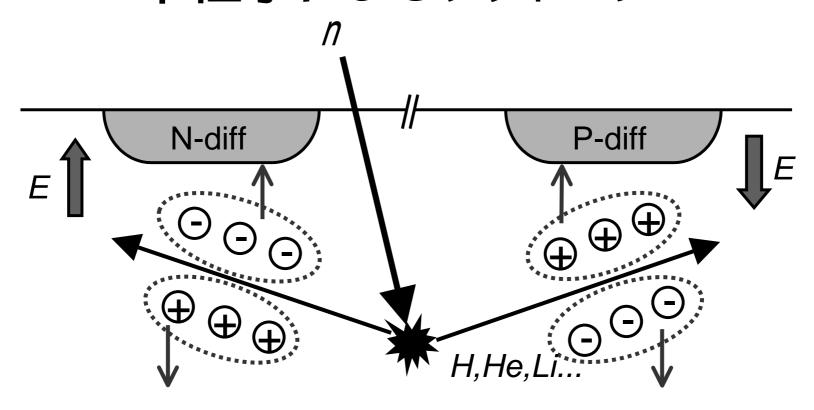

# 中性子によるソフトエラー

- 宇宙線により生成された中性子が半導体に進入

- Si原子との核反応により、多数の高エネルギ粒子を生成

- ノイズの極性は接合の極性に依存

- ノイズ電荷発生量 150fC/um

# ソフトエラーの水準

■ ITRS2000 勧告

√ソフトエラー率 < 1000FIT

</p>

(1FIT=109 Device·h)

### メモリの状況

- SRAMに問題が顕在化

- ✓DRAMはQnを減らさない回路方式

- ✓SRAMは微細化低電圧化によりQnが減少

- ECCによるデータ補正

- ✓2次、3次キャッシュにECC(Intel, 2002 ISSCC)

- ✓中性子による複数ビットエラーに対処した ECC方式(日立、2003 ISSCC)

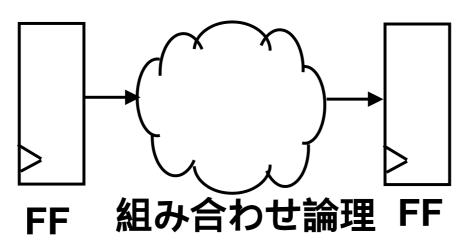

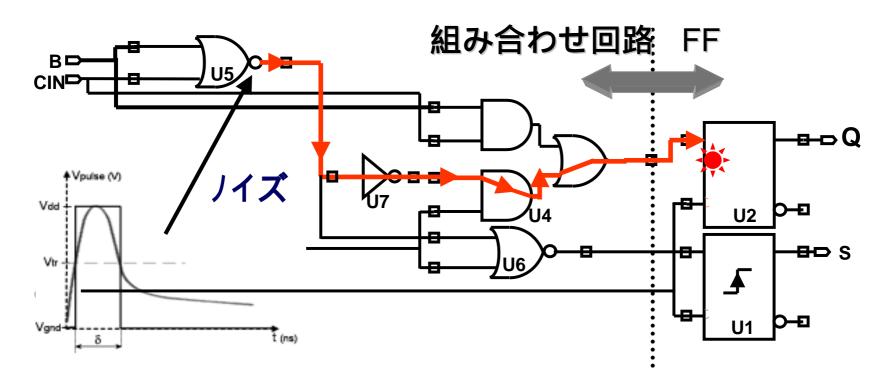

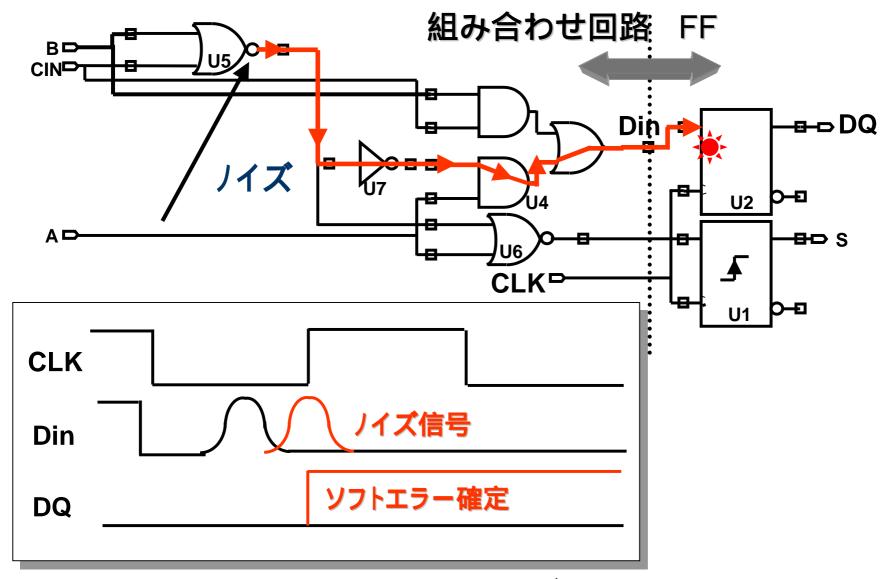

### 論理回路のソフトエラー

■ 組み合わせ論理回路のソフトエラー ✓内部ノードの電位が一時的に反転

■ フリップフロップ回路のソフトエラー ✓ラッチのデータ保持部の情報が反転

# 組み合わせ論理回路のソフトエラー SET(Single Error Transient)

■ ノイズによってデータが一瞬反転する。 この反転がラッチに取り 込まれるとエラーになる。

# エラー信号のFFへの取り込み

エラー率は、クロック周波数、ノイズパルス幅に依存

**Work in Progress - Do not publish**

STRJ WS: March 4, 2004

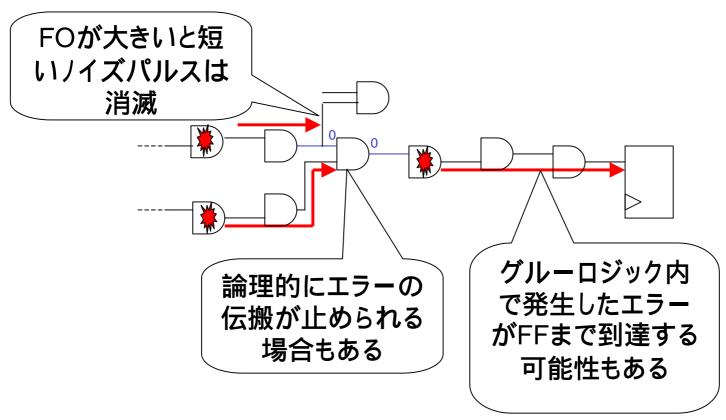

### ソフトエラーの緩和現象

- ノイズパルス波 > > 周波数 基本的に論理回路は修正される。

- ノイズ自体の減衰 ノイズが伝搬しない。

- 動作時の論理(AND等) FFまで伝搬しない。

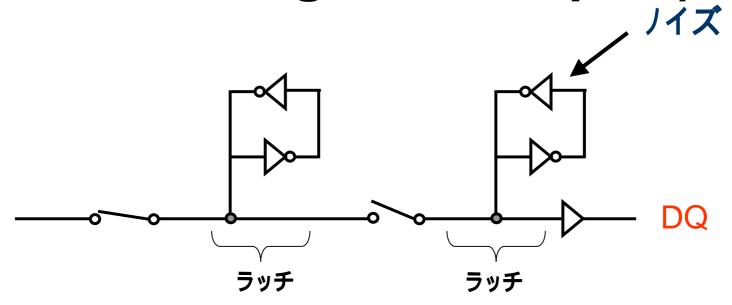

FFのソフトエラー SEU(Single Error Upset)

• **FF回路**Qnoise>Qcritでデータが反転

### SEUによるソフトエラー率の見積

Process scaling makes: 104

- Q<sub>crit</sub> small

- Sensitive area/chip large

- Transistor size shrinks

- However, the number of transistors on a chip increases

[Chip Size:100mm<sup>2</sup>, Latch:14mm<sup>2</sup>]

SER keeps increasing

**Work in Progress - Do not publish**

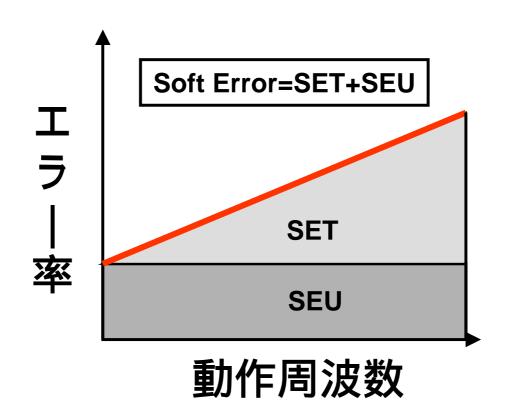

# 論理回路のソフトエラー率の傾向

3GHz/65nm辺りからSETの問題も顕在化する。

# 各社の取り組み

- 論理回路:Boeing、NASDA

- <u>ラッチ回路: NASA, Intel, IBM</u>

- **■** STARC

### STARCの低電力技術開発

- ロジック、アナログ、メモリの超低電圧動作

- Digital

- 0.5V digital circuit

- Power Management

- Analog

- 1V operation ADC

- Noise suppression scheme

- Memory

- 0.5V operation on-chip RAM

# 超低電圧動作のメリット・デメリット

- 各種リーク電流の低減 ゲートトンネルリーク、GIDL,BIDL

- 信頼性 EM,SM,HC,NMT

- × SER

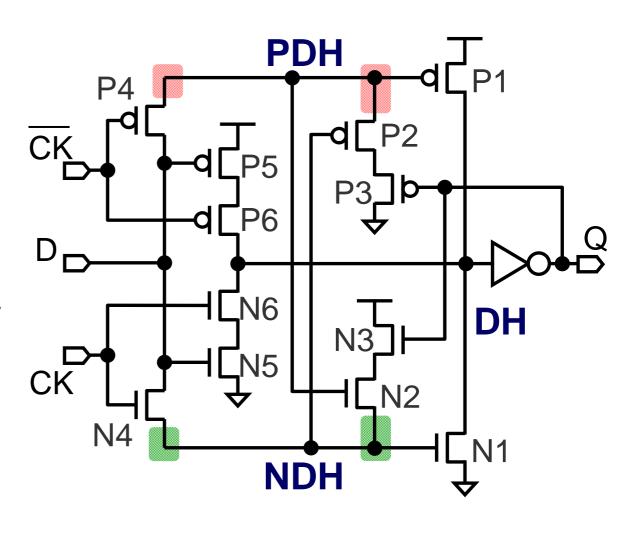

# 耐ソフトエラーラッチ回路(STARC提案)

- Error correction circuit

- P2, P3 for PDH

- N2, N3 for NDH

- Error separation

- PDH: 0 → 1 error

- NDH: 1→0 error

- Feedback path cut off function

- no error propagation

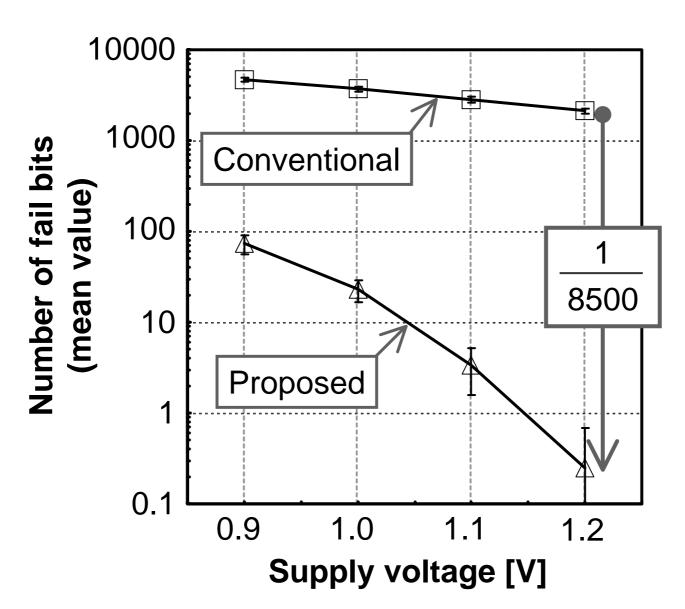

# アルファ線照射実験結果

# 結論

- 論理回路のソフトエラー

- ✓組み合わせ論理回路 動作周波数依存

- ✓ラッチ回路 Qc依存

- **✓90nm時点で1000FITを超えるレベル**

- 耐放射線ラッチ回路の提案