# 新材料導入ロードマップ

High-k & メタルゲート同時導入に向けて

2006年3月10日 窪田 通孝 (ソニー) 奈良 安雄 (Selete)

## 内容

(1)2005年度活動紹介: <u>窪田</u> ITRS2005の主な変更点

(2)技術動向報告: 奈良 High-k & メタルゲート同時導入可能性について

### FEP WGメンバー

リーダ: 窪田通孝 (ソニー)

サブリーダ: 丹羽正昭(松下)\*

水島一郎 (東芝)\*

幹事: 中西俊郎(富士通研)

委員: 藤原英明(三洋)

内田英次 (沖):米国Surf. Prep. WG

藤原伸夫(ルネサステクノロジ)

北島洋(NECエレクトロニクス)

三冨士道彦(ローム)

奈良安雄(Selete)

特別委員: 河村誠一郎(産総研)\*

大形俊英(日立ハイテクノロジーズ):SEAJより

河野光雄(コマツ電子金属)#:新金属協会より

中嶋 定夫(日立国際電気):SEAJより

渡辺正晴(ニューフレアテクノロジー)#:米国Start. Mat. WG

\*:国際対応

#:次世代大口径ウェーハ

検討小委員会参加

## 2005年度活動

### ITRS2005(大改定の年)

Stacked DRAMとFeRAMをPIDSと協力し改訂。 FEP全体の見直し。 450mmウェーハ関係(Position Paper)。

## 技術動向調査(全10回)

担当領域が広範囲に及ぶため、各分野のヒアリングを積極的に行い、最新技術動向を把握。

### **450mmウェーハ**

次世代大口径ウェーハ検討小委員会への貢献。

# **Starting Materials**

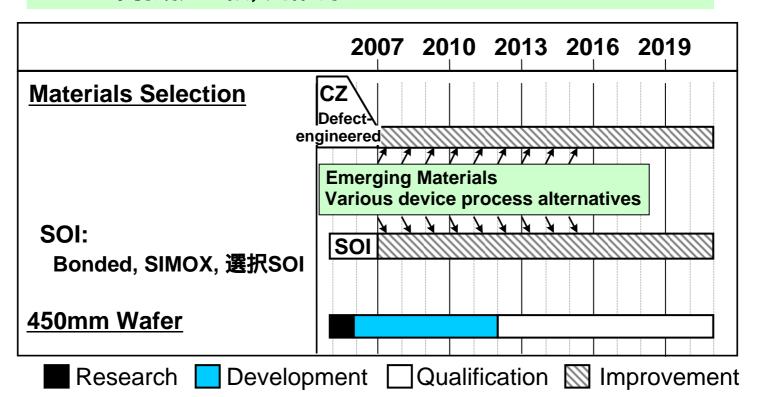

#### ITRS2005における顕著な変更点

Emerging Materials記載追加(Sub-chapter text)

- ·熱伝導制御: Si/Diamond, Si/SiC, Si/AIOx, 同位体Si

- ·移動度増加: 歪Si, ゲルマニウム, 結晶方位, CN

- ·SoC:高抵抗基板,光配線

**Work in Progress - Do not publish**

STRJ WS: March 10, 2006, WG3 FEP

## **450mmウェーハ技術**

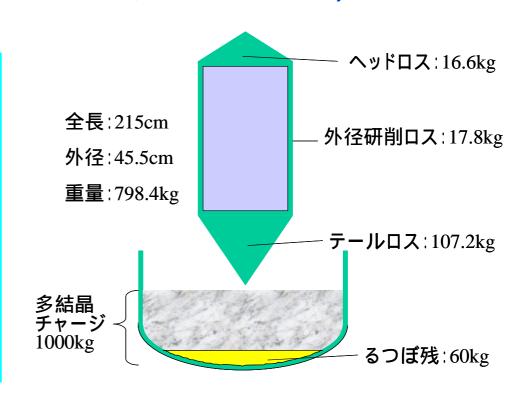

#### 450mmウェーハに関するポジションペーパー追加

- ·歴史展望

- ・450mmウェーハ形状予測

- ・課題(引上げ、多結晶Si原料、ウェーハ加工)

・経済性とその課題

#### <u>ウェーハ・50!分科会</u>

- 450mmの技術的側面を検討が3月で中断

- ・装置開発用メカニカルウェーハ仕様策定に着手

- 2006年度はJEITAシリコン技術委員会のWGで議論を継続する

#### ITRS2005における表面処理に関する変更点

- 1. Siおよび酸化膜ロス許容量の低減

- 2. ウォーターマーク基準の再登場

- 3. その他の値は変更なし、または小幅修正

|     |                                  |      | Near-term |      |      |      |      |            | Langterm |      |      |      |      |      |      |      |      |

|-----|----------------------------------|------|-----------|------|------|------|------|------------|----------|------|------|------|------|------|------|------|------|

|     | Year of Production               | 2005 | 2006      | 2007 | 2008 | 2009 | 2010 | 2011       | 2012     | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 |

| Was | Siliconloss (Å) per deaning step | 0.8  | 0.7       | 0.5  | 04   | 04   | 04   | 04         | 04       | 04   | 04   | 04   | 0.4  | 0.4  | 0.4  |      |      |

| ls  | Siliconloss (Å) per deaning step | 0.8  | 0.7       | 0.5  | 04   | 04   | 0.3  | 03         | 0.3      | 0.2  | 0.2  | 02   | 02   | 0.2  | 02   | 02   | 02   |

| Was | Oxide loss (Å) per dearing step  | 0.8  | 0.7       | 0.5  | 04   | 04   | 04   | <b>Q</b> 4 | 04       | 04   | 04   | 04   | 0.4  | 04   | 04   |      |      |

| ls  | Oxide loss (Å) per dearing step  | 0.8  | 0.7       | 0.5  | 04   | 0.4  | 0.3  | 0.3        | 03       | 0.2  | 0.2  | 02   | 02   | 0.2  | 02   | 02   | 02   |

| ls  | Allowable watermarks             | 0    | 0         | 0    | 0    | 0    | 0    | 0          | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

### FRONT END ETCH

#### ITRS2005におけるゲートCD精度に関する変更点

- 1.CD要求精度緩和

- 2. レシ'ストCD値増加

- 3. Litho/Etch分配比率变更

(1.2.は、Industry survey に基づく)

許容CD(3 )は、Etch 35%、Litho.18%緩和された(ITRS2003比)。 Red Brick Wallは2007年に後退。

| ITRS2005での変更要点 | 2003  | 2005     |

|----------------|-------|----------|

| Gate CD精度      | ± 10% | ± 12%    |

| Resist CD(りム前) | 1     | 1.2(相対比) |

| Litho/Etch分配   | 80/20 | 75/25    |

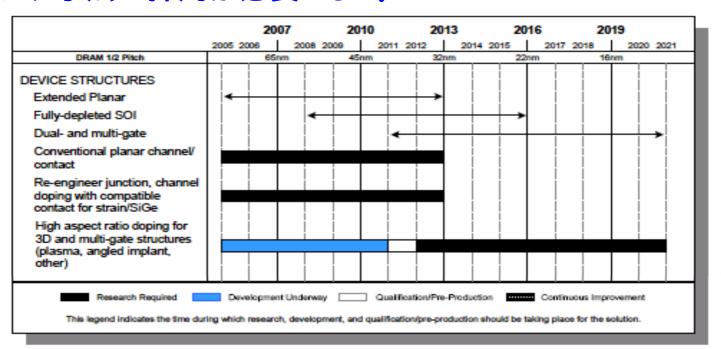

## Doping and Junctions

- EOTのスケーリングの鈍化により、接合形成における要求深さはさらに浅くなっているが、その値は MOSFETの動作に対して、浅い接合深さと低いシート抵抗と両立できるぎりぎりのところまで来ている。

- ・将来の三次元構造のデバイスにおいては、その構造に対応可能なドーピング手法の採用が必要となる。

# Stacked-Capacitor DRAM Changes in 2005

| tear of Production      | 04                                                 | US                | Ub                 | 07 | 08  | 09                  | 10     | 77  | 12     | 13     | 14  | 15   | 70    | 17     | 10    | 19    | 20   |

|-------------------------|----------------------------------------------------|-------------------|--------------------|----|-----|---------------------|--------|-----|--------|--------|-----|------|-------|--------|-------|-------|------|

| Cell size factor a      |                                                    |                   |                    | -  | -   | -                   |        |     |        | -      |     |      | -     | -      |       |       |      |

| 2003/2004 ITRS          | 8.0                                                | 7.5               | 7                  | 7  | 6   | 6                   | 6      | 6   | 6      | 6      | 6   | 6    | 6     | 5      | 5     |       |      |

| 2005 ITRS               |                                                    | 8                 | 8                  | 8  | 6   | 6                   | 6      | 6   | 6      | 6      | 6   | 6    | 6     | 6      | 6     | 6     | 6    |

| Dielectric constant     |                                                    |                   | -                  |    |     |                     |        |     |        |        |     | -    |       | •      |       |       |      |

| 2005 ITRS               | 22                                                 | 40                | 50                 | 50 | 50  | 50                  | 50     | 60  | 60     | 60     | 80  | 80   | 80    | 100    | 100   | 100   | 10   |

| Capacitor dielectric ma | apacitor dielectric material – potential solutions |                   |                    |    |     |                     |        |     |        |        |     |      |       |        |       |       |      |

| 2003/2004 ITRS          | ALO/TAO                                            | ALO<br>/TAO       |                    |    | ALO | /TAC                | ) /oth | ers | <br>   | ]<br>I |     |      | new   | mat    | erial |       | <br> |

| 2005 ITPS               |                                                    | Al <sub>2</sub> O | <sub>3</sub> , HfO | 2, | Ta  | O <sub>r</sub> . Ti | 0.     | ult | ra-hiç | gh-k,  | new | mate | rials | , stro | ntiun | n-bas | ed,  |

・キャパシタ絶縁膜の材料選択は、継続的な課題となっている。

perovskites

Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>

$Ta_2O_5$

**2005 ITRS**

## Flash Memory

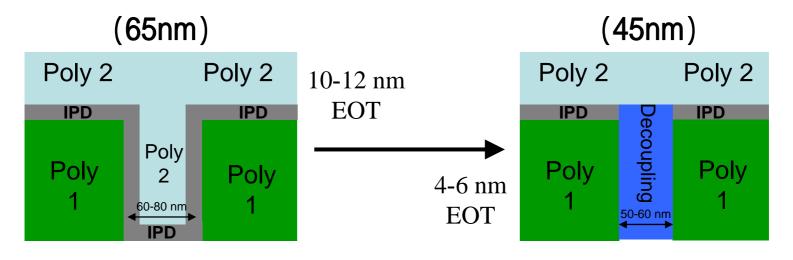

・ 45-50nm世代以降において、線幅の縮小、およびカップリング比の維持のため、インターポリの薄膜化が必要となる。

- ONO (Oxide-Nitride-Oxide) ではEOTのスケーリングは困難であり、high-k膜等の新材料が必要。

- あるいは、SiNに電荷を蓄えるような新しい構造の採用が考えられる。

- STIに関しては、浮遊ゲート形成後の形成となるされることがあり、また動作電圧が高いため、logicデバイスよりも高いアスペクト比の埋め込みが必要。

### FeRAMの変更点と2006に向けた課題

#### ITRS2005における変更点

- 記憶容量を削除し、単体、混載に関わらず2社月産1万個に到達したFeature size で規定した。

- 強誘電体材料からくる電荷量の上限30uC/cm²に達した時点、すなわち2010年に3D化が必要と判断。

### ITRS2006updateに向けて

• 量産ベースFeRAMの継続的調査。

| Year of Production                                               | 2005  | 2006  | 2007  | 2008  | 2009  | 2010  | 2011  |

|------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Feature size (μm) [A]                                            | 0.13  | 0.11  | 0.1   | 0.09  | 80.0  | 0.065 | 0.057 |

| Cell area factor: a [D]                                          | 34    | 34    | 30    | 30    | 30    | 24    | 24    |

| Capacitor active area (µm²)                                      | 0.32  | 0.23  | 0.158 | 0.128 | 0.101 | 0.076 | 0.069 |

| [G]<br>Cap active area/footprint ratio<br>[H]                    | 1     | 1     | 1     | 1     | 1     | 1.55  | 1.85  |

| Capacitor structure [J]                                          | stack | stack | stack | stack | stack | 3D    | 3D    |

| Minimum switching charge density (μC/cm²) at V <sub>op</sub> [M] | 11.4  | 14.2  | 19    | 22    | 26    | 30    | 30    |

## High-k & メタルゲート同時導入に向けて

#### 内容

- 1. ITRS2005の概要(ゲートスタック)

- 2. High-k & メタルゲート同時導入に向けて

- High-k/メタルゲートの技術動向

- 2008年同時導入は可能か?

# ITRS2005における主な変更点(1)

### 1.High-k/メタルゲートの実用化時期を2008年に延期

| 新技術                | ITRS2003 | ITRS2005       |

|--------------------|----------|----------------|

| Enhanced mobility  | 2004     | 2004           |

| High-k (Low power) | 2006     | 2008 ]         |

| High-k (MPU)       | 2007     | 2008 2008年に重要な |

| Metal gate         | 2007     | 2008 新技術を導入    |

| FD-SOI             | 2008     | 2008           |

#### 実用化時期延期の理由:

- 1. Enhanced mobility技術の実用化

- 2. ローパワーデバイスのCV/Iの増加率緩和(17%/year 14%/year)

# ITRS2005における主な変更点(2)

### 2. メタルゲートの仕事関数値をデバイス毎に規定

Metal gate仕事関数要求値のまとめ(年代によらず一定)

Bulk: バンド端から0.2eV以内

FD-SOI: Ei  $\pm$  0.15eV(HP), Midgap (LOP), Ei  $\pm$  0.1eV (LSTP)

Multi-gate: Midgap (HP, LOP), Ei ± 0.1eV (LSTP)

#### Bulk LSTPの例

| Year of Production                                                                                                | 2005    | 2006    | 2007    | 2008    | 2009    | 2010    | 2011    | 2012    | 2013    |

|-------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| DRAM ½ Pitch (nm) (contacted)                                                                                     | 80      | 70      | 65      | 57      | 50      | 45      | 40      | 36      | 32      |

| Physical gate length low standby power (LSTP)                                                                     | 65      | 53      | 45      | 37      | 32      | 28      | 25      | 23      | 20      |

| Vdd:Power supply voltage (V)                                                                                      | 1.2     | 1.2     | 1.2     | 1.1     | 1.1     | 1.1     | 1       | 1       | 1       |

| Equivalent physical oxide thickness for bulk low standby power $T_{ox}$ (nm) for 1.5E20-doped poly-Si [A, A1, A2] | 2.1     | 2       | 1.9     | 1.2     | 1.1     | 1       | 1       | 0.9     | 0.8     |

| Equivalent physical oxide thickness for bulk low standby power $T_{ox}$ (nm) for metal gate [A, A1,               | 2       |         | 11.0    | 1.6     | 1.5     | 1.4     | 1.4     | 1.3     | 1.2     |

| Gate dielectric leakage at 100°C for bulk (A/cm²)<br>LSTP [B, B1, B2]                                             | 1.5E-02 | 1.9E-02 | 2.2E-02 | 2.7E-02 | 3.1E-02 | 3.6E-02 | 4.8E-02 | 7.3E-02 | 1.1E-01 |

| Metal gate work function for bulk LSTP  E <sub>c,v</sub> – f   (eV)  S                                            |         |         |         | <0.2    | <0.2    | <0.2    | <0.2    | <0.2    | <0.2    |

# High-k材料

merits/demerits of HfO<sub>2</sub>, nitrided HfO<sub>2</sub>, Hf-silicates, and HfSiON (my interpretation - pseudo-ternary alloy)

| dielectric                   | 'merits'                                                                                                                                                           | 'demerits'                                                                  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| HfO <sub>2</sub>             | "only good thing about<br>high-k's are their high<br>values of k" Bob Wallace                                                                                      | nanocrystalline-intrinsic<br>defects: O-vacancies &<br>grain boundary traps |  |  |

| nitrided<br>HfO <sub>2</sub> | none, that I know of!!                                                                                                                                             |                                                                             |  |  |

| Hf<br>silicates              | non-crystalline as-<br>deposited, but                                                                                                                              | inherent network<br>disruption - chemical<br>phase separation               |  |  |

| 'HfSiON'                     | if done <i>right*</i> - a viable<br>3rd generation solution!<br>*ternary alloy, with high<br>Si <sub>3</sub> N <sub>4</sub> content - stable to<br>at least 1100°C | k ~8-10, but<br>with high CB offset<br>enough for<br>EOT to ~ 0.7-0.8 nm    |  |  |

G. Lucovsky (2<sup>nd</sup> International Workshop on Advanced Gate Stack Technology, 2005)

### HfSiONとHfO2にほぼ絞り込まれた。

- HfSiON: 熱安定性高〈CMOSプロセス適合性良好

- HfO2: 誘電率高く(HfSiON比較)膜厚スケーリングに有利

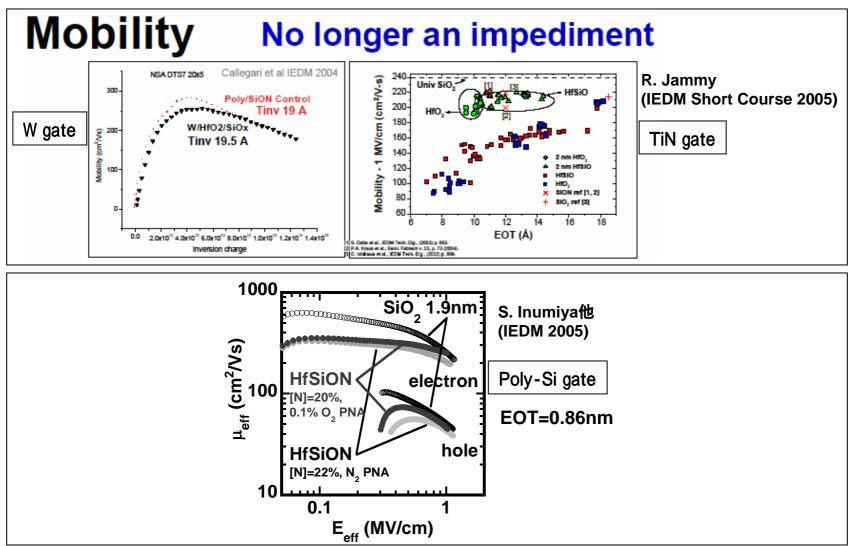

# High-k膜の電気的特性

EOT (<0.9nm)、移動度もほぼ問題ないレベル

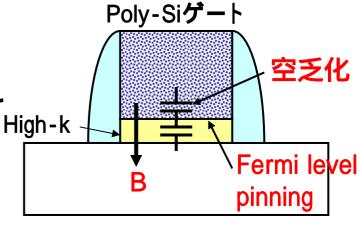

# メタルゲートの導入とその課題

#### メタルゲート導入のメリット(従来のPoly-Siゲートと比較して)

- ゲート空乏層(約0.3nm相当)による薄膜化阻害を解消

- ゲート不純物(特にボロン)のチャネルへの突き抜けなし

- -Vth制御性改善

(High-kとの組み合わせにおけるFermi Level Pinning解消)

#### メタルゲート技術の課題

- -材料選択

- ・NMOS、PMOSのVthに適する材料

- ・成膜などプロセス技術構築

- -インテグレーション方式

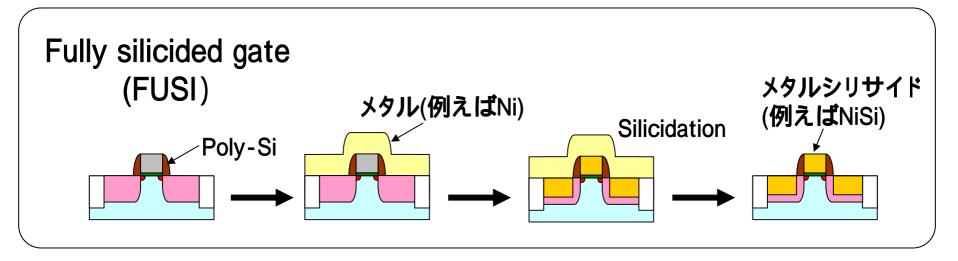

- FUSI (Fully silicided)

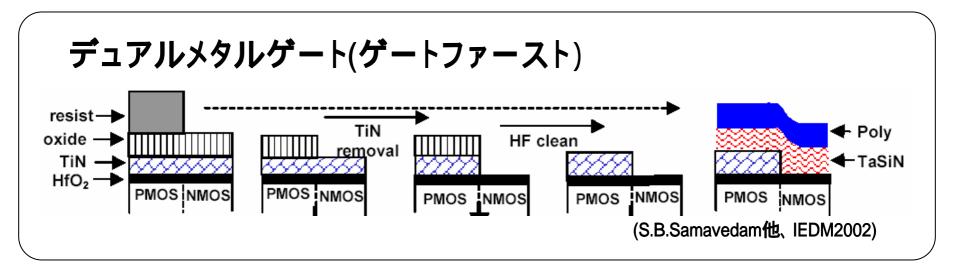

- ·デュアルメタル (ゲートファースト/ゲートラスト)

## メタルゲート形成方式

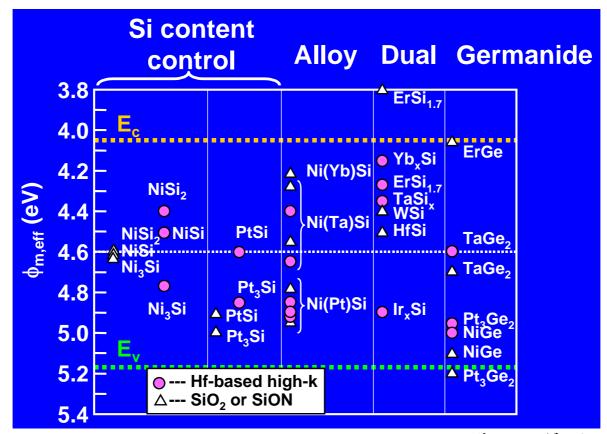

## 種々のFUSIの実効仕事関数

生田目 (ゲートスタック研究会 2006)

- Poly-Siゲートと同様にFermi level pinning発生 (バンドエッジ近傍の仕事関数が得られていない)

- High-k上での仕事関数制御法が大きな課題

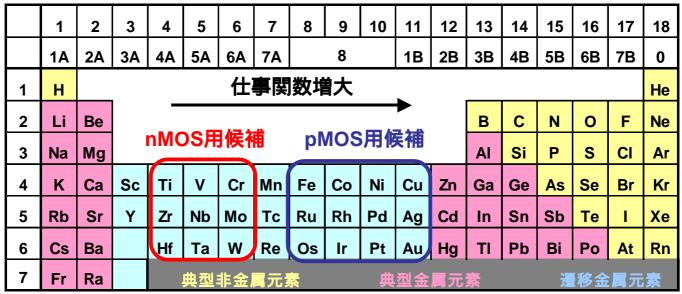

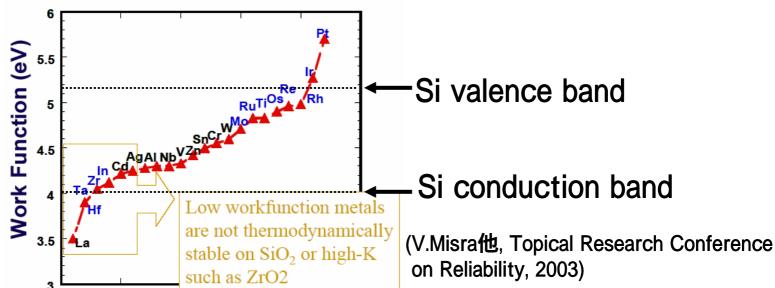

# FUSI以外(デュアルメタル)のゲート材料

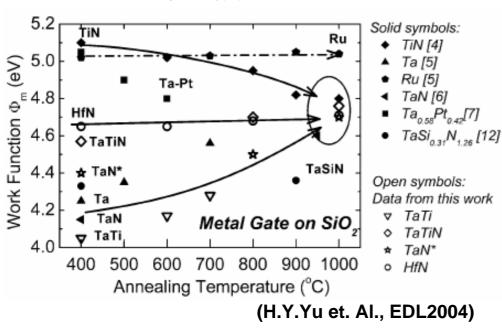

# デュアルメタルゲートの課題

#### 実効仕事関数の変動

#### EOTの増大

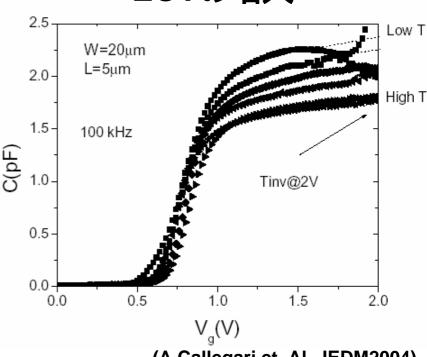

(A.Callegari et. Al., IEDM2004)

- メタル材料の絞込みが不十分

- 耐熱性(実効仕事関数、EOT)の確保

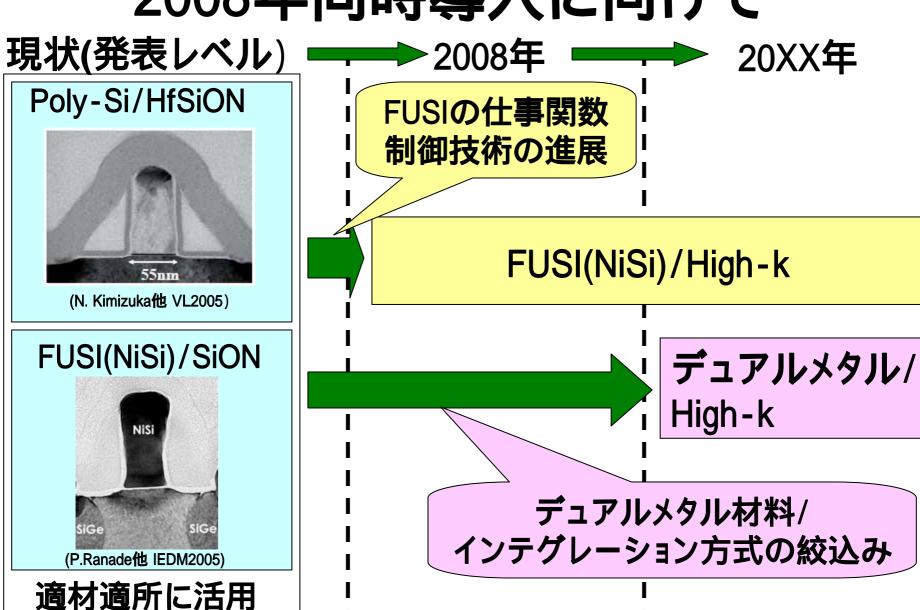

## 2008年同時導入に向けて

## まとめ

#### Hf系High-k**膜はほぼ**Ready

- 材料: HfSiON or HfO<sub>2</sub>

- EOT<0.9nm、移動度=SiO<sub>2</sub>の90%程度

- Vth制御性(Fermi level pinning)により現状では 用途は限定

### High-k+メタルゲート技術は課題多い

- まずは、High-k、メタルゲートそれぞれの特徴を 生かせるデバイスで活用の方向

- FUSIのFermi level pinning対策を加速すべき

- デュアルメタルゲート: 材料絞込み/インテグレーション方式の決定