# 微細化/複雑化の設計への影響

- 回路パス遅延ばらつきのロードマップ化 -

- 設計遅れ要因変化の分析 -

2007年 3月 9日

JEITA半導体技術ロードマップ専門委員会(STRJ) 設計ワーキンググループ (WG1)

# 2006年度メンバ 設計WGメンバ

新メンバ

柏木 治久(リーダ) 半導体理工学研究センター 隅谷 三喜夫(サブリーダ) 松下電器産業 樋渡 有(国際対応) 東芝 山田 明宏(幹事) トッパン・テクニカル・デザインセンター 山本 一郎 沖電気工業 向野 守 三洋電機 豊田 忠雄 シャープ 大川 和彦 セイコーエプソン 柿本 勝

古井 芳春 半導体理工学研究センター 富重 了一 トッパ、ン・テクニカル・テ、サ、インセンター 松崎 正己 富士通 塩月 八宏 半導体理工学研究センター 浅井 健史 ローム 小野 信任 ジーダット・イノベーション 今井 正治 大阪大学 藤波 義忠 NECエレクトロニクス 中山 勝敏 ルネサステクノロジ

### 用語集

- <u>RTL</u>: <u>Register Transfer Levelの略。回路をフリップフロップ + 組み合わせ論理回路で表現したレベルのこと. 現在の論理回路設計はおもにこのレベルの記述を使用する.</u>

- <u>SLD</u>: System Level Designの略

- <u>L/C/P</u>: <u>L</u>ogic/<u>C</u>ircuit/<u>P</u>hysical Designの略

- <u>DFM</u>: <u>D</u>esign <u>F</u>or <u>M</u>anufacturabilityの略

- <u>DFT</u>: <u>D</u>esign <u>F</u>or <u>T</u>estの略

- **PMBOK**: (Guide to) **P**roject **M**anagement **B**ody **O**f **K**nowledgeの略。プロジェクトマネジメント知識体系で、業種/分野の特異性を排除している。

- <u>CMM</u>: <u>Capability Maturity Modelの略。組織のソフトウェアプロセスの成熟度を示すリファレンスモデル。

</u>

- <u>DPAM</u>: <u>Design Process Assessment and improvement Modelの略。日本企業の設計プロセスの特徴を考慮した設計プロセス評価モデルのこと。</u>

- <u>SW/HW協調設計</u>:システムを構成するハードウエア部とソフトウエア部を,システムの性能やコストなどの観点から最適となるように協調して設計すること。

- 高位合成: C/C++などのアルゴリズム記述から、RTLを自動的に合成すること。

- <u>設計手法(メソドロジ)</u>:設計を行うための、統合された一連の設計フロー、手順、方法のこと。

- <u>構成管理</u>:プロジェクトの成果物の版数管理のこと。これができないと、古いバージョン のデータが紛れ込んだりする。

- **IPコア**: SOCを構成する機能ブロックのこと。

- ・ <u>Pelgromモデル</u>:トランジスタ特性のばらつきモデルとして広く用いられてきたモデル。

仕様

SLD <

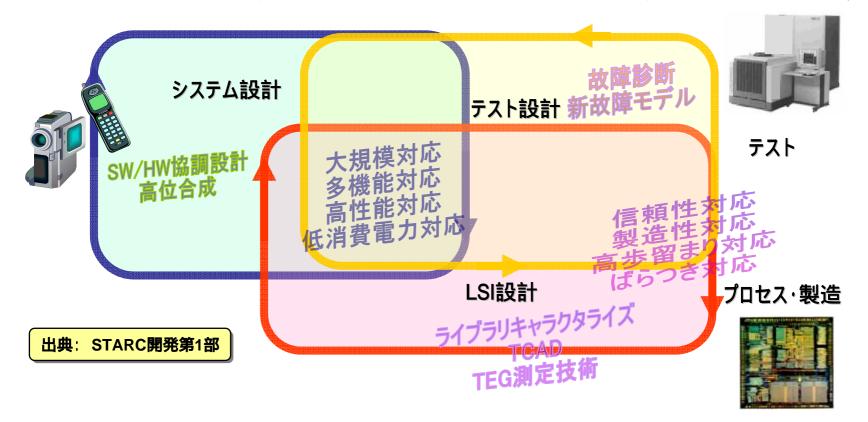

設計WGのスコープ

- System Level Design

- 仕様からRTL記述を生成する。

- Logic / Circuit / Physical Design

- RTL記述から製造可能な設計品質のレイアウト データ(GDS) を生成する。

- Design Verification

- RTL記述の機能と性能を、仕様に基づき検証する。

- Design For Manufacturability

- プロセスの物理現象モデルに基づき、製造可能性/歩留まりを検証/最適化する。

# 設計WGの特徴

- ・分野が広い

- -SLDからDFMまで一人でカバーできる人 はいない。

- ・全員参加のテーマは「広く、浅く」になる。

- ・特定技術テーマの深耕はSWG活動になる。

- -関係分野が多岐にわたる。

- ・DFM プロセス

- ・SLD 組込み機器、組込みソフトウェア

- L/C/P DFT、プロセス

## ミッション

### • 国際活動

- ITRSのSystem Drivers章とDesign章を設計 TFと分担

- System Drivers章

- ITRSのすべての技術分野をドライブするLSI商品を定義

- Design章

- 設計技術に対する将来課題と課題解決策の提示

### • 国内活動

- SOC構造・規模を時間軸で定量化しロードマップ検討の基礎として提示

- 設計技術課題を時間軸で定量評価し解決策を 提案(設計技術ロードマップ)

## 2005、2006年度活動

|        | 国際活動                                                                             | 国内活動                                                                                                      |

|--------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 2005年度 | System Drivers章<br>携帯Consumer SOCドライ<br>バを提案、採択。<br>Design章<br>課題項目の確認と<br>修正案提示 | SOC設計技術ロードマップの見直し<br>SLD,L/C/P,Verification,DFMの4サブワーキング<br>(SWG)による<br>·メッセージと重要な技術課題の明示<br>·課題抽出と解決策の提案 |

#### 微細化

ばらつきの影響増大 目標歩留達成困難 低消費電力設計の複雑化 イタレーションの増加

#### 複雑化

設計コスト/期間の増大 仕様変更の影響増大 品質確保と 検証効率の向上必要

### 2006年度

#### System Drivers章

据置Consumer SOCドライ バを提案、採択。

#### Design章

課題の項目値の確認と 修正案提示

#### DFM-SWGの深耕

SOC設計におけるプロセスばらつきの影響を定量化するための調査活動を行う。

# 設計遅れ要因変化の分析と提言

設計遅れ要因変化(3年間)の分析を行い、解決に向けて提言を行う。

# 2006年度国際活動

### 設計WGの国際活動

|                | update<br>方針            | ITRS2004                    | ITRS2005                                                               | ITRS2006          | ITRS2007                                  |

|----------------|-------------------------|-----------------------------|------------------------------------------------------------------------|-------------------|-------------------------------------------|

| System Drivers | マーケット<br>ドライバ<br>の追加    | 微修正1                        | Office/PC(US)与携帯Consumer与                                              | 据置Consumer        | Done Done Done Network(US) Automotive(EU) |

| Design         | 設計工程<br>毎の<br>課題定量<br>化 | DFM章追加<br>課題項目の確認と<br>修正案提示 | 課題定量化 +<br>課題解決策<br>System Level<br>L/C/P<br>Verification<br>DFT<br>DF | 課題定量化見直<br>し<br>/ | 見直し(継続)                                   |

# System Drivers章

#### 2005年度

#### **Consumer Portable**

- Consumer Portable SOC:パーソナ・ ル・モバイル機器の中核SOC

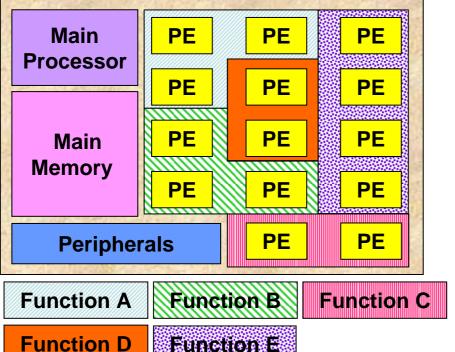

- 専用HW化により機能を低消費電力で実現するために、機能毎の専用エンジン (PE、Processing Engine)を複数搭載

**Work in Progress - Do not publish**

#### 2006年度

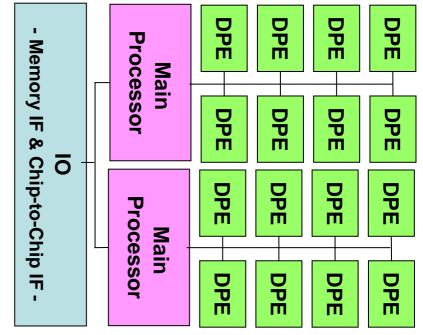

#### **Consumer Stationary**

- Consumer Stationary SOC: デジタルAV家電機器の中核SOC

- SWにより高度化の進む機能を柔軟に実現するため、SW実行環境として高演算能力を有するデータ演算エンジン(DPE、Data Processing Engine)を多数搭載

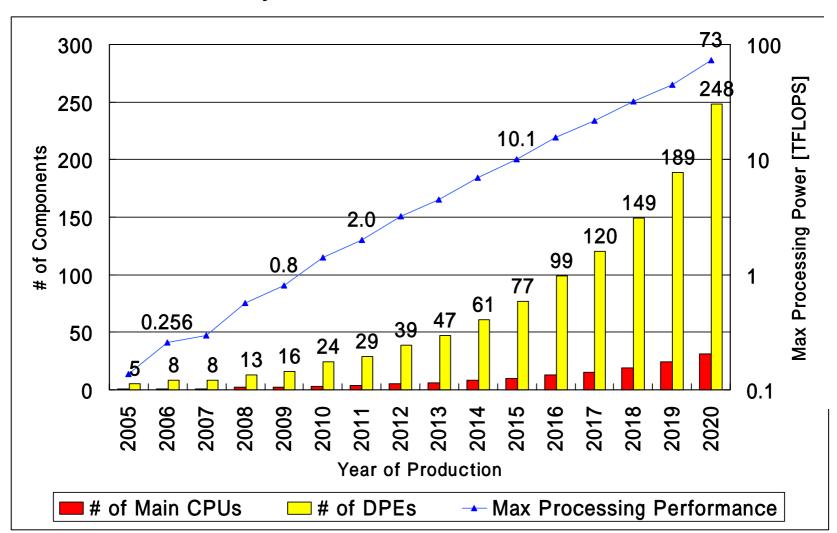

2006年度

# System Drivers章

• Consumer Stationary SOCのコンポーネント数とプロセッシング能力の推移

# Design章

### 設計WGの国際活動

2005年:項目内容確認

2006年:項目值確認

### ITRS2003 Design章

| New of Production                                  | .00  | 2004 | 300 | -   | 287  | 207 | 206  | 201 | 3911 | 304 | (free   |

|----------------------------------------------------|------|------|-----|-----|------|-----|------|-----|------|-----|---------|

| Schnigston                                         |      | 400  | 100 |     | 1947 |     |      | -   |      |     |         |

| Shart Shinh (rep)                                  | .100 | .00  | de  | -   | 81   | 188 | 40   | 98. | 10   | 10: |         |

| artheir stranger                                   | .101 | -    | 10. | =   | 107  | 10  | .10  | PT  | 41   | -18 |         |

| APT/Prometries larger prod                         | 40   | 30   | 40  | 40  | 185  | 84  | 24   | 200 | 411  | 36  |         |

| APTITION OF DOMESTICS                              | - 62 | 317  | 10. | 38. | 18.  | 188 | -27  | 100 | 10   | 2.0 |         |

| ECNI KISP (HE HARL)                                | tt.  | 12   | 13  | 12  | .12  | 12  | 0.75 | 14  | 18.  |     | 300     |

| 200 kg a Mit per dingran yann.<br>Il Pupin di anni | 1.8  | 28   | 13  | 43  | 14   | 7.4 |      | 388 | 784  |     | 30¢     |

| 200 ferror power technism.<br>Second coding (III.  |      | 9.1  | 0.1 | 82  | 82   | 0.2 | 0.2  | *   | 42   |     | 300     |

| ECC analy year nature<br>legal rating (II)         | 9.27 | 1.4  | 24  | 34  | 8.1  | 8.4 | 0.70 | -   |      |     | sec     |

| NACOWAN SET                                        | 20   | -    | 26  | =   |      | 40  |      |     |      |     | Mercani |

### ITRS2005 Design章

**SLD**

L/C/P

Verification

DFT

**DFM**

# 2006年度国内活動

### 1. 設計遅れ要因変化の分析と提言

- 2003年度調査との比較

- 微細化、複雑化の影響把握

- ・ 各社対策の効果確認

- ・ 設計遅れ撲滅への提言

### 2. DFM-SWG活動

- 最終目標: SOC設計へのばらつきの影響を定量化ップ(スピード、電力)

- ・ 今年度は、回路パスの遅延ばらつきを定量化

- 遅延ばらつきモデルの策定とブラッシュアップ

- 回路パスモデル、デバイス容量(C)モデル デバイス実効Rモデル、配線RCモデル

- PIDSとのクロスカット

- 回路パス遅延ばらつきを算出

# 1. 設計遅れ要因変化の分析と提言

- ・ 微細化、複雑化に伴い設計の難易度が高くなっている。これがSOC設計遅れにどのような影響を及ぼしているか?

- 2003年度調査との比較

- 微細化、複雑化の影響把握

- 各社対策の効果確認

- 設計遅れ撲滅への提言

| 年度   | 国内活動内容                                                       |

|------|--------------------------------------------------------------|

| 2003 | 設計遅れ起因の分析と提言<br>– 設計現場から課題を抽出 Time to market短縮への提言           |

| 2004 | 設計生産性ロードマップの策定 -ロードマップ策定のためのSOCモデルの設定 -課題抽出とポテンシャルソリューションの検討 |

| 2005 | SOCのハードウェア設計技術ロードマップ                                         |

| 2006 | 設計遅れ要因変化の分析と提言                                               |

# 2003年度の分析と提言

- 設計マネジメント

- SOC設計の特徴を踏まえたマネジメント技術の調査と確立

- マネジメント技術を普及させるために、 テキスト作成と資格認定制度の確立

- 設計スキル

- 電気(物理現象)の把握と潜在課題を 抽出する能力の育成 大学教育に期待

- 教育ツール:電気(物理現象)のテキスト、 トラブル事例集、 課題抽出の方法論

- EDA技術

- 実現すべき機能のロードマップ化と EDAベンダへの要求

- IDM内EDA部門の位置付けの変更 ツール評価 次世代技術の提示、 ドライブ

# 3年間の各社の対策

### • 設計マネジメント

- 設計マネジメント教育実施(PMBOK等)

- マネジメント体制の整備/強化(組織的リスク管理など)

- **チェック体制の整備/強化**(チェック専任組織など)

### 設計スキル

- 設計スキルの向上(設計教育、設計技能検定など)

- 検証技術力の強化

- **不具合事例の分析と情報展開**(失敗事例分析のデータベースなど)

### • EDA技術

- 新技術導入

- SW/HW協調設計、高位合成

- 設計メソドロジプラットフォーム

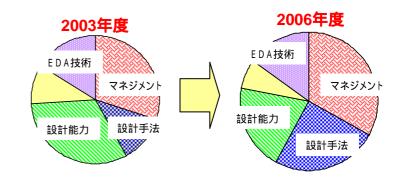

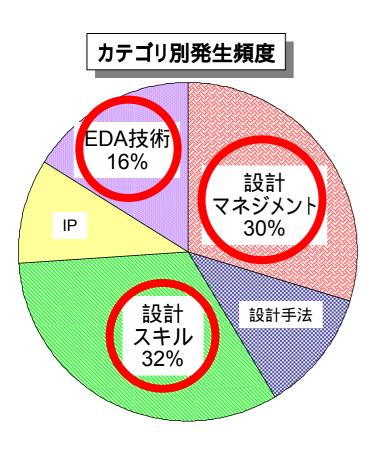

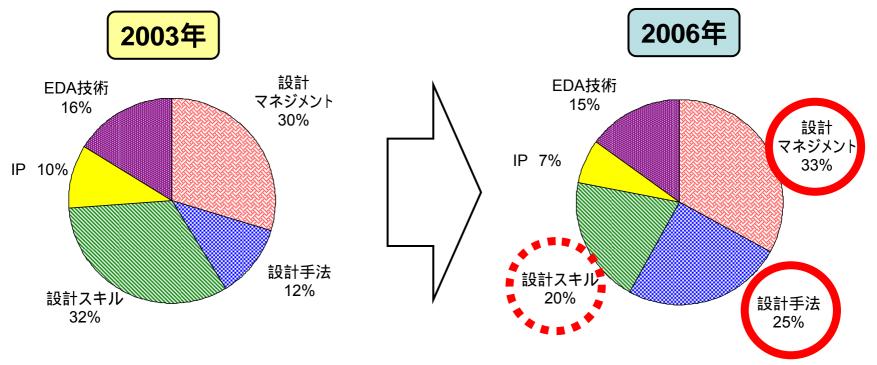

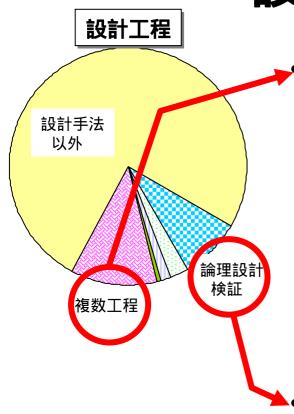

# 2006年度分析

- カテゴリの変化

- ─ 設計マネジメント原因がNo1に (+3%)

- 設計手法(メソドロジ)原因が増加 (+13%)

- 設計スキル原因が減少 ( 12%)

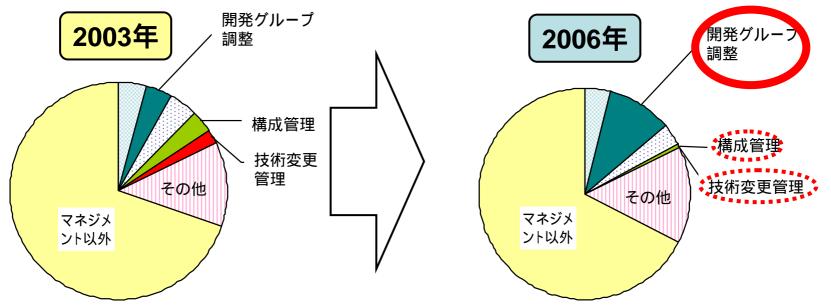

# 設計マネジメントの分析

- 構成管理、技術変更管理原因が減少

- 各社対策 の効果

- チェック体制の整備/強化が効き、初歩的な管理は行き届いてきた。

- 開発グループ調整原因が増加

- PMBOK等、マネジメント教育は 実施されているが、プロジェクト管 理の実践に結びついてない。

- 業務間の境界が曖昧、業務のスケジュール調整不足、リスク想定不足など、設計工程の複雑化にマネジメント力が追いついてない。

# 設計手法の分析

複数工程にまたがる手法原因が最も多い。うち半分がレイアウト設計工程を含む。

- DFM検証の違反をどこまで修正するか曖昧

- 微細化によるリーク電流対策、マルチVth、 電源分離などの処理により設計負荷増大

- コーナー条件が多く、タイミング収束の為の イタレーションが増大

あちらをたてれば、こちらがたたずという設計制約条件が、複数の設計工程にまたがって現れている。

単独工程では、論理設計検証工程の手法原因が多い。

- SOC機能の複雑度増大で検証漏れが発生

- 個々のブロック毎にDFT実施したため、 TOPでのDFT回路作成時に不整合発生

# その他の変化

### 今回の調査で新たに出てきた傾向を分析

RTL設計における、テ SW開発との連携問題 高位合成の適用問題 スト設計問題の発生 の発生 の発生 分 SOC全体としてのDFT戦 析 SW/HW協調検証など、 高位合成(C記述 RTL) 略など、テスト設計に関 SW開発との連携に関わ 適用による原因が3件あ わる原因がRTL設計原因 る原因が5件あった。 った。 27件中8件を占める。 課 SOC全体のテスト戦略 SW/HW協調設計手法 新技術導入 題

設計工程の複雑化を緩和する設計技術と設計手法の確立

# 課題と提言(設計マネジメント)

課題:設計工程の複雑化に対応できるマネジメント力

- PMBOK等、マネジメント教育は実施されているが、プロジェクト管理の実践に結びついてない。

- 設計工程複雑化に伴い、計画策定の重要性が増大

- 業務間の境界仕様が曖昧(IPコア/マクロ再利用/単体検証と統合検証)

- 業務間のスケジュール調整不足(SW/HW協調検証、テストベンチ作成)

- リスク想定不足(外部委託/新規開発の規模見積り)

- 後ろから切られる日程、仕様未確定のまま開発開始

提言:計画を重視したマネジメントの実践

# 提言(設計マネジメント)

### 提言:計画を重視したマネジメントの実践

- マネジメント手法としてPMBOK、CMM、指標としてDPAMなど様々なものが研究され、実在している。

- これらのマネジメント手法を活用して、設計現場として計画的な業務遂行を実践しなければならない。

### 計画重視を阻むもの

#### 1. 計画立案が困難

- 落ち着いて計画を立てられない

- リスクを読みすぎると、計画が成り立たない

- マネジメント技術の実践的な応用力が不十分

- 2. 無理な計画を強いられる

- 計画をたてても、リソースが確保できない

- 後ろから切られる日程

- 仕様未確定のまま開発開始

·SOC開発向けマネジ メントガイドの作成 ①

・プロジェクトマネージャの拒否権確保

# 課題と提言(設計手法)

# 課題:設計工程の複雑化を緩和する設計技術と設計手法の確立

- あちらをたてれば、こちらがたたずという設計制約条件が、複数の設計工程に 跨って現れて来ている。

- 複数の設計工程を繋げる設計手法だけでな〈、各工程で複雑化微細化に対応する技術開発(=EDA技術)も必要。

提言:全体最適なSOC設計手法の確立

# 提言(設計手法)

### 提言:全体最適なSOC設計手法の確立

- 複雑に絡み合うSOC設計要素を設計環境全体の中で捉え、全体最適化により SOCが確実に動作する高効率な設計手法を半導体業界で共同開発。

- 必要なEDA技術は、半導体業界がイニシアティブを持って、EDAベンダに要求。

# 分析と提言(まとめ)

|                                 | 設計マネジメント                                   | 設計手法                                         | 新たな傾向                                                         | 設計スキル                                                             |

|---------------------------------|--------------------------------------------|----------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------|

| 比率                              | 3 3 % (前回 + 3%)                            | 25%(前回+13%)                                  |                                                               | 20%(前回-12%)                                                       |

| <b>分析</b> A.複雑化微細化の影響 B.各社対策の効果 | A.開発グループ内調整原因が増加<br>B.構成管理、技術変更<br>管理原因が激減 | A.複数の設計工程にまたがる手法原因が多い。 A.単独では論理設計検証の手法原因が多い。 | A.テスト設計問題<br>の発生<br>A.SW開発との連<br>携問題の発生<br>A.高位合成の適<br>用問題の発生 | B.CADを使い<br>こなす力が向<br>上した。<br>・考慮すべき事<br>項を考え出す<br>力は向上して<br>いない。 |

| 課題                              | 設計工程の複雑化に対応できるマネジメント力                      | <br>  設計工程の複雑化<br>  術と設計手法の確立                |                                                               |                                                                   |

| 提言                              | 計画を重視したマネジメ<br>ントの実践                       | 全体最適なSOC設                                    |                                                               |                                                                   |

### 2.DFM-SWG活動

#### ■目標

▶最終目標

SOCの性能に対する「プロセスばらつき」の影響を、時間軸を持った形で定量化し、 課題解決に必要な設計技術を示すロードマップの作成

- ▶今年度目標:パス遅延ばらつき評価モデルの構築

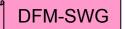

- ■パス遅延ばらつき評価モデル

- ▶パス遅延に対する、「プロセスばらつき」の影響を定量化するためのモデル

- ▶検討範囲内: 有用性を早期に示すために、モデルに取り込む要素は限定

- → 回路対象: パス(組み合わせ回路)

- がはらつき: デバイスばらつき

PIDS-WGとクロスカット討議のうえ、設計WGで「ばらつきロードマップ」を設定 ばらつきは、すべてチップ内のランダムと仮定

- ▶ 検討範囲外

- ^ クロック回路

- ル配線ばらつき

- ▲ ばらつきのランダムとシステマティック分離

STRJ WS: March 9, 2007, WG1 Design

DFM-SWG

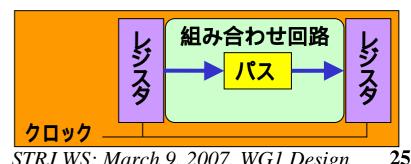

### パス遅延ばらつき評価モデル

STRI

:主要変数

∶算出過程

XX

- 入力: PIDS & Interconnect Roadmap、パス構造(設計WGで設定)

- ■出力:パス遅延

- 機能:パス遅延に対するばらつきの影響をモンテカルロ手法で評価

- ▶ New Roadmap Tableに基づき、変動量を乱数発生させ、パス遅延への影響を評価

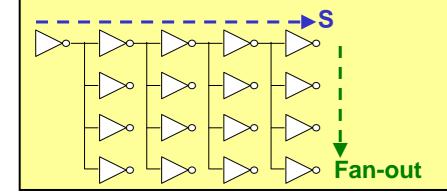

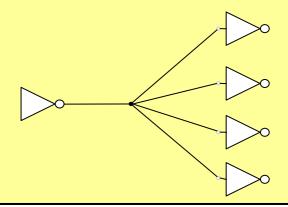

### パス構造

#### ■回路構造

▶簡単化のため、S段のInverterで構成

▶ 全パスで: S=8

▲ 高速回路部分を検討対象として設定

▶全段で: Fan-out = 4

#### ■レイアウト構造

▶接続構造:

5個のセグメント(下図: ~ )で構成

▶ セグメント長: 配線ピッチ×50

▶ 使用配線: Intermediate

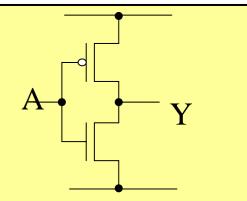

#### ■セル(Inverter)構造

▶ NMOS ゲート幅Wg: 配線ピッチの2.5倍

▶ PMOS ゲート幅Wg: NMOS-Wgの1.5倍

♠ 配線ピッチ = Intermediate Wiring Pitch

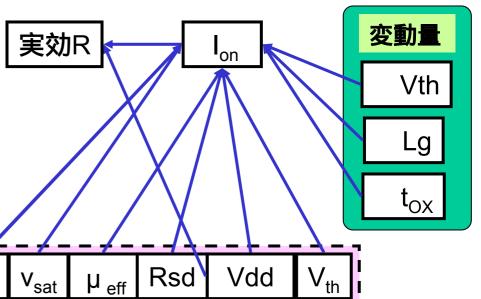

# 実効Rの算出

■実効R算出の目的: パス遅延の算出

■入力: PIDS-Table

■ばらつき評価: モンテカルロ手法実現のため、Vth、Lg、toxをランダムに変動

#### <実効Rの算出式>

$\mu_{\text{eff}} = \text{(Mobility Enhancement Factor for Idsat)} \times \text{(Ideal NMOS Mobility)}$

$$I_{\text{drain\_ideal}} = v_{\text{sat}} \, \frac{\epsilon_{\text{SiO}_2}}{t_{\text{OX\_gate\_inv}}} \big(V_{\text{dd}} - V_{\text{th}}\big) \frac{\big(V_{\text{dd}} - V_{\text{th}}\big)}{\big(V_{\text{dd}} - V_{\text{th}} + 2\,L_{\text{g}}\,v_{\text{sat}}\big/\mu_{\text{eff}}\big)}$$

$$I_{ON} = \frac{I_{drain\_ideal}}{1 + R_{sd}I_{drain\_ideal} / (V_{dd} - V_{th})}$$

$$R_{\text{gate\_unit}} = \frac{V_{\text{DD}}}{I_{\text{ON}} \times W_{\text{gate}}}$$

# ゲート長と酸化膜厚の変動量

- ■ゲート長変動量(Lg)

- ▶ Lgは、 (Lg)をSigmaとする正規分布に従い、発生すると仮定

- (Lg) は、

Lithography RoadmapにおけるGate CD control (3 sigma) の50%である

と仮定

- ■酸化膜厚変動量( tox\_gate\_inv)

- ▶評価モデルではチップ内に着眼 酸化膜厚の変動量はゼロであると仮定

# Vth**の変動量** (1/2)

- 仮定: Vthバラツキにおけるゲート長と不純物密度の独立影響

- ▶ Vthの変動量 Vthは、独立な変動 Vth(Lg)と Vth(NA)の和であると仮定

- ▶ Vth(Lg): ゲート長(Lg)の変動を起因とするVth変動量

- ▶ Vth(NA): 不純物密度の変動を起因とするVth変動量

- Vth(Lg)と Vth(NA) に対するPelgromモデルの導入

- ▶ Vth(Lg)と Vth(NA)に対して独立にPelgromモデルが成立すると仮定

- ▶ Vth(Lg)と Vth(NA)のPelgrom係数をA(Lg)、A(NA)とするとき Vth(Lg)と Vth(NA)のSigmaは、Lg×Wgの平方根に反比例

$$\sigma(\operatorname{Vth}(Lg)) = \frac{A(Lg)}{\sqrt{Lg * Wg}} \qquad \sigma(\operatorname{Vth}(NA)) = \frac{A(NA)}{\sqrt{Lg * Wg}}$$

▶ Vth全体のPelgrom係数A(all)は、A(Lg)、A(NA)の自乗平均に等しい

$$A(all) = \sqrt{A(L_g)^2 + A(NA)^2}$$

### Vth**の変動量** (2/2)

- ■Pelgrom係数の将来トレンドに対する仮定

- ►仮定 :

Vthバラツキ全体に対するPelgrom係数A(all)は、3.0[mV・μ m]で一定 (2005年~2010年)

- ▶ 仮定 :

ゲート長及び不純物濃度変動によるVthバラツキに対する影響は等しい

$$A(all) = \sqrt{A(L_g)^2 + A(NA)^2} = \sqrt{2.12^2 + 2.12^2} = 3.0$$

- ■ゲート長&不純物濃度の変動による「Vthばらつき」に対する Pelgrom係数

- ▶ Pelgrom係数A(Lg) = 2.12[mV·μm] (一定、2005年~2010年)

- ▶ Pelgrom係数A(NA) = 2.12[mV·μm] (一定、2005年~2010年)

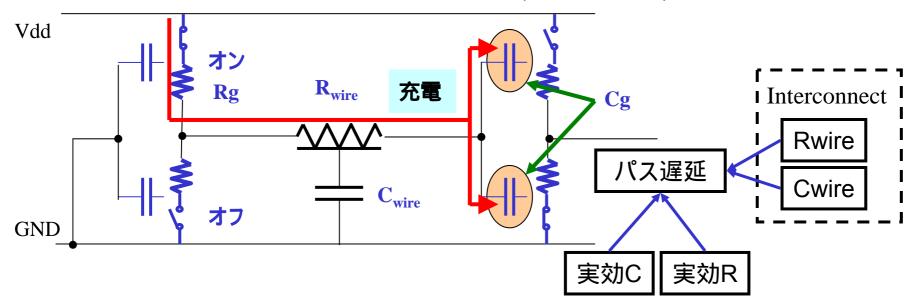

### パス遅延の算出

■パス遅延:各論理段の遅延時間を算出 合計値

■各論理段の遅延時間算出

▶入力: トランジスタの実効RgとCg、配線の寄生RwireとCwire

▶計算式: 説明簡単化のためfan-out=1のケースを以下に示すが

評価モデルではfan-out=4に拡張した計算式を使用(補足参照)

$$T = 0.693 * R_g * (C_{wire} + C_g) + 0.693 * R_{wire} * (\frac{1}{2}C_{wire} + C_g)$$

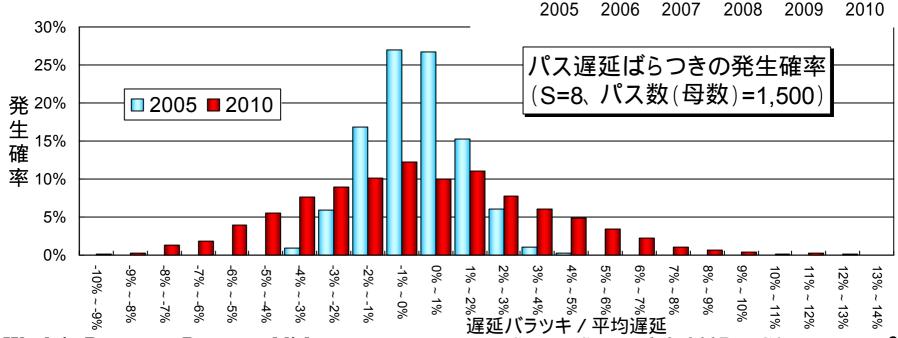

### パス遅延ばらつきのトレンド:高速化への影響

12% 10%

> 8% 6%

> 4% 2%

0%

遅延ばらつき3

の対平均遅延比率

#### ■2005年 2010年で、遅延ばらつきの広がりが2.7倍に!

- デバイス性能向上は、遅延バラツキ増加分でだけ減速

- 遅延ばらつき3 の対平均遅延比率

- = (遅延ばらつき )×3÷(遅延平均値)

- = タイミング・マージンの概数

**Work in Progress - Do not publish**

STRJ WS: March 9, 2007, WG1 Design

DFM-SWG

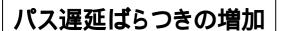

### パス遅延ばらつきのトレンド:統計的手法の利用

パス遅延ばらつきを統計的に扱う タイミング設計技術

パス遅延ばらつきを統計的に扱う

**重要性拡大**

- ケースAとBは、パス遅延の平均値は等しいが、遅延ばらつきはBはAの1.4倍

- ▶ ケースA: 論理段数S=8、セグメント配線長=50配線ピッチ

- ▶ ケースB: 論理段数S=4、セグメント配線長=129配線ピッチ

### DFM-SWG:まとめと提言

- ▶今年度の取り組み

- ▶パス遅延に対する「プロセスばらつき」の影響を定量化

- ▶2005年 2010年で、遅延ばらつきの広がりが2.7倍に

- ▶モデルで扱う要素は限定したが、年度目標「モデルの有用性確認」を達成

- ■設計WGからの提言

- ▶「プロセスばらつき」の定量化(ロードマップ化)

- ▶ ばらつき定量化により、SOC性能に対する影響度が評価可能 設計 + テスト + プロセスの技術開発における注力ポイントが明確化

- ■来年度以降の検討候補

- ▶未検討事項を含めたトータルなばらつき評価

- ↑ 未検討事項: 配線ばらつき、クロックスキューばらつき

ランダムばらつきとシステマティックばらつきの分離

# 2006年度国内活動

### 設計遅れ要因変化の分析と提言

微細化、複雑化による設計工程の複雑化

分析

マネジメント要因 :33%(前回+ 3%)

設計手法要因 : 25% (前回 + 13%)

設計スキル要因 : 20%(前回 - 12%)

提言

計画を重視したマネジメントの実践 全体最適なSOC設計手法の確立

### DFM-SWG活動

回路パスの遅延ばらつきを定量化

2005年 2010年で、

遅延ばらつきの広がりが2.7倍に!

# 参考データ1 [設計遅れ要因分析補足]

- ・マネジメント方法論

- -CMM

- -PMBOK

- ・組込み業界の取り組み

- -プロジェクトマネジメントガイド

#### CMMの体系

STRI

KP:キープラクティス

| 成熟度レベル     | キープロセスエリア(KPA)名称                                                        | KPA略号 | KP数   |

|------------|-------------------------------------------------------------------------|-------|-------|

|            |                                                                         |       | 7 7 7 |

| 5 最適化する    | 欠陥予防(Defect Prevention)                                                 | DP    | 18    |

| KP数:56     | (P数:56 技術変更管理(Technology Change Management)                             |       | 19    |

|            | プロセス変更管理(Process Change Management)                                     | PCM   | 19    |

| 4 管理された    | 定量的プロセス管理(Quantitative Process Management)                              | QPM   | 18    |

| KP数:31     | ソフトウエア品質管理(Software Quality Management)                                 | SQM   | 13    |

|            | 組織プロセス重視(Organization Process Focus)                                    | OPF   | 7/16  |

|            | 組織プロセス定義(Organization Process Definition)                               | OPD   | 6/11  |

| 3 定義された    | トレーニングプログラム(Training Program)                                           | TP    | 6/16  |

| KP数:49/108 | ソフトウエア統合管理(Integrated Software Management)                              | ISM   | 11/19 |

|            | ソフトウェアプロダクトェンジニアリング(Software Product Engineering)                       | SPE   | 9/20  |

|            | グループ間調整(Intergroup Coordination)                                        | IC    | 7/17  |

|            | ピアレビュー(Peer Review)                                                     | PR    | 3/9   |

|            | 要件管理(Requirements Management)                                           | RM    | 3/12  |

| 2 反復できる    | ソフトウエアプロジェクト計画(Software Project Engineering)                            | SPP   | 15/25 |

| KP数:65/121 | ソフトウェアプロシ <sup>・</sup> ェクト進捗管理(Software Project Tracking and Oversight) | РТО   | 13/24 |

|            | ソフトウェア品質保証(Software Quality Assurance)                                  | SQA   | 8/17  |

|            | ソフトウェア構成管理(Software Configuration Management)                           | SCM   | 10/21 |

|            | ソフトウェア外注管理(Software Subcontract Management)                             | SSM   | 16/22 |

#### **PMBOK** (Project Management Body of Knowledge)

#### 5つのプロジェクトマネジメント プロセス群(44のプロセスを定義)

立上げプロセス群

計画プロセス群

実行プロセス群

監視コントロール・プロセス群

終結プロセス群

| 9つの知識エリア                |

|-------------------------|

| プロジェクト統合マネジメント          |

| プロジェクト・スコープ・マネジメント      |

| プロジェクト・タイム・マネジメント       |

| プロジェクト・コスト・マネジメント       |

| プロジェクト品質マネジメント          |

| プロジェクト人的資源マネジメント        |

| プロジェクト・コミュニケーション・マネジメント |

プロジェクト・リスク・マネジメント

プロジェクト・調達・マネジメント

へつかけませている

#### 実際のプロジェクトマネジメントは「フェーズ」に分けて実施

- 例) 1) 計画フェーズ

- 2)要件定義フェーズ

- 3)設計・開発フェーズ

- 4)テスト・移行フェーズ

- 5) 運用・保守フェーズ

# 組込み業界の取り組み

[計画書編]

独立行政法人 情報処理推進機構 ソフトウェア・エンジニアリング・センター 編

ソフトウェアの品質と生産性向上へ! プロジェクト計画策定への指針

- マネジメント術の整備と適用が規模拡大に追いついていない。

- プロジェクトの基本 はきちんとした計画 である。

- プロジェクト運営の ベースとなる計画書 作成の雛形を提供 する。

# 参考データ2 [パス遅延ばらつき評価モデル補足]

- 1. パス遅延ばらつき評価モデルへの入力値評価モデルの入力値におけるデータ源、値

- 2. 評価モデル入力値の定義 評価モデルの入力値に対する定義、補足説明

- 3. VthとLgの変動量を連動させる方法 独立でないVthとLgの変動量を、モンテカルロシミュレーションで連動させる ために用いた手法

- 4. 実効C(Cgate)の算出モデル

PIDS-Tableから実効C(Cgate)を算出するためのモデル

- 遅延計算近似式 < fan-out=4 >

遅延計算式を、fan-out=4に拡張したモデル。ばらつきモデルでは、本近似式を使用

- 6. PMOSの各係数設定方法 NMOSのロードマップ値からPMOSの各係数を算出する方法

### 1. パス遅延ばらつき評価モデルへの入力値

NMOS-Roadmap

| NIVIOS-Roadr | пар               |                                                                                  |            |          |          |          |          |          |          |

|--------------|-------------------|----------------------------------------------------------------------------------|------------|----------|----------|----------|----------|----------|----------|

| Source       |                   | Definition                                                                       | Unit       | 2005     | 2006     | 2007     | 2008     | 2009     | 2010     |

| PIDS         | Vdd               | Power Supply Voltage                                                             | V          | 0.9      | 0.9      | 8.0      | 0.8      | 0.8      | 0.7      |

| PIDS         | tox_gate_inv      | EOTelec: Electrical Equivalent Oxide Thickness in inversion Extended planar bulk |            | 20.5     | 19.5     | 18.4     | 14.3     | 13.2     | 12.2     |

| (*1)         | σ(tox gate inv)   | ·                                                                                |            | 0.0      | 0.0      | 0.0      | 0.0      | 0.0      | 0.0      |

| PIDS         | Lg                | Lg: Physical gate length for LOP                                                 | nm         | 45       | 37       | 32       | 28       | 25       | 22       |

| Lithography  |                   | Gate CD control (3 sigma)                                                        | nm         | 3.3      | 2.9      | 2.6      | 2.3      | 2.1      | 1.9      |

| (*1)         | $\sigma(Lg)$      |                                                                                  | nm         | 8.0      | 0.7      | 0.6      | 0.5      | 0.5      | 0.4      |

| PIDS         | Vth               | Saturation Threshold                                                             | mV         | 288      | 303      | 285      | 274      | 275      | 226      |

| (*1)         | A(Lg)             | σ( Vth(Lg))のPelgrum係                                                             | mV∙μm      | 2.12     | 2.12     | 2.12     | 2.12     | 2.12     | 2.12     |

| (*1)         | A(NA)             | σ( Vth(NA))のPelgrum係                                                             | mV∙μm      | 2.12     | 2.12     | 2.12     | 2.12     | 2.12     | 2.12     |

| PIDS         | vsat              | Effective Saturation Carrier Velocity                                            | cm/sec     | 1.00E+07 | 1.00E+07 | 1.00E+07 | 1.00E+07 | 1.00E+07 | 1.00E+07 |

| PIDS         |                   | Mobility Enhancement<br>Factor for Idsat                                         |            | 1.12     | 1.11     | 1.11     | 1.12     | 1.12     | 1.11     |

| PIDS         |                   | Ideal NMOS Mobility                                                              | cm^2/V-sec | 285      | 272      | 285      | 235      | 219      | 282      |

| (*2)         | μeff              | Effective NMOS Mobility                                                          | cm^2/V-sec | 3.2E+02  | 3.0E+02  | 3.2E+02  | 2.6E+02  | 2.5E+02  | 3.1E+02  |

| PIDS         | Rsd               | Effective Parasitic series source/drain resistance                               | Ω-µm       | 180      | 180      | 180      | 180      | 180      | 180      |

| 物理定数         | ε_0               | electric constant (permittivity of free space)                                   | F/m        | 8.85E-12 | 8.85E-12 | 8.85E-12 | 8.85E-12 | 8.85E-12 | 8.85E-12 |

| 物理定数         |                   | SiO2の比誘電率                                                                        |            | 3.9      | 3.9      | 3.9      | 3.9      | 3.9      | 3.9      |

| (*3)         | ε <sub>sio2</sub> |                                                                                  | F/m        | 3.45E-11 | 3.45E-11 | 3.45E-11 | 3.45E-11 | 3.45E-11 | 3.45E-11 |

| PIDS         | Cgate_unit        | Cg,total: Ideal NMOS Device Gate Capacitance for calculating of CV/I             | F/µm       |          |          |          |          |          | 8.04E-16 |

| Interconnect |                   | Intermediate: Wiring pitch                                                       |            | 200      | 167      | 140      | 118      | 104      | 90       |

| (*4)         | Wg                | gate width                                                                       | nm         | 500      | 417.5    | 350      | 295      | 260      | 225      |

| (*1) | ばらつき度を表す係数であり、PIDS-WGとクロスカット討議のうえ設定 |                                                                                                                                      |  |  |  |  |  |

|------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|      | (tox_gate_inv)                      | tox_gate_invにおける、ばらつきの偏差値<br>チップ内ランダム成分は少ないとして、評価モデルではゼロを仮定                                                                          |  |  |  |  |  |

|      | (Lg)                                | Lgにおける、ばらつきの偏差値<br>(Lg) は、Lithography RoadmapにおけるGate CD control (3 sigma) におけるばらつ<br>き成分のうち50%はチップ内ランダムであると仮定して設定                   |  |  |  |  |  |

|      | A(Lg)                               | Vth(Lg)は、 (Vth(Lg))をSigmaとする正規分布に従い、発生すると仮定。 (Vth(Lg))は、A(Lg)を係数とするPelgromモデルに従うと仮定。 A(Lg)の2005年における値は2.12[mV・μ m]とし、2010年まで一定を仮定。   |  |  |  |  |  |

|      | A(NA)                               | Vth(NA)は、(Vth(NA))をSigmaとする正規分布に従い、発生すると仮定<br>(Vth(NA))は、A(NA)を係数とするPelgromモデルに従うと仮定<br>A(NA)の2005年における値は2.12[mV・μ m]とし、2010年まで一定を仮定 |  |  |  |  |  |

| (*2) | μ eff                               | Effective NMOS Mobility<br>(Mobility Enhancement Factor for Idsat) × (Ideal NMOS Mobility)で算出                                        |  |  |  |  |  |

| (*3) | sio2                                | (electric constant (permittivity of free space)) × (SiO2の比誘電率)で算出                                                                    |  |  |  |  |  |

| (*4) | Wg                                  | gate widthであり、Intermediate wiring pitchの2.5倍に設定                                                                                      |  |  |  |  |  |

### 3. VthとLgの変動量を連動させる方法

#### ■連動方法

- ▶Lg が大の方向に変動するとき、Vthも大の方向に変動することから、 Lgと Vth(Lg)には、同じさいころの目を用いてシミュレーション

- ▶ モンテカルロ手法の適用手段

- ↑ ゲート長に対する乱数を r として、Sigma = 1の正規分布に従う乱数を発生

- $\bullet$  Lg = (Lg)  $\times$  r

- $\wedge$  Vth(Lg) = (Vth(Lg))  $\times$  r

#### ■背景

- ▶ Lgから Vthを算出するのが理想であるが、算出に使用可能な(誰もが 納得可能な)式は存在しない

- ▶簡便な手段として、上記モデルを用いるとした

- ■PIDS-Tableから実効C(Cgate)を算出するためのモデル

- ▶ (Cg,total) × (Wg)を基本Cgate量として算出

- ▶ 変動としては、Lgおよびtoxを考慮

$$C_{gate} = \left(C_{g,Total} \times W_g\right) \times \left(1 + \frac{\Delta L_g}{L_g} - \frac{\Delta tox\_gate\_inv}{tox\_gate\_inv}\right)$$

- ■遅延計算式を、fan-out=4に拡張したモデル。ばらつきモデルでは、本近似式を使用

- ■配線はWire 0、1、2、3、4の5部分で構成と設定(将来の配線ばらつき導入のため)

配無はいい

$$= 0.1$$

(  $= 0.1$  (  $= 0.1$  (  $= 0.1$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.00$  )  $= 0.00$  (  $= 0.0$

### 6. PMOSの各係数設定方法

■各係数における、PMOSの対NMOS倍率は以下を仮定

▶ Ideal NMOS Mobility: 0.50倍

▶W: 1.50**倍**

▶他: 1倍