## 2011年度WG14活動報告 (計測WG)

メンバー

河村栄一 (富士通セミコンダクター)

山崎裕一郎(東芝)

池野昌彦 (日立ハイテク/ロジース)

上澤史且 (SONY)

小泉太一 (パナソニック)

横田和樹 (ルネサスエレクトロニクス)

市川昌和(東京大学)

水野文夫(明星大学)

新井 優 (産総研)

西萩一夫 (堀場製作所)

堺澤秀行 (NGR)

## 2011年度活動概要

#### ITRSに関する活動内容、Topics

- ERM Metrology, FEP, Lithography Metrology関連改訂

- 3D計測の要求に対しHybrid Metrologyの提案

- 「3D interconnect metrology」のサブチャプター追加

- ⇒重要性が増加 ⇒ SEMATECHでHandling, 日本ではCTに 注目してSurveyした。

#### 国内活動(近年の3D計測要求に対応した技術調査の一環として)

- 口(TSV計測一般のヒアリング)

- ⇒ 微細化だけでなく高集積化(3D化)の一環としてTSVに注目

- 1. Bonding-lessのChip on Wafer技術(東大大場先生)

- ⇒ Chipの張り合わせの際の赤外線を用いたアライメント精度向上必要(1 µ m以下)

- ⇒ X線Tomographyは数 *μ* mの空間分解能しかない。

- 2. "高密度実装基板への適応性から観た工業用X線CT装置の現状と近未来への展望" (ヤマト科学); X-ray Tomography

- 3. "計測メーカーから見たTSVの現状について"(レーザーテック); 赤外線裏面干渉を用いたTSV の深さ、形状計測

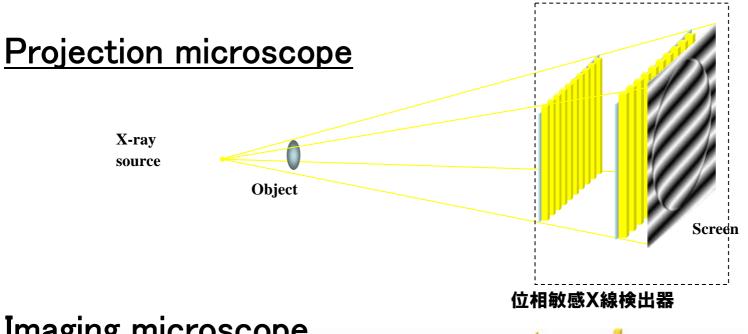

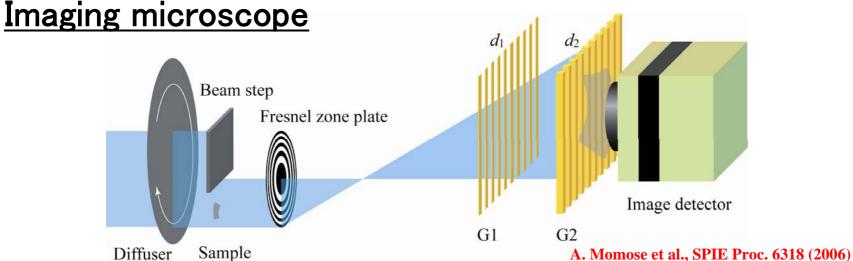

- 4. "X線位相イメージングとその応用展開"(東大百生先生)

- **□SEMATECH Symposium Japanにて**

- "Current Requirements for Metrology in fab-lite and beyond"と題しShort Presentation

#### 6. 3D Interconnect Metrology

- 6.1 Bonding overlay

- 6.2 Bonded interface void detection

- 6.3 Bonded interface defect identification

- 6.4 Bonded interface defect review

- 6.5 Edge bevel defect

- 6.6 Bond strength uniformity

- 6.7 Bonded wafer pair thickness

- 6.8 TSV etch depth

- 6.9 TSV etch profile

- **6.10 TSV liner**, barrier, seed thickness

- 6.11 Shape and stress

- 6.12 3D metrology for Cu nail and pillars

Work in Progress - Do not publish

## 国際活動

## 2012 Metrology Roadmap Table

|             |                                                                              | 2010   | 2013  | 2016       | 2019       | 2024 |

|-------------|------------------------------------------------------------------------------|--------|-------|------------|------------|------|

|             | Flash 1/2 pitch (nm)                                                         | 24     | 18    | 14         | 11         | 8.0  |

|             | DRAM ½ Pitch (nm)                                                            | 40     | 28    | 20         | 14         | 8.0  |

|             | MPU Printed Gate Length (nm)                                                 | 41     | 28    | 20         | 14.0       | 6.0  |

|             | MPU Physical Gate Length (nm)                                                | 27     | 20    | 15.0       | 12.0       | 7    |

|             | Wafer Overlay Control (nm) - 20% DRAM                                        | 8.0    | 6.0   | 4.0        | 2.8        | 1.3  |

|             | Wafer Overlay Control Double Patterning (nm)                                 | 6      | 4     | 2          | 1          | ?    |

|             | Lithography Metrology                                                        |        |       |            |            |      |

| Φ           | Physical CD Control (nm) Allowed Litho Variance = 3/4 Total Variance         | 2.8    | 2.1   | 1.6        | 1.2        | 0.7  |

| Gate        | Wafer CD metrology tool <b>uncertainty</b> (3 $\sigma$ , nm) at P/T = 0.2    | 0.55   | 0.42  | 0.31       | 0.25       | 0.15 |

|             | Etched Gate Line Width Roughness (nm) <8% of CD                              | 2.1    | 1.6   | 1.2        | 1.0        | 0.6  |

| Lines       | Printed CD Control (nm) Allowed Litho Variance = 3/4 Total Variance          | 2.5    | 1.9   | 1.5        | 1.1        | 0.8  |

| Dense Lines | Wafer CD metrology tool <b>uncertainty</b> (3s, nm) at P/T = 0.2             | 0.6    | 0.4   | 0.3        | 0.3        | 0.2  |

|             | Double Patterning Overlay Metrology                                          |        |       |            |            |      |

|             | Double Exposure and Etch - Process Range (nm)                                | 6.4    | 5.1   | 4.0        | 3.2        |      |

|             | Double Exposure and Etch - <b>Uncertainty</b> (nm)                           | 1.3    | 1.0   | 0.8        | 0.6        |      |

|             | Spacer PEE process                                                           |        |       |            |            |      |

|             | Core Gap Line CD Control (carrier Line) (nm)                                 | 1.9    | 1.5   | 1.1        | 0.9        | 0.64 |

|             | First pass CD control (after etch) - Uncertainty (nm)                        | 0.4    | 0.3   | 0.2        | 0.2        | 0.13 |

|             | Front End Processes Metrology                                                |        |       |            |            |      |

|             | High Performance Logic EOT equivalent oxide thickness (EOT), nm              | 0.65   | 0.5   | 0.5        | 0.5        |      |

|             | Logic Dielectric EOT Precision 3 <sub>o</sub> , nm                           | 0.0026 | 0.002 | 0.002      | 0.002      |      |

|             | Interconnect Metrology                                                       |        |       |            |            |      |

|             | Barrier layer thick (nm)                                                     | 3.3    | 2.4   | 1.7        | 1.3        |      |

|             | Void Size for 1% Voiding in Cu Lines  Detection of Killer Pores at (nm) size | 4.0    | 2.8   | 2.0<br>2.0 | 1.4<br>1.4 |      |

Work in Progress - Do not publish

STRJ WS: March 2, 2012, WG14 Metrology

## **ERM Metrology**

## - Graphene Metrology-

- 2011年はCDV Grapheneが注目

- CVD GrapheneのGrain Size, Grain Boundary 構造, 積層数, モビリティー 等の計測要求が明確化

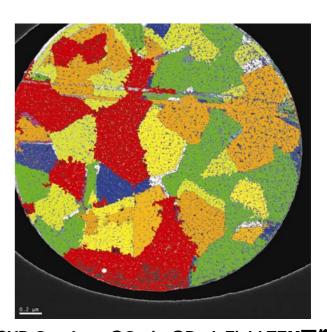

- 収差補正暗視野TEMによるGrain Boundary構造の観察が可能

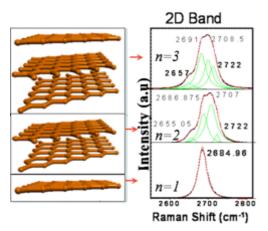

- 積層数は、Raman分光, LEEM等による計測が可能

CVD GarpheneのGrain のDark Field TEM画像 同一色が同一の結晶方位を持つ (Nelson, College of Nanoscale Science and Engineering)

**LEEM: Low Energy Electron Microscope TEM: Transmission Electron Microscope**

#### Raman分光, LEEM画像によるGraphene膜積層

Ref; Ferrari, A. C. et al. Raman spectrum of graphene and graphene layers. Phys. Rev. Lett. 97, 187401 (2006).

## FEP, Lithography Metrology

- FEP Metrology

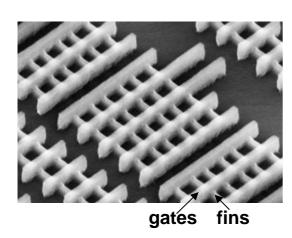

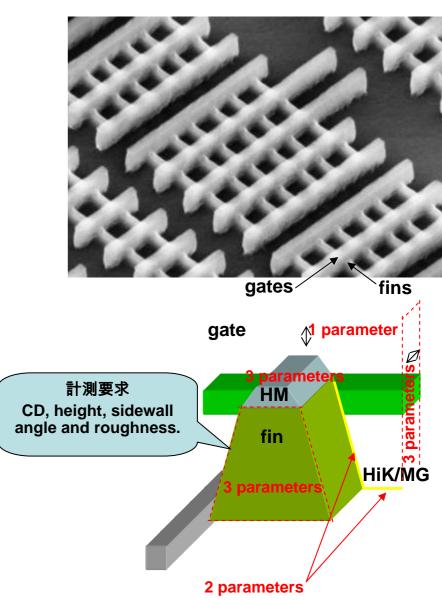

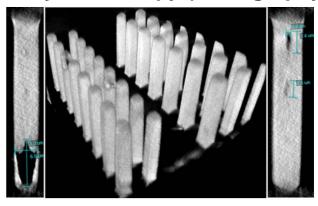

- Alternate Channel Material (Ge, III/V)と3D デバイス Metrologyがキー

- Fin FET構造では計測パラメータの増大が課題 ⇒ Hybrid Metrology への挑戦

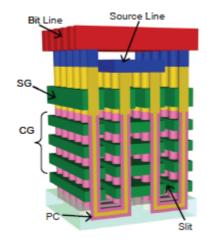

- Advanced 3D Memory (Non Planer 3D Structure)は数社で22nm世代と同時期に展開される可能性があり、Metrology技術の整備が必要

- Lithography Metrology

- 2011年は大幅変更なし

初回のWeb掲載内容の訂正あり

Fin FET 3D Structure

**Advanced Memory**

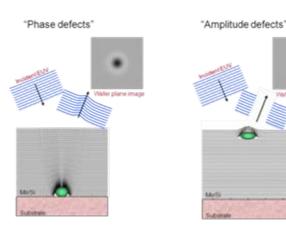

**EUV Mask Metrology**

## Hybrid Metrology

- FinFETの3D構造の計測

- 12 パラメータにもおよぶ多様な計 測要求(top corner rounding, footing, or etch recess under fin, etc)

- ゲートのSpacerはさらにパラメータ 数を増大

- 2011 SPIEにて Fin 構造の CD-SEM/AFM のフィードフォー ワード計測の提案あり

- OCD (scatterometry) に導入(FF)することで、少ないパラメータを高 精度、高速に計測か可能

- Hybrid Metrology

- <u>複数の計測を組み合わせて補完することで、高精度化、高速化を実現</u>

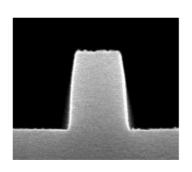

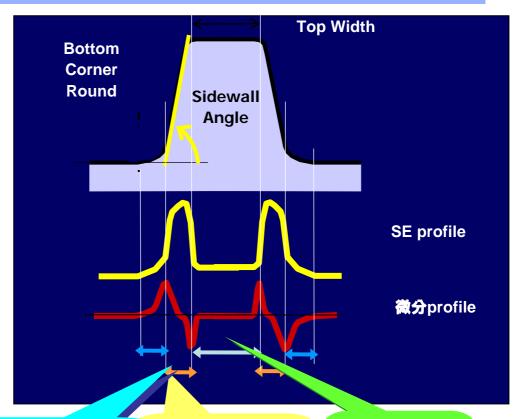

## 2次電子のWave formからの形状予測(1)

#### Multiple Parameters Profile Characterization

Footing Index | Sidewall Angle Index

Top Width Index

2次元予測から3次元化へ

提供:日立ハイテクノロジーズ

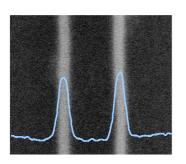

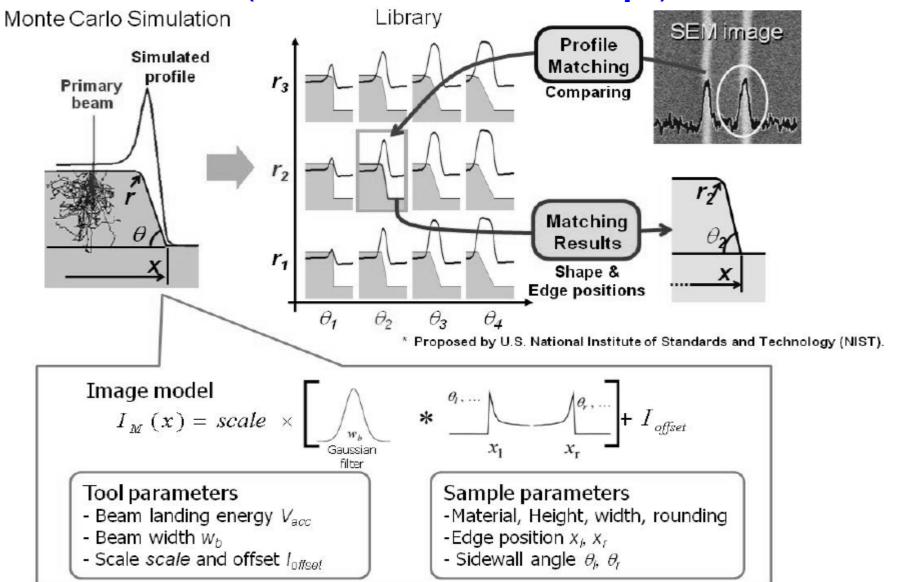

## 2次電子のWave formからの形状予測(2)

(Model Based Libraries Technique)

Proc. of SPIE 2011 Vol. 7971 79710Z-1

# 国内活動

## 3D技術の現状と課題

#### (過去のsurveyのまとめ)

- 1. TEM and/or + Tomographyは収差補正技術と合わせて破壊測定においては空間分解能が最も高い。現状のTomographyでは、試料回転に伴う空間配置補正技術の自動化が不完全のため高精度な画像再生が難しい。

- 2. GI-SAXS(Glazing Incidence Small Angle X-ray Scattering)は所謂 Scatterometryであり、X線であるが故に波長分解能は高いが、試料観察深さ制限がある。また、CT(Computed Tomography)とは異なり、 Iterative作成したLibraryを参照しながら最適解を求める。構造パラメータが多い分Library作成時間が膨大でかつ、最適解が見つけにくい。

- 3. X線Tomographyの半導体ウェーハ計測応用は殆ど進んでいない。

- 4. Hybrid Metrologyが2011年提案され、事前に他の手法で決定できる 構造パラメータを用いて未定構造パラメータの数を縮小する手法であり、 注目されている。ただし、計測機間のoffset or biasの解消(Calibration) が課題。

- \*GI-SAXSは透過型SAXS同様まだ商用化されていない。日本ではビジネスモデルに合わないため試作すら躊躇との声がある。

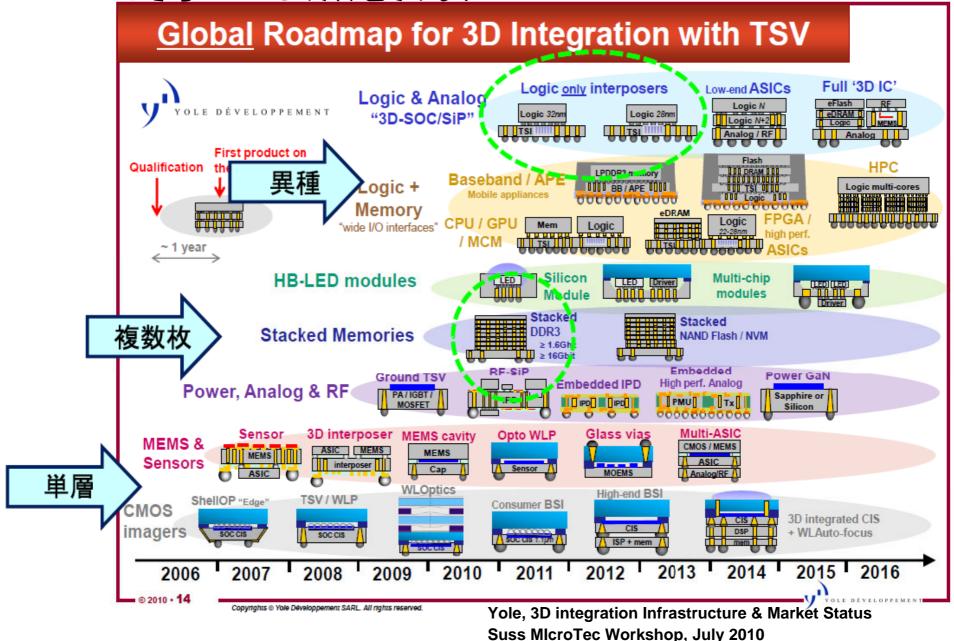

## TSVに関する計測surveyのモチベーション

1. SEMATECHの活動や、ITRSにおけるTSVに対する計測要求に対応

2. TSVはデバイスによって適用時期、適用方法が大きく異なり、現状を認識する意味がある。

Slide 14 ⇒ Slide12 順番の変更と修正

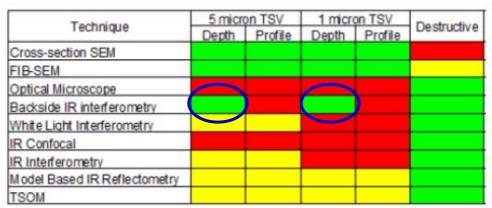

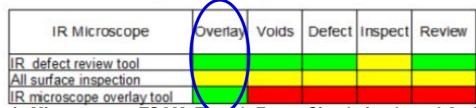

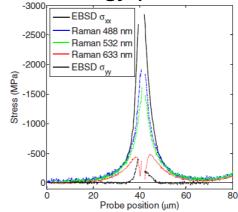

## SEMATECHのTSVに関する評価結果

Table 10 TSV Etch Depth and Profile Metrology Assessment

TSV**の深さ計測は、** 破壊であれば問題 無し、

・非破壊の場合は、 裏面赤外線干渉を 用いた計測で1um サイズのTSV径まで 可能

TSV形状計測に関しては、破壊は問題ないが、

- ・非破壊で観察できる確実なものが現 状存在しない。

- ・黄色は検証まで 至っておらず実現可 能性は未定

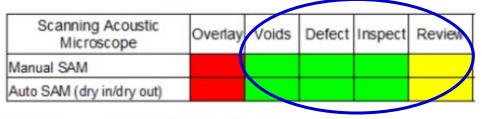

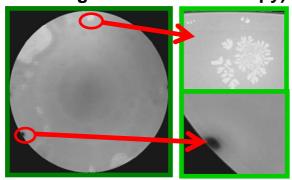

•SAMでvoids, defect, Inspect可能

・Overlay**は赤外顕微** 鏡で可能

Table 1 SAM Supplier Landscape

Green = Yes

Red = No

Yellow = Maybe

Table 2 IR Supplier Landscape

SAM: Scanning Acoustic Microscope, TSOM: Trough-Focus Simulation-based Optical Microscope

13

## **3D** Interconnect Metrology

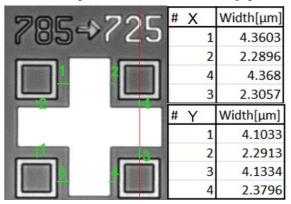

## 2011 ITSR Metrology RoadmapではThrough Silicon Via (TSV)の計測要求を拡張

#### **Overlay – IR Microscopy**

## **Bonding Defects – SAM**(Scanning Acoustic Microscopy)

#### X-Ray Microscopy (Tomography)

#### **Stress Metrology (Raman Microscopy)**

STRJ WS: March 2, 2012, WG14 Metrology

## TSVを用いた3次元実装のロードマップ

STRJ WS: March 2, 2012, WG14 Metrology

# ヒアルグから の情報のInput

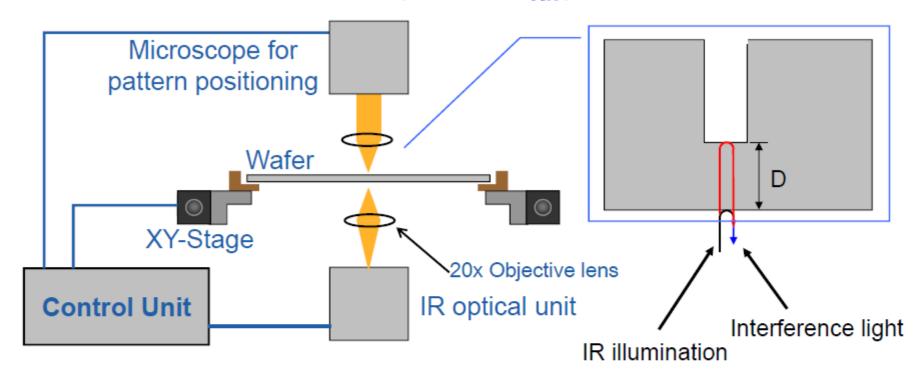

## 赤外光を用いた背面干渉によるTSV深さ計測

(レーザーテック様からの計測情報)

### Via深さの測定原理

IR光をウェハ裏面から照射し、Viaの深さ・ウエハの厚さを干渉光強度から計測

サンプル条件: Si裏面(下面)には金属層が無いこと。

表面・裏面が鏡面研磨されていること(砂面では測定精度が低下します)。

Work in Progress - Do not publish

STRJ WS: March 2, 2012, WG14 Metrology

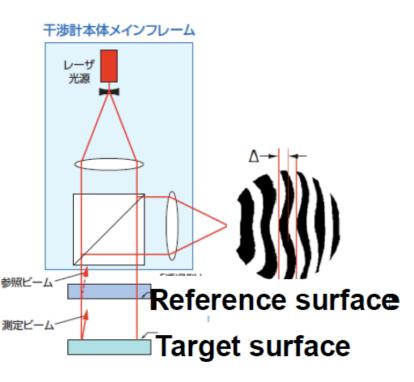

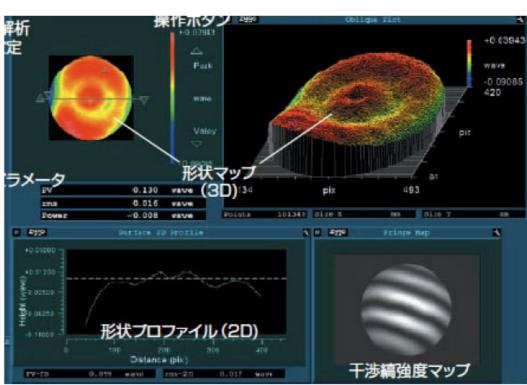

# TSVの形成方法参照表面を用いた干渉箱による表面凹凸形状の計測

・基本的には、基準表面と試料表面 間の距離に対応した干渉縞から高さ 情報に変換して凹凸形状mapを得る。

Ref; http://cweb.canon.jp/pdf-catalog/indtech/zygo/pdf/las.pdf

## TSV形状計測情報のまとめ

- 1. TSVの深さ計測は赤外線背面干渉を 用いた計測によって要求を満たせている

- 2. TSVの底面形状に関しては現在開発中 (現状TSVの底面および全体形状につい て非破壊で正確に計測できていない)

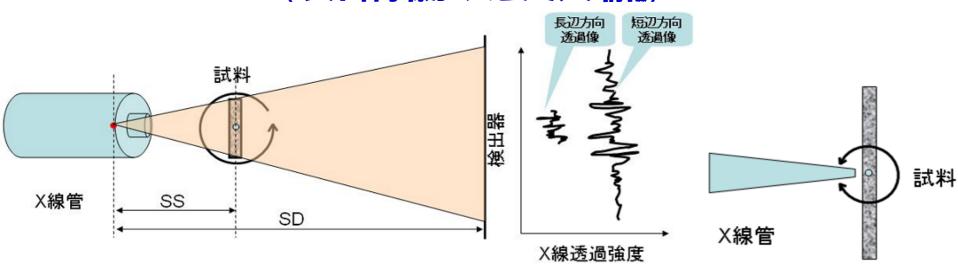

## TSVのX線計測(X線CT)

(ヤマト科学様からのヒアリング情報)

- 1. 現状のX線CTは、複素屈折率のβ(吸収係数)を利用。非破壊では数μmの空間分解能、破壊で数十nm。

- 2. 既存の技術の寄せ集めで空間分解能は1桁上がる。(SS距離の低減by cone beam、受光素子のpixel sizeの縮小100万画素⇒1000万画素、bit諮調を挙げる⇒8bit⇒16or24bit)、角度制限(含Laminography)でも検査対象によっては観察可能。

- 3. 光源に関してはElastic Emission Machining技術(X線の集光ミラー技術:NEDO(光源))等の応用の可能性

- 4. 現状市場規模が無ければ試作or製造は困難。

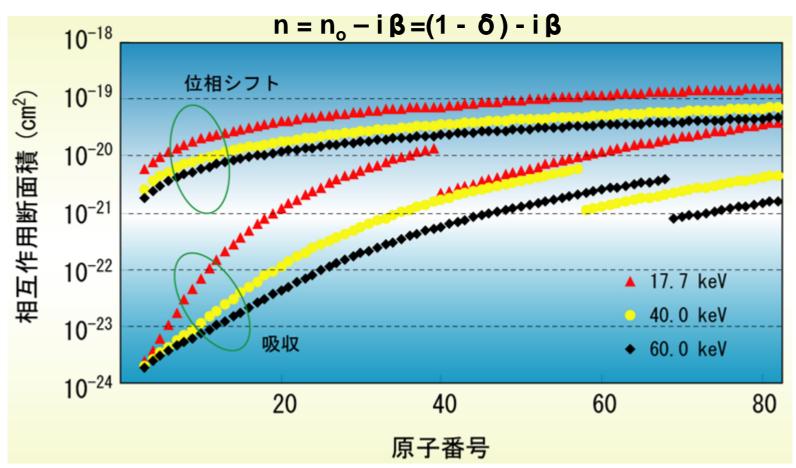

## X線CTで何を計測すべきか?

(東大百生先生からの計測情報)

ref: http://repository.dl.itc.u-tokyo.ac.jp/dspace/bitstream/2261/37090/1/K-02041.pdf

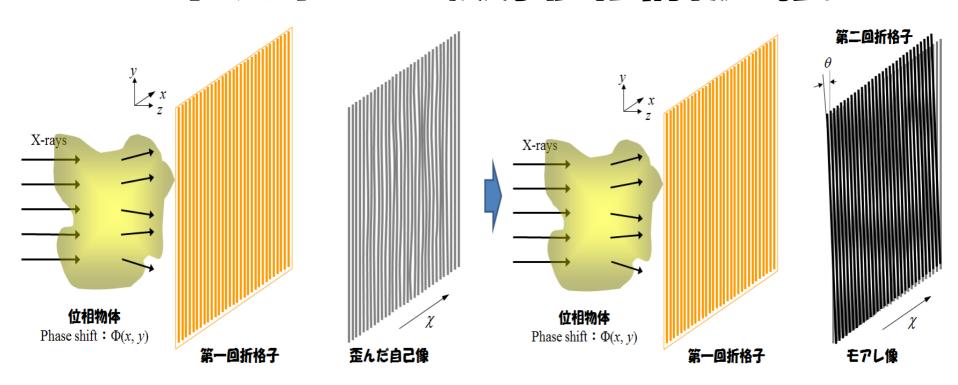

## Talbo干渉計による微分位相情報の抽出

#### 歪んだ自己像

#### モアレ像

$$\sum_{n} b_{n} \exp \left[ i2\pi \frac{nx}{d} \right] \Rightarrow \sum_{n} b_{n} \exp \left[ i2\pi \frac{n}{d} \left( x - z \frac{\partial \Phi}{\partial x} \right) \right] \qquad I(x, y, z) = b_{0} c_{0} + 2 \sum_{n>0} b_{n} c_{n} \cos \left[ 2\pi \frac{n}{d} \left( y\theta + z \frac{\partial \Phi}{\partial x} + \chi \right) \right]$$

- ・モアレ像から位相物体の微分位相情報を抽出する手法。(第2格子を $\chi$ 方向に移動させながら観察)

- ・モアレ縞は、回折格子よりピッチが大きく、検出器の空間分解能が荒くて済む利点がある

- ・微細な位相物体は、顕微鏡拡大して計測する

ref: http://repository.dl.itc.u-tokyo.ac.jp/dspace/bitstream/2261/37090/1/K-02041.pdf

**Work in Progress - Do not publish**

STRJ WS: March 2, 2012, WG14 Metrology

## Talbot干渉計とX線顕微鏡の融合

## 位相情報を用いた計測情報のまとめ

(東大百生先生のヒアリングより)

- 1.X線のδの性質は軽元素の生体系で効果が大きい。特にβはXの吸収のため熱的ダメージにより使用が困難

- 2. 6 は半導体においても応用できるのではないか?

- 3.小角散乱像についても興味深い情報であり、その応用が期待される。

## WG14今後の活動

- 1. TSV関連の計測要求のまとめ

- 2. ITRS 2011 updateに関する内容の把握

- 3. SEAJの情報共有化と連携、分担

- 4. 故障解析タスクフォースとの情報共有

## 故障解析SWG 2011年度活動状況報告

リーダー 二川 清(大阪大学)

## 故障解析SWGメンバー(2012/1/27現在)

| 1        |        |                 |      | I     |                    |

|----------|--------|-----------------|------|-------|--------------------|

| 役 職      | 氏名     | 所属              | 役 職  | 氏名    | 所属                 |

| リーダー     | 二川 清   | 大阪大学            | 特別委員 | 小川 真一 | 産業技術総合研究所          |

| サブリーダー   | 益子 洋治  | 大分大学            | "    | 中島 蕃  | デバイス・アナリシス(株)      |

| 委員       | 長谷川 芳樹 | 富士通セミコンダクター(株)  | "    | 八坂 行人 | エスアイアイ・ナノテクノロジー(株) |

| "        | 和田 慎一  | ルネサスエレクトロニクス(株) | "    | 三井 泰裕 | (株)日立ハイテクノロジーズ     |

| "        | 小守 純子  | ルネサスエレクトロニクス(株) | "    | 柿林 博司 | (株)日立ハイテクノロジーズ     |

| "        | 則松 研二  | (株)東芝 セミコンダクター社 | "    | 二村 和孝 | (株)日立ハイテクノロジーズ     |

| "        | 平賀 則秋  | ローム(株)          | "    | 寺田 浩敏 | 浜松ホトニクス(株)         |

| 特別委員(大学) | 中前 幸治  | 大阪大学            | "    | 須賀 三雄 | 日本電子(株)            |

| "        | 眞田 克   | 高知工科大学          | "    | 橋本 秀樹 | (株)東レリサーチセンター      |

| "        | 上野 和良  | 芝浦工業大学          | "    | 杉江 隆一 | (株)東レリサーチセンター      |

| 特別委員     | 渡辺 雄一  | 三洋半導体(株)        | "    | 桑原 純夫 | (株)半導体理工学センター      |

| 合計人数     |        |                 | 22   |       |                    |

## 故障解析SWGでの討議内容と講師一覧

| 第44回 日時:2011年4月15日(金)13:30~17:00 |

|----------------------------------|

| 1: 寺田 浩敏 (浜松ホトニクス)               |

| 「故障解析標準フォーマット用コンバータソフトについて:      |

| 現状報告」                            |

| 2: 伊藤 誠吾 (東京大学)                  |

| 「ターゲット励起による準静電界センシング手法他」         |

| 3: 山口屋 奈穂 (ルネサスエレクトロニクス)         |

| 「Wet 処理と TEM 観察による拡散層可視化技術」      |

| 4. 渡辺 雄一(三洋半導体)                  |

| 「ナノエ」カトロニカフ計測八折は歩延空をについて」        |

| 第45回 日時:2011年7月1日(金)13:30~17:00           |

|-------------------------------------------|

| 1: 田中 弘治 (アストロン)                          |

| 「故障解析標準フォーマット用コンバータソフトのGUI版」              |

| 2: 今野 充 (日立ハイテクノロジーズ)                     |

| 2.1「原子分解能SEMによるLSIデバイス構造解析」               |

| 2.2「顕微鏡学会より」                              |

| 3: 遠藤 徳明 (日本電子)                           |

| 3.1 「半導体デバイスにおけるTEMを用いた                   |

| 低加速電圧による観察・分析の有効性」                        |

| 3.2 「顕微鏡学会より」                             |

| 4: 中西 伸登 (ルネサスエレクトロニクス)                   |

| 「High Reliable Strain Measurement         |

| for Power Devices Using Stem-CBED Method」 |

|                                           |

| 第46回 日時:2011年10月14日(金)13:30~17:00 |

|-----------------------------------|

| 1: 越川 一成 (浜松ホトニクス)                |

| 「位相計測による故障解析:                     |

| サーマルロックイン・OBIRCHロックイン」            |

| 2: 戸田 徹 (DCGシステムズ)                |

| 「ロックインサーマルを用いた                    |

| 非破壊検査での3次元故障位置特定技術」               |

| 3: 田中 弘治 (アストロン)                  |

| 「故障解析標準フォーマットの進捗状況」               |

|                                   |

| 第47回 日時:2011年1月14日(金)13:30~17:00 |

|----------------------------------|

| 1: 田中 弘治 (アストロン)                 |

| 「故障解析標準フォーマット用コンバータソフトの          |

| 進捗状況と今後の進め方」                     |

| 2: 小川 真一(産総研)                    |

| 「Heイオン顕微鏡技術の最新動向」                |

| 3: 茂木 忍 (DCGシステムズ)               |

| 「CW-LVP/LVIの原理と応用例の紹介」           |

| ·                                |

**Work in Progress - Do not publish**

STRJ WS: March 2, 2012, WG14 Metrology

#### トピックス

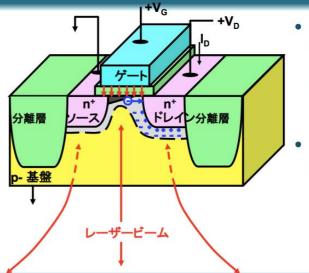

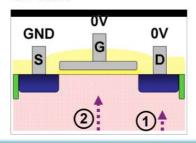

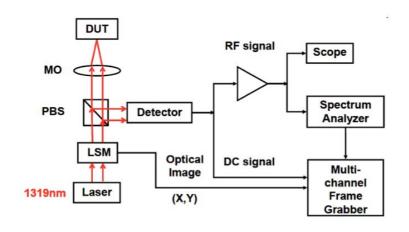

## LVP (Laser Voltage Probing) LVI (Laser Voltage Imaging) 原理と事例

#### レーザーボルテージプロ-ビング (LVP)原理

反射光にデバイスの動作状態に依存した、変調が生じる。

それは主に、フリーキャリヤの振る舞いに依存する。

屈折率

$$\Delta n = -\frac{\lambda^2 q^2}{8\pi^2 c_0^2 \varepsilon_0 n_0} \left[ \begin{array}{c} \Delta N_e \\ m_e \end{array} \right] \left[ \begin{array}{c} \Delta N_h \\ m_h \end{array} \right]$$

吸光係数

$$\Delta \alpha = \frac{\lambda^2 q^3}{4\pi^2 c_0^3 \varepsilon_0 n_0} \left[ \frac{\Delta N_e}{m_e^2 \mu_e} + \frac{\Delta N_h}{m_h^2 \mu_h} \right]$$

△N:チャージキャリアの密度

- n0 is the index of un-doped silicon

- q is the electron charge

- λ is the wavelength

- e0 is the permittivity of free space

- c0 is the speed of light in vacuum u is the mobility

- m is the effective mass

- $\Delta\,N$  is the changes in charge carrier densities The indices h and e stand for holes and

#### レーザーボルテージプロ-ビング (LVP)原理

#### LASERビーム (1320nm)を裏面 より照射し、拡散 層エリアに焦点を 合わせる。

主な活性領域から の反射光を得る。

#### レーザーボルテージプロ-ビング (LVP)原理

デバイスの異なるスイッチング状態に依存して反射光に変調がおこる

①反転層の形成

②空乏層の形成

オン状態でキャリアの密度の変化が生じる

#### off state

# on state – saturation 1.2V GND 1.2V GND 1.2V 1.2V

Work in Progress - Do not publish

#### LVI: 画像ベースの LVP 素早くIC回路の状態を確認する事が可能

#### Inverter chain

LSM Reflected Image

$27 \times 27 \mu m^2$  FOV

Laser Voltage Image

赤色で表示されている部分が動作領域

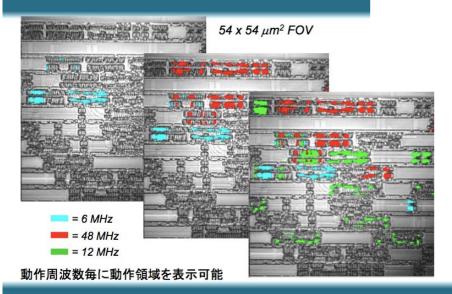

#### **Multi-frequency LVI Overlay**

#### Work in Progress - Do not publish

#### Functional Block (multiple frequencies)

#### セットアップ模式図

#### 事例紹介

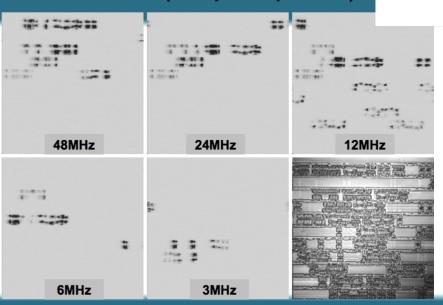

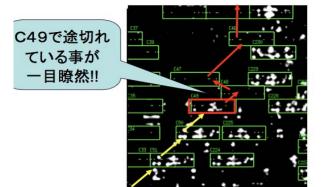

- Chip is 40nm CMOS Graphics Processor Unit (GPU)

- The failure was identified on a production <u>compressed shift</u> <u>pattern</u>

- A <u>11001100...</u> repeating pattern was cycled through the scan chain

- Scan clock = 11 MHz

- Scan data = ¼ scan clock = 2.75 MHz

- LVI was captured for both clock and data frequencies

- LVI was captured for both failing die and a good die

#### Chain Overlay on 50x LSM Image

- Scan Chain has ~ 500 flops

- In a good chain, each flop should have LVI activity

- The area in blue is where LVI activity was missing

#### **Good/Bad Comparison of LVI**

LVI captured on the good die confirms the "dead zone"

Bad Die

#### LVI captured High Magnification

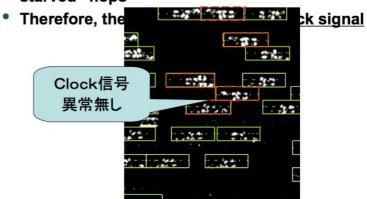

- LVI here is captured with 220x Solid Immersion Lens (SIL)

- Data shifts from flop<highest> (Scan In) to flop<0> (Scan Out)

- Flop overlay shows data signal "breaking up" in flop C49

50倍LVI画像

#### LVI for Clock in Same Area

- LVI captured for the <u>clock frequency</u>

- The clock is reaching all flops, including "datastarved" flops

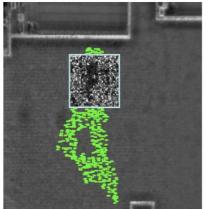

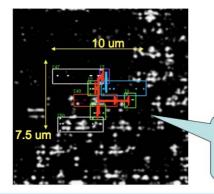

#### C49 Fanout to Define PFA Area

- Fanout of flop C49 is shown overlaid on LVI data image

- Fanout: random logic (green), buffer to flop C48 (purple), flop C48 (blue)

- This fanout defined the area for destructive physical analysis

物理解析に 必要な絞り込み 完了!!

#### **PFA Results**

- Physical Failure Analysis confirmed that the defect was inside flop C49 (物理解析の結果、C49内に欠陥が有った 事が確認された)

- The defect was cited as "hard mask remain" at the output of this flop (欠陥は、このフロップ出力のコンタクト接合 箇所でのハードマスク残留であった。)

STRJ WS: March 2, 2012, WG14 Metrology

## ご清聴ありがとうございました

## Appendix (関連資料)

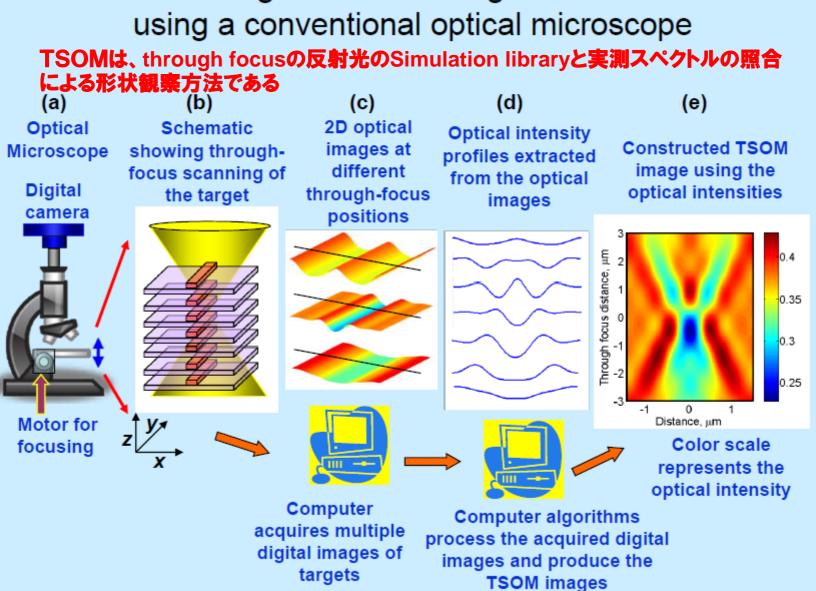

## NISTのTSOMの概要

Animation showing the TSOM image construction method using a conventional optical microscope

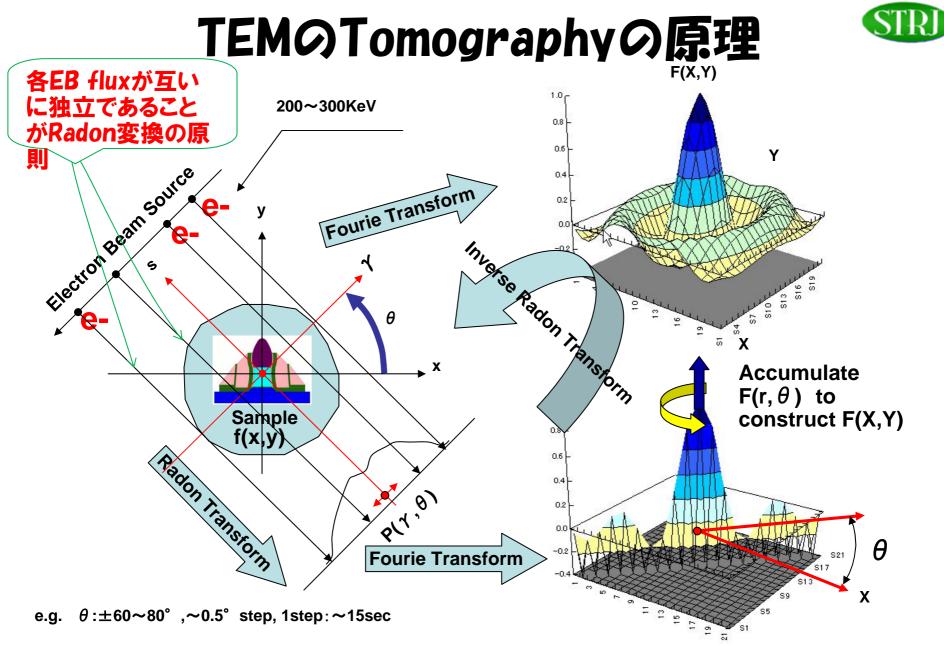

#### 数学的に断面透過強度分布P(Y, θ)から断層強度分布f(x,y)が求まる

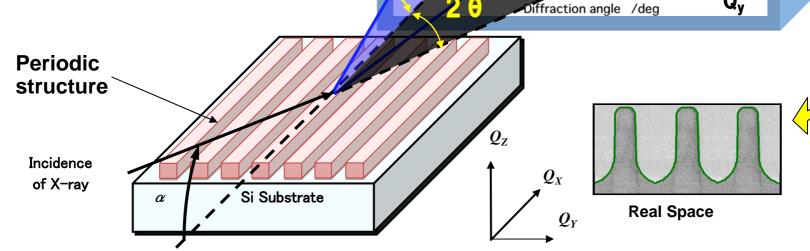

## GI-SAXS (nondestructive)の原理

$Q_{z}^{2.0}$

Analysis of 2D diffraction image to obtain cross-sectional view of the sample

**2 θ**: Diffraction angle

**β**:exit angle

(Courtesy of Toshiba) / STRJ WS: March 7, 2008, WG11 Metrology

**2D Detector**

**Spatial frequency**

.... Q, diffraction profile

.... Q<sub>v</sub> diffraction profile

様々な形状の回折パターンを事前にシミュレーションによりLibrary化し、 実際の計測パターンと照合して断面形状を特定する手法

**Work in Progress - Do not publish**

STRJ WS: March 2, 2012, WG14 Metrology

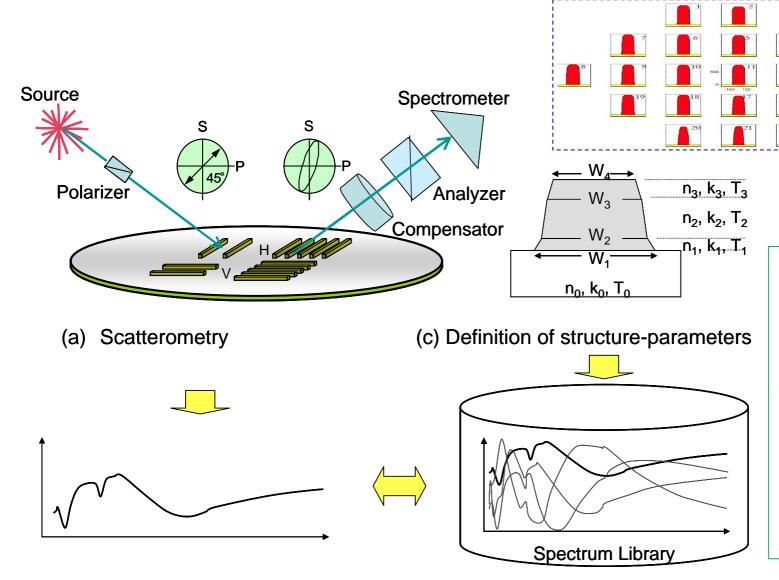

Scatterometryによる形状計測の原理

(b) Measurement spectrum Work in Progress - Do not publish

(d) Spectrum library making