### WG6(PIDS 及びRF&AMS)活動報告

# ロジックおよびメモリデバイスの スケーリングトレンド ~FinFETで大きく変わるロジックトレンド

STRJ WS 2013 2014年3月7日 品川:コクヨホール

WG6主査:尾田秀一(ルネサスエレクトロニクス)

### 用語集

#### PIDS

(Process Integration, Devices, and Structures)

- Logic

- •HP: High Performance

- •LOP: Low Operation Power

- LSTP: Low-Standby Power

- •LP: Low Power

- •FD-SOI: Fully-Depleted Silicon On Insulator

- •MG: Multi Gates --- FinFET, TriGate等の総称

- •Ge: Germanium

- ·III-V: III族-V族化合物半導体

- •Vdd,VDD: 電源電圧

- ·Ion: オン電流、動作時駆動電流

- ・Wfp:Wチャネル幅のfootprint 投影トランジスタ幅

- Tr.: Transistor

- •DIBL: Drain Induced Barrier Lowering

- SS: Sub threshold Swing

- Memory

- SRAM: Static Random Access Memory

- DRAM: Dynamic Random Access Memory

- •RCAT: Recessed-Channel Transistor

- VTC: Vertical Channel Transistor

- •MRAM: Magnetic( Tunneling Junction ) RAM

- STT-MRAM: Spin-Torque Transfer Magnetic RAM

- PCRAM: Phase Change RAM

- Memory (continuation)

- •FeRAM: Ferro-electric RAM

- ReRAM: Resistance RAM

- RTN: Random Telegraph Noise

- SOMOS. Silicon Oxide Nitride Oxide Semiconductor

- MONOS:Metal Oxide Nitride Oxide Silicon

- Reliability

- •TDDB:Time Dependent Dielectric Breakdown

- pBTI:Positive Bias Temperature Instability

- nBTI:Negative Bias Temperature Instability

#### RF&AMS

(Radio Frequency & Analog/Mixed -Signal)

- LNA: Low Noise Amplifier

- VCO: Voltage Controlled Oscillator

- PA: Power Amplifier

- •ADC: Analog to Digital converter

- SerDes: Serializer Deserializer

- •HV: High Voltage

- CIS: CMOS Image Sensor

主査:尾田秀一(ルネサス) 副主査:井上裕文(東芝) 幹事:久本大(日立)

| SWG  | SSWG        | 委員                                             | 特別委員                                                                       |  |  |

|------|-------------|------------------------------------------------|----------------------------------------------------------------------------|--|--|

| PIDS | Logic       | *尾田秀一(ルネサス)<br>倉田創(富士通セミコン)<br>福崎勇三(ソニー)       | 若林整(東工大)<br>井田次郎(金工大)<br>平本俊郎(東京大)<br>高木信一(東京大)<br>赤坂泰志(TEL)<br>吉見信(aBeam) |  |  |

|      | Memory      | *井上裕文(東芝)<br>岩本邦彦(ローム)                         | 杉井寿博(LEAP)<br>笠井直記(東北大)                                                    |  |  |

|      | Reliability | *最上徹(PETRA)                                    | 丹羽正昭(東北大)                                                                  |  |  |

| RF&/ | AMS         | *久本大(日立)<br>田辺昭(ルネサス)<br>安茂博章(ソニー)<br>大黒達也(東芝) | 田中徹(東北大)                                                                   |  |  |

\*印は、SSWG リーダー

PIDS: Process Integration, Devices, and Structures

- ■ロジックとメモリデバイスの15年間の技術ロードマップの策定 量産に必要なデバイス技術とデバイススペックの提示

- ■スケーリングに必要な技術やソリューションの提示

- ■技術範囲:Scopes

- ・デバイス性能(速度、密度、電力等)

- デバイス構造

- ・新規プロセス・インテグレーション技術

- •信頼性

### PIDS 構成

#### ■ロジック

#### Table PIDS5 Comparison of HP, LP, and III-V/Ge technologies

2013年版

|                        | HP | LP                  | III-V/Ge |

|------------------------|----|---------------------|----------|

| Speed (I/CV)           | 1  | ~0.4                | >1       |

| Dynamic power $(CV^2)$ | 1  | ~1                  | <1       |

| Static power (I off)   | 1  | ~1×10 <sup>-4</sup> | 1        |

2011年版

|                          | HP | LOP                | LSTP               | III-V/Ge |

|--------------------------|----|--------------------|--------------------|----------|

| Speed (I/CV)             | 1  | 0.5                | 0.25               | 1.5      |

| Dynamic power $(CV^2)$   | 1  | 0.6                | 1                  | 0.6      |

| Static power $(I_{off})$ | 1  | 5x10 <sup>-2</sup> | 1x10 <sup>-4</sup> | 1        |

#### ■メモリ

- DRAM

- Non-volatile

- ・電荷蓄積型FET:浮遊ゲート(NOR and NAND)

電荷トラップ型(NOR and NAND),SONOS,MONOS

•非電荷蓄積型FET:FeRAM, PCRAM, MRAM,STT-MRAM, ReRAM

#### ■信頼性

# 2013年版 ロジック変更点(前提条件)

#### ■TCADシミュレーションを使用

- ・バルクデバイス:量子効果を組み入れたdrift-diffusionモデル

- •FDSOI,MG:非平衡グリーン関数、バンド構造

- ・従来の解析モデル"MASTAR"も比較用として使用する

- ・量子効果への対応などから TCADシミュレーションに切り替えてゆく

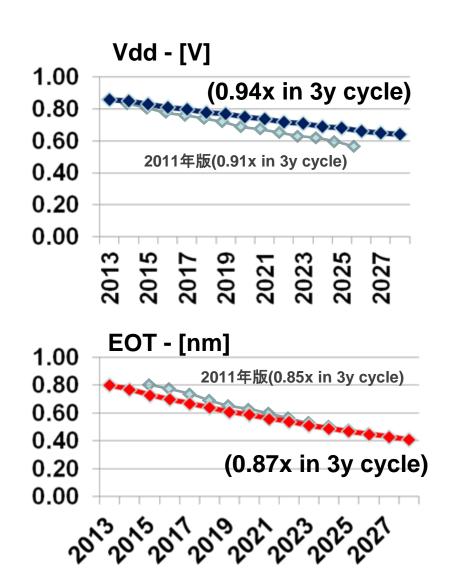

- I/CV(速度)年率8%改善 ゲート長スケーリングは2011年版と同等 電源電圧(Vdd)のスケーリングを鈍化。Ioff は一定。

- · Vdd が低くなると高移動度基板が必要となることが明確に

- ・ゲート長のスケーリング限界は、トンネル電流で決まる5nm

- ■Nodeと世代は、量産 (1st、2nd ベンダー)を反映

| [    | 2013   | 2014  | 2015  | 2016  | 2017  | 2018  | 2019  | 2020  | 2021  | 2022  | 2023  | 2024  | 2025  | 2026  | 2027  | 2028  |

|------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Node | '22/20 | 16/14 | 16/14 | 16/14 | 11/10 | 11/10 | 11/10 | "8/7" | "8/7" | "8/7" | "6/5" | "6/5" | "6/5" | "4/3" | "4/3" | "4/3" |

| Gen  | "G1"   |       |       | "G2"  |       |       | "G3"  |       |       | "G4"  |       |       | "G5"  |       |       | "G6"  |

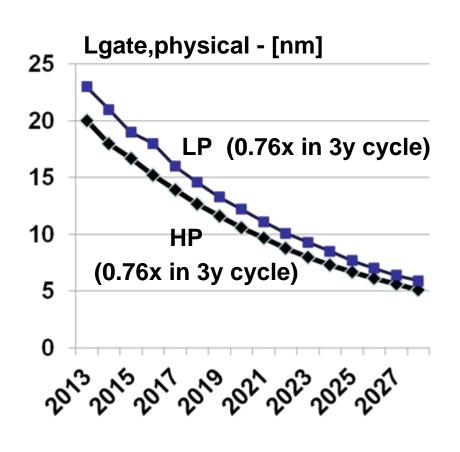

### Lg、Vdd、EOTスケーリングトレンド(前提条件)

HPのLgトレンドは、ITRS2011と同じ

# 2013年版 ロジック変更点(TCAD Sim結果)

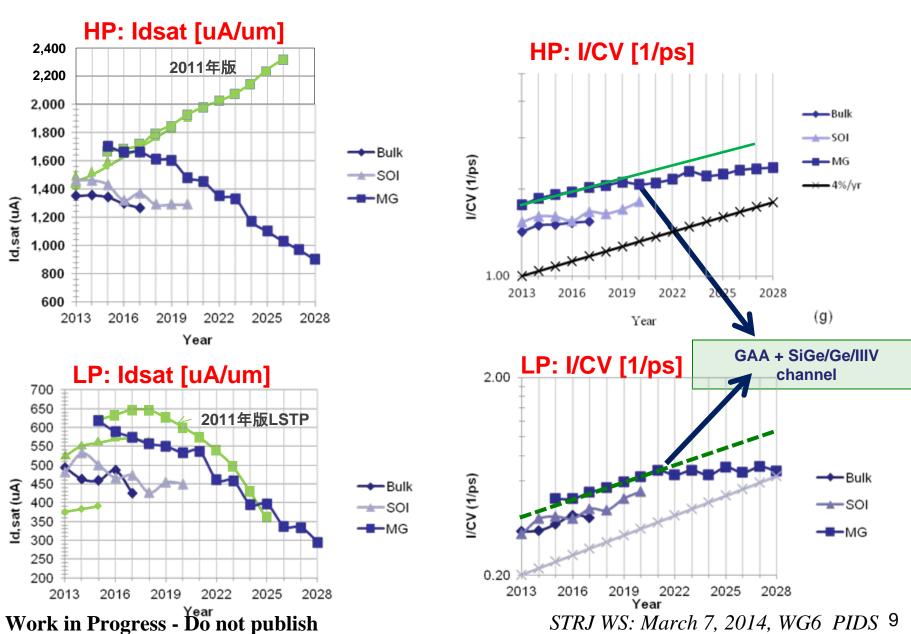

- Ion(オン電流) は年々低下 2019年から急激に低下

- Ioff (オフ電流)一定:前提条件

- → 実効ゲート電圧の減少

- → 誘起電荷減、Ion 減

- •2019年Lg=12nm以下では、ソースドレイン間のトンネル電流が急増

- I/CV (速度)は、2018年まで年率4%改善 2019年以降改善が止まり一定となる。 I/CV 年率4%改善維持には、

- 2019年以降、GAAやSiGe/Ge、III-Vチャネル導入と予想される

- ・III-V、Geのテーブルは修正が間に合わずITRS2011のまま。 (解析モデル"MASTAR"で見積もった値)

- CV (動作電力) は年率9%改善を維持

# オン電流と速度のトレンド

STRJ WS: March 7, 2014, WG6 PIDS 9

### オン電流低下要因

- ■実験結果基づいた解析モデルシミュレータから量子効果を含む 物理モデルに基づいたTCADシミュレータに変更

- ・ITRS2013は、現実的な量子効果を含むモデルのTCADツールでの計算

- → Vdd減とトンネル電流増加が電流劣化原因。 トンネル電流増加でサブスレショルドスイングが劣化。 オフ電流一定を維持するため、(仕事関数を変えて)Vthを高くする。 チャネル内に誘起される電荷減り、電流劣化が生じる

- → ソース・ドレインの空乏層幅の最小値は5nm。 Lg<12nm(Leff<10nm)でソース空乏層とドレイン空乏層が接し トンネルリークが急増する。Lg<12nmは2019年。

- ITRS2011までは、CV/I 13%改善が目標でロードマップは指標。 テーブル作成には、実験結果を基にした解析モデルのMASTARを使用 "nearer term"は良く合う。移動度のパラメーター"Mobility Enhancement Factor", "Ballistic Enhancement Factor"を調整し、CV/I 13%を満たす ようにテーブルを作成。結果、オン電流を年々増加。

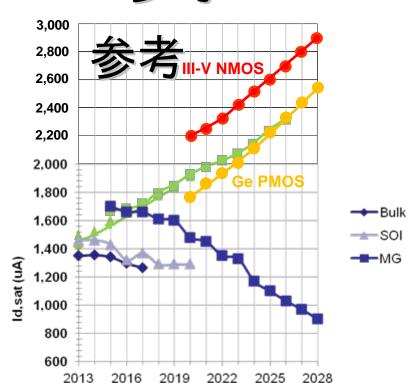

### ITRS2011 III-V 見直し要

Year

■III-Vのテーブルの改訂は、次回。 2011年年度版はMASTARで作成。 モデルが異なるため TCADツール との比較は、意味がない

■TCADシミュレーションで見積もる 予定。

| i oui                                                               |         |         |         |         |         |         |         |       |       |       |       |       |       |       |       |       |

|---------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Table PIDS4 III-V/Ge High-performance Logic Techn                   | ology R | equiren | nents   |         |         |         |         |       |       |       |       |       |       |       |       |       |

| Year of Production                                                  | 2013    | 2014    | 2015    | 2016    | 2017    | 2018    | 2019    | 2020  | 2021  | 2022  | 2023  | 2024  | 2025  | 2026  | 2027  | 2028  |

| Logic Industry "Node Range" Labeling (nm) [based on 0.71x reduction | "22/20" | "16/14" | "16/14" | "16/14" | "11/10" | "11/10" | "11/10" | "8/7" | "8/7" | "8/7" | "6/5" | "6/5" | "6/5" | "4/3" | "4/3" | "4/3" |

| per "Node Range" ("Nyde" = $\sim 2x M_E$ )                          | 22,20   | 10,14   | 10/14   | 10/14   | 11/10   |         |         | •     | 0,,   | •     | 0.0   | 0,0   | 0,0   |       | 4,0   |       |

| Logic Industry "General Labory Louised on 0.71x Mx reduction        | "G1"    |         |         | "G2"    |         |         | "G3"    |       |       | "G4"  |       |       | "G5"  |       |       | "G6"  |

| per "Generic Node " ell, " y);beginning 2013/"G1"/40nm              |         |         |         |         |         |         |         |       |       | ٠.    |       |       |       |       |       |       |

| MPU/ASIC Metal 1 ( ) ½ Pitch (nm, contacted)                        | 40      | 32      | 32      | 28.3    | 25.3    | 22.5    | 20.0    | 17.9  | 15.9  | 14.2  | 12.6  | 11.3  | 10.0  | 8.9   | 8     | 7.1   |

| L <sub>g</sub> : Physical Lgate for HP Logic (nm)                   | 24      | 22      | 20      | 18      | 17      | 15.3    | 14.0    | 12.8  | 11.7  | 10.6  | 9.7   | 8.9   | 8.1   | 7.4   | 6.6   | 5.9   |

| Mobility Enhancement Factor due to Channel Material [10]            |         |         | •       | -       | •       | -       | •       | •     |       | •     |       | •     |       | ,     | _     |       |

| III-V NMOSFET MG                                                    |         |         |         |         |         |         |         | 8     | 8     | 8     | 8     | 8     | 8     | 8     | 8     | 8     |

| Ge PMOSFET MG                                                       |         |         |         |         |         |         |         | 4     | 4     | 4     | 4     | 4     | 4     | 4     | 4     | 4     |

| Effective Ballistic Enhancement Factor, Kbal [11]                   |         |         |         |         |         |         |         |       |       |       |       |       |       |       |       |       |

| III-V NMOSFET MG                                                    |         |         |         |         |         |         |         | 3.85  | 4.05  | 4.25  | 4.52  | 4.82  | 5.13  | 5.46  | 5.82  | 6.20  |

| Ge PMOSFET MG                                                       |         |         |         |         |         | Ì       |         | 2.31  | 2.43  | 2.55  | 2.71  | 2.89  | 3.08  | 3.28  | 3.49  | 3.72  |

### 2013年版 DRAM変更点

#### 日本PIDSの調査結果を反映

- ■ハーフピッチはやや緩和

- ■縦型トランジスタ(VCT)導入は2年遅れの2016年から、 以降、リセスチャネルトランジスタ(RCAT+Fin)を置き換える これに伴い、6F<sup>2</sup>から4F<sup>2</sup>の移行も2年遅延し2016年

|     | Year of Production                             | 2013     | 2014               | 2015               | 2016             | 2017 | 2018 | 2019 | 2020 |

|-----|------------------------------------------------|----------|--------------------|--------------------|------------------|------|------|------|------|

| NEW | MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (contacted) | 40       | 32                 | 32                 | 28.3             | 25.3 | 22.5 | 20.0 | 17.9 |

| WAS | Half Pitch (Contacted line) (nm)               | 28       | 25                 | 22                 | 20               | 18   | 16   | 14   | 13   |

| IS  | Half Pitch (Contacted line) (nm)               | 28       | <b>26</b>          | 24                 | 21               | 20   | 18   | 16   | 15   |

| WAS | DRAM cell FET structure [6]                    | RCAT+Fin | VCT                | VCT                | VCT              | VCT  | VCT  | VCT  | VCT  |

| IS  | DRAM cell FET structure [6]                    | RCAT+Fin | RCAT+Fin           | RCAT+Fin           | VCT              | VCT  | VCT  | VCT  | VCT  |

| WAS | Cell Size Factor: a [11]                       | 6        | 4                  | 4                  | 4                | 4    | 4    | 4    | 4    |

| IS  | Cell Size Factor: a [11]                       | 6        | 6                  | 6                  | 4                | 4    | 4    | 4    | 4    |

| NEW | Gb/1chip target                                | 4G       | 8G                 | 8G                 | 8G               | 8G   | 16G  | 16G  | 16G  |

|     |                                                | Manu     | ufacturable soluti | ons exist, and are | being optimized  |      |      |      |      |

|     |                                                |          | Ma                 | ınufacturable solu |                  |      |      |      |      |

|     |                                                |          |                    | Interim solu       | tions are know n | •    |      |      |      |

|     |                                                |          | Manufa             | cturable solutions | are NOT know n   |      |      |      |      |

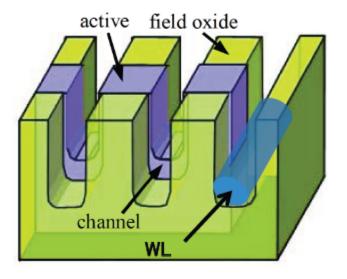

### DRAMセルトランジスタ構造

- RCAT+Fin: Saddle-Fin

- Symp. on VLSI Tech. 2006, T5-1.

- RCAT: Recessed-Ch. Tr.

Fig. 1. Schematic diagram of S-Fin. The groove like RCAT and fin structure to the channel width direction are formed.

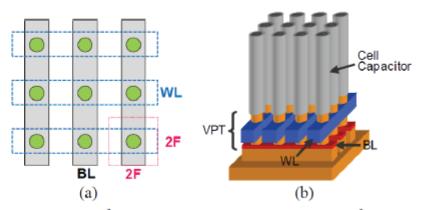

- VCT: Vertical Channel Transistor

- ESSDERC 2011, p. 211.

- ◆VPT (Vertical Pillar Tr.)

Figure 2. (a) 4F<sup>2</sup> cell layout, (b) Schematic diagram of VPT 4F<sup>2</sup> cell array

STRJ WS2013. WG6 PIDS 若林

### 2013年版 NAND Flash変更点

#### 日本PIDSの調査結果と新製品のプレスリリースを反映

- ■2Dセルのスケーリング限界は12nm、2019年。

- ■3Dセルは、ハーフピッチが緩和し、積層数は増加する。

|           | NAND Flash            |          |       |        |        |        |         |

|-----------|-----------------------|----------|-------|--------|--------|--------|---------|

|           | Year of Production    | 2013     | 2016  | 2019   | 2022   | 2025   | 2028    |

| Was       | 2D poly 1/2 pitch     | 18nm     | 14nm  | 11nm   | 8nm    | 8nm    | 8nm     |

| Is        | 2D poly 1/2 pitch     | 18nm     | 14nm  | 12nm   | 12nm   | 12nm   | 12nm    |

| Was       | 3D cell x-y 1/2 pitch |          | 32nm  | 28nm   | 24nm   | 18nm   |         |

| ls        | 3D cell x-y 1/2 pitch | 64nm     | 45nm  | 30nm   | 27nm   | 25nm   | 22nm    |

| Was       | Cell type             | FG       | CT-3D | CT-3D  | CT-3D  | CT-3D  |         |

| Is        | Cell type             | FG/CT/3D | CT-3D | CT-3D  | CT-3D  | CT-3D  | CT-3D   |

| Unchanged | Product density       | 128G     | 512G  | 1T     | 2T     | 4T     | 8T      |

| Was       | Number of 3D layers   |          | 4-32  | 16-128 | 48-392 | 64-512 |         |

| ls        | Number of 3D layers   | 16-32    | 16-32 | 32-64  | 64-128 | 96-192 | 192-384 |

**FG**: Floating Gate

**CT**: Charge Trap

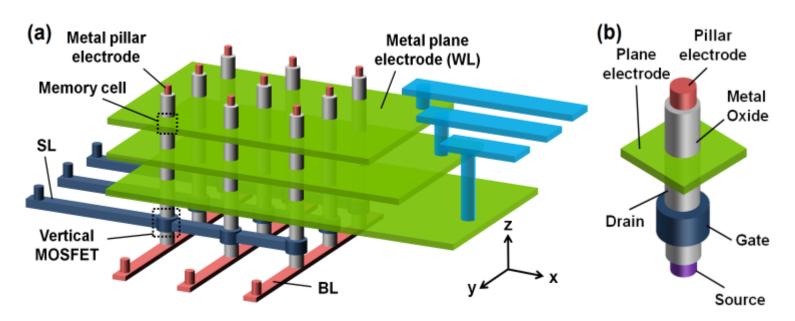

## 2013年版 ReRAM(new)

- 4F<sup>2</sup>セルで2018年登場。2021年実装密度で3D Flashを キャッチアップ

- ■セレクタ電極、ワード線がメタル平面電極になるなど課題多い

| D. Resistive memory (ReRAM)                |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

|--------------------------------------------|------|------|------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Year of Production                         | 2013 | 2014 | 2015 | 2016     | 2017     | 2018     | 2019     | 2020     | 2021     | 2022     | 2023     | 2024     | 2025     | 2026     | 2027     | 2028     |

| ReRAM technology node F (nm)               |      |      |      |          |          | 12       | 12       | 12       | 8        | 8        | 8        | 6        | 6        | 6        | 4        | 4        |

| ReRAM cell size area factor a in multiples |      |      |      |          |          | 4        |          | 4        | 4        | 4        |          | ,        |          | 4        |          |          |

| of F <sup>a</sup>                          |      |      |      |          |          | *        | 4        | *        | *        | *        | 4        | 4        | 4        | •        | *        | 4        |

| ReRAM cell footprint (nm²)                 |      |      |      |          |          | 576      | 576      | 576      | 256      | 256      | 256      | 144      | 144      | 144      | 64       | 64       |

| ReRAM array efficiency (%) (2D array)      |      |      |      |          |          | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    |

| ReRAM number of bits per cell (MLC)        |      |      |      |          |          | 2        | 2        | 2        | 3        | 3        | 3        | 4        | 4        | 4        | 4        | 4        |

| ReRAM cell area per bit size (nm2) with    |      |      |      |          |          | 288      | 288      | 288      | 85       | 85       | 85       | 36       | 36       | 36       | 16       | 16       |

| MLC                                        |      |      |      |          |          | 200      | 200      | 200      | 65       | 65       | 65       | 30       | 30       | 30       | 16       | 10       |

| ReRAM storage density (SLC, 2D)            |      |      |      |          |          | 1.19E+11 | 1.19E+11 | 1.19E+11 | 2.68E+11 | 2.68E+11 | 2.68E+11 | 4.76E+11 | 4.76E+11 | 4.76E+11 | 1.07E+12 | 1.07E+12 |

| ReRAM storage density (MLC, 2D)            |      |      |      |          |          | 2.38E+11 | 2.38E+11 | 2.38E+11 | 8.03E+11 | 8.03E+11 | 8.03E+11 | 1.90E+12 | 1.90E+12 | 1.90E+12 | 4.28E+12 | 4.28E+12 |

| bits/cm2                                   |      |      |      |          |          | 2.30ET11 | 2.30ET11 | 2.30ET11 | 0.U3E+11 | 0.U3E+11 | 0.U3E+11 | 1.30E+12 | 1.502712 | 1.502712 | 4.20E+12 | 4.20E+12 |

| Ref Max. 2D/3D NAND storage density        |      |      |      | 3.40E+11 | 3.40E+11 | 6.47E+11 | 7.33E+11 | 1.14E+12 | 1.23E+12 | 1.73E+12 | 1.73E+12 | 2.73E+12 | 2.95E+12 | 3.21E+12 | 6.68E+12 | 7.30E+12 |

| (MLC, 3D max. layeres) bits/cm2            |      |      |      | 3.40E+11 | 3.40E+11 | 0.4/E+11 | 7.33E+11 | 1.14E+12 | 1.23E+12 | 1.73E+12 | 1.735+12 | 2.736+12 | 2.53E+12 | 3.21E+12 | 0.00E+12 | 7.30E+12 |

| ReRAM 3D layers (using 4F2 GAA x-y         |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| selector + high ON/OFF ratio in-layer      |      |      |      |          |          | 4        | 4        | 4        | 8        | 8        | 8        | 16       | 16       | 16       | 32       | 32       |

| selecting device)                          |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| ReRAM cell area per bit (nm2) with MLC     |      |      |      |          |          | 72       | 72       | 72       | 10.67    | 10.67    | 10.67    | 2.25     | 2.25     | 2.25     | 0.5      | 0.5      |

| and 3D layers                              |      |      |      |          |          | 12       | 12       | 12       | 10.07    | 10.07    | 10.07    | 2.23     | 2.23     | 2.23     | V.3      | 0.5      |

| ReRAM array efficiency (%) (using 4F2      |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| GAA x-y selector + high ON/OFF ratio       |      |      |      |          |          | 48.6%    | 48.6%    | 48.6%    | 46.0%    | 46.0%    | 46.0%    | 43.6%    | 43.6%    | 43.6%    | 41.5%    | 41.5%    |

| in-layer selecting device)                 |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| ReRAM storage density (MLC, 3D max.        |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| layeres, using 4F2 GAA x-y selector +      |      |      |      |          |          | 6.75E+11 | 6.75E+11 | 6.75E+11 | 4.31E+12 | 4.31E+12 | 4.31E+12 | 1.94E+13 | 1.94E+13 | 1.94E+13 | 8.30E+13 | 8.30E+13 |

| high ON/OFF ratio in-layer selecting       |      |      |      |          |          | 6.73E+11 | 0.73E+11 | 0.73E+11 | 4.51E+12 | 4.51E+12 | 4.51E+12 | 1.84E+15 | 1.54E+15 | 1.54E+15 | 0.30E+13 | 0.30E+13 |

| device) bits/cm2                           |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| ReRAM nonvolatile data retention (years)   |      |      |      |          |          | >10      | >10      | >10      | >10      | >10      | >10      | >10      | >10      | >10      | >10      | >10      |

| 85C                                        |      |      |      |          |          | >10      | 710      | 710      | 710      | >10      | >10      | 710      | 710      | >10      | >10      | >10      |

| ReRAM write endurance (read/write          |      |      |      |          |          | 1.0E+09  |

■ワード線が平面電極 :巨大キャパシタ、コンタクトの取り方など 課題は多い。

Source: IEDM 2012, Chen et al, "HfOx Based Vertical Resistive Random Access Memory for Cost-Effective 3D Cross-Point Architecture without Cell Selector",

## 2013年版 Reliability (全面改訂)

- TDDB,BTIにフォーカス

- ・2013年のVddを10年間保証する最大電圧(Vmax)と仮定

- ・世代ごとに10年間保証する最大電圧を記載

| Year of Production                                                                                                                        | 2013    | 2016    | 2019    | 2022  | 2025  | 2028  |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|-------|-------|

| Logic Industry "Node Range" Labeling (nm) [based on $0.71x$ reduction per "Node Range" ("Node" = $\sim 2x$ Mx)                            | "22/20" | "16/14" | "11/10" | "8/7" | "6/5" | "4/3" |

| Logic Industry "Generation" Label (nm) [based on 0.71x Mx reduction per "Generic Node" (or .5x cell; 2x density);beginning 2013/"G1"/40nm | "G1"    | "G2"    | "G3"    | "G4"  | "G5"  | "G6"  |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (contacted)                                                                                            | 40      | 28.3    | 20.0    | 14.2  | 10.0  | 7.1   |

| Lg Proposed for 2013 (Bulk, SOI, MG)                                                                                                      | 20.00   | 15.22   | 11.58   | 8.82  | 6.71  | 5.11  |

| Vdd Proposed for 2013 (Bulk, SOI, MG)                                                                                                     | 0.864   | 0.813   | 0.765   | 0.720 | 0.678 | 0.638 |

| EOT Proposed for 2013 (Bulk, SOI, MG)                                                                                                     | 0.80    | 0.70    | 0.61    | 0.54  | 0.47  | 0.41  |

| nTDDB Vmax (Max Vdd for 10 years mean lifetime)[1]                                                                                        | 0.864   | 0.838   | 0.815   | 0.796 | 0.779 | 0.765 |

| nMOSFET pBTI Vmax (Max Vdd for 10 years mean lifetime)[2]                                                                                 | 0.864   | 0.799   | 0.745   | 0.701 | 0.664 | 0.634 |

| pMOSFET nBTI Vmax (Max Vdd for 10 years mean lifetime)[3]                                                                                 | 0.864   | 0.768   | 0.692   | 0.630 | 0.581 | 0.542 |

#### CMOS

・設計の強い希望により、planar bulk PMOSに限りfT値を テーブルに追加。PIDSのIon\_nとIon\_pの比を用いる。

#### ■Bipolar

・高速のSiGe PNPは、テーブルから削除。 C-BiCMOSとしての利用が非常に少ないため。

#### III-V

- •InP HEMTとGaAs HEMTは一つにして、メトリックを統一。

- •InGaP HBTは、ポータブルデバイスのパワーアンプとしての要求があるため、再度、載せることにする。

- •InP HBTのメトリックは、SiGe biolarと合わせることにする。

### 日本PIDS 2014年の予定

- オン電流低減の見直し Weff / Wfootprint の導入

- •FinFETのオン電流を Weff / Wfootprint を用いて定義する Ids = Idsat(PIDS table) × Weff / Wfootprint

- ・現状の定義は Weff = 2 × Fin height, Fin Pitch=0.75 × (M1 harf pich) 結果、Weff / Wfootprint=1.6 (Intel22nmは、1.27)

- メモリ大手へのサーベイの実施

- •DRAM、NAND Flashで実施

- ・ORTCと整合し、7月までに原案を作成予定

- ■メモリの4F²セル、3Dセルの実現に向けての課題の整理

- RF & A/MS CMOS:ファンダリーを含む大手のサーベイを実施

- •PIDSのテーブルを基に、RF/AMSの CMOS ロードマップを作成してきたが、 実測と異なっており、その見積もり方法の検証が必要 メタルゲートや化合物半導体(III-V, Ge, etc)もテーブル化されており、 これらの技術に対しても検証が必要。

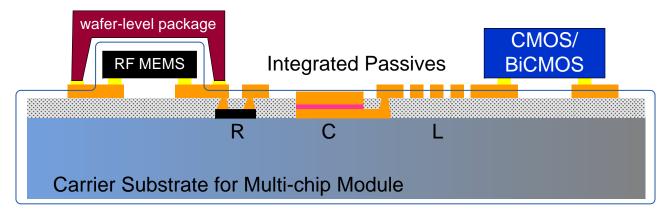

#### ■On-Chip Passives

- ■受動部品は、基板上で作成されるon chip passiveについてRoadmap table が存在する。

- •今後は、実装基板上で作成されるものやMEMSによる高性能化が求められ るため、コラボレーションして受動部品のロードマップを考案する。

### まとめ

- STRJ WG6の活動を報告した。

- ITRS2013のPIDS、RF/AMSを紹介し、 日本PIDS: STRJ WG6の2014年に向けた活動を紹介した。