# 2014年度STRJワークショップ 異種デバイスを対象とするテストの課題

WG2(テストWG) 安藏 顕一(東芝)

#### 目次

- 1. テストWG活動の位置づけ

- 2. WG2体制

- 3. 世界の潮流と日本の現状

- 4. 2014年度活動

- 5. ATE-SWG活動

- 6. DFT-SWG活動

- 7. WG2活動まとめ

| 略語     | 用語                                         | 説明                                                                       |

|--------|--------------------------------------------|--------------------------------------------------------------------------|

| ATE    | Automatic Test Equipment                   | 大型テスタ他テスト装置・システム全般の呼称                                                    |

| DFT    | Design for Test/Testability                | テスト容易化を考慮した設計                                                            |

| DFX    | Design for X                               | Xを考慮した設計、DFTだけでなく、DFR (Design for Repair)、DFY (Design for Yield)なども含めた総称 |

| ATPG   | Automatic Test Pattern Generation          | 自動テストパターン生成                                                              |

| BOST   | Built-Out/Off Self-Test                    | テスタの計測機能を補完する為にテスト・ボード上にテスト機能回路を搭載する手法                                   |

| BIST   | Built-In Self-Test                         | チップ内蔵の自己テスト                                                              |

| SoC    | System-on-a-Chip                           | 複数の機能ブロックなどを一つのLSIに搭載してシステムを実現する設計手法                                     |

| SiP    | System-in-a-Package                        | 複数のLSIを一つのパッケージに搭載してシステムを実現する設計・実装手法                                     |

| TSV    | Through-Silicon Via                        | シリコン製半導体チップの内部を垂直に貫通する電極。主に3D ICの積層チップ間接続に使用。                            |

| DPM(O) | Defects per Million (Opportunities)        | 百万回(個)のうち、欠陥が含まれる割合。製品の品質を示す指標として用いられる                                   |

| IP     | Intellectual Property                      | 一般には知的財産の意。LSI設計では、ある機能を実現する回路部品の情報を意味する                                 |

| OSAT   | Outsourced Semiconductor Assembly and Test | 半導体組み立て検査受託会社                                                            |

| IJTAG  | Internal Joint Test Action Group           | IEEE1687規格の通称。チップに搭載されている様々なIPをテストするための規格。                               |

| 用語                       | 説明                                                          |

|--------------------------|-------------------------------------------------------------|

| ハンドラ                     | テスト時のチップの搬送、テストソケットへの装着、温度制御等を一貫して行う装置                      |

| プローブカード(Probe Card)      | ウェーハ上のLSIを電気測定するための冶具。髪の毛以下の太さの針(プローブ)の集合体                  |

| バーンイン                    | チップの初期劣化不良を検出するため熱・電圧ストレス等を長時間かける工程                         |

| テストソケット                  | テスト時にLSIパッケージを挿入固定するための治具                                   |

| 治工具                      | ソケットやプローブカード、インタフェースボード等、テスト時に必要な治具                         |

| 構造化テスト                   | LSIの機能をテストするのではなく、LSIが設計通りの構造に出来上がっているかをテストする手法             |

| スキャンテスト                  | ランダムロジックを対象とするDFTの代表的手法                                     |

| 同測テスト                    | 複数のチップを同時にテストする手法、多数個同時測定テスト。テストスループット向上によるコスト低減が可能         |

| コンカレントテスト                | チップ内の複数のコアおよび回路を並列にテストする手法                                  |

| トグル率                     | 全クロック数におけるゲート出力の反転回数(トグル数)の割合                               |

| 同測効率                     | テスタの多数個同時測定効率 N個同測のテスト時間を T0+T1×N とすると同測効率は T0/(T0+T1)      |

| IR-Drop                  | 配線の抵抗成分による電位降下のこと。半導体の特性で信号遅延などを起こす                         |

| 高速IO(HSIO/High speed IO) | LSIが外部と高速にデータ送受信を行うための回路やインタフェース。USB,DDR,SATA等標準規格がある       |

| 3D IC                    | チップ同士を三次元的に積層し、TSV等で互いに接続した構造を持つIC。                         |

| コアテスト                    | チップをコア(IPブロック等)単位で試験する手法。コアテストのためのインターフェース規格としてIEEE1500がある。 |

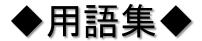

# 1. テストWG活動の位置づけ

- テスト=製造工程において、良品/不良品を選別するための手段

- LSIテスタを用いることが一般的

- LSIとLSIテスタの接続のために、様々な検査治具を用いる

- 【プローブカード、プローバ、ハンドラー、<u>ソケ</u>ット、検査ボード・・・

- LSIにはテストを容易にするための設計(DFT)を施している

## 1. テストWG活動の位置づけ: ITRS2.0

"Heterogeneous Integration" Focus Teamを中心に活動

2005~2010年度: SiPのテスト技術について調査、課題検討

・さまざまな種類のダイを1パッケージで実装した場合のテスト とDFTの技術的課題を抽出

2011~2012年度: 3D-ICのテスト技術の調査、課題検討

-TSV(Through Silicon VIA)ベースの積層IC

SoCモデルがフィーチャーフォン からスマートフォンモチーフへ 2015年以降の異種デバイス統合の現状は?

- Analog/Mixed-Signal、MEMS/RF

- Photonics

- -2.5D/3D IC

テストとDFTの技術課題を抽出し、 解の候補を探る

# 2. WG2体制(2015/02現在)

|                               | DFT-SWG                                                                                    | ATE-SWG                                                                 |

|-------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 委員                            | 安藏(東芝) WGリーダ<br>濱田(富士通セミコンダクター)サブ<br>リーダ<br>青木(ソニーLSIデザイン)<br>佐々木(ルネサスシステムデザイン)<br>佐藤(ローム) | 田村(ルネサス セミコンダクタ パッケージ&テスト ソリューションズ)サブリーダ<br>平山(富士通セミコンダクター)<br>武田(東芝)   |

| 特別委員<br>(SEAJ技術部会<br>検査専門委員会) | テスト装置メーカー<br>からの知見を得る<br>目的で参加                                                             | 北川(アドバンテスト) 近藤(アドバンテスト) 清水(東京エレクトロン) 鈴木(浜松ホトニクス) 薗田(シバソク) 清藤(日本マイクロニクス) |

| 特別委員<br>(大学その他)               | 佐藤(九州工業大学)<br>畠山(群馬大学)<br>清水(スパンション・イノベイツ)                                                 | 多田(徳島文理大学)<br>佐藤(TRL)<br>堀部(エスティケイテクノロジー)<br>渡辺(スパンション・イノベイツ)           |

全21名

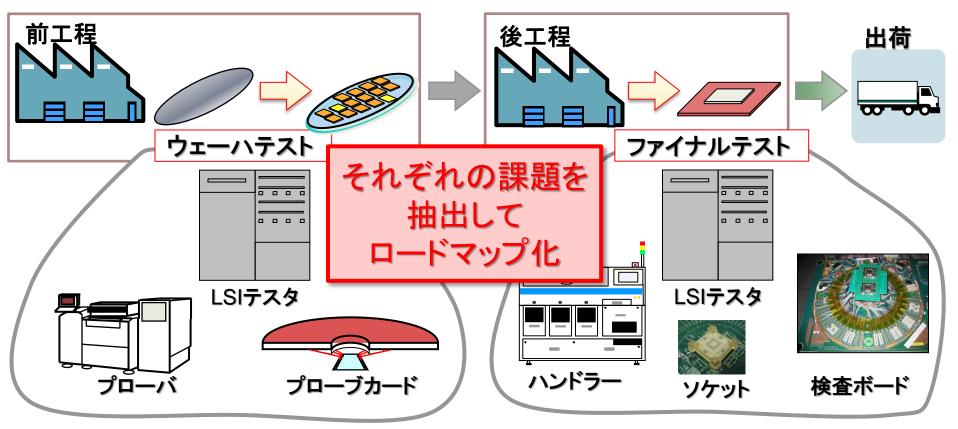

# 3. 世界の潮流と日本の現状[測定データ活用の浸透]

Work in Progress - Do not publish

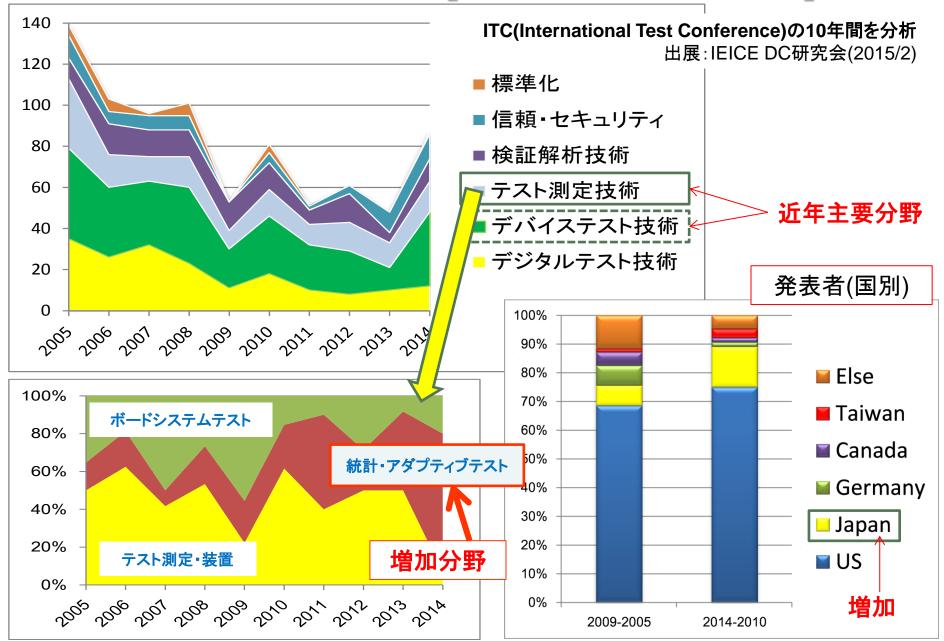

## 3. 世界の潮流と日本の現状[新デバイスで台湾の増加] STRD

**Work in Progress - Do not publish**

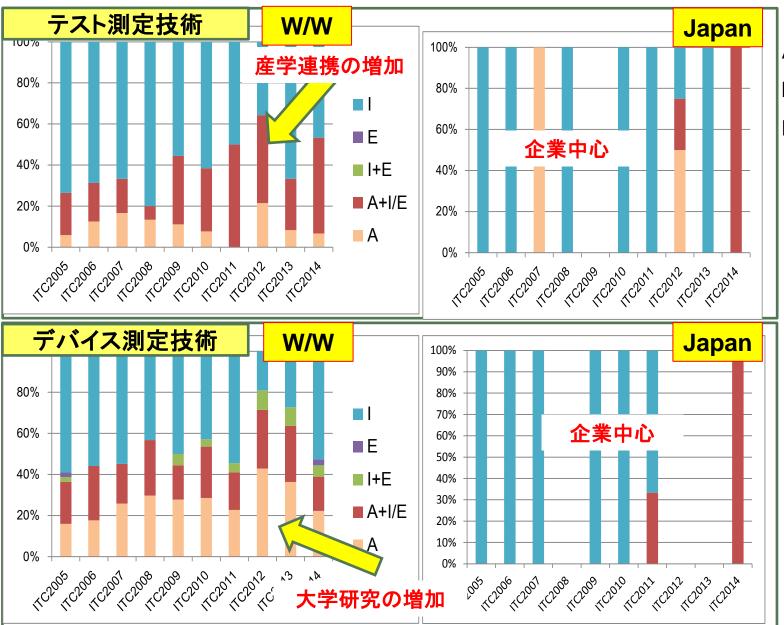

## 3. 世界の潮流と日本の現状 [産学連携の有効活用]

A: Academia

I:Industry

E:EDA vendor

# 4. 2014年度活動

| 区分   | 活動内容     |                                                       |

|------|----------|-------------------------------------------------------|

| 国際活動 | ITRS2014 | ・ITRS2.0に対応した今後の活動内容を議論 ・テストコストの考え方について議論             |

|      | 国際会議     | ・ドイツ会議、韓国会議に出席                                        |

|      | WG2      | ・ITRS2013の和訳                                          |

| 国内活動 | ATE-SWG  | ・非接触プロービングの技術調査<br>・MEMSのテスト、テストコスト削減の技術調査            |

|      | DFT-SWG  | ・ITRS2015改訂対応(コンカレントテスト テーブルの定量化)<br>・低電力設計対応テストの課題抽出 |

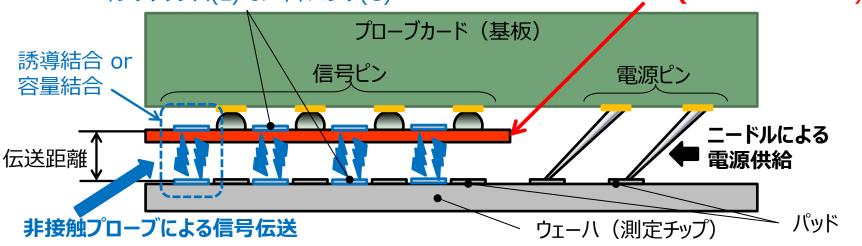

### > 非接触プロービングの期待分野

◆KGD(Known Good Die)対応(ウェーハやベアチップの高速テスト)、 3D ICのテスト(TSVのテスト)、ウェーハー括テスト(コンタクト荷重低減)等

#### > 非接触プロービングの状況

◆大別して2つの方法があり、それぞれ要素技術は確立しているが、一長一短があり、また、量産関係の課題も多く、現時点で実例は、あまり見受けられない。

### > 非接触プロービングの現状比較 (誘導型と容量型)

|           | 誘導型(インダクタ)                                            | 容量型(キャパシタ)               |

|-----------|-------------------------------------------------------|--------------------------|

| 伝送速度      | 〇:数Gbps以上                                             | 〇:数Gbps以上                |

| 伝送距離      | <b>Δ</b> : 100um程度 ※コイル径に依存                           | ▲: 数um程度 ※容量に依存          |

| 面積オーバヘッド  | ▲ : コイル作成のためやや大きいが、<br>パッド周辺への配置など省面積化は可能             |                          |

| 消費電力      | O: 1mW/Gbps以下                                         | ▲ :数mW/Gbps以下            |

| 量産コスト     | <ul><li>: 非接触プロービングICの<mark>設計・製造が必要</mark></li></ul> | × : 非接触プロービングICの設計・製造が必要 |

| プローブカード製造 | △: 非接触プロービングICの実装が困難                                  | × : 非接触プロービングICの実装が非常に困難 |

### > 非接触プロービングの実施例

インダクタンス(L) or キャパシタ(C) 非接触プロービングIC(信号伝送用IC)

- > 非接触プロービング適用の問題点

- ◆非接触プロービングICの設計・製造を製品毎に行うことが必要

- ◆非接触プロービングICのプローブカード実装が困難(並行度、高さばらつき抑制)

- >今後の要求項目(小ピン製品のKGD対応から適用をめざすには)

- ◆製品設計を含め、非接触プロービングICの標準化によるコスト削減の実施

- ◆ 伝送距離の拡大によるプローブカード製造負担の軽減(並行度、高さばらつきを吸収)

- ◆非接触ブロービングIC不要(ミリ波による非接触プローブ等)の新技術の適用検討

### 5. ATE-SWG活動: MEMSテストの検討-1

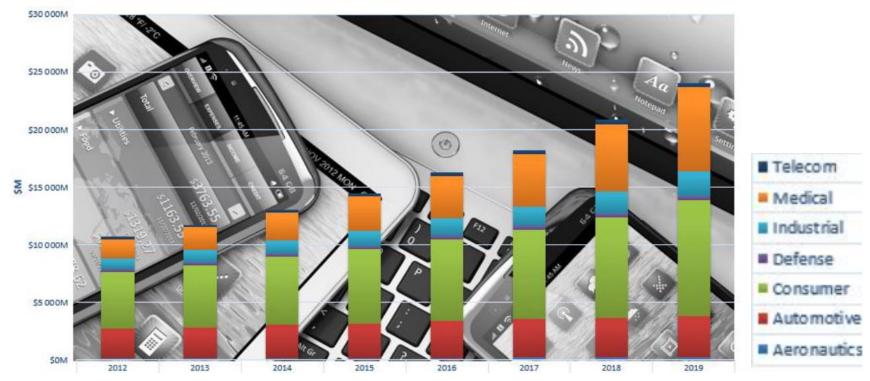

#### > MEMSの市場動向

- ·IoT/IoEの普及に合わせ、市場は年+10%以上の伸び率

- ・各分野とも堅調に成長、特にメディカル向けは高成長(23.9%: 2013-2019 CAGR)

### 2012-2019 MEMS Markets by Application (US\$M)

Source: Yole 2014

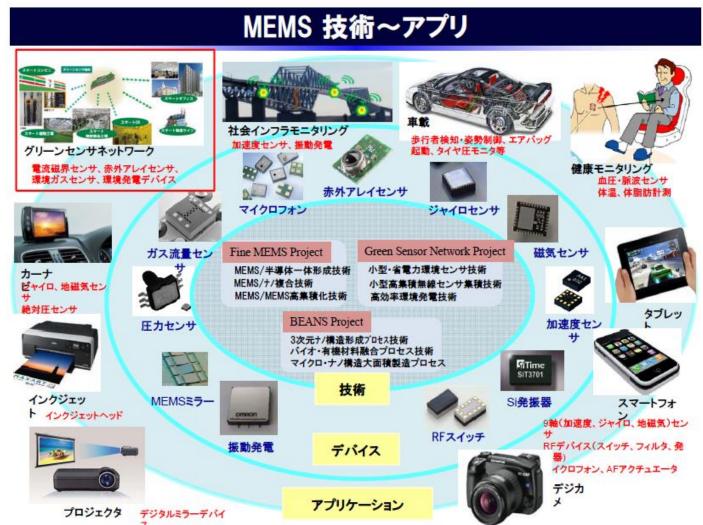

#### ➤ MEMSの技術とアプリケーションの動向

・センサの種類も用途も多い。 **近年スマートフォン用加速度センサ、ジャイロが増加。**

Source: センサ技術の課題と現状: マイクロマシンセンター 2013/12/17

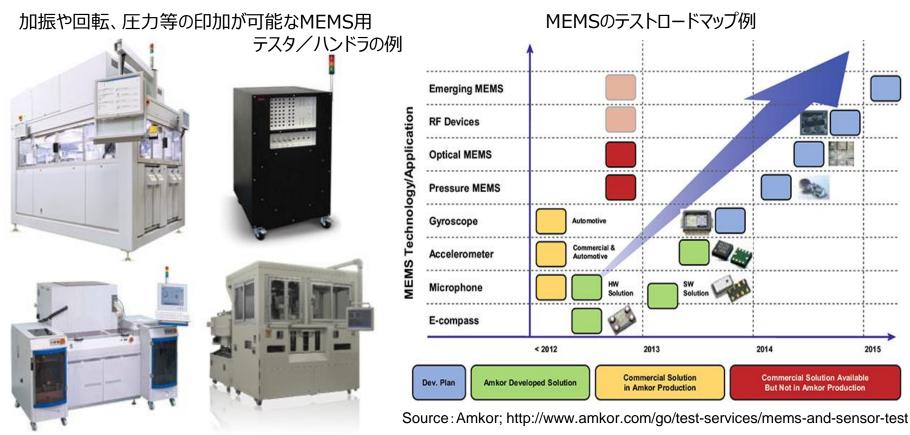

### 5. ATE-SWG活動: MEMSテストの検討-3

#### ➤ MEMSテストの状況

- **◆テストコストが製品コストの20%~50%**を占める(ITRS2013)

- ◆加振や回転、圧力等を印加するテストが高コストの要因、テスタ/ハンドラも高額

- ◆多自由度化、マルチファンクション対応が進み、**テストが複雑化**

- ◆OSAT(組立・検査受託会社)でもLSIと同様テストサービスが展開され始めている

Work in Progress - Do not publish

### 5. ATE-SWG活動: MEMSテストの検討-4

#### > MEMSテストの課題

- ◆テストコストが最大の課題

- ◆テストコスト削減検討に向け、WG15(MEMS WG)と協働することを合意

- ・目標: ITRS2015 ロードマップ掲載

- 対象:加速度/角加速度センサから検討

- ・重要課題の検討

- ①テスト項目の分類(通常の電気的テスト、機械的な印加を伴ったテスト等)

- ②各テスト項目のスペックやそのコストトレンドの予測

- ③上記予測に際し、測定限界に近づいているテスト項目についての検討

- ④標準化の検討(テスト項目やテストスペック、テスタ/ハンドラ等)

#### > 今後の活動

◆WG15とのクロスカット(WG間技術交流)活動を行い、ITRS2.0 の"Heterogeneous Integration"の一環としてITRS2015へのロードマップ掲載を提案する

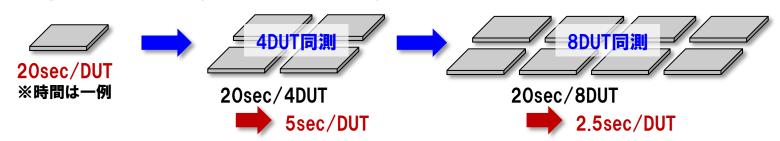

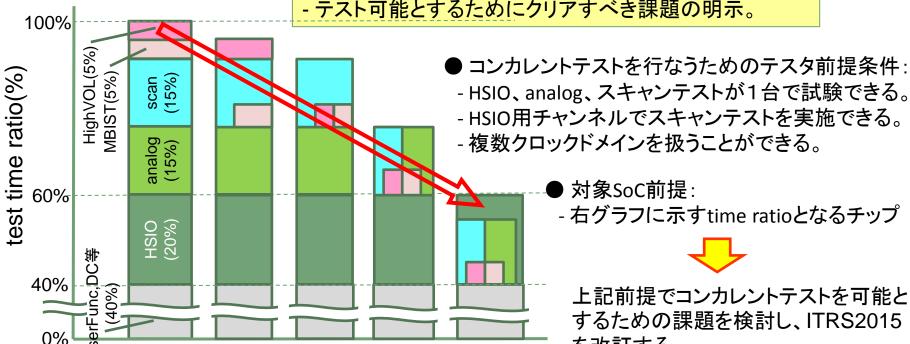

### 6. DFT-SWG活動: テストコスト上昇への対策

#### コストはテスト時間に比例 ⇒並列化による時間短縮

#### 対策①:同時測定数の向上

同時に測定するDUT (Device Under Test)を増やす。

注)実際には同時測定効率、プローブカード費用等の考慮要

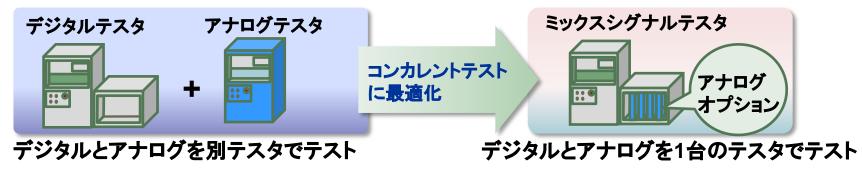

#### 対策②:コンカレントテストの導入

1DUTの中で同時に測定する項目を増やす

Logic: 7sec

メモリ: 1sec

通常IO: 2sec HSIO: 6sec

HSIO: 6sec アナログ: 4sec

Total: 20sec

以下の組合せでコンカレント

➤ Logic +メモリ

Logic+HSIO

Logic: 7sec

メモリ: 1sec 通常IO: 2sec

世帯10・ 25ec HSIO: 6sec

アナログ: 4sec Total: 13sec

※時間は一例

### 対策①と対策②を併用すれば、更にテスト時間短縮が可能

### 6. DFT-SWG活動: コンカレントテスト導入への課題

### ◆ 技術的課題

- ✓ メモリBISTとロジックテストの同時試験対応

- ✓ 多くのコアに対する柔軟な同時試験対応(Power、ノイズ影響を考慮)

- ✓ 使用可能なATE資源に対するDFTの最適化

#### ◆ コスト的課題

- ✓ 追加DFT回路(コアテスト・IJTAG等)及びDFT実装工数増加への対応

- ✓ テスタコストとテスト時間のトレードオフ最適化

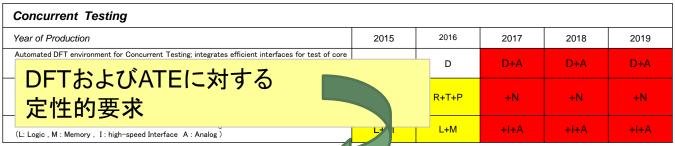

#### 6. DFT-SWG活動: ITRS2015 コンカレントテスト テーブルの定量化

#### [ITRS2013 DFTテーブル]

#### [ITRS2015改訂]

#### 定量化:

- コンカレントテスト対象とそのテスト時間比率を明確化。

- テスト可能とするためにクリアすべき課題の明示。

2016

2017

2018

2019

- 〕コンカレントテストを行なうためのテスタ前提条件∶

- HSIO用チャンネルでスキャンテストを実施できる。

- 複数クロックドメインを扱うことができる。

#### ) 対象SoC前提:

- 右グラフに示すtime ratioとなるチップ

上記前提でコンカレントテストを可能と するための課題を検討し、ITRS2015 を改訂する。

**Work in Progress - Do not publish**

2015

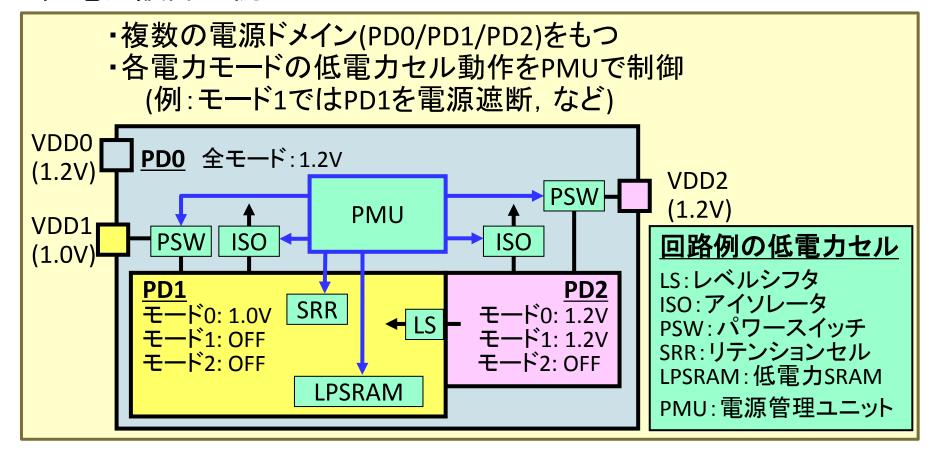

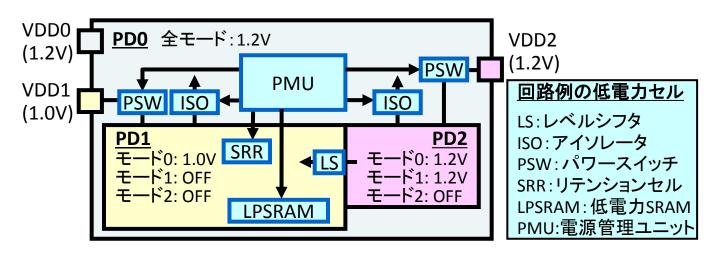

### 6. DFT-SWG活動: 低電力設計対応テスト

• 低電力設計の例

- 低電力セルに対するテストが必要

- パワーオン・オフを考慮したテスト

- 機能(リテンション等)に注目したテスト

低電力機能利用のため 構造化テスト(スキャン) では対応が困難

### 6. DFT-SWG活動: 低電力セルテストーITRS提案内容

"Requirements table"として提案する

Test for low power cells requirements

|   | 検出対象     | 内容                                |  |

|---|----------|-----------------------------------|--|

| 1 | アイソレータ   | 非アクティブ・アクティブの両状態をATPGが制御 しパタンを生成  |  |

| 2 | レベルシフタ   | 仮定故障に当該セルを含んでパタンを生成               |  |

| 3 | リテンションセル | リストア後にセーブ値の保持を確認するパタンを生成          |  |

| 4 | 低電力SRAM  | sleep中に周辺回路を動作させ、セル値保持を確認するパタンを生成 |  |

| 5 | パワースイッチ  | PDのon/offを制御してIDDQ(静止電流)試験パタンを生成  |  |

- COMMents •PMUの制御信号は1-5が実現できれば検出可能である

- •基板バイアス制御回路は、従来テストと5と同様の手法で検出可能である

### 6. DFT-SWG活動:低電力セルテストーEDAベンダヒアリング調査

調査対象: 国内に販売店を持つ4社

調査時期: 2014年11月~12月

調査内容: 低電力設計で用いるセル/回路(青枠)に対する故障

検出機能の実装状況

調査結果:

低電力設計を理解しているDFT技術者が 手間と時間をかけないとできない

### 7. WG2活動まとめ

#### 2014年度活動結果

ITRS: ·ITRS2.0に対応しつつ旧来の活動を継続する方針

ATE: ・非接触プロービングの技術調査完了

・MEMS WG(WG15)とのクロスカット準備完了

ー市場動向、MEMSテスト技術調査、ターゲット製品絞込

DFT: ·ITRS2015コンカレントテストテーブルの定量化作業完了

·Low power cellテストに関し、ITRS2015 Requirements tableへ提案準

備完了

#### 2015年度活動予定

ITRS: ·ITRS2015の担当セクション・テーブルの更新検討、およびITRS2.0対応

ATE: ·MEMSのテストついて継続調査

・異種デバイス混載によるテストの複雑性に対する検討とテストコスト削減

技術の検討を行う

DFT: ・低電力セルテストのITRSへの提案

·MEMSに対するDFTの調査・検討

異種デバイスのテスト・ DFTの課題を検討

# 以上