# WG6(PIDS 及びRF&AMS)活動報告 🖤

# ロジックおよびメモリデバイスの スケーリングトレンド ~見えてきたFinFET時代のスケーリングトレンド~

**STRJ WS 2014** 2015年3月6日 品川:コクヨホール

WG6主査:福崎勇三(ソニー)

#### 用語集

#### ■ PIDS

(Process Integration, Devices, and Structures)

- Logic

- •HP: High Performance

- ·LP: Low Power

- •FD-SOI: Fully-Depleted Silicon On Insulator

- ・MG: Multi Gates --- FinFET, TriGate等の総称

- ·NW: Nanowire

- ·GAA: Gate All Around

- ·Ge: Germanium

- ·III-V: III族-V族化合物半導体

- ·Vdd,VDD: 電源電圧

- ·Ion: オン電流、動作時駆動電流

- ・Wfp: Wチャネル幅のfootprint (MGに対応)

- ・Weff: 実効Wチャネル幅 (MGに対応)

- Tr.: Transistor

- •DIBL: Drain Induced Barrier Lowering

- ·SS: Sub-threshold Swing

#### Memory

- ·SRAM: Static Random Access Memory

- •DRAM: Dynamic Random Access Memory

- •RCAT: Recessed-Channel Array Transistor

- VCT: Vertical Channel Transistor

- MRAM: Magnetic (Tunneling Junction) RAM

- •STT-MRAM: Spin-Torque Transfer MRAM

- PCRAM: Phase Change RAM

- Memory (continuation)

- ·FeRAM: Ferro-electric RAM

- ·ReRAM: Resistance RAM

- •RTN: Random Telegraph Noise

- ·SONOS: Silicon Oxide Nitride Oxide Semiconductor

- •MONOS: Metal Oxide Nitride Oxide Silicon

#### Reliability

- •TDDB: Time Dependent Dielectric Breakdown

- •PBTI: Positive Bias Temperature Instability

- •NBTI: Negative Bias Temperature Instability

#### ■ RF&AMS

(Radio Frequency & Analog/Mixed -Signal)

- ·LNA: Low Noise Amplifier

- VCO: Voltage Controlled Oscillator

- ·PA: Power Amplifier

- •ADC: Analog to Digital converter

- ·SerDes: Serializer Deserializer

- ·HV: High Voltage

- ·CIS: CMOS Image Sensor

## 2014年度 WG6メンバーと活動

主査:福崎勇三(ソニー) 副主査:井上裕文(東芝) 幹事:久本大(日立)

|      | <u> </u>    | リーロ・ハートロス(不た)                                                              | TIT 174774 (H4)                                        |

|------|-------------|----------------------------------------------------------------------------|--------------------------------------------------------|

| SWG  | SSWG        | 委員                                                                         | 特別委員                                                   |

| PIDS | Logic       | 若林整(東工大)<br>井田次郎(金工大)<br>平本俊郎(東京大)<br>高木信一(東京大)<br>赤坂泰志(TEL)<br>吉見信(aBeam) |                                                        |

|      | Memory      | *井上裕文(東芝)<br>岩本邦彦(ローム)<br>笠井直記(NEC)                                        | 杉井寿博(LEAP)                                             |

|      | Reliability | *最上徹(PETRA)                                                                | 丹羽正昭(東北大)                                              |

| RF&  | AMS         | *久本大(日立)<br>田辺昭(ルネサス)<br>安茂博章(ソニー)<br>大黒達也(東芝)                             | <b>田中徹(東北大)</b><br><b>堀敦(日本インター)</b><br>* 印は、SSWG リーダー |

■国際会議 ; ドイツ(4月) 井上委員、平本特別委員、安茂委員、福崎 韓国(10月) 大黒委員、福崎

■国内会議;6回

■ヒアリング ; 3回 2014/8/29 「VLSI2014まとめ」 若林特別委員 2015/1/21 「IoT時代のデバイス」 東工大 益教授 2015/2/13 「IEDM2014まとめ」 若林特別委員

#### PIDS構成

#### ■ロジック

- HP = High Performance (高速)

- LP = Low Power (例;高性能モバイルなど)

- ●III-V/Ge = Si代替となるCh材料、低パワーかつ高速向け

|                                  | HP  | LP     | III-V/Ge HP (HP) |

|----------------------------------|-----|--------|------------------|

| Speed (I/CV)                     | Ref | Slower | Fastest          |

| Dynamic Power (CV2f)             | Ref | Lowest | Mildly lower     |

| Static Power (I <sub>off</sub> ) | Ref | Lowest | Higher           |

#### ■ メモリ

- DRAM

- Non-volatile

- ·電荷蓄積型FET:浮遊ゲート (NOR and NAND)

電荷トラップ型 (NOR and NAND),SONOS,MONOS

·非電荷蓄積型FET: FeRAM, PCRAM, MRAM, STT-MRAM, ReRAM

#### ■ 信頼性

#### **More Moore Mission**

- More MooreをPPAC(Power、Performance、Area、Cost)の評価軸で維持して、Big Data, Mobile, クラウド (IoT, サーバ)用途デバイスのスケーリングを行う為に必要な物理的、電気的、信頼性の要求スペックの提示

- ■ロジックとメモリの主流となる量産技術について15年間のデバイス技術ロードマップの策定

- □技術範囲 (PIDS) : Scopes

- ・デバイス性能(速度、密度、電力等)

- ・デバイス構造

- ・新規プロセス・インテグレーション技術

- ·信頼性

## Cloud and mobile computing drives More Moore Williams

## Application KPIs and PPAC scaling for More Moore Will

- KPI: 高パフォーマンス @ 同一パワー密度

- 制約:温度,エネルギー消費

#### Mobile computing

- KPI:同一パワー、コストにおいて性能と機能の向上

- 制約:コスト、バッテリ、他の部品のリークも増大

#### ●自律センシング & コンピューティング (IoT)

- KPI:リーク削減、Vth近傍のバラつき低減

- 制約:フォームファクタ、コスト、セキュリティ

#### More Moore platform for node-to-node PPAC value

- **P**erformance: >50% 高性能 @ 同一パワー

- Power: >60% パワー削減 @ 同一性能

- Area: >50% エリア削減

- Cost: <25% ウエファーコスト増 … 30%コストダウン @同一機能チップ

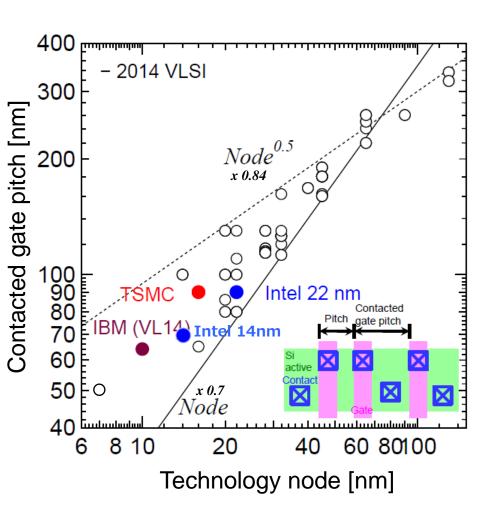

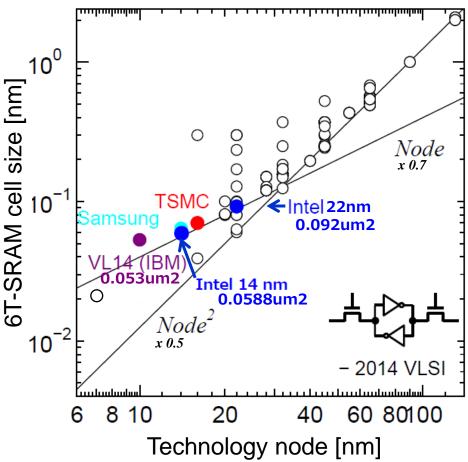

## Area scaling per technology node

## ■ Pitch scalingは進行中

# ■ SRAM-cell-size scalingは鈍化傾向

出典;東工大 若林特別委員

STRJ WS: March 6, 2015, WG6 PIDS

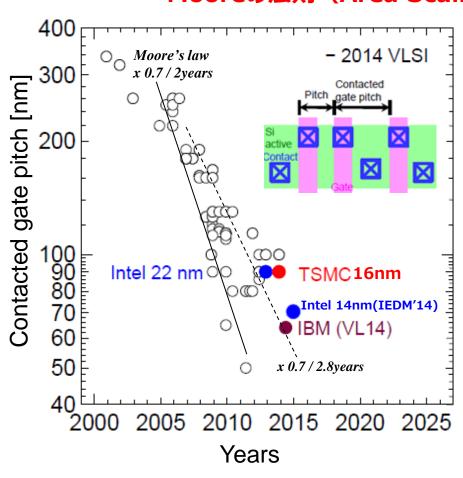

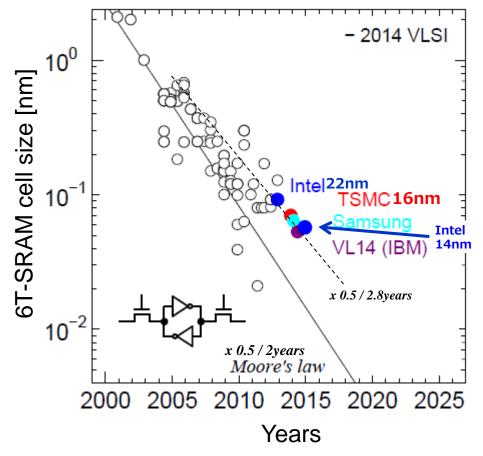

## Area scaling per years

## ■ Scalingは2.8年毎に鈍化

# ■ SRAM-cell-size scalingも2.8年毎に鈍化

Mooreの法則(Area Scaling)は近年鈍化傾向(2年→2.8年)

出典;東工大 若林特別委員

STRJ WS: March 6, 2015, WG6 PIDS

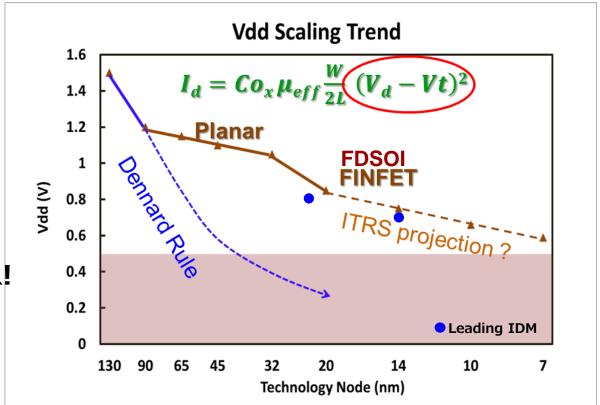

## Vdd scaling slowed down since N90

## **Mobile Computing – The Vdd Scaling Issue**

Vdd scaling most difficult: V<sub>t</sub> associated with leakage – SCEs, RDF

Past: Flops/Sec

Now: Flops/W

**ALL ABOUT POWER!**

N90: 90nm Node

FOM: Figure of Merit

SCE: Short Channel Effect

Low Power Device: SS, DIBL, σΔVt

RDF: Random Dopant Fluctuation

## 2013 ITRS, scaling knobs

11

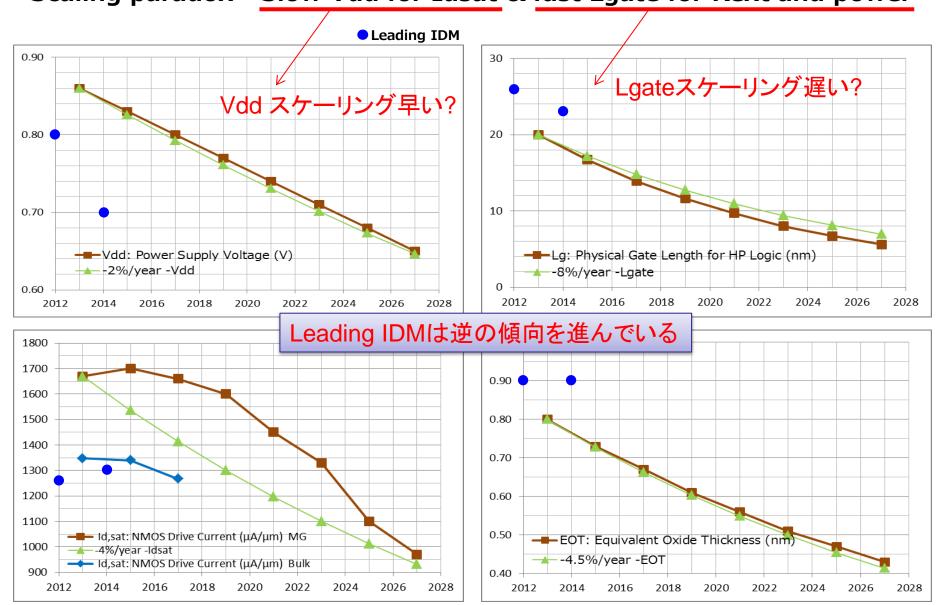

Scaling paradox - Slow Vdd for Idsat & fast Lgate for Rext and power

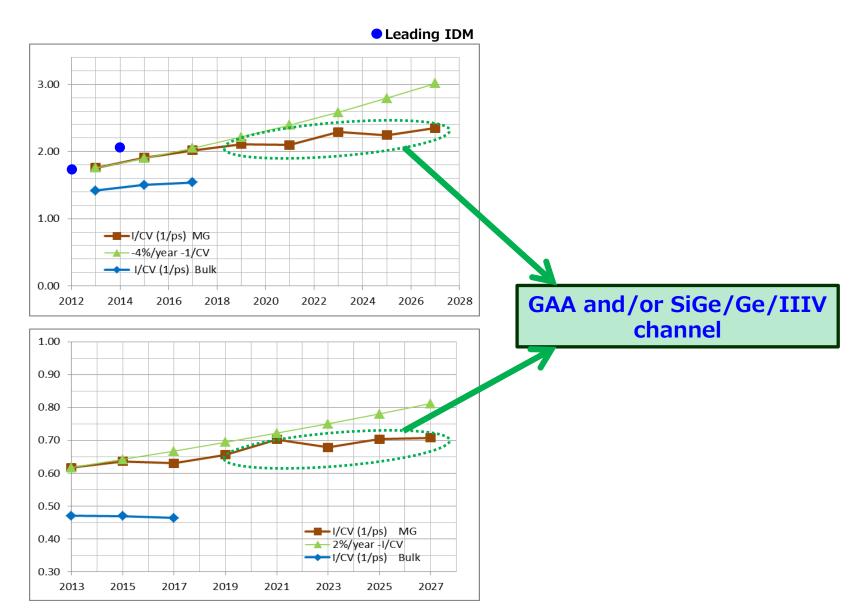

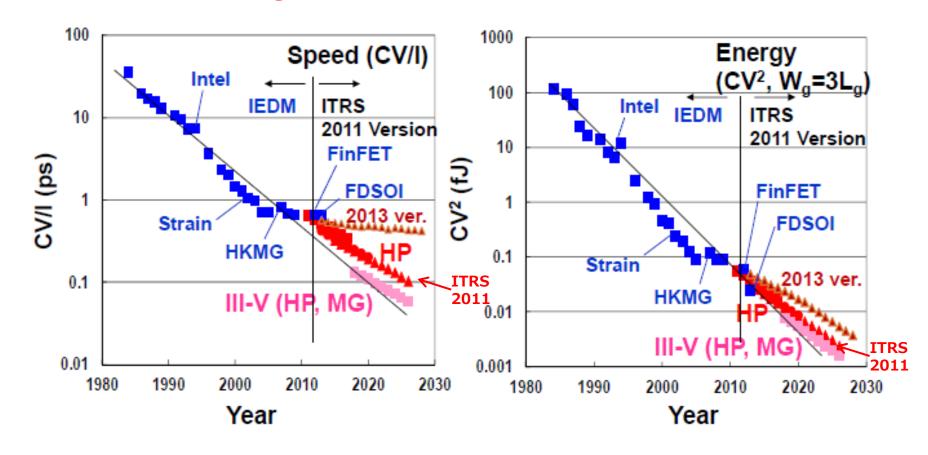

## ITRS 2013, performance

## ITRS2011→2013で鈍化傾向

#### 性能指標 4% キープ @2013 ITRS → 従来から鈍化

出典;東大 平本特別委員

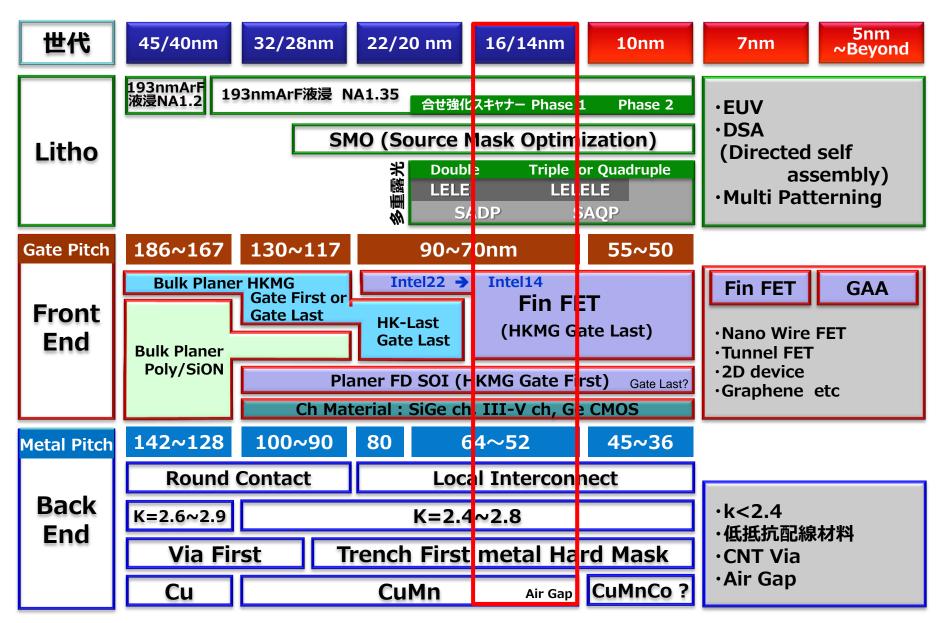

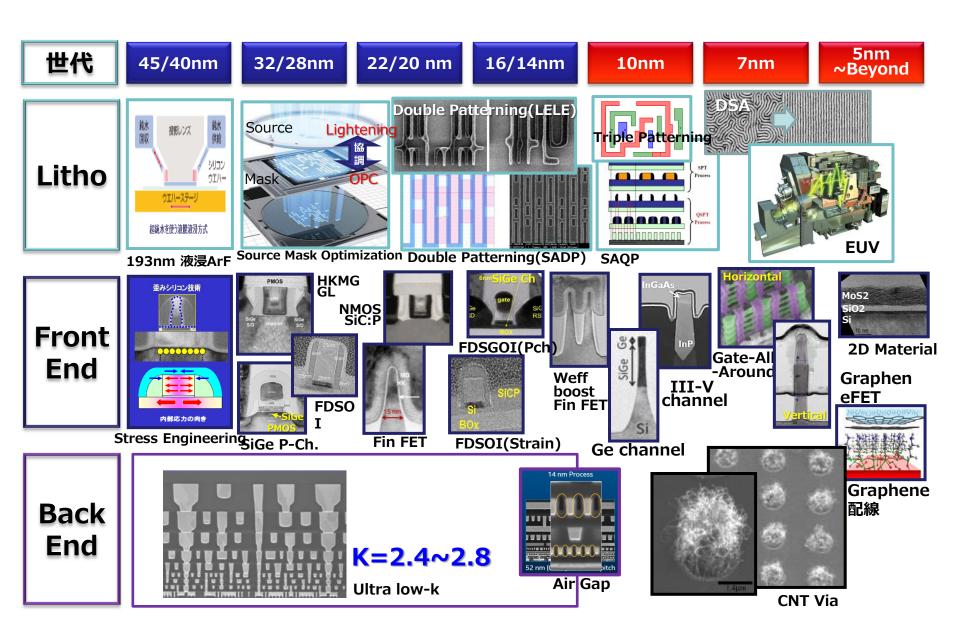

## 世代毎のTechnology

## 世代毎のTechnology(説明)

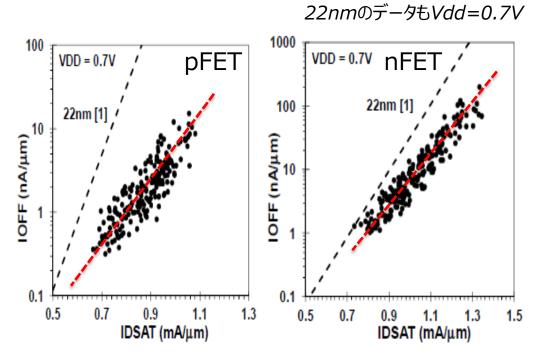

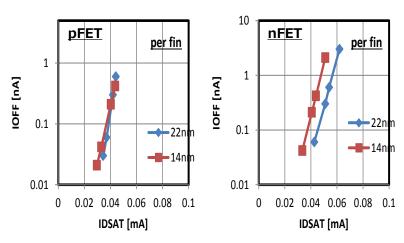

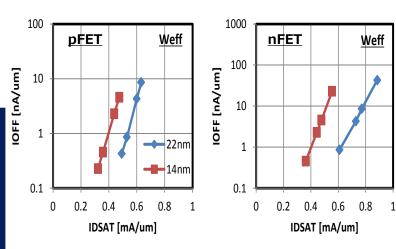

## 14nm FinFET, Leading IDM

#### DC特性;単位Wfp(FootPrint)で規格化

- ✓ 単一Weff当たりのIon/Ioffは22nmの方が良い

- ✓ Fin高さを増加→単位Wfp当たりのWeff(電流パス)を稼ぎ、実効的な電流を増大させている

- ✓ この時、Weffで見たときIoffを改善させている Fin幅をスケーリングしているので電界強度はUp

#### Fin当たりの特性

#### 単位Weffで規格化

#### Scaling enablers for coming nodes

17

|                            | 2014             | 2016             | 2018                 | 2021                      | 2024                      | 2027                      |

|----------------------------|------------------|------------------|----------------------|---------------------------|---------------------------|---------------------------|

| Node                       | N14              | N10              | N7                   | N5                        | N3                        | N1.5                      |

| Ground rules(CPP,MP,FP,LG) | 70,52,42,22      | 52,36,27,16      | 42,24,18,12          | 32,16,12,10               | 25,10,NA,10               | 25,10,NA,10               |

| Device structure           | finFET<br>Planar | finFET<br>Planar | finFET<br>Lateral NW | Lateral NW                | Stacked<br>Vertical NW    | Stacked<br>Vertical NW    |

| Substrate                  | Si, SOI          | Si, SOI          | Si, SOI, SRB         | Si, SOI, SRB              | Si, SOI                   | Si, SOI                   |

| S/D strain                 | Yes              | Yes              | Yes                  | Yes                       | Yes                       | Yes                       |

| Strained substrate         | No               | Yes              | Yes                  | Yes                       | Yes                       | Yes                       |

| N-Ch                       | Si               | sSi              | sSi, Ge              | sSi, Ge, IIIV             | sSi, Ge, IIIV             | sSi, Ge, IIIV             |

| P-Ch                       | Si               | SiGe             | SiGe, Ge             | SiGe, Ge                  | Ge                        | Ge                        |

| Transport scheme           | DD               | Quas<br>Ballis.  | Ballistic            | Ballistic<br>Band-engine. | Ballistic<br>Band-engine. | Ballistic<br>Band-engine. |

| Contact scheme             | Silicide, DC     | MIS, DC          | MIS, DC              | MIS, DC                   | MIS, DC                   | MIS, DC                   |

| Vdd                        | 0.70             | 0.65             | 0.60                 | 0.55                      | 0.50                      | 0.45                      |

| Weff at unit footprint     | 2                | 2.5              | 4                    | 6                         | 6                         | 6                         |

| Leading IDM             | 22nm | 14nm | 10nm?  |

|-------------------------|------|------|--------|

| Fin Height              | 34   | 42   | 50 ?   |

| Wfin                    | 10   | 9    | 8?     |

| Weff at unit footprint  | 1.3  | 2.2  | 3.6 ?  |

| Ratio Weff Node to Node | N/A  | 1.7  | 1.63 ? |

N14: 14nm Node

CPP: Contacted Poly Pitch

MP: Metal Pitch

FP: Fin Pitch

LG: Gate Length

NW: Nanowire

MIS: Metal Insulator Silicon

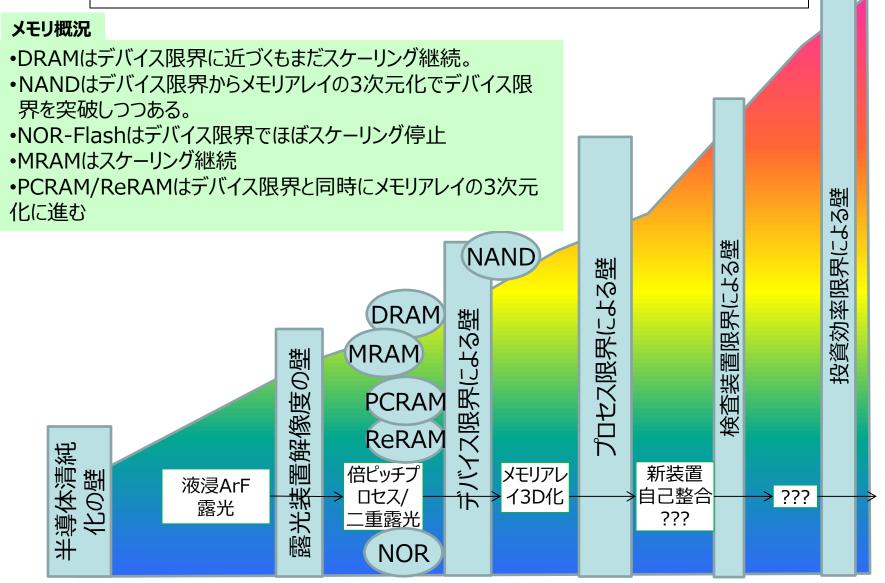

## メモリのトレンドと今後のスケーリング見込み

メモリデバイスのスケーリング状況と今後の壁イメージ図

## DRAMの状況と2015年活動計画

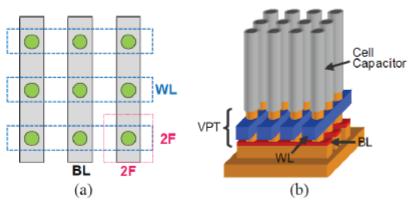

日本PIDSの調査結果を反映した2013年版では、ハーフピッチはや粉緩和。縦型トランジスタ (VCT)導入は2年遅れの2016年から、以降、リセスチャネルトランジスタ (RCAT+Fin)を置き換える。これに伴い、6F<sup>2</sup>から4F<sup>2</sup>の移行も2年遅延し2016年

上記トレンドも大きく変わらず2014年はほぼ2013年版通りにスケーリング。2015年版に向けて、再度日本PIDSがサーベイを含めトレンドを調査。特に4F2化の遅れ状況を反映させる予定。

|           | Year of Production                               | 2013       | 2014               | 2015               | 2016            | 2017 | 2018 | 2019 | 2020 |

|-----------|--------------------------------------------------|------------|--------------------|--------------------|-----------------|------|------|------|------|

| NEW       | MPU/ASIC Metal 1 (M1) 1/2 Pitch (nm) (contacted) | 40         | 32                 | 32                 | 28.3            | 25.3 | 22.5 | 20.0 | 17.9 |

| WAS       | Half Pitch (Contacted line) (nm)                 | 28         | 25                 | 22                 | 20              | 18   | 16   | 14   | 13   |

| IS        | Half Pitch (Contacted line) (nm)                 | 28         | <b>26</b>          | 24                 | 21              | 20   | 18   | 16   | 15   |

| WAS       | DRAM cell FET structure [6]                      | RCAT+Fin   | VCT                | VCT                | VCT             | VCT  | VCT  | VCT  | VCT  |

| IS        | DRAM cell FET structure [6]                      | RCAT+Fin   | RCAT+Fin           | RCAT+Fin           | VCT             | VCT  | VCT  | VCT  | VCT  |

| WAS       | Cell Size Factor: a [11]                         | 6          | 4                  | 4                  | 4               | 4    | 4    | 4    | 4    |

| <b>IS</b> | Cell Size Factor: a [11]                         | 6          | 6                  | 6                  | 4               | 4    | 4    | 4    | 4    |

| NEW       | Gb/1chip target                                  | 4 <b>G</b> | 8G                 | 8 <b>G</b>         | 8 <b>G</b>      | 8G   | 16G  | 16G  | 16G  |

|           |                                                  | Manu       | ıfacturable soluti | ons exist, and are | being optimized |      |      |      |      |

|           |                                                  |            | Ma                 | nufacturable solu  |                 |      |      |      |      |

|           |                                                  |            |                    | hterim solut       | tions are known | •    |      |      |      |

|           |                                                  |            | Manufa             | rturable colutione | are NOT known   |      |      |      |      |

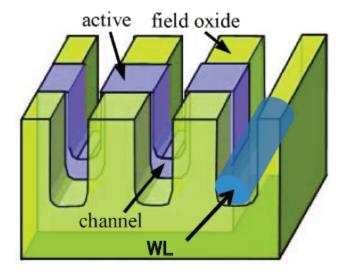

## 参考)DRAMセルトランジスタ構造

埋め込み型サドルFinトランジスタ(現在)

- RCAT+Fin: Saddle-Fin

- Symp. on VLSI Tech. 2006, T5-1.

- RCAT: Recessed-Ch. Tr.

Fig. 1. Schematic diagram of S-Fin. The groove like RCAT and fin structure to the channel width direction are formed.

垂直トランジスタ(4F2化で必須)

- VCT: Vertical Channel Transistor

- ESSDERC 2011, p. 211.

- ◆VPT (Vertical Pillar Tr.)

Figure 2. (a) 4F<sup>2</sup> cell layout, (b) Schematic diagram of VPT 4F<sup>2</sup> cell array

STRJ WS2013, WG6 PIDS 若林

## NANDの状況と2015年活動計画

2013年版では、NANDFlashの3D化について、大きく積層数を 減らす方向の予測に変更し、2013-2014年に製品化が始まりつ つあり、24層、32層とほぼ想定通りの積層数となった。2015年版 に向けて、日本PIDS中心にサーベイ・技術予測を行いUpdate見

込み。

|           | NAND Flash            |          |       |        |        |        |         |

|-----------|-----------------------|----------|-------|--------|--------|--------|---------|

|           | Year of Production    | 2013     | 2016  | 2019   | 2022   | 2025   | 2028    |

| Was       | 2D poly 1/2 pitch     | 18nm     | 14nm  | 11nm   | 8nm    | 8nm    | 8nm     |

| ls        | 2D poly 1/2 pitch     | 18nm     | 14nm  | 12nm   | 12nm   | 12nm   | 12nm    |

| Was       | 3D cell x-y 1/2 pitch |          | 32nm  | 28nm   | 24nm   | 18nm   |         |

| ls        | 3D cell x-y 1/2 pitch | 64nm     | 45nm  | 30nm   | 27nm   | 25nm   | 22nm    |

| Was       | Cell type             | FG       | CT-3D | CT-3D  | CT-3D  | CT-3D  |         |

| ls        | Cell type             | FG/CT/3D | CT-3D | CT-3D  | CT-3D  | CT-3D  | CT-3D   |

| Unchanged | Product density       | 128G     | 512G  | 1T     | 2T     | 4T     | 8T      |

| Was       | Number of 3D layers   |          | 4-32  | 16-128 | 48-392 | 64-512 |         |

| ls        | Number of 3D layers   | 16-32    | 16-32 | 32-64  | 64-128 | 96-192 | 192-384 |

ISSCC2014, Three-Dimensional 128Gb MLC Vertical NAND Flash-Memory with 24-WL Stacked Layers and 50MB/s High-Speed Programming, Ki-Tae Park et al.

#### ReRAMの状況

#### 2013年版より、ReRAMをtable化。

2018年に4F2ReRAMで登場し、 2021年に3D-NAND Flashを 2021年に集積度で上回ると予測。 セレクターの選択、安定した低電流 スイッチング膜、巨大平面電極等が

(a) Metal pillar (b) Pillar Metal plane electrode **Plane** electrode electrode (WL) electrode Memory cell Metal Oxide Vertical MOSFET

開発の課題となる。

Source: IEDM 2012, Chen et al, "HfOx Based Vertical Resistive Random Access Memory for Cost-Effective 3D Cross-Point Architecture without Cell Selector",

| D. Resistive memory (ReRAM)                                     |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

|-----------------------------------------------------------------|------|------|------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Year of Production                                              | 2013 | 2014 | 2015 | 2016     | 2017     | 2018     | 2019     | 2020     | 2021     | 2022     | 2023     | 2024     | 2025     | 2026     | 2027     | 2028     |

| ReRAM technology node F (nm)                                    |      |      |      |          |          | 12       | 12       | 12       | 8        | 8        | 8        | 6        | 6        | 6        | 4        | 4        |

| ReRAM cell size area factor a in multiples<br>of F <sup>2</sup> |      |      |      |          |          | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 4        | 4        |

| ReRAM cell footprint (nm²)                                      |      |      |      |          |          | 576      | 576      | 576      | 256      | 256      | 256      | 144      | 144      | 144      | 64       | 64       |

| ReRAM array efficiency (%) (2D array)                           |      |      |      |          |          | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    | 68.5%    |

| ReRAM number of bits per cell (MLC)                             |      |      |      |          |          | 2        | 2        | 2        | 3        | 3        | 3        | 4        | 4        | 4        | 4        | 4        |

| ReRAM cell area per bit size (nm2) with                         |      |      |      |          |          |          | 200      | 222      |          |          | 0.5      |          |          |          | 40       | 40       |

| MLC                                                             |      |      |      |          |          | 288      | 288      | 288      | 85       | 85       | 85       | 36       | 36       | 36       | 16       | 16       |

| ReRAM storage density (SLC, 2D)                                 |      |      |      |          |          | 1.19E+11 | 1.19E+11 | 1.19E+11 | 2.68E+11 | 2.68E+11 | 2.68E+11 | 4.76E+11 | 4.76E+11 | 4.76E+11 | 1.07E+12 | 1.07E+12 |

| ReRAM storage density (MLC, 2D)                                 |      |      |      |          |          | 2.38E+11 | 2.38E+11 | 2.38E+11 | 8.03E+11 | 8.03E+11 | 8.03E+11 | 1.90E+12 | 1.90E+12 | 1.90E+12 | 4.205.42 | 4.28E+12 |

| bits/cm2                                                        |      |      |      |          |          | 2.38E+11 | 2.38E+11 | 2.38E+11 | 8.03E+11 | 8.03E+11 | 8.03E+11 | 1.90E+12 | 1.90E+12 | 1.90E+12 | 4.28E+12 | 4.28E+12 |

| Ref Max. 2D/3D NAND storage density                             |      |      |      | 0.405.11 | 0.405.11 | 6.47E+11 | 7.33E+11 | 1.14E+12 | 1.23E+12 | 1.73E+12 | 1.73E+12 | 2.73E+12 | 2.95E+12 | 3.21E+12 | 6.68E+12 | 7.30E+12 |

| (MLC, 3D max. layeres) bits/cm2                                 |      |      |      | 3.40E+11 | 3.40E+11 | 6.4/E+11 | 7.33E+11 | 1.14E+12 | 1.23E+12 | 1./35+12 | 1./3E+12 | 2./3E+12 | 2.53E+12 | 3.21E+12 | 0.00E+12 | 7.30E+12 |

| ReRAM 3D layers (using 4F2 GAA x-y                              |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| selector + high ON/OFF ratio in-layer                           |      |      |      |          |          | 4        | 4        | 4        | 8        | 8        | 8        | 16       | 16       | 16       | 32       | 32       |

| selecting device)                                               |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| ReRAM cell area per bit (nm2) with MLC                          |      |      |      |          |          | 72       | 72       | 72       | 10.67    | 10.67    | 10.67    | 2.25     | 2.25     | 2.25     | 0.5      | 0.5      |

| and 3D layers                                                   |      |      |      |          |          | 12       | 12       | 12       | 10.07    | 10.07    | 10.07    | 2.23     | 4.43     | 4.43     | V.J      | V.J      |

| ReRAM array efficiency (%) (using 4F2                           |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| GAA x-y selector + high ON/OFF ratio                            |      |      |      |          |          | 48.6%    | 48.6%    | 48.6%    | 46.0%    | 46.0%    | 46.0%    | 43.6%    | 43.6%    | 43.6%    | 41.5%    | 41.5%    |

| in-layer selecting device)                                      |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| ReRAM storage density (MLC, 3D max.                             |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| layeres, using 4F2 GAA x-y selector +                           |      |      |      |          |          | 6.75E+11 | 6.75E+11 | 6.75E+11 | 4.31E+12 | 4.31E+12 | 4.31E+12 | 1.94E+13 | 1.94E+13 | 1.94E+13 | 8.30E+13 | 8.30E+13 |

| high ON/OFF ratio in-layer selecting                            |      |      |      |          |          | 5.752-77 | 5.752    | 5.1.52   | 4.012112 | 4.012112 | 4.012112 | 11042110 | 1.542    | 1.542    | 0.002110 | 0.002-10 |

| device) bits/cm2                                                |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| ReRAM nonvolatile data retention (years)                        |      |      |      |          |          | >10      | >10      | >10      | >10      | >10      | >10      | >10      | >10      | >10      | >10      | >10      |

| 85C                                                             |      |      |      |          |          |          |          |          |          |          |          |          |          |          |          |          |

| ReRAM write endurance (read/write                               |      |      |      |          |          | 1.0E+09  |

## RF and analog/MS CMOS working group

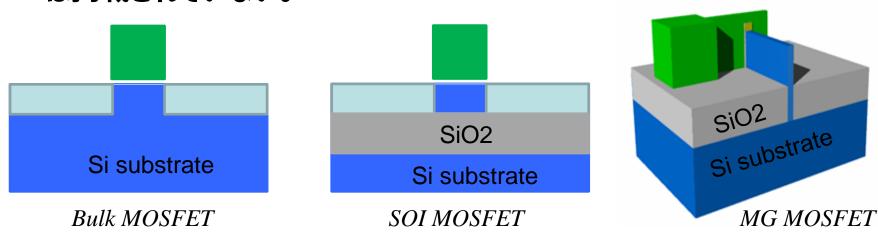

- 1. PIDS tableの値を用いて、バルク、SOIそしてMG MOSFETのRF及 びanalogのroadmap table\*を作成した。

- 2. RF及びanalog特性としては、fT, fmax, 1/f noise, minimum noise figure at 60GHz, low-frequency analog power gain, maximum stable gain at 60GHz, analog transistor voltage gain, Vth matchingがある。

- 3. 設計者からの要求が高いPMOSのfTについて、バルクMOSに関して追加した。

- 4. このtable\*は、PIDS tableのリリースが遅れたために、2013年版には掲載されていない。

\* *Modified Table(P.26)*

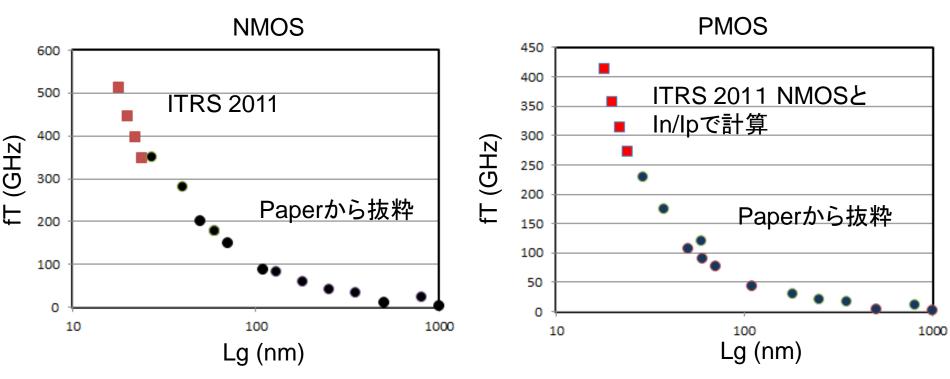

#### PMOSのfT見積もり

- 1. 2011 versionでのfTと既発表の比較から、bulk NMOSに関しては既発表値と良く合っていることを確認。

- 2. PIDSのroadmapのIon\_n/Ion\_pを用いて、bulk PMOSのfTを計算。この fTも既発表値と良く合っていることを確認。

- 3. 上記の結果から、2013 versionのbulk PMOSのfT見積もりには、PIDSの roadmapのIon\_n/Ion\_pを用いることとした。

Work in Progress - Do not publish

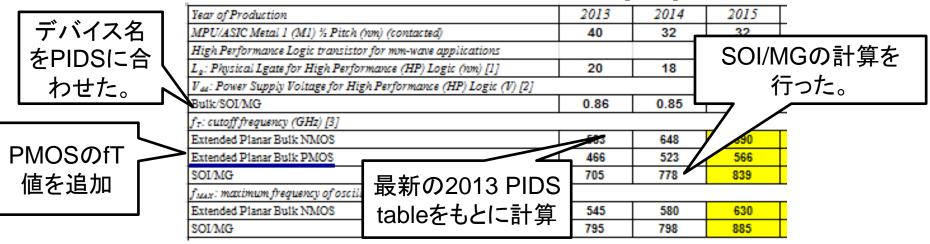

#### 2013 versionの現状

#### 2013 version of PIDS table (HP)

| Year of Production                                                             | 2013         | 2014 | 2015      |

|--------------------------------------------------------------------------------|--------------|------|-----------|

| Logic Industry "Node Range" Labeling (rvn) [based on 0.71x reduction per "Node | 114 (214 411 |      | 114414011 |

| Range" ("Node" = $\sim 2x Mx$ )                                                | "16/14"      |      | "11/10"   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (rnn) (contacted)                                | 40           | 32   | 32        |

| Lg: Physical Gate Length for HP Logic (rvn)                                    | 20           | 18   | 16.7      |

| L ch : Effective Channel Length (rnn) [3]                                      | 16.0         | 14.4 | 13.4      |

| V dd: Power Supply Voltage (V)                                                 |              |      |           |

| Bulk/SOI/MG                                                                    | 0.86         | 0.85 | 0.83      |

| EOT: Equivalent Oxide Thickness                                                |              |      |           |

| Bulk/SOI/MG (nm)                                                               | 0.80         | 0.77 | 0.73      |

| Dielectric constant (K) of gate dielectrics                                    | 12.5         | 13.0 | 13.5      |

| Physical gate oxide thickness (nm)                                             | 2.56         | 2.57 | 2.53      |

| Channel Doping (10 18 /cm 3) [4]                                               |              |      |           |

| Bulk                                                                           | 6.0          | 7.0  | 7.7       |

| SOI/MG                                                                         | 0.1          | 0.1  | 0.1       |

#### 2013 version of RF CMOS table (HP)

デバイス名 の違い

|         |                                    |                                  |      |      |      | _     |

|---------|------------------------------------|----------------------------------|------|------|------|-------|

| Ye      | ar of Production                   |                                  | 2013 | 2014 | 2015 |       |

| M       | PU/ASIC Metal 1 (M1) ½ Pitch (n    | m) (contacted)                   | 40   | 32   |      |       |

| Hi      | igh Performance Logic transistor j | for mm-wave applications         |      |      | MGO  | 見積もりが |

| $L_s$   | : Physical Lgate for High Perfori  | nance (HP) Logic (nm) [1]        | 20   | 18   |      |       |

| $V_{d}$ | id : Power Supply Voltage for High | n Performance (HP) Logic (V) [2] |      |      | されて  | ていない。 |

| Bυ      | ilk/UTB FD/MG                      |                                  | 0.85 | 0.82 |      |       |

| $f_T$   | : cutoff frequency (GHz) [3]       |                                  |      |      | 7 /  |       |

| Ex      | stended Planar Bulk                |                                  | 445  | 512  | /8   |       |

| U       | TB FD                              |                                  | 477  | 545  | 614  |       |

| M       | G                                  |                                  | 7    |      | 620  |       |

| $f_M$   | ux: maximum frequency of oscill    | 古い2011 PIDS                      |      |      |      |       |

| Ex      | stended Planar Bulk (junction)     | • •                              | 389  | 439  | 510  |       |

| U       | TB FD (body)                       | tableをもとに計算                      | 412  | 462  | 531  |       |

| M       | G (body)                           |                                  |      |      | 560  |       |

#### RF CMOS tableの修正

#### 2013 version of PIDS table (HP)

| Year of Production                                                                                     | 2013    | 2014 | 2015    |

|--------------------------------------------------------------------------------------------------------|---------|------|---------|

| Logic Industry "Node Range" Labeling (nm) [based on 0.71x reduction per "Node Range" ("Node" = ~2x Mx) | "16/14" |      | "11/10" |

| MPU/ASIC Metal 1 (M1) ½ Pitch (vm) (contacted)                                                         | 40      | 32   | 32      |

| L g: Physical Gate Length for HP Logic (rvm)                                                           | 20      | 18   | 16.7    |

| L ch : Effective Channel Length (rnm) [3]                                                              | 16.0    | 14.4 | 13.4    |

| V dd: Power Supply Voltage (V)                                                                         |         |      |         |

| Bulk/SOI/MG                                                                                            | 0.86    | 0.85 | 0.83    |

| EOT: Equivalent Oxide Thickness                                                                        |         |      |         |

| Bulk/SOI/MG (nm)                                                                                       | 0.80    | 0.77 | 0.73    |

| Dielectric constant (K) of gate dielectrics                                                            | 12.5    | 13.0 | 13.5    |

| Physical gate oxide thickness (nm)                                                                     | 2.56    | 2.57 | 2.53    |

| Channel Doping (10 12 /cm 3) [4]                                                                       |         |      |         |

| Bulk                                                                                                   | 6.0     | 7.0  | 7.7     |

| SOI/MG                                                                                                 | 0.1     | 0.1  | 0.1     |

#### Modified 2013 version of RF CMOS table (HP)

## まとめ

## STRJ WG6 (PIDS、RF&AMS)の活動を報告した。

- 最新版ITRS2013と、14nmプロセスの性能を比較し、 2015ITRS以降に向けて議論中のスケーリングパラメータ 表を示した。 メモリについて、今後のスケーリング見込み、各メモリの状況と 2015ITRSサーベイ計画を示した。

- RF&AMSの活動についてITRS2013の現状と改訂中のテーブルについて示した。