## 2015年度STRJワークショップ IoT時代のスマートテスト

WG2(テストWG) 安藏 顕一(東芝)

#### 目次

- 1. テストWG活動

- 2. WG2体制

- 3. WG2活動実績

- 4. 2015度活動

- 5. ATE-SWG活動

- 6. DFT-SWG活動

- 7. WG2活動まとめ

- 8. 未来への展望

| 略語   | 用語                                         | 説明                                           |

|------|--------------------------------------------|----------------------------------------------|

| ATE  | <b>Automatic Test Equipment</b>            | 大型テスタ他テスト装置・システム全般の呼称                        |

| DFT  | <b>Design for Test/Testability</b>         | テスト容易化を考慮した設計                                |

| ATPG | Automatic Test Pattern<br>Generation       | 自動テストパターン生成                                  |

| BIST | Built-In Self-Test                         | チップ内蔵の自己テスト回路、およびこれを用いるテスト手法                 |

| SoC  | System-on-a-Chip                           | 複数の機能ブロックなどを一つのLSIに搭載してシステムを実現する設計手法         |

| SiP  | System-in-a-Package                        | 複数のLSIを一つのパッケージに搭載してシステムを実現する設計・実装手法         |

| TSV  | Through-Silicon Via                        | シリコン製半導体チップの内部を垂直に貫通する電極。主に3D ICの積層チップ間接続に使用 |

| MEMS | Micro Electro Mechanical Systems           | 加速度センサ等の微小な電気機械システム                          |

| IP   | Intellectual Property                      | 一般には知的財産の意。LSI設計では、ある機能を実現する回路部品の情報を意味する     |

| OSAT | Outsourced Semiconductor Assembly and Test | 半導体組み立て検査受託会社                                |

| 用語                        | 説明                                                    |

|---------------------------|-------------------------------------------------------|

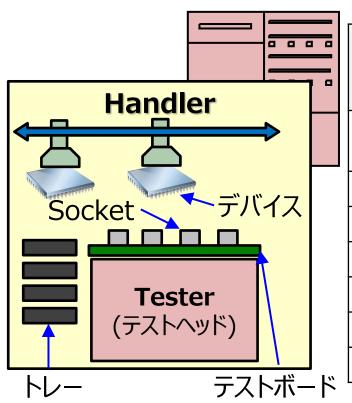

| ハンドラ                      | テスト時のチップの搬送、テストソケットへの装着、温度制御等を一貫して行う装置                |

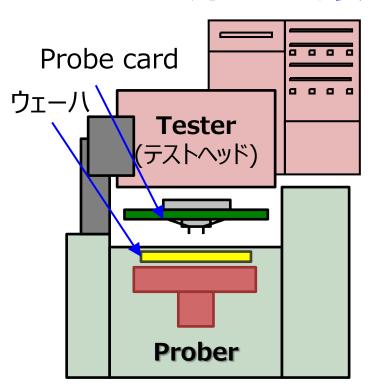

| プローブカード(Probe Card)       | ウェーハ上のLSIを電気測定するための冶具。髪の毛以下の太さの針(プローブ)の集合体            |

| バーンイン                     | チップの初期劣化不良を検出するため熱・電圧ストレス等を長時間かける工程                   |

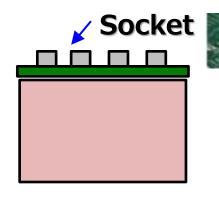

| テストソケット(ソケット)             | テスト時にLSIパッケージを挿入固定するための治具                             |

| 治工具                       | ソケットやプローブカード、インタフェースボード等、テスト時に必要な治具                   |

| スキャンテスト                   | ランダムロジックを対象とするDFTの代表的手法                               |

| 同測テスト                     | 複数のチップを同時にテストする手法、多数個同時測定テスト。テストスループット向上によるコスト低減が可能   |

| コンカレントテスト                 | チップ内の複数のコアおよび回路を並列にテストする手法                            |

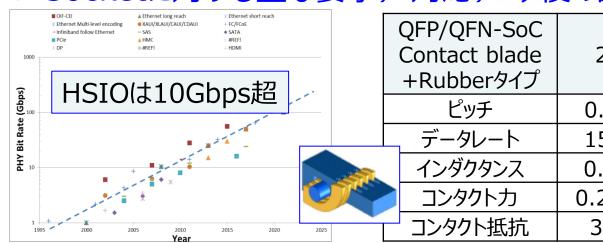

| 高速IO (HSIO/High-Speed IO) | LSIが外部と高速にデータ送受信を行うための回路やインタフェース。USB,DDR,SATA等標準規格がある |

| 3D IC                     | チップ同士を三次元的に積層し、TSV等で互いに接続した構造を持つIC                    |

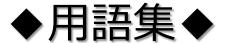

### 1. テストWG活動: 位置づけ

- テスト= 製造工程において、良品/不良品を選別するための手段

- LSIテスタを用いることが一般的

- <u> LSIとLSIテスタの接続のために、様々な検査冶具を用いる</u>

- 、プローブカード、プローバ、ハンドラー、ソケッ<u>ト、</u>検査ボード・・・

- LSIにはテストを容易にするための設計 (DFT) を施している

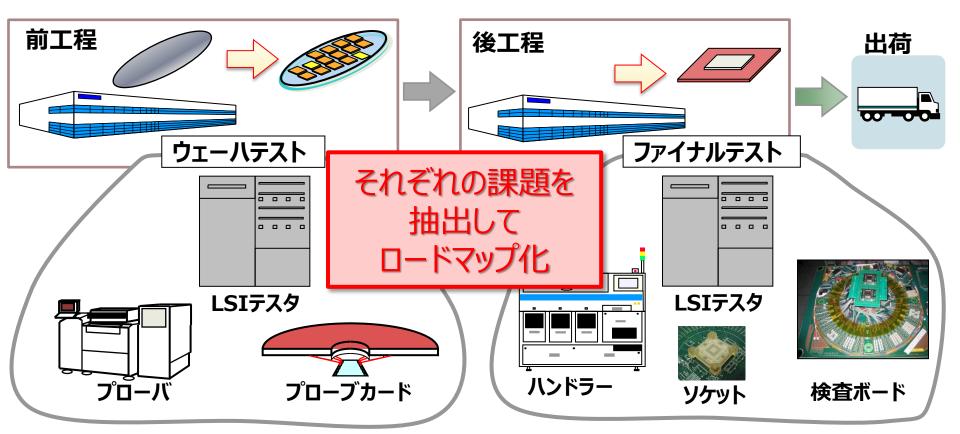

### 1. テストWG活動: ITRS2.0

2005~2010年度: SiPのテスト技術について調査、課題検討

・さまざまな種類のダイを 1 パッケージで実装した場合のテストと DFTの技術的課題を抽出

2011~2012年度: 3D-ICのテスト技術の調査、課題検討

・TSV(Through Silicon VIA)ベースの積層IC

"Heterogeneous Integration" Focus Topicに属する活動

2014年度: ITRS2.0公表

2015年度: 異種デバイス(MEMS)のDFT/テスト手法を検討

2015年度: IoTデバイスに対するセキュリティ関連テストについて

調查•検討

"System Integration" Focus Topicに属する活動

今後Mixed-signal/Analog/RF/Photonics/MEMSに対する信頼性確保が重要になる

## 2. WG2体制

|                               | ATE-SWG                                                                                          | DFT-SWG                                                                            |

|-------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 委員                            | 田村(ルネサス セミコンダクタ パッケージ&テスト ソリューションズ)サブリーダ<br>平山(ソシオネクスト)<br>武田(東芝)                                | 安藏(東芝) WGリーダ<br>濱田(ソシオネクスト)サブリーダ<br>青木(ソニーLSIデザイン)<br>佐々木(ルネサスシステムデザイン)<br>佐藤(ローム) |

| 特別委員<br>(SEAJ技術部会<br>検査専門委員会) | 北川 (アドバンテスト) 市川 (アドバンテスト) 清水 (東京エレクトロン) 鈴木 (浜松ホトニクス) 薗田 (シバソク) 清藤 (日本マイクロニクス)                    | テスト装置メーカー<br>からの知見を得る<br>目的で参加                                                     |

| 特別委員(大学その他)                   | 多田 (徳島文理大学)<br>佐藤 (TRL)<br>堀部 (エスティケイテクノロジー)<br>渡辺 (サイプレス・イノベイツ)<br>鈴木 (山一電機)<br>島田 (エンプラス半導体機器) | 佐藤(九州工業大学)<br>畠山(群馬大学)<br>清水(サイプレス・イノベイツ)                                          |

全23名

### 3. WG2の活動実績

| 区分   | 活動内容      |                                                                                                  |

|------|-----------|--------------------------------------------------------------------------------------------------|

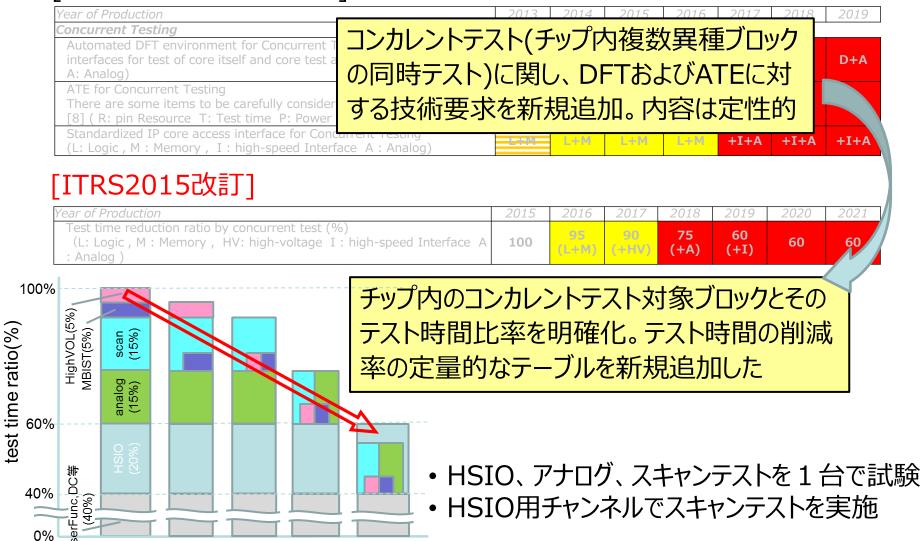

| 国際活動 | ITRS 2015 | ・ハンドラ、プローバ、ソケットの各テーブルを改訂 ・ロジックテーブル改訂に協力 ・コンカレントテストに関しDFTテーブル及び本文の修正・追記 ・Low powerセルテストに関し本文へ新規追加 |

|      | 国際会議      | ・米Stanford(7月)、Atlanta(2月)の国際会議に参加。上<br>記の改訂に関して関係者とレビューを実施                                      |

| 日内注制 | ATE-SWG   | ・今後のテスト技術の方向性とその価値に関する検討<br>・テストコストに関する検討                                                        |

| 国内活動 | DFT-SWG   | ・MEMSの試験に関する調査・検討 ・セキュリティ関連デバイスのテストに関する調査・検討                                                     |

| テーブル  | 担当        | 改訂内容                                           |

|-------|-----------|------------------------------------------------|

| プローバ  | STRJ      | - 450mmウエハ量産化時期(2020年)に対応<br>- フレームプローバテーブルの追加 |

| ハンドラ  | STRJ      | - 各項目の色や数値を全般的に変更                              |

| ソケット  | STRJ      | - DRAMおよび SoC用ソケットの峡ピッチ化、高速化に対応                |

| Logic | ITRS/STRJ | - モチーフデザイン変更(*)に対応(実施内容・時期の見直し)                |

| DFT   | STRJ      | - コンカレントテストテーブルを定量化                            |

(\*) SoCモデルがフィーチャーフォンからスマートフォンモチーフへ

STRJが上記テーブルを担当し、改訂作業を主導的に行った

### 5. ATE-SWG活動: ITRS2015 テーブル改訂

#### ▶ Proberに対する主な要求/対応/今後の課題

|                     | 200mm         | 300mm        | 450mm        |

|---------------------|---------------|--------------|--------------|

| 対応年                 | 2015-2019     | 2015-2019    | 2020~        |

| ウェーハサイズ             | 6, 8inch      | 8, 12        | 12, 18       |

| テストヘッド<br>重量(max)   | 1000kg        | 1000         | 1500         |

| プローブカード<br>サイズ(max) | 580mm         | 580          | 725          |

| XY精度                | 2.0um         | 2.0          | 2.0          |

| Z精度                 | 5.0um         | 5.0          | 5.0          |

| チャック平坦度             | 7.5um         | 5.0          | 5.0          |

| チャック耐荷重             | 60kg          | 450          | 500          |

| 温度範囲                | -55∼<br>+300℃ | -55~<br>+250 | -55~<br>+250 |

・要求:広範囲な位置決め精度、多個取り数増加による平坦度/耐荷重、車載要求 による温度範囲、450mmウェーハ

・対応:アライメント精度向上、チャックのステージ強化、温度制御改善

・課題:450mmウェーハで難易度up、プロービングシステム全体での最適化、プローブ カード治工具の大口径化、重量増加に伴う装置運用の安全性確保

### 5. ATE-SWG活動: ITRS2015 テーブル改訂

#### ➤ Handlerに対する主な要求/対応/今後の課題

| 水平搬送<br>(Consumer SoC/<br>Automotive) | 2015          | 2017         | 2019         |

|---------------------------------------|---------------|--------------|--------------|

| テスト温度                                 | -55~<br>+175℃ | −55~<br>+190 | −55~<br>+190 |

| Index時間                               | 0.3秒          | 0.3          | 0.25         |

| 処理能力                                  | 2∼30k/H       | 2~30k        | 2~30k        |

| 消費電力散逸                                | 30W/DUT       | 40           | 40           |

| パッケージサイズ                              | 2.5x2.5mm     | 2.5x2.5      | 2x2          |

| パッケージ厚さ                               | 0.4-1.8mm     | 0.2-1.8      | 0.2-1.8      |

| ピンピッチ                                 | 0.35mm        | 0.35         | 0.3          |

・要求:短Index時間、薄いパッケージのハンドリング、車載向け温度対応

・対応:ハンドリング方法やハンドラ内温度制御の最適化

・課題:温度制御のレスポンスや精度、アプリケーション毎に対応した最適化

### 5. ATE-SWG活動: ITRS2015 テーブル改訂

### ➤Socketに対する主な要求/対応/今後の課題

| QFP/QFN-SoC<br>Contact blade<br>+Rubberタイプ |         | 2015                | 2017    | 2019    |

|--------------------------------------------|---------|---------------------|---------|---------|

|                                            | ピッチ     | 0.3mm               | 0.3     | 0.3     |

|                                            | データレート  | 15GT/s              | 20      | 40      |

|                                            | インダクタンス | 0.15nH              | 0.15    | 0.1以下   |

|                                            | コンタクトカ  | 0.2-0.3N            | 0.2-0.3 | 0.2-0.3 |

|                                            | コンタクト抵抗 | $30 \text{m}\Omega$ | 30      | 30      |

|                                            |         |                     |         |         |

| BGA-SoC<br>Rubberタイプ |         | 2015                  | 2017  | 2019  |

|----------------------|---------|-----------------------|-------|-------|

|                      | ピッチ     | 0.3mm                 | 0.25  | 0.25  |

|                      | データレート  | 56GT/s                | 56    | 56    |

|                      | インダクタンス | 0.15nH                | 0.1以下 | 0.1以下 |

|                      | コンタクト力  | 0.15N                 | 0.1   | 0.1   |

|                      | コンタクト抵抗 | $50 \mathrm{m}\Omega$ | 50    | 50    |

・要求:高速化、コンタクタの狭ピッチ化、低インダクタンス、低コンタクトカ

・対応:コンタクタの微細化、低インダクタンス化(導体長を短くする)

・課題:高速・高周波対応、コンタクタの耐久性

### 5. ATE-SWG活動:独自活動

#### > テスト技術の方向性

|                | 1998年(STRJ発足)              | 現在                           | 今後                                           |

|----------------|----------------------------|------------------------------|----------------------------------------------|

| 主力製品           | メモリ                        | SoC                          | SiP, 2.5D/3D IC, IoT                         |

| 製品のキー技術        | 製造技術(前工程)<br>装置技術(前工程)     | 製品提案<br>設計技術                 | 実装技術                                         |

| 国内各社の事業<br>形態  | IDM                        | ファブレス <i>/</i><br>ファブライト化の進行 | ファブレス <i>/</i><br>ファブライト                     |

| テストの主目的        | 製造へのフィードバック<br>GO/NOGO判定   | 設計へのフィードバック<br>歩留まり向上        | 信頼性へのフィードバック<br>歩留まり向上<br>トレーサビリティ           |

| 注力されるテスト<br>技術 | 自社テスト工程のコスト<br>削減<br>同測テスト | テスト時間の短縮<br>テスト容易化           | テストの標準化<br>アナログテスト容易化<br>テストデータ解析<br>付加価値の増大 |

ファブレス化によるスマートテスト技術への移行

### 5. ATE-SWG活動:独自活動

- ▶ テスト工程が生み出す付加価値について

- セキュリティ、トレーサビリティの向上:セキュリティキーやIDの書込み

- 歩留まりおよび精度の向上:トリミング技術

- 不良メモリセルの救済:リダンダンシ技術

- 品質向上、歩留まり向上、テスト最適化: ビッグデータの活用

- ◆ビッグデータ活用に必要なこと

- 大容量ネットワーク化

- テストデータの即時性向上

- データのセキュリティ確保

- データ解析、データ応用技術者の育成

- データ解析結果の妥当性検証

テスト工程は必要悪ではなく、ビッグデータ活用で さらに価値を生む工程に!

## 6. DFT-SWG活動: ITRS2015 テーブル改訂

#### [ITRS2013 DFTテーブル]

2016

2017

2018

2019

2015

### 6. DFT-SWG活動:独自活動(背景)

- > セキュリティ関連デバイスのテスト

- IoTデバイスの普及に伴いセキュリティ対策が重要になってきている

- 一般にDFTはチップ内を観測する技術であり、セキュリティホールになり得る

#### セキュリティデバイスのテストに関する調査を実施

- ➤ IoTにおけるセキュリティに対する脅威

- セキュリティコードの読み出し手段

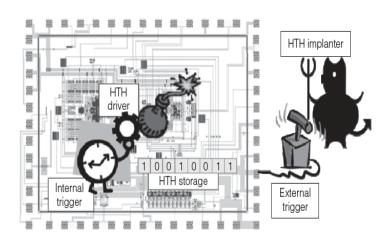

- Hardware Trojan

- 設計者による挿入

- 実装技術者による挿入

- 製造者による挿入

- 偽造IC(\*)

- サイドチャネル攻撃

- スキャンチェインによる内部情報の読み出し

(\*) 一般には正規品と同等機能をもつ安価な粗悪IC、ここでは悪意ある機能が追加されたICを含む

## 6. DFT-SWG活動:独自活動(攻撃への対策)

- ▶ セキュリティコード読出し等への対策

- PUF (Physical Unclonable Function) による暗号鍵の保護等

- LSIの個体毎の物理的差異を利用して個体の識別情報を作る

- ➤ Hardware Trojanへの対策

- Hardware Trojanとは?

- 設計で仕込まれた悪意のある回路

- 何かをトリガに故障誘発/情報リーク

- サードパーティーIPに仕込まれる例も

- サードパーティIPに仕込まれた場合の対策(ITC 2015より)

- 冗長ベース手法(異なるベンダのIPを併用)

- ナレッジベース手法 (既存の信頼性の高い回路のみ利用)

- ●回路/信号ベース手法 (回路や信号を分析)

- ソフトウエアベース手法(ソフトウエアの特性分析手法を適用)

## 6. DFT-SWG活動:独自活動(攻撃への対策)

STRI

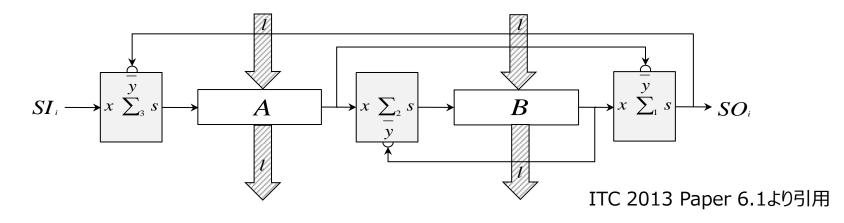

- > スキャンチェインによる読み出し

- ■テストモードで内部の値を外部から読み出す

- > 対策例

- ■テストモード切り替えに鍵を掛ける

- ●状態遷移やeFUSEを利用

- ■テストモードを無効にする

- ●スクライブ領域配線やモード信号のボンディング時固定

- Differential Scan等によりデータを秘匿化する

ITRS 2015年改訂に参加。最後のITRSの改訂に、テスト・DFTの面で貢献した

#### **ATE-SWG**

- ITRS table(ハンドラ、プローバ、ソケット)および本文改訂

- 今後のテスト技術の方向性とその価値に関する検討

#### **DFT-SWG**

- ITRS table改訂(コンカレントテスト、Low powerセルテスト)および本文追記

- MEMSテスト及びセキュリティ関連テストの調査・検討

### 8. 未来への展望

スマートテスト

LSI設計

#### スマートテスト:

ICT基盤上でのテストビッグデータの有効活用とサプライチェーン全体の最適化を行うことで、 半導体の価値を最大化するコンセプト

信頼性 トレーサビリティ セキュリティ 設計インテント 歩留り

# 以上