### 第3章 WG2 テスト

### 3-1 はじめに

テストWGの目的は、DFT(Design for Testability)、ATE(Automatic Test Equipment)に関する将来を見通した課題を抽出しあるべき方向へ情報発信することにある。このため、STRJ 会員会社、コンソーシアム・大学等のメンバの他、SEAJ(Semiconductor Equipment Association of Japan)技術部会の半導体装置ロードマップ専門委員会の検査WGから関係メンバの参加を得て、DFT技術、ATE および周辺装置技術について幅広い観点から調査活動を続けてきた。特に、

- (1) テスト設計関連 EDA ベンダに技術開発項目とその指針を示し、将来、ツールとして反映されることで 半導体開発の設計技術向上、生産性向上を目指す。

- (2) ATE 関連ベンダに技術開発項目とその指針を示し、将来、装置等に反映されることで半導体開発の テスト技術向上、生産性向上を目指す。

- (3) 大学等の研究者に企業の課題を明示し、あるべき方向に研究を加速する。 等を念頭に置いている。

図表 3-1 は、2008 年度の活動概況を示す。「More Than Moore」に象徴される LSI の多様化に対応するため、SoC、SiP のテスト、あるいは高速 I/F に代表されるチップ構成部品の多様化等のテーマに取組んできた。またテスト品質とのバランスを取りながらテストコスト低減を図る新手法についても検討を行なった。ITRS については、2008 年度に多数のテーブルを見直した他、2009 年度の改訂へ向け、海外の ITWG メンバと議論を行い進めている。詳細は後述の各節に示す。

|                 |                  |                                                                 |   | ITRS |             |

|-----------------|------------------|-----------------------------------------------------------------|---|------|-------------|

| 区分              |                  | 活 動 テーマ<br>                                                     |   | 2008 | 2009<br>(予) |

| I SoC I         |                  | <ul><li>構造化テスト(スキャン, BIST)の駆使と課題</li><li>・低電力化への取り組み</li></ul>  | د |      | ν           |

| 国内活動            | 高速//F<br>【SWG合同】 | ・ATE/BOST/BISTのバランスによるコスト低減課題                                   | ٧ |      | V           |

| 活<br>  動<br>    | SiP              | チップ状態での品質保証技術とDFTの課題                                            | V |      | V           |

|                 | コスト              | <ul><li>アダプティブテスト(テスト仕様・フローの適合化)</li><li>によるコスト低減の可能性</li></ul> | د |      | ν           |

| SoC<br>【設計WG合同】 |                  | ・改訂(クロック・電源設計複雑化への対応, 他)                                        |   |      | ν           |

| 国際活動            | DFT<br>【設計WG合同】  | ・【設計章】と【テスト章】の記載の整合化                                            |   |      | ν           |

| 動               | ATE              | ・小改訂(RF, ミックスドシグナル, 同測テスト)                                      | V | ۷    |             |

|                 | 周辺               | ・大改訂(プローバ, ハンドラ, その他全テーブル)                                      | V | ·    | V           |

図表 3-1 2008 年度の活動状況

#### 3-2 国際活動

本年度は、年3回のITWG参加以外に、月1回ペースの電話会議を開催し、ITRS2008テーブルの改訂およびITRS2009の更新内容を議論した。STRJが中心になって提案したITRSの要求テーブル項目(テストデータ圧縮率等)は、これまで多くの学会の国際会議論文や EDA ベンダのパンフレット等に引用されていることが確認され、研究者やEDA ベンダ等の研究開発の指針となって技術進歩を促していることが伺える。またATEおよび周辺装置については、多くのテーブルオーナーとなりITWG メンバと議論しながら見直しを進めている。

### 3-2-1 ITRS/ORTC への貢献 (DFT 関連)

ITRS2008 の「テスト章(Test & Test Equipment)」における SoC テーブル(Table TST3a/b System on Chip Test Requirements)の内容見直しを実施した結果、改訂項目は無いと判断し ITWG の合意を得た。ITRS2009 については、以下の 2 つの項目を中心に見直しを推進中である。

### ● DFT 技術記載の枠組み見直しの取組み

ITRS2008 までの「テスト章」における記載は、SoC のテストに関する DFT 技術が SoC テーブルに書かれていたものの、各種 IP(メモリやロジックなど)のテストに関する DFT 技術の記載はなかった。そこで、各種 IP のテストに関する DFT 技術を対応する IP のテーブルに記載すべき、と考え提案した。また DFT 技術は、「テスト章」だけではなく「設計章(Design)」にも関連する記載が含まれており、重複や内容の不整合について指摘した。2 つの章に跨る記載の統一を図るため、STRJ から以下の方針の提言を行い ITWG と議論を進めている。

- 「設計章」: テストに関係する設計トレンドおよび意図の提示、および DFT 技術への要求と具体例の提示。

- ・「テスト章」: ポテンシャルソリューションを、DFT 技術と ATE 技術の両面から提示。

### ● SoC コンシューマコアモデルの最新設計手法に対応する見直し

SoC テーブル検討に用いているコンシューマコアモデルを、低電力化設計等の最新の設計手法に対応させ、より実践的なものに見直すため、STRJ の設計 WG と 3 回のクロスカット会議を実施し検討した。従来のSoC テーブルは、設計 WG(WGI)より「システムドライバ章」へ掲載されたコンシューマコアモデル(SoC Consumer Portable Driver)をベースに DFT 関連の要求事項をまとめているが、高速 I/F や多数個のコアの搭載、電源設計やクロック設計の高度化など、最新の設計手法に対応する考慮が不足していた。そこで、新たに追加したい項目をテスト WG より提示し、設計 WG に検討いただいた。また、従来の SoC テーブルの数値パラメータに対する考え方の確認なども行った。外部電源数やクロックドメイン数などは、設計の多様化のために、標準的な数字の提示は困難との結論だったが、低電力化設計に重要なパラメータであることを WG 間の共通認識とできた。コンシューマコアモデルのパラメータ項目は、「既存パラメータ」と「新規追加パラメータ」に分かれる。主なパラメータは、FF数(既存)、コアの種類数、クロックドメイン数、電源ドメイン数、IO 数などで、内容を図表 3-2 にまとめる。クロックドメイン数、電源ドメイン数などの影響については、3-3-3 節「複雑化する SoC へ対応する要求テーブルの変更検討」に述べる。

| パラメータ                                     | 分類 | 現状の算出方法                                                                                                               | WG1 検討 | 補足                                      |

|-------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|

| 回路規模(FF 数)                                |    | 計算式: (論理部トランジスタ数) × 50%<br>÷ 40 トランジスタ/FF<br>前提: 論理部を 50%が FF と推定。スキャン FF 内<br>のトランジスタは 40 個(非スキャン FF 内は 26 個)<br>で算出 | 現状通り   | 変更根拠は現状なし。                              |

| コア種類数                                     | 既存 | 全コア数の 1/8 の種類を想定                                                                                                      | 現状通り   | 同上                                      |

| クロックドメイン数<br>(内部)                         | 新規 | クロック1本                                                                                                                |        | SoC の多様性のため、<br>標準値推定が困難。               |

| 外部電源数<br>(同一電圧でもデジタ<br>ル・アナログ別系統な<br>ら2本) | 新規 | 電源種別と電圧値でカウント ・デジタルとアナログ電源で分ける ・IO 部の電源の数 ・内部の電源の数、など                                                                 | 検討中    |                                         |

| IO数                                       | 新規 | 現状該当なし<br>・エリア PAD や TSV の扱いが今後の課題                                                                                    | 困難     | チップサイズ、PAD ピッ<br>チ、電源 PAD 数から<br>算出を検討。 |

| メモリ数                                      | 既存 | WG2 にて ITRS2005 にて検討した方法(内容省略)                                                                                        | 現状通り   | 変更根拠は現状なし。                              |

| 高速 IO の周波数、<br>転送レート、ビット幅                 | 新規 | 現状該当なし                                                                                                                | 困難     | 現状の WG1 活動内容<br>に含まれず                   |

図表 3-2 コンシューマモデルのパラメータ検討結果

### 3-2-2 ITRS/ORTC への貢献(ATE 関連)

ITRS2008 においては、同測個数、ミックスドシグナル、RFのテーブルについて、数値及び条件の変更を 行った。ITRS2009 については、全テーブルの見直しを行うことになっているが、そのうち Table TST10 から TST15 までを日本側がテーブルオーナーとなり見直している。以下に各テーブルの見直しの要点を示す。

### • Table TST6 Memory Test Requirements

混載メモリのサイズについて従来の ITRS のテーブルでは小さ過ぎるため、見直しを提案中。

### • Table TST7 Mixed-signal Test Requirements

ミックスシグナルテストの対象となるデバイス分野が広く要求値の妥当性が分かりづらかったため、低周波/ 高周波の項目毎に対象とするデバイスアプリケーションを明確化し、注記にて示すことを提案中。

### • Table TST8 RF Test Requirements

最新の無線規格動向をもとに、ITRS メンバと協議して、Modulation RF BW と Carrier Frequency の要求値を 見直すことを提案中。

### • Table TST10 Test Handler and Prober Difficult Challenges

小さくて薄いパッケージ、あるいは薄いウェーハ/チップのハンドリング、および「Difficult Challenges」として挙げられている ISM (Image Sensor Module)、MEMS (Micro Electro Mechanical Systems)などへの対応などの新たな課題を整理中。

#### • Table TST11 Prober Requirements

プローバのロードマップは、ITRS 発足時に掲載されて以来、大きな改訂は行われなかった。しかし近年のデバイスやプローブカードの進化に伴い、例えばウェーハバーンイン時に見られる従来の単純なテスト枠を超えた使われ方も発生し、プローバに求められる要求も大きく変化しつつある。FWC (Full Wafer Contact)、SiP、薄ウェーハ、WLCSP (Wafer Level Chip Scale Package)、多ピン LSI での多数個同時測定テスト、あるいはパッドの縮小化への対応等、多様化/細分化する要求に呼応するべく、実際の装置の仕様や今後の要求に沿った形に改訂中。

#### • Table TST12 Handler Requirements

従来、「High Power」と呼んでいたカテゴリでは、発熱が 50W を超えるものと 10~50W の範囲では、多数 個同時測定数、テスト温度範囲、あるいはピン数が大きく異なるため 2 つに分割する。 具体的には以下を見直し中。

「High Power: 50W/DUT」: 「pin 数」、「Parallel Testing 数」、「Max Socket Load 値」などを改訂。

「Mid To High Power: 10~50W/DUT」: 「Index-Time 値」の 0.3s 実現が製品未対応。

「Medium Power: 0.5~10W/DUT」: SoC をターゲットとして、「Parallel Testing 数」などを改訂。

「Low Power: <0.5W/DUT」: メモリをターゲットとし、「Pin/land Pitch」の 0.2mm 以下の実現性を未確認に見直し。

#### • Table TST13 Probing Difficult Challenges

LCDドライバにおけるパッドの狭ピッチ化や2重列化への対応、ダイシング後チップの多数個同測可能化など新たな課題を整理。

#### • Table TST14 Wafer Probe Technology Requirements

各製品群のパッドピッチ、ピン当たりの最大電流値および最大ピン数を、現在の量産ベースに合わせ下方修正。スクラブマークについては、これまでパッドの面積比率で表記していたが、定義の不明確さや年度毎の変更する必要性が少ない事から、パッドサイズに対するプローブ先端径比率の表記に変更。これによりプロービング時に必要なアライメント精度が、年度毎に明確となり、プローバの要求テーブル(Table TST11)と整合した。また新たに、最も狭パッドピッチ化が進んでいるLCDドライバに対する要求値を加えることを提案中。

### •Table TST15 Test Socket Technology Requirements

ITRS2007で日本側より提案し新規掲載されたが、ピッチ数、インダクタンス値および周波数のトレンドの関係をわかり易くする目的で、フォーマット含めた見直しを実施中。

### 3-2-3 テスト TWG サブワーキング活動

SiPのテストについて日本側の検討結果を3回のITWG会議で説明し議論した。2008年4月の欧州会議(ドイツ)では、前年度の日本側の検討結果を用いて議論を行ったが、KGD (Known Good-Die)の必要性は理解されているものの、故障の検出工程や発生度合いにより、具体的なテスト方法の検討が必要とされた。また、組立て後のテストで品質保証が完全にはできない問題に対し、表現方法の変更も含めて今後の課題とした。2008年7月の米国会議では、課題となっていた7項目についてその後の日本側の検討結果を示し議論した。主な議論は、KGDを実現するのに必要なテスト手法(構造化テストや低速のファンクションテストにより必要な DPM (Defects per Million)レベルを保証できるか?)、テスト時に観測可能なピンが制約されるSiP組立て後のテストコスト低減戦略、BIST (Built-In Self-Test)やとテストエンジン(3-4節)の可能性、およびチップの大量発熱の影響緩和策などであった。これらはITWGにSiPサブワーキングを設けて継続議論することにした。2008年12月のアジア会議(韓国)では、Assembly & Packaging WGで検討しているSiPモデル(3-4-1節)を例に、SiPテストを4工程に分けて、各テスト課題やポテンシャルソリューションについて議論した。この会議はメモリベンダーからの参加者が多く、SiPに用いられる積層メモリについて活発な議論が行われた。その結果、8段に積層したメモリブロックのままでのテスト(コンタクト)は難しく、基板に取り付けてからのテストが一般的との提案があり、それまでの検討結果に反映させることができた。

その他、ATE 関連では、アダプティブテスト(3-4-2 節)、テストコストなどのサブワーキングが ITWG に発足し、日本からも参加し議論していく予定である。

### 3-3 国内活動 (DFT 技術)

#### 3-3-1 概要

下記の2項目について注力して調査検討活動を行った。以下、これらについて報告する。

- (1)構造化テスト(スキャンテスト、BIST)の駆使と課題に対する検討

- (2)複雑化する SoC へ対応する要求テーブルの変更検討(設計 WG との共同検討を含む)

#### 3-3-2 構造化テストの駆使と課題に対する検討

昨今のますます大規模化および高機能化する SoC のテストは、テスト開発期間、テスト時間 (コスト)および テスト品質のいずれの面においても、構造化テストなしでは全く成り立たなくなっている。しかし一方で、通常 動作を模したファンクションテスト(機能テスト)は、多くの SoC で採用されており、一向に消滅の気配がない。 「構造化テスト」と「実動作」のミスマッチなどという声も聞かれるが、いったい、「構造化テストの駆使でどこまで テストできるか?」という観点で、現在の構造化テストでは不十分な項目の洗い出しを行った。なお、ここで構造 化テストとは、スキャンテスト(圧縮ディタミニスティックパタンテスト、以下、圧縮スキャンテストと呼ぶ-2007 年度 STRJ 報告書第4章参照、およびロジック BIST を含む)、メモリ BIST、バウンダリスキャンテスト(JTAGとも呼ぶ)、あるいは提供されるコアごとの BIST を含む、と定めた。SoCを、IO セル、ロジック、メモリ、コア、アナログ、高速 I/F などの各部品に分け、各々に対して実施される構造化テストに対する課題について調査検討を実施した。その結果、以下の 4 点の大きな問題点を抽出した(図表 3-3)。

- ① SoC の低消費電力化

- ・テスト時の消費電力やノイズの影響による歩留まりロス(オーバーキル)等の発生。

- ・低消費電力 LSI で使われる低消費電力素子のテスト手法が未確立。

- ② メモリーロジック間のテスト

- ・メモリ周りの実動作パスに対する遅延テスト手法が未確立。

- ③ クロックドメイン間のテスト

- ・組合せ数が多く、テストパタン数、あるいはテスト時間が膨大化。

- ④ アナログテスト・高速 I/F テスト

- ・DFT を用いたテスト手法と ATE や BOST(Built-Out Self-Test)を用いた他のテスト手法との使い分けが 必要

ここで、①は、SoC の大規模化が進む一方で低消費電力化に対する要求も顕著になってきていることから、 昨今着目されてきた課題であり、②は今回の調査検討を通じて、事象を整理して気づいた課題である。これら の課題を解決することで、構造化テストの実質的なテスト検出率は大幅に向上すると考えられる。

「構造化テスト(スキャン、BIST)を駆使したら どこまでテストできるか」について調査・検討 大きく4つの課題を抽出

SoC テストのイメージ図

### ①SoCの低消費電力化への対応

### 最近着目されてきた課題

- ・テスト時の消費電力/ノイズ

- ・低消費電力LSIで使われる素子のテスト

②メモリーロジック間のテスト

#### 整理してみて気づきのあった課題

実動作パスに対する遅延テスト

### ③クロックドメイン間のテスト

・組み合わせが多く、パターン(テスト時間) が膨大になる

### ④アナログテスト・高速IOテスト

-DFTと他テスト手法(ATE/BOST)との使い 分けが必要

図表 3-3 SoC テストの課題

### 3-3-2-1 SoC の低消費電力化への対応

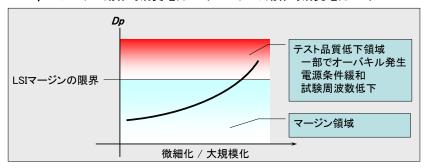

#### (1) テスト時の消費電力

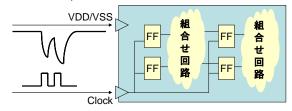

スキャンテスト設計(各種の圧縮スキャンテスト手法を含む)を適用したSoCにおいて、実際のシステム動作時 の消費電力に比べ、テスト動作時の消費電力はかなり大きい事はよく知られている。論理の大規模化や実速 度(At-speed)テスト等によるテスト周波数の増加など、テスト動作時の消費電力増加要因はますます増えている。 一方で、システム動作時の電力は、低消費電力設計により抑制されており、テスト動作時の消費電力とシステ ム動作時の消費電力の違いが大きくなっている。この差分がマージン値を越えると、テスト品質の低下を招くこ とになる。テスト動作時に発生するノイズについても同様であり、テスト環境への悪影響が懸念される(図表  $3-4)_{0}$

テスト動作時の消費電力の増加要因としてスキャンシフト動作が挙げられる。スキャンシフトは、シフトレジス タ構成された FF (Flip-Flop)群をシフト動作させることで、所望の FF に信号値を設定するか、あるいは所望の FFに保持した信号値を読み出す動作である。この過程において、各 FFには"0"及び"1"の値が不規則に設定 され、その信号値が FF の出力端子に接続されている組合せ回路に伝播することで、システム動作時より高い 回路動作率を発生する。また、遅延テストではシステム動作時とは異なった、比較的低速なシフト動作と、高速 なシステム動作が交互に繰返される。これにより電源系にノイズが発生する(図表 3-5)。これらの問題に対する 現状の対策を図表 3-6 に示す。いずれも現状では不充分であり、今後、コストを増加させない対策の研究開発 が必要である。

### テスト時の消費電力/ノイズ

## テスト時消費電力 > 実動作時消費電力

・テスト動作時の動作率大

- · 低消費電力設計

- 試験周波数のUp (At Speed Test適用)

Dp =システム動作時消費電力/ノイズーテスト動作時消費電力/ノイズ

図表 3-4 テスト時の消費電力/ノイズ問題

# テスト動作時の消費電力/ノイズ

- シフト動作時の消費電力

- FFの信号変化によりLSI全体が動作し、消費電力が増加する。

### 組合わせ回路

- ローンチ動作時、キャプチャ動作時の消費電力

- 一時的なIRDrop(高周波ノイズ)が発生する。

図表 3-5 テスト時の消費電力/ノイズ事例

### テスト時の消費電力/ノイズ

### 現状の対策

|          | LSI設計対策               | テストパタン対策 | テスト方法対策                                |

|----------|-----------------------|----------|----------------------------------------|

| シフト時電力   | 電源強化<br>ム<br>(面積コスト増) | トグル低減パタン | シフト周波数低減<br>LSI内部分割試験<br>ム<br>(テスト時間増) |

| キャプチャ時電力 | 電源強化<br>ム<br>(面積コスト増) | トグル低減パタン | LSI内部分割試験<br>ム<br>(テスト時間増)             |

### コスト増を伴わない対策が望まれる

図表 3-6 テスト時の消費電力/ノイズ対策

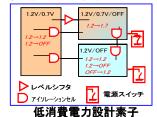

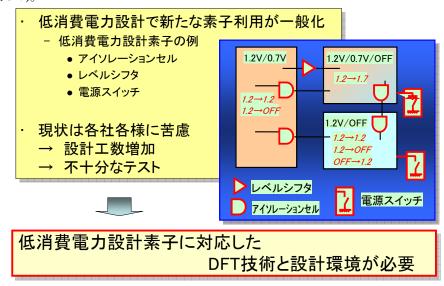

### (2)低消費電力設計素子のテスト手法

SoC の低消費電力化に対する要求が高まる中、その実現のために SoC 内に複数の電源を持たせ、動作モード切り替えにより一部の電源を遮断したり、あるいは低電圧で動作させたりするような設計が一般的になってきた。このような低消費電力化を考慮した SoC には、電源ドメインのオン/オフを制御する電源スイッチや、電源を制御した際に電源ドメイン間で生じる物理的不整合の影響を吸収するために、アイソレーションセル、レベルシフタ、電源遮断中に遮断前の状態を保持するためのリテンションセルなどの低消費電力設計素子が搭載されている。これらの低消費電力設計素子に対するテストはその手法が確立していないため、各社各様のテスト手法をとっているが、テストが不十分なために品質に影響を与えたり、テスト設計工数が増大したりしている。低消費電力設計素子に対するテスト手法の確立とそれに対応した DFT 技術の研究開発および設計環境が早急に望まれる(図表 3-7)。

図表 3-7 低消費電力 LSI で使われる素子のテスト

#### 3-3-2-2 メモリーロジック間テスト

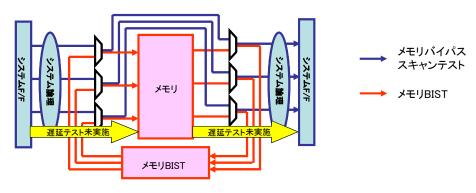

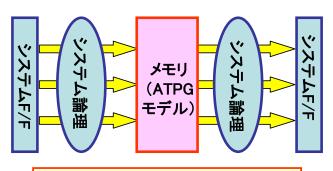

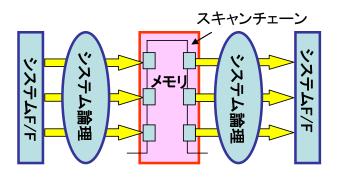

微細化による遅延故障の増加やデバイスの高速化によるタイミングマージンの減少から遅延テストの重要性が増している。特にメモリーロジック間の遅延テストは、システムのクリティカルパスになりやすいことに加えて、昨今の搭載メモリ数の増加により、ますます重要となっているが、現状十分なテストができていない。図表 3-8 に従来のメモリーロジック間テストの実施例を示す。スキャンテスト時にはメモリはバイパスされ、またメモリBIST時には、メモリのみをテストするため、メモリーロジック間の遅延テストができていない。その対策としては、図表 3-9 に示すように、ファンクションパタン、シーケンシャルテスト、メモリ入出力回路のスキャン化等があるが、それぞれ一長一短があり、決定打がない。シーケンシャルテストの実施例を図表 3-10 に示す。メモリのテスト時動作モデルを作成し ATPG(Automated Test Pattern Generation)ツールにライブラリとして与えることで、メモリーロジック間の遅延テストパタンが生成可能だが、現在の ATPG ツールの性能では、十分な遅延故障検出率が得られない場合がある。またパタン長が長くなるという問題もある。メモリ入出力回路のスキャン化の実施例を図表 3-11 に示す。本手法により高い遅延故障検出率が期待できるが、メモリの面積オーバヘッドが大きいという問題がある。また、既存のメモリの入出力回路がスキャン化されていない場合、新規のメモリ開発が必要となる。

図表 3-8 従来のメモリ・ロジック間テストの実施例

| テスト手法          | 特徴              |

|----------------|-----------------|

| ファンクションパタン     | 〇システム動作でのテスト    |

|                | ×パタン生成困難        |

| シーケンシャルテスト     | 〇メモリ再設計不要       |

|                | ×低検出率           |

|                | ×パタンが長い         |

| メモリ入出力回路のスキャン化 | 〇高検出率           |

|                | ×メモリの面積オーバーヘッド大 |

図表 3-9 現状のメモリーロジック間テスト手法

シーケンシャルテスト (メモリを介してのATPG)

図表 3-10 シーケンシャルテスト手法

# メモリ入出力回路のスキャン化

図表 3-11 メモリ入出力回路のスキャン化

以上のように現時点では、メモリーロジック間の遅延テストを高品質・低コストで実施する適切な方法がない。 そのため、今後以下の条件を満たすメモリーロジック間の遅延テスト手法の研究開発が求められる。

- •高い遅延故障検出率

- ・小さいパタンサイズ(圧縮スキャンテスト技術が適用可能)

- ・小規模回路追加 (理想は回路追加なしでシステムと同じ動作を実現)

#### 3-3-2-4 クロックドメイン間テスト

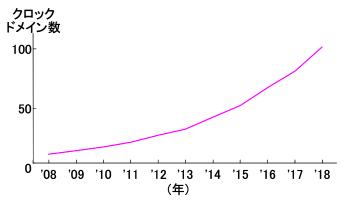

SoC に搭載される IP の多様化に伴ってクロックドメイン数も増加傾向にある。図表 3-12 は一例として ITRS2007 「テスト章」の Table TST4 にある「consumer unique cores 数(異なる種類のコア数)」をもとにクロックドメイン 数の動向を予測したものである。実際には、クロックドメイン数は用途により大幅に異なると考えられるが、いずれに しても今後ますます増加する方向である。これに伴い以下の点が問題となる。

- ファンクションテストの限界

- ・スキャンテストでのパタン数の増加の問題

- ・非同期転送のテストの問題

- ・クロック生成回路のテストの問題

これらの問題の対策として、以下の技術課題に取組む必要がある。

- ・スキャンテストでのパタン数削減手法

- ・クロック生成回路の DFT 手法

図表 3-12 クロックドメイン数の動向

### 3-3-2-5 アナログテスト、高速 I/F テスト

アナログマクロや高速 I/F のテストについては、前述のとおり DFT を用いたテスト手法の他に ATE や BOST を用いたテスト手法があり、測定精度やテスト時間を考慮した両者の適切な使い分けが課題である。特に近年の SoC への搭載が一般化してきている高速 I/F については、ATE との合同テーマとして検討した(2006、2007年度 STRJ 報告書テスト章を参照)。今後の高速化については ATE で測定できる限界を超えつつあるが、BIST だけでは測定機能の校正困難なため、高精度の特性測定は難しい。ATE / BIST / BOST を使い分ける技術が重要である。

### 3-3-3 複雑化する SoC へ対応する要求テーブルの変更検討

複雑化する SoC に対応して ITRS「テスト章」の SoC テーブル(Table TST3a/b System on Chip Test Requirements) の見直しが必要と考えられるが、その際考慮すべき項目として図表 3-13 が挙げられる。なお、個々の項目に関しては 2009 度以降検討予定である。

### 図表 3-13 SoC 複雑化への対応として考慮すべき項目

| 狙い       | 項目                                      |

|----------|-----------------------------------------|

|          | ・ばらつき考慮テスト                              |

|          | 欠陥除去テストから選別テストへ                         |

|          | ・パワー低減テストからパワー制御テストへ                    |

|          | ・よりファンクショナルな自動化テスト                      |

|          | ソフトウェアベースセルフテストと狙いは同じ                   |

| テスト品質向上  | ・デザインインテントのテスト設計反映                      |

|          | パワー制御構造、ディレイ制御構造、等                      |

|          | ・テスト品質の定量化                              |

|          | ・新規搭載デバイスのテストと DFT                      |

|          | 内蔵 Flash/FeRAM/RRAM/等、MEMS、RF(ワイヤレステスト) |

|          | ・プロトコル考慮テストと DFT の寄与                    |

|          | ・アナログ・高速 I/O の DFT/BIST                 |

| テストコスト削減 | ・アナログキャラクタライゼーション機能のテスト利用               |

|          | ・アダプティブ/予測型テストと DFT の寄与                 |

|          | ・システム/フィールドテストへの BIST 活用                |

|          | ・フォールトトレランスとテスト                         |

| 信頼性向上    | ・暗号(セキュリティ)とテスト                         |

|          | ・信頼性スクリーニング                             |

|          | バーンイン、高電圧スクリーニング、低電圧スクリーニング、等           |

|          | ・エラートレラントテスト                            |

|          | 軽度欠陥品の選別、用途別選別                          |

| 歩留まり向上   | ・マルチコア/メニーコア対応テスト&リペア                   |

| 少田より門上   | ・オンチップ故障診断                              |

|          | 不良タイプ判定などによるシステマティック不良診断                |

|          | ・テスタ不再現不良解析                             |

| 設計生産性向上  | ・テスト回路のデバッグ/その他システム目的共用                 |

なお、前述のとおり、SoC テスト要求テーブルで用いる SoC モデルに関して設計 WG と協力して見直しを 行っているが、とくに以下の点に関して変更の影響を検討した。

- ・クロックドメイン数の影響

- ・クロックドメイン数を $N_{CD}$ とするとドメイン間テストのパタン数は" $\alpha \times N_{CD}^2$ "になる。

- ・ただし設計者の意図を反映すればドメインの組合せをすべて考える必要はないはずであり、その点も 考慮する必要がある。

- ・なお、αの値については別途検討が必要である。

- ・電源ドメイン数の影響

- ・電源ドメイン数を $N_{PD}$ とすると追加分のパタン数は" $\beta \times N_{PD}$ "になる。

- ・テスト方法にも大きく依存するが、パタン数全体への影響はそれほど多くないと考えられる。

- ・ただし、同一コア同時テストの効果が低減する可能性もあり、その点も考慮が必要である。

### ·IO 数の影響

- ・IO数はとくに影響なし。

- •ただし、少ピンテストについては別途考慮が必要である。

### 3-4 国内活動 (ATE 技術)

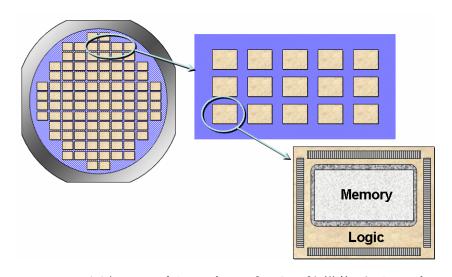

ATE 分野における国内活動は、2007 年度より取組んでいる SiP に対するテスト課題について深堀を行い、 具体的なターゲットとして 2010 年 SiP モデル(2006 年度 STRJ ワークショップ実装 WG 報告を参照)を題材に、 SiPテスト課題の整理とポテンシャルソリューションについての提案をまとめた。また、最近ITWG において議論 が開始されたアダプティブテストについて、その背景や現状の整理を行い、SiP に対するアダプティブテストの 適用例を考察し、これらの技術をロードマップ化するための考え方を整理した。以下に詳細を記す。

#### 3-4-1 SiP テスティング

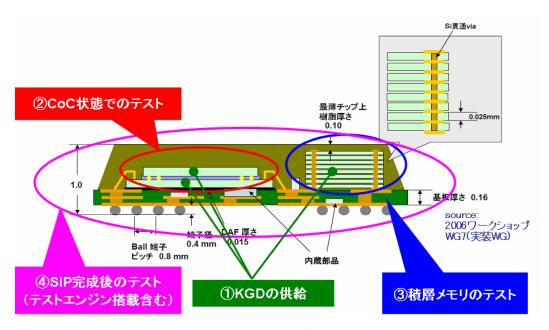

2007年度の活動に引き続き、以下の4つの切り口で課題の整理と対策について検討した(図表 3-14)。

- ① KGD の供給: SiP の前提といってもよい KGD の供給の課題と対策案

- ② CoC (Chip On Chip)状態でのテスト: ここでは、ロジック(SoC)とその上に接続されたメモリの状態でのテストの課題と対策案

- ③ 積層メモリのテスト: ここでは、メモリが TSV(Through Silicon Via、シリコン貫通電極)によって接続され、 8 段重なっている状態でのテストの課題と対策案

- ④ SiP 完成後のテスト(テストエンジン搭載含む): SiP をシステム動作でテストする仕掛け、課題と対策案

図表 3-14 2010 年の SiP モデルを題材としたテスト課題検討

### 3-4-1-1 KGD(Known Good Die)のテスト

#### (1)KGD の必要性

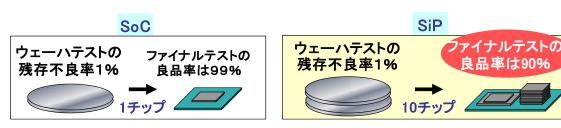

SiP の不良率は個々のチップの不良率の累積となるため、ウェーハテストを強化した組立て前のチップレベルでの不良率低減が重要となる。例えば SoC においてはウェーハテストを簡易的に実施し、例えば残存不良率が 1%であったとしても、組立て後のファイナルテストでスクリーニングできれば、トータルとしては低コストで品質の保証が可能となる。ところが、図表 3-15 に示す SiP のように 10 個のチップを実装したケースでは、ウェーハテストでの残存不良率が各々1%生じた場合、ファイナルテストの良品率は組立て要因を除外しても 90%となり、ロスコストが膨大となる。

図表 3-15 SiP におけるチップ品質の影響

### (2)KGD の定義

SiP ビジネスの拡大に伴い、KGD という言葉が頻繁に使用されつつあるが、議論をクリアにするため定義を明確にしておく。海外ベンダでは独自に定義している例も見られるが、本報告書では「ベアダイのガイドライン(EIAJ-EDR-4703)」に基づき下記定義(抜粋)で話を進めることとする。

|       | KGD (Known Good Die) | KTD (Known Tested Die) | PD (Probed Die) |

|-------|----------------------|------------------------|-----------------|

|       | プロービングテストにより, パッケ    | プロービングテストにより, パッケ      | ウェーハ状態でプローブテストを |

|       | ージ品を想定した場合の最終特       | ージ品を想定した場合の最終特         | 実施し、パッケージ品を想定した |

| 電気的特性 | 性テスト合格品と同等の特性を目      | 性テスト合格品と同等の特性を目        | 場合の最終特性テスト合格品と同 |

|       | 指したテストを実施            | 指したテストを実施              | 等の特性を目指したテスト項目の |

|       |                      |                        | 一部を実施           |

|       | パッケージ組立てや実装に起因       |                        |                 |

|       | する故障モードを除く,ウェーハ      |                        |                 |

|       | 工程起因のベアダイの初期故障       |                        |                 |

|       | に関してはパッケージ品と同等の      |                        | 品質保証の対象外        |

| 知地光陰  | 初期故障率を満足すること。        | 日所担封の社会が               |                 |

| 初期故障  | なお,規定の水準を満足しない       | 品質保証の対象外               |                 |

|       | 場合には、通常パッケージ品と同      |                        |                 |

|       | 等に、バーンインを含めたスクリ      |                        |                 |

|       | ーニングを実施し, その達成を図     |                        |                 |

|       | れるようにする              |                        |                 |

|       | パッケージ組立てや実装に起因       |                        |                 |

|       | する故障モードを除く,ウェーハ      |                        |                 |

| 長期信頼性 | 工程起因のベアダイの故障に関       | 品質保証の対象外               | 品質保証の対象外        |

|       | しては、パッケージ品と同等の信      |                        |                 |

|       | 頼性特性値を満足すること         |                        |                 |

図表 3-16 KGD/KTD/PD の定義

### 3)KGD 実現の課題とポテンシャルソリューション

#### a.高周波ウェーハテストの実現

前項の定義では、PDと KTD/KGD の違いはパッケージ品の最終特性テスト合格品と同等の特性を保証できるテストを実施できるか否かにある。ウェーハテストにおいて最も測定が困難な電気的特性の1つが、RF 帯域の高周波特性である。近年、チューナー等の RF チップも SiP 内に取り込まれ、システムの簡易化、低コスト化が急速に進みつつある。従来はパッケージ品の最終特性テストでのみ実施できれば良かった GHz 帯の RF テストを、ウェーハ状態で実現することが求められ、大きな課題となっている。

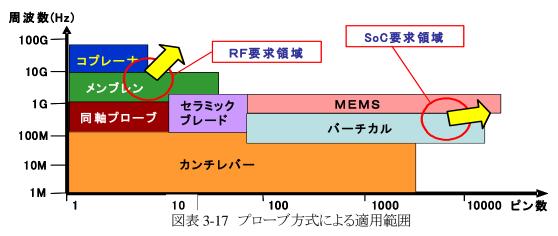

低コストウェーハテストにおいて使用されているカンチレバー方式のプローブは、100MHz~200MHz を特性保証の上限とするため、RF 用途に使用することは出来ない。RF 帯域の測定を可能にするポテンシャルソリ

ューションの 1 つがメンブレンプローブの適用で、インピーダンスマッチングを取ったフレキ基板でコンタクト点の直近まで波形品質の制御を行うことで、数 GHz の信号伝達を可能にしている。50  $\mu$  m 程度の狭ピッチ対応、同測を含めた量産化技術が確立されつつあり、RF 帯測定での適用が進んでいる。更に数十 GHz 帯の測定が必要な場合は、コプレーナ導波路により針先までの厳密なインピーダンス制御を行い、挿入損失を 1dB 未満に抑えるコプレーナプローブを用いれば実現の可能性がある。但しコプレーナプローブは数ピンが上限と用途が限られるため、プローブユニットの小型化によるピン数の向上、またはメンブレン方式での周波数特性の更なる向上が求められる。

### b.ウェーハテストコストの低減

DFT の導入が進んでいる SoC 内蔵のメモリブロックやロジックブロックにおいては、パッケージ品と同等のテストを実施することは比較的容易であるが、高速シリアル I/F や DDR 系等の高速メモリ I/F など数百 MHz~1GHz の高周波特性を要求される測定となると、カンチレバー方式のプローブカードでは保証が困難である。またこれらの高速 I/F はコスト要求が厳しいコンシューマ向けの、数百~1000 ピン超の大規模チップに搭載される例が多く、同測によるコスト低減を図るためには、針立てレイアウトの制約が少なく、数千ピン以上のコンタクトを低コストに実現できるプローブ技術が求められている。

これらの用途に応える可能性があるのが、MEMS 方式やバーチカル方式のプローブで、1GHz、10000 ピンクラスの適用が可能である。しかしながらイニシャルコストが高額となることもあり、生産ボリュームの大きい汎用メモリ、MPU を中心に適用され、ロジックチップでの適用は十分には進んでいない。今後更に多ピン高速への要求に対応する技術開発を進めると共に、標準化の推進によるイニシャルコストの低減、TAT 短縮、メンテナンス容易性の向上を進め、SiP に主に適用されるコンシューマ用途のロジックチップへの適用が期待される。

### c.ウェーハテストにおける高信頼性の確保

近年 SiP においてはパッケージ内に電源発生回路を持つ製品が多く提供されているが、これらの製品は、外部からスクリーニング加速性を高めるストレス印加ができない問題がある。また SiP においては様々なプロセスルールで製造したチップを同一パッケージ内に実装するため、SiP 化後にはストレス温度、ストレス電圧の制約を受ける。そこでウェーハ状態で信頼性も含めて保証する KGD が重要となり、その実現のポテンシャルソリューションがウェーハレベルバーンインである。

#### d.ウェーハ・レベル・バーン・イン(WLBI)の最新状況

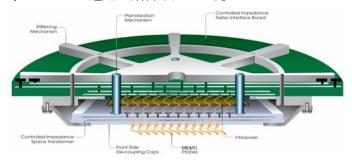

近年、SiP や MCP(Multi-Chip Package)の生産増加に伴い、製品の歩留まりの向上を図るために KGD の要求が高まってきている。従来のバーンインは、パッケージ状態のデバイスで行なっていたが、KGD の必須条件として、ウェーハ状態でのバーンイン(WLBI)が要求されている。WLBI の技術は、概ね完成されているが、導入に向けては未だ多くの課題が残されている。第一の課題として、プローブカードに関することがあげられる。

WLBI に用いられるプローブカードは、ウェーハテストに用いられているカードと同じものが使用できるが、WLBI に用いられるプローブカードは、テスト用のカードに比べて多くのコンタクト数を必要としている。ウェーハテストにおいては、ウェーハ上の複数個のデバイスを何回かに分けてテストする方法が一般的であるが、WLBI においてはウェーハ上の全デバイスに同一なストレスをかける必要性と、処理能力の向上、及び、パッケージ・バーンインと同等なバーンインをおこなうために、ウェーハ上の全デバイスを同時に処理する一括コンタクト方式を用いるので、多くのコンタクト数を必要としている。

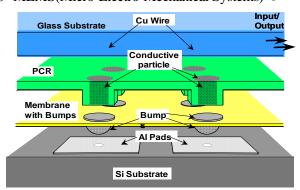

従来方式のプローブカード価格は、コンタクト数にほぼ比例するために、多くのコンタクト数を必要とする WLBI 用のプローブカードは高価になってしまう。しかしながら、KGD を要求されるデバイスは低価格なメモリ デバイスなどもあり、コストをかけることが出来ない状況にある。これらの問題を可決するために、MEMS プローブ(図表 3-18)や TPS(Tree Parts Structure)プローブ(図表 3-19)が開発され、WLBI に採用され実績を上げ始めている。TPS プローブにおいては8万コンタクトの実績と、15万コンタクトに向けての開発、また MEMS プローブにおいても4万コンタクトの実績と、7万コンタクトへの開発が行なわれており、近い将来に完成が見込まれている。また、両プローブカードとも、従来のプローブカードの製造方法と異なるため、多コンタクト化において製造コストの圧縮が見込め、WLBIへの適用に期待されている。

図表 3-18 MEMS(Micro-Electro-Mechanical Systems) プローブ参考図

図表 3-19 TPS(Tree Parts Structure) プローブ参考図

#### 3-4-1-3 CoC(Chip On Chip)のテスト

#### (1)CoC 状態とは

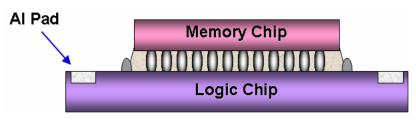

CoC とは(図表 3-20)のように、チップの上に別のチップを重ねた状態を指す。ここでは、下側はロジック(SoC) チップ、上側がメモリチップかつ下側のチップサイズが上側よりも大きく、下側チップの周辺アルミパッドにプローブする際の課題について検討を行った。

図表 3-20 CoC(Chip On Chip) の構造

### (2)CoC 状態でのテストが必要となる可能性

- ·CoC 後の上下チップ間のコンタクトの不完全性

- ・CoC 工程履歴(熱や応力など)による上下のチップの特性変化

- ・ペアとなっているチップの発熱による温度特性変化

などが考えられる。組立工程での作りこみのレベルと不良となった場合のコスト、CoC 状態でのテストのコストなどとのバランスが重要である。

### (3)CoC の形態別の課題と対策案

CoC は組立工程により、大きく二つの状態に分けられる。ひとつは下側のチップを個片状態にしてから上側のチップを接続する方法で、もうひとつは、下のチップはウェーハ状態のままで上のチップを接続する方法である。それぞれの課題と対策の概略を以下に記す。なお、メモリチップにもバウンダリースキャンなどの DFT を導入して上下チップ間の接続テストを実動作速度で効率よくできるようにすることが重要である。

| 形態            | 課題               | 対策案など              |

|---------------|------------------|--------------------|

| 個片チップを接続      | 下側のチップのパッドにプロービン | ・ N-ショットアライメント     |

| (個別のチップ同士を接続) | グする際のアライメント      | (ダイシングテープなどに再マウント) |

|               |                  | ・トレイ方式             |

| 下側のウェーハに上側の   | 下側の不良チップの処理      | (重なったチップ状態)        |

| チップを接続        | (組立て側の技術)        |                    |

図表 3-21 CoC のテスト課題とその対策案

### a.個片チップの接続の場合

課題は、上にチップがある状態での下側チップの周辺パッドへのプロービングであり、現在の技術では大きく二通りが考えられる。ひとつは CoC 状態でダイシングテープなどに再貼り付けした状態でのプロービングであり、他方は CoC チップ個片状態でのプロービングである。

### •ダイシングテープ貼り付け

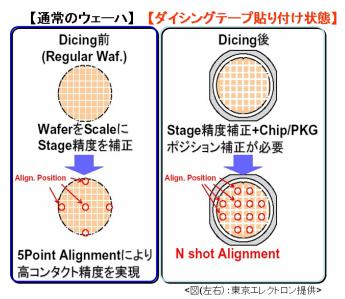

この状態を図表 3-22 に示す。CoC 後のチップをダイシングテープに貼り付けて疑似的にウェーハに近い形状にするものである。ダイシングテープへの貼り付け作業(通常、マウンターによって行われる)により、ウェーハ状態に比べるとチップの位置ずれが発生する。この場合、x、y(座標)の横方向だけでなく、θ (角度)のずれも発生し、それらの絶対値も重要だが、ばらつきが小さいことがプロービング上でもっとも重要となる。

図表 3-22 ダイシングテープにチップを搭載したイメージ

この状態においては、ウェーハでのプロービングに比べてアライメントに工夫が必要となる。概略を図表 3-23 に示す。通常ウェーハではチップ(パッド)は正確に並んでおり、5ポイント程度でアライメントすれば、ウェーハ全面のテストが可能となる。ダイシングテープ貼り付け状態では、x、y、θのアライメントが必要となるために多数箇所(最悪、1 チップ毎)のアライメントが必要となる。アライメント時間はマウント時のばらつきの大きさに大きく依存する。複数個同測ができるかはマウント時のばらつきの大きさとパッドサイズ(大きければ、より、ばらつきを吸収できる)による。

### ·CoC 個片状態

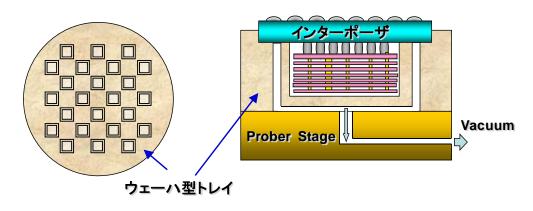

個片状態での位置出しのために、トレイが用いられる。概念図を図表 3-24 に示す。この方式のメリットは、 従来のウェーハプローバが使えることである。ただし、ステージのバキューム穴位置の都合でチップを搭載 できる場所(箇所)が制限され、トレイあたりの搭載チップ数が少なくなる。アライメントをそれぞれのチップ毎 に行う必要があるかはトレイの加工精度による。現状では、トレイの穴を CoC の下側チップぎりぎりのサイズ にすると、落としこみ・吸い上げが困難になるため、チップ毎のアライメントになる可能性がある。

Prober Stage Vacuum

図表 3-23 テープ上の CoC アライメント方法

図表 3-24 トレイ上の CoC イメージ

### b.ウェーハ状態の場合

下側がウェーハ状態のまま、上側チップを接続することができれば(組立て技術に課題はあると推定されるが)、プロービング自体は従来技術の応用で複数個同測も含めて対応可能である。

#### c.今後解決すべき課題

前述のように、現状でもある程度の対応策はあるが、更なる課題として以下がある。

- ・アライメント時間の短縮

- ・多数個同時測定数の増加

- ・上下チップの温度制御 (下側チップの発熱による上側チップの温度上昇、上側チップからの放熱経路など)

- 薄いチップのハンドリング、など。

### 3-4-1-3 積層メモリのテスト

積層メモリ化の新たな技術として注目されている TSV による積層方法で期待される点は、高密度実装による 小型化(薄化)と高速化である。しかしながら TSV では、積層による熱影響と薄膜化、貫通ビア抵抗による PI(Power Integrity)/SI(Signal Integrity)の低下、およびこれらの要因による特性劣化が課題とされている。従って、メモリ個片状態では KGD が前提ではあるが、積層メモリ状態での動作保証テストが必須と考えられ、その

保証のためには各層毎と全層同時動作時の特性テスト(TSV 毎のコンタクトチェック/リーク電流、メモリ機能、スタンバイ電源電流、At-Speed テスト等)と不良救済機能が必要である。今回、積層メモリをテストする上での固有の問題として、積層メモリのコンタクト方法とSiP後のテスト方法の2つの観点より課題検討を行った。

### (1)積層メモリ状態でテストする場合のコンタクト技術の確立

積層メモリ状態でのテストには、テスト装置およびテスト部材により、積層メモリのテスト端子に安定且つ容易に接触可能なコンタクト技術と位置合わせ技術が必要となる。今回一例として、図表 3-25 にトレイ方式を検討した。CoC でのトレイ方式の延長技術として、積層メモリがインターポーザと接続された状態で、セラミック基板に積層メモリ部を落とし込み、インターポーザ裏面に配置された半田ボールに接触する方式である。この方法は現状のプローバ装置で運用可能で、積層メモリの温度コントロールがセラミック基板を通し比較的容易に可能と考えられるが、チップ毎のコンタクト位置合わせが必要であることとセラミック基板の搭載個数が制限されることによるスループットの低下が今後の課題として残る。

図表 3-25 積層メモリのプロービング方法

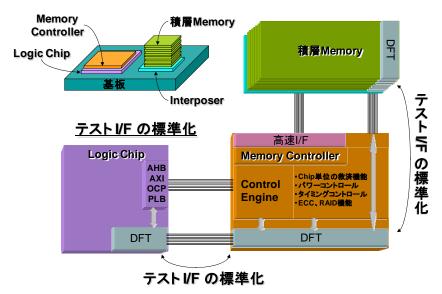

### (2)SiP 後のテスト容易化設計された各チップのテスト I/F 標準化

もう一つの課題は組立て後の動作保証テストである。積層メモリは、CoCと接続されているのでI/Oピンに直接アクセスする事が困難となるため、システム動作と同様に CoC の I/O を通した積層メモリの内部制御と観測が必要となる。しかしメモリに DFT 構造が組込まれていない場合は、こうしたアクセスはメモリテストのパタン長増大や検出率の低下を招く。そのためメモリ DFT の搭載が必須となる。図表 3-26 に示す積層メモリのテストは、CoC の DFT 回路よりメモリコントローラと積層メモリの DFT を制御してテストを行う。従って DFT 回路のテストI/F が各社各様の方式では接続が困難となるためテストI/F の標準化が重要である。例えば IEEE 1500 にて SoC 内のラッパーによるコアテストI/F の標準化が行われたが、SiP でも同様な検討が望まれる。必要なテスト機能としては、積層メモリの機能テスト、At-Speed テスト、不良救済テスト等であり、またそれらがメモリの各層毎と全層同時動作時でテスト可能であることが必要であると考えられる。設計/テストコストの低減、信頼性の向上のため、SiP に搭載されるチップのテストI/F は早急な標準化が望まれる。

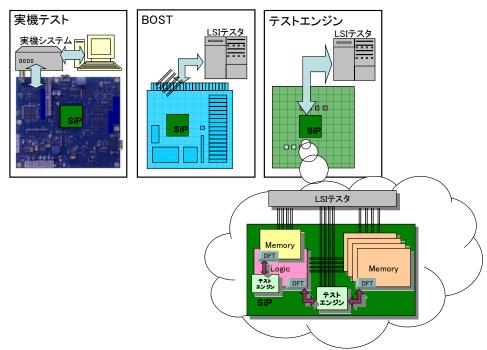

#### 3-4-1-4 SiP 全体のテスト

SiP 全体(組立て後)のシステムレベルのテストは、その SiP を構成するチップ単体のテスト、あるいは CoC や積層メモリ等のモジュール個別テストの重要性もさることながら、近年その重要性が増している。チップ単体のテストとチップ間の接続テストだけでは、SiP としてのテストは十分でない。例えば、チップ間やモジュール間でのノイズの影響、発熱の影響、あるいはマージン差等による影響は、システムレベルで検証を行う必要がある。シミュレーション技術の発達によりこれらの検証の負荷は軽減される傾向にあるものの、その必要性は今後も依然として残り続けるであろう。しかしながら、現状のシステムレベルのテスト、いわゆる実機テストは、一般的に、テスト品質は確保できるものの、量産性が悪く、コスト面でデメリットとなる傾向がある。量産性が良く、低コストで、しかも汎用的にシステムレベルのテストができる仕組みを構築する必要がある。そこで今回、システムレベルのテストとして、①実動作テスト(高速テスト)、②量産テスト性(低テストコスト)、③故障個所の特定、という 3

### つの課題の解決に向けた検討を行った。

図表 3-26 SiP の DFT 概念図

### (1)現状の SiP 全体のテスト

SiP 全体のテストは、究極的には、エンドユーザーでの使用環境を完全に再現し、その時の動作を確認することである。これは実機テストにより可能であるが、スループット等の量産テスト性が悪く、特別な品質が要求される場合に限って実行するのが一般的である。現状、量産テスト性とテスト品質の両立のために、BOST(Built-Out Self-Test)技術がSiPに限らず広く使われている。特に高速I/Fテストでは、テストボード上にテスト対象の高速I/F回路と通信相手のデバイスを配置してテストを実行する使い方が多く用いられている(BOSTの定義はいくつかあるが、ここではこのような広義の意味でBOSTと呼ぶ。また、テスト対象回路に対しては、BOSTを実現するためのDFTの組込みが前提となる)。BOSTを用いると比較的に安価なテスタでテストを実行できるメリットがある反面、BOSTは、テストボード設計や製造の難易度が高く、テスト全体のデバッグ性や解析性も困難なことが多い。上記のような高速I/F用BOSTにおいては量産テスト性に優れる場合もあるが、一般的に量産までのテスト開発期間や不良デバイスの解析は長期化する傾向がある。

### (2)今後の SiP 全体のテスト

今後のSiP全体のテストは、そのSiPを構成するチップやモジュールの高速化や複雑化に伴い、チップレベルからシステムレベルへ移行し、その重要性や必要性も一層増すと考えられる。そのためにも、量産テスト性に優れたシステムレベルテストの実現が望まれる。

SoC において、DFT、BIST、メモリ BIST 等に代表される「テスト用 IP 技術」に、その実現へのヒントがあると考えられる。SiP においても、SoC チップそのものテストや、SoC-メモリ間の At-speed テストは BIST 等による対応が必要であることは言うまでもないが、高速テスト、ノイズ検出、解析を目的とした高精度なタイミングプローブ等の要求、故障診断、救済等の要求に対しては、BIST の考え方を拡張し、それぞれの要求を実現するための Infrastructure-IP (2006 年度 STRJ 報告書テスト章を参照)を搭載して対処することが必要と思われる。Infrastructure-IP の SiP への応用には、上記に加え、実動作テストを可能とする仕組みを搭載することが要求される。この仕組みを「テストエンジン」と呼ぶことにする。「テストエンジン」とは、下記のような機能を持ったInfrastructure-IP である。

- ・実機をエミュレートする機能

- ・LSIテスタにより制御可能

- ・各チップに内蔵された DFT の制御(BIST の制御、チップのアイソレート、Bypass 機能等)

「テストエンジン」は SoC チップに搭載しても良いが、面積オーバヘッドやタイミングの問題等がある場合は、

専用チップとしての搭載が有効であると考えられる。例えば FPGA を用いて機能を実現する方法では、SiP の機能に応じてプログラム(システム制御)が変更可能である。

今後、「テストエンジン」と各チップに内蔵されたDFTとのI/Fの整備(標準化)や「テストエンジン」が不良の時の対応(Repairable チップへの対応)等の検討課題は多いが、SiP の実動作テストの実現と量産テスト性を兼ね備えた手法、また、SiP 解析性を向上する手法として期待される。

図表 3-27 SiP 全体テストの各手法イメージ

|        | 実機テスト | BOST | テストエンジン |

|--------|-------|------|---------|

| 量産テスト性 | ×     | 0    | ©       |

| テスト品質  | 0     | Δ    | 0       |

| 故障解析性  | Δ     | ×    | 0       |

図表 3-28 SiP 全体テストの各手法比較とテストエンジンへの期待

#### 3-4-2 アダプティブテスト

### (1)背景

従来のテスト手法では、全てのデバイスを同一のテスト条件で測定し良否判定することを基本としていた。 しかし最近では、単にデバイスの良否を判定するのみならず、品質や歩留まり向上を図る目的がテストに課せられ、そのためテスト時間が長くなるなどテストコスト増大の一因となっている。アダプティブテストは、デバイスが必要なテストをそのデバイスの出来映えで判断し、必要なテストのみを行うことで、デバイスの信頼性向上と、全体テストコスト低減を狙いとする技術である。半導体テストエンジニアが(特に日本では)、10 年以上も前から実践していた暗黙知が最近、アダプティブテストとしてネーミングされ、システマティックな手法として注目されてきているとも言える。ITRS2007 の「Difficult Challenges」の一つにも取り上げられ、日本側も活動の一つのテーマとして歩留まり/品質向上とコスト削減の両立を狙った有望な手法として検討開始した。

### (2)アダプティブテストの定義と期待する事

品質とコストの両立を狙ったアダプティブテストは、ITRS で 2009 年から定義の明確化を含めた検討活動が 開始されたところである。日本側は 2008 年度にアダプティブテストの定義付けおよび相応しい和訳を目指した が、結局、時期尚早と考え、現状技術調査を中心に行った。また SiP のテスト課題に対しアダプティブテストに よるポテンシャルソリューションの可能性を検討した。 具体的には、5 分野(テスタベンダ、関連特許、ツールベンダ、テスト関連の国際会議、半導体ベンダ)の調査を実施し現状を明確化した。また講演会では、ビジネス最先端に従事している講師より最新のホットな話題を紹介頂きアダプティブテストに関する次の知見を得た。

『従来手法のテストは、全てのデバイスに同じテストプログラムを実施していたが、アダプティブテストはデバイスにどんなテストが必要かを判断し、必要なテストのみを行う。その狙いは、信頼性を向上し、品質を保証し、全体としてのテストコストを下げることである。先進のアダプティブテスティングは、あらゆるデータを利用しリアルタイムにテストプログラムを更新できるようになった。工程間、ウェーハ、ロット、といった単位でテストを管理し、時間とともに状況をラーニングして、テスト時間を削減する。例えば、歩留まりベースラインと称するツールでは、TTR(Test Time Reduction)#1では90%、TTR#2では80%、TTR#3では70%と、初期時のテストに比べてテスト時間が削減されることをサポートするものである。その手法の概要は、最初、基準チップの選び方を様々なアルゴリズムによって決定し全てのテストを実施する。次に、全テスト結果のデータログが取られ、その結果をもとに最適なテスト項目を判断し、時間とともに TTR を実現する。また、ロット内の数枚のウェーハで検証を行う。検証ウェーハでは全項目のテストを行い、そのロットの健全性を判定し、その他のウェーハのテスト項目を決定する、と云うものである。』

アダプティブテスト課題のソリューションのロードマップ化を通して、従来テストエンジニアが行ってきた暗黙知が体系化され、アダプティブテスト技術が大きく進展することを期待したい。

### (3)SiP における考察

テスト技術は対象とするデバイスにより検討内容が大きく左右される。アダプティブテスト課題のソリューション検討においても対象デバイスを明確にすることが重要であると考えた。今年度は対象デバイスを SiP に絞り、テスト WG で 2007 年度に検討した SiP の FEMA(故障モード影響解析)分析まとめの課題(2007 年度 STRJ 報告書テスト章を参照)に対し、アダプティブテストで解決できるか否かを検討した。その結果を図表 3-29 にまとめる。アダプティブテスト(テスト測定データのフィードバック/フィードフォワード)を活用した解決策の一例として以下が挙げられる。

- ·SiP に搭載される各チップの動作マージンを個別に実測し、データベースに格納する。

- ・その実測データを基に、SiP 全体の動作シミュレーションを行い、SiP の動作スペックを満たす VLSI チップ の組合せを選定する。

- ・選定した VLSI チップを組立てる。

このようにアダプティブテストを用いることで、従来のテスト枠を超えた可能性が開けることも期待できる。

#### (4)ロードマップ策定に向けて

前述のように、アダプティブテストの定義が明確化されない段階でのロードマップ化は時期尚早との認識から、今年度はロードマップイメージの共有(ロードマップ策定に向けたフォーマット整備)に焦点を絞って討議した。具体的にはアダプティブテストによって恩恵を被る半導体技術のチャレンジ項目を洗い出し、その項目をカテゴリ別に分類してロードマップのイメージを作り上げることにした。カテゴリには、【品質、テスト時間、歩留まり、プロセス、設計マージン、ウェーハテスト、ファイナルテスト】の7項目を取り上げた。

この中で微細化や低電圧化に伴い今後ますます困難化が予想される設計マージンについて、図表3-30 のフォーマットを考案し、ロードマップ策定に向けてキーワードを検討した。設計マージンの検証技術に関し、その技術を支えている技術要素(キャラクタライゼーション、ベリフィケーション、評価項目)、更に支える技術要素(ユーザーインターフェース、評価テストパタン、CAD ツール、設計検証専用テスタ、EB テスタ、電源電圧、タイミング)を洗い出し、それらの要素が将来どの様な技術になるかを予測するフォーマットとした。そして、将来を予測する手助けに過去(1970 年代から)の該当技術に相当するキーワードを議論し洗い出した。今後、本フォーマットを元にロードマップ策定を推進予定である。

| 課題       | テスト困難な項目                  | テストの方法                                 | 実現に必要な機能                      | 必要な設備                                         | 解決策例                                                           |

|----------|---------------------------|----------------------------------------|-------------------------------|-----------------------------------------------|----------------------------------------------------------------|

|          | 動作時の電源ノイズ                 |                                        | 搭載部品の周囲への電気的<br>影響をシミュレートする機能 | SiP 組込みシステムから該<br>当 SiP のみを除いた SiP<br>対応テスト装置 | <ol> <li>搭載部品の動作マージン(実測データ)を<br/>SiP データベースに登<br/>録</li> </ol> |

| 搭載品相互の影響 | 共通端子<br>(電源/GND)の一<br>部断線 | 単体での徹底した動作マージ<br>ンチェック                 | 個々の端子の接続を独立し<br>て確認できる機能      | 超高精度の抵抗測定器等                                   |                                                                |

|          | 隣接チップ発生の<br>熱の影響          | 相関  ナップ (/ ))温焼採油                      | 搭載部品の周囲への熱的影響をシミュレートする機能      | SiP に搭載された部品と同等の発熱装置                          | 2. SiP 組立て前に動作<br>するかどうか確認                                     |

|          | 不良箇所の特定                   | 全体のシミュレーション環境構<br>築(含む、部品のモデル決定)       |                               |                                               | 3. 確認結果で搭載部<br>品の組合せ選定しSiP<br>組立て作業に入る                         |

| 不良部品の取扱い | 不良品の取替え                   | 少なくとも実装時に交換することを前提とした方法で製造する<br>ことは不可欠 |                               |                                               |                                                                |

図表 3-29 SiP におけるテスト課題とアダプティブテストによるソリューション例

| 設計マージン検証技術 | キャラクタライゼーション | ユーザーインターフェース |  |

|------------|--------------|--------------|--|

|            |              | 評価テストパタン     |  |

|            |              | CADツール       |  |

|            | ベリフィケーション    | 設計検証専用テスタ    |  |

|            |              | EB テスタ       |  |

|            | 評価項目         | 電源電圧         |  |

|            |              | タイミング        |  |

| 1970 年代 | 丁稚奉公による設計者伝承     |

|---------|------------------|

| 1980 年代 | 」作学公による以刊 1日 14年 |

| 1990 年代 | 設計検証専用システム       |

| 1995 年代 | 以可拠証号用ンハノム       |

| 2000 年代 | 高度 CAD との連携      |

| 2005 年代 | 同及 CAD CV/ 建伤    |

| 現在      |                  |

図表 3-30 ロードマップ策定に向けたフォーマット整備例

### 3-5 まとめと今後の課題

2008 年度は ITRS 2009 改訂へ向けた準備を中心に活動した。特に、テスト技術における DFT 技術の役割をより明確に ITRS へ反映しようとの日本からの呼びかけに対して、ITWG の賛同を得て、活発な議論が進められている。また ATE 技術においては、プローバやハンドラ、その他多くのテスト技術について日本が中心に見直している。また、平行して 2006 年度から継続検討してきた SiP テスト技術について ATE、DFT 技術を融合した形での検討および提案を行った。かなり専門的な分野に立ち入って具体的な方式を検討し、課題が明確化できたと考えている。今後、更なる検討と、ロードマップへの反映、および関係者へのアピール活動(クロスカットによる検討を含む)を推進予定である。