# 第 12章 WG14 メトロロジ(計測)

#### 12-1 はじめに

2008年度の主な活動は、ITRS国際会議(サンフランシスコ、韓国、ブリュッセル)の参加(2008年度ITRSのupdate)、日本におけるリソグラフィー、ERD/ERMとのクロスカットによる計測要求の把握、計測ヒアリングを通しての技術動向の把握であった。国際会議における主なポイントは、欧州参加メンバーのASMLからの提案もあり、2重露光についてリソとのクロスカットを通して、要求項目の議論を行った。歪みに関しては2007年度から継続して要求内容の具体化に向け情報のインプットを各TWGに要請している状況であり、2009年度にまとめる方向で活動を継続している。また、ITRSのtextのupdateについても議論を行った。計測のヒアリングに関しては、従来から電顕の比重が大きく、今後はバランスをとったヒアリングの計画を立てる予定である。2008年度は、ERMとのクロスカットにおいて、低損傷、高分解能の計測要求もあり、電顕の収差補正についての情報の紹介を行った。2009年3月のSTRJワークショップにおいては、全体的なテーマがエコということもあり、今までのSTRJの計測としての活動から得られた知見を基に発表を行った。以下詳細な活動報告を項目ごとにまとめて紹介をする。

#### 12-2 ITRS 2008 Update 版の主な改訂ポイント(図表 12-1 参照)

従来から計測の代表として図表 12-1 に示す要求項目について改訂内容を紹介しているが、今回の主な改訂としては、MPU のエッチング後の物理ゲート長のトレンドが実情に併せて 3 年後ろ倒しされたことに伴い関連する箇所が変更になっている点である。

|     | able MET3 Lithography Metrology (Wafer) Technology Requirements                                               |           |             |             |            |            |             |              |

|-----|---------------------------------------------------------------------------------------------------------------|-----------|-------------|-------------|------------|------------|-------------|--------------|

|     | Year of Production                                                                                            | 2009      | 2010        | 2011        | 2012       | 2013       | 2014        | 2015         |

|     | Flash ½ Pitch (nm) (un-contacted Poly)(f)                                                                     | 40        | 36          | 32          | 28         | 25         | 22          | 20           |

|     | DRAM ½ Pitch (nm) (contacted)                                                                                 | 52        | 45          | 40          | 36         | 32         | 28          | 25           |

|     | MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                            | 52        | 45          | 40          | 36         | 32         | 28          | 25           |

|     | MPU Printed Gate Length (nm) ††                                                                               | 34        | 30          | 27          | 24         | 21         | 19          | 17           |

|     | MPU Physical Gate Length (nm) [after etch]                                                                    | 20        | 18          | 16          | 14         | 13         | 11          | 10           |

| IS  | MPU Physical Gate Length (nm) [after etch]                                                                    | 27        | 24          | 22          | 20         | 18         | 17          | 15           |

|     | Wafer minimum Overlay control DRAM single litho tool (nm)                                                     | 10.3      | 9.0         | 8.0         | 7.1        | 6.4        | 5.7         | 5.1          |

|     | Wafer overlay output metrology uncertainty (nm, 3 σ)* P/T=.2                                                  | 2.1       | 1.8         | 1.6         | 1.4        | 1.3        | 1.1         | 1.0          |

|     | Gate (MPU Physical Gate Length)                                                                               |           |             |             |            |            |             |              |

|     | Printed gate CD control (nm)                                                                                  |           |             |             |            |            |             |              |

| IS  | Uniformity (variance) is 12% of CD                                                                            |           |             |             |            |            |             |              |

|     | Allowed lithography variance = 3/4 total variance of physical gate length *                                   | 2.8       | 2.5         | 2.3         | 2.1        | 1.9        | 1.7         | 1.6          |

|     | Wafer CD metrology tool uncertainty (nm) * 3\sigma at P/T = 0.2 for isolated printed and physical lines [A]   | 0.42      | 0.37        | 0.33        | 0.29       | 0.27       | 0.23        | 0.21         |

| IS  | Wafer CD metrology tool uncertainty (nm) * $3\sigma$ at P/T = 0.2 for isolated printed and physical lines [A] | 0.55      | 0.50        | 0.46        | 0.42       | 0.38       | 0.35        | 0.32         |

|     | Table MET5a                                                                                                   | Front End | Processes I | Metrology T | Technology | Requireme  | ent         |              |

|     | EOT (Extended planar bulk) for High Performance MPU/ASIC for 1.5E20 doped Poly-Si [FEP Table 69]              |           |             |             |            |            |             |              |

| IS  | EOT (Extended planar bulk) for High Performance MPU/ASIC for 1.0 E20 doped Poly-Si [FEP Table 69]             | <u>1</u>  |             |             |            |            |             |              |

| WAS | EOT (FDSOI) High Performance MPU/ASIC for metal gate [FEP Table 69]                                           |           | 0.7         | 0.6         | 0.55       | 0.5        | 0.5         | 0.5          |

| IS  | EOT (FDSOI) High Performance MPU/ASIC for metal gate [FEP Table 69]                                           |           |             |             |            | <u>0.7</u> | <u>0.65</u> | <u>0.575</u> |

| WAS | EOT (multi-gate) High Performance MPU/ASIC for metal gate [FEP Table 69]                                      |           |             | 0.8         | 0.7        | 0.6        | 0.6         | 0.6          |

| IS  | EOT (multi-gate) High Performance MPU/ASIC for metal gate [FEP Table 69]                                      |           |             |             |            |            |             | 0.77         |

| WAS | Low operating power EOT (bulk) for 1.5E20 doped poly-Si [FEP Table 69]                                        | 0.7       | 0.6         | 0.5         | 0.5        |            |             |              |

| IS  | Low operating power EOT (bulk) for 1.5E20 doped poly-Si [FEP Table 69]                                        | 1.1       | 0.7         | 0.7         | 0.6        | 0.5        |             |              |

| WAS | Low operating power EOT (multi gate using metal-gate) FEP Table 69                                            |           |             | 0.9         | 0.9        | 0.9        | 0.8         | 0.8          |

| IS  | Low operating power EOT (multi gate using metal-gate) FEP Table 69                                            |           |             |             |            | 0.9        | 0.9         | 0.85         |

| WAS | Low operating power EOT (FD-SOI) (metal gate) [FEP Table 69]                                                  |           |             | 0.9         | 0.9        | 0.8        | 0.8         | 0.8          |

| IS  | Low operating power EOT (FD-SOI) (metal gate) [FEP Table 69]                                                  |           |             |             |            | 0.9        | 0.85        | 0.8          |

|     | Table MET6                                                                                                    |           |             |             |            |            |             |              |

|     | Measurement of deposited barrier layer at thickness (nm)                                                      | 3.7       | 3.3         | 2.9         | 2.6        | 2.4        | 2.1         | 1.9          |

|     | Process range $(\pm 3 \sigma)$                                                                                | 10%       | 10%         | 10%         | 10%        | 10%        | 10%         | 10%          |

|     | Precision $\sigma s$ (nm) for P/T=0.1 [B]                                                                     | 0.037     | 0.033       | 0.029       | 0.026      | 0.024      | 0.021       | 0.019        |

|     | Detection of post deposition and anneal process voids at or exceeding listed size (nm) when these voids       |           |             |             |            |            |             |              |

|     | constitute 1% or more of total metal level conductor volume of copper lines and vias.                         | 5         | 4.5         | 4           | 3.5        | 3.2        | 2.8         | 2.5          |

|     | Detection of killer pore in ILD at (nm) size                                                                  | 5         | 4.5         | 4           | 3.5        | 3.2        | 2.8         | 2.5          |

図表 12-1 ITRS 2008 update

MPU のゲート長のバラツキの要求値はゲート長の 12% であり、リソグラフィーは分散として、その 3/4 を加工

精度として担っている。また本ケースでは規格値に対する計測精度(P/T:Precision to Tolerance)が 0.1 と規定されているので、 $CD \times 0.12 \times (3/4)^{1/2} \times 0.1$  が計測要求精度ということになっている。色分けに関しては、ゲート長のスケーリングが緩和された分の恩恵を受けている。リソグラフィーの CD 計測は 2012 年まで白色である。また FEP の EOT に関しても MPU のゲート長の後ろ倒しで、2009, 2010 年に空白の欄が生じるため、それぞれ 1, 0.95 が挿入されている。他のデバイスにおいても 2 年ほどスケーリングが後ろ倒しになっている。

Interconnect に関しては、従来からの変更は特に無いが、ローカルな void の検出要求に対しては、対応する空間分解能を有する計測原理、手法がないため継続して赤色状態が続いている。実際問題、他の代替手段で不良や、信頼性に関わる void の発生が無い事が検証されていると思われるため、本当に要求項目としての必然性があるかも今後議論が必要と思われる。

# 12-3 国際会議での主な議論テーマ

以下に2008年度に議論された内容について概容を記載した。

- 1. 2 重露光に関しては ITWGの Metrology のメンバーが ASML ということもあり、さらに要求項目のブレーク ダウンが必要との提案があり@2008 ITRS Spring Meeting、2008 ITRS San Francisco でリソグラフィーとの crosscut を行い、2 重露光に関する要求項目について議論。会議の効率化のため事前に日本で crosscut を実施し叩き台を準備。計測要求としては、SWA(Side Wall Angle)といった単純な台形パターン近似から、三次元プロファイル、すなわち、トップのラウンデング、裾引き、太鼓形状といった断面形状を計測し、管理する必要性が増している点がリソグラフィー側から指摘。また、母集団の異なるパターンが対象となり、測定点も、Line の 1,2、Independent space、Dependent space の同時計測で、かつ、一回目の露光で形成されるパターンと、二回目の露光で形成されるパターンを判別して測定することなどが要求項目として挙げられた。2009 年度にリソグラフィーから要求項目が整理され情報のインプットがなされる予定である。また、2009ITRS Spring meeting では、マスクレスの NGL(Next Generation Lithography)に対応した、フルウェーハの die to database の必要性が挙がった。問題はスループットであるが、具体的な要求項目案はリソグラフィー側から提示予定。また、マスクの計測として EUV(Extreme Ultra Violet)に対応した AIMS(Aerial Image Measurement System)の要求も上がった。

- 2. 歪み計測に関しては継続して情報のインプットを各 ITWG に要請 2009 年度に update 予定。

- 3. 近年3次元の形状計測要求がリソグラフィー、FEP, Interconnect からも上がっており、対応する計測技術について Metrology 側として整理する方向で検討。Scatterometry に関しては NIST(National Institute of Standard and Technology)や ISMI(International SEMATECH Manufacturing Initiative)等から報告がなされているが、scatterometry はモデルベースの計測のため精度検証方法についても今後議論が必要と思われる。SAXS(Small Angle X-ray Scattering)については、実験データも報告されているが、今後の製品化を待った上での評価結果が期待されている。

- 4. ERD(Emerging research Device)/ERM(Emerging Research Material)の要求として低ダメージの観察技術の要求があるが、日本側で、現状最も高い分解能を有する TEM(Transmission Electron Microscope), STEM(Scanning Transmission Electron Microscope)の技術について収差補正技術の現状と動向を踏まえ review を行った。また、低ダメージに関しては、低エネルギーの電顕観察にフォーカスが行われており、色収差補正等を用いた技術の紹介が有り情報の共有を行った@2009ITRS Brussel。これは主にカーボン材料の観察に対応できるというものである。一方他のカーボン材料の観察手段(フェムト秒レーザーを用いた Atom Probe?)についても今後調査を進めて行く予定。

- 5. Precision が Uncertainty に変更になったが、要求値自体の変更は成されていないのが現状である。また、 要求値の coloring の根拠となるデータも Precision(精密さ)をベースにしたものであり、Uncertainty(不確か

- さ)に変更した意味が薄れている。Uncertainty は運用環境的な要素も入るために、数値化は難しく、再度要求値の表現方法については議論が必要であると考えられる。2008年度はこの問題点の指摘を行った。

- 6. FEP からの要求の確認(新しいチャネル材料・構造導入に伴う Metrology への要求、具体事例として、 Vertical な表面を有するデバイスの、表面状態やドーパントプロファイル計測、 20nm サイズのパーティ クルのインラインでの測定、 ドーパントのアクティブ及びケミカルな濃度の測定、STT(Spin Torque Transfer)の stack 構造の一括膜厚計測等)

- 7. Interconnect からの要求の確認(3D 配線、CNT 配線、光配線等々。具体的事例、soft Matter(有機材料、カーボンナノチューブとグラフェンなど)の顕微鏡観察、スピン構造の顕微鏡観察等)また、voidの計測にあたっては以前から coloring が赤のままであり、本当に必要な要求項目なのか検討を依頼。

- 8. ERD/ERM からの要求の確認(おもにカーボン系の低損傷の観察) 米国から LEEM(Low Energy Electron Microscope)の紹介有り。 ERM からは、フェムト秒レーザーを用いた Atom Probe によるカーボン構造の観察の状況についての問い合わせ有り。

- 9. FI: 計測データのファイルフォーマット、APC(Advanced Process Control)/AEC (Advanced Equipment Control)関連計測技術を今後議論。

- 10. YE: air-born contamination と particle size の計測についての要求があった。前者に関しては、計測環境 時の汚染や UV 計測における光源自体の影響(化学的変化)が無い計測の要求があった。状況によって は、計測時の影響の排除としての後処理等について議論した。この辺の専門家がメンバーに居ないことも あり、今後 Metrology として扱えるかどうか検討。

### 12-4 計測ヒアリングの内容

計測のヒアリングとして、1. 電顕(TEM, STEM 含)の収差補正による空間分解能の向上、2. 貫通電極(TSV: Through Silicon Via)エッチング深さ計測、3. 反り/膜ストレス検査について概容を紹介する。

#### 12-4-1 電顕(TEM, STEM 含)の収差補正による空間分解能の向上

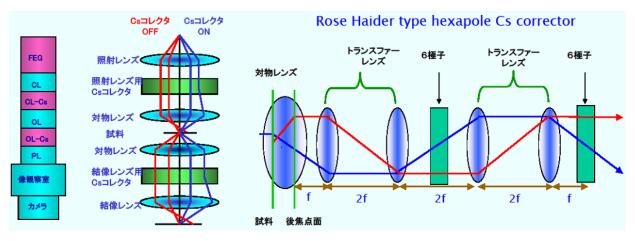

電子顕微鏡(以下電顕)に対する大きな関心事として空間分解能の改善が挙げられる。これに関しては、2007年度の計測の活動としても取り上げ、収差補正によるその効果についてヒアリングを行い、2007年度の報告書でも詳細な解説を行っている。電顕の収差補正については TEM, STEM への適用から、観察 SEM への導入とその適用範囲が拡大している状況である。2008年度のヒアリングからの知見として、さらに収差補正の機能の補足を行うこととする。図表 12-2に収差 Cs-correctorを搭載した(S)TEMのレンズ構成を図表 12-2、図表 12-3に示した。ちなみに Cs は、spherical aberration(球面収差)係数のことであり(Coefficient of spherical aberration)、この収差係数を 0にすることが、球面収差補正を 0にすることと同じことを意味する。STEMの場合は照射レンズ用 Cs-correctorが用いられ、TEM の場合は結像レンズ用 Cs-correctorが用いられ。各 Cs-correctorの現在主流の構成は、Rose、Haider らによって開発されたものであり、図表 12-3に示す様に 6極子とトランスファーレンズを組み合わせた構成であることに特徴がある。

図表 12-2 図表 12-3

6極子は同等な2式が用いられ、それぞれの6極子の中心は対物レンズの後焦点面と光学的等価面になるようにトランスファーレンズ(2 式のラウンドレンズからなる)を用いて、互いに逆極性で働くように配置されている。この様な光学系により6極子場が主に発生する3回対称2次非点が相殺され、6極子場内部でコンビネーション収差として発生する球面収差を6極子場の適正な励磁により対物レンズの球面収差の逆符号で発生することができる。(図表 12-3)

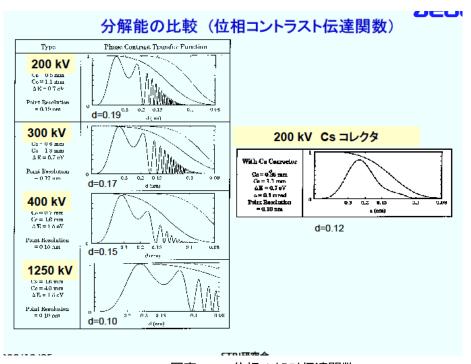

図表 12-4 極子磁場によるビーム形状の変化

Cs-corrector を搭載した(S)TEM の理論分解能は位相コントラスト伝達関数(PCTF: Phase Contrast Transfer Function)によって示される。図表 12-5 にその計算例を示す。PCTF が最初に"0"となる箇所が理論分解能を示 している(情報量の伝達限界)。Cs-corrector を搭載した(S)TEM の分解能を制限するのは色収差であり、これを 低減させるために、電子銃に冷陰極 FE(Field Emission)を搭載したり、各種のモノクロメータを搭載したものもあ る。これら Cs 補正、色収差低減を施した鏡筒で、最近では 200kV~300kV で分解能 0.05 の超高分解能が 達成されている。

図表 12-5 位相コントラスト伝達関数(PCTF)

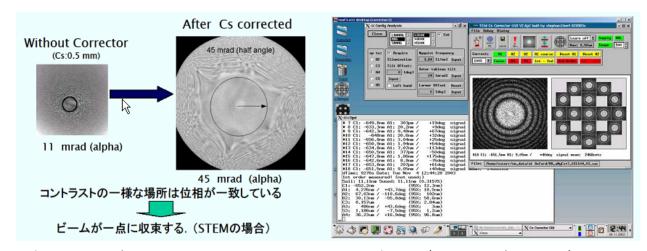

上述したように Cs 補正は複数の多極子を使用する為、複雑な励磁バランスが必要であり、収差補正の自動化 が開発されている。そのためには収差の定量化が必要であり、照射系の場合ではロンチグラフ(図表 12-6)から、 結像系の場合にはディフラクトグラム タブロー(図表 12-7)からそれぞれ精度よく抽出することができる。

図表 12-6 ロンチグラフ

このような Cs 補正を施すと、次の様な効果が現れる。

図表 12-7 ディフラクトグラム タブロー

## TEM Cs 補正では、

- 1. サブオングストロームのリアルタイム高分解能観察が可能

- 2. 界面、表面の正確な観察が可能(格子縞はみ出しがない)。

#### STEM Cs 補正では、

- 1. サブオングストロームの分解能が得られる、

- 2. EELS(Electron Energy-Loss Spectroscopy)分析により column by column の分析が可能となる、

- 3. EDS(Energy-Dispersive X-ray Spectroscopy), EELS 分析に於いて、感度を 1 桁向上できる。

昨今では、新材料として期待されているが電子線ダメージに弱いカーボンナノチューブの観察に関心が注がれている。

#### 12-3-2 貫通電極(TSV)エッチング深さ計測

今日、微細化や歪技術、High-k/Metal Gate に代表されるテクノロジーブースターと並行し、貫通電極(TSV: Through Silicon Via)を用いて3次元に回路を積層し、デバイスのさらなる高密度、高速動作、低消費電力を目指す動きが急速に高まりつつある。この貫通電極形成技術において、必要な計測の一つとしてエッチング深さ計測があげられる。この背景は、深さが数十 um から百 um 程という通常の半導体工程に比べて一桁深い特殊な工程である事や、Memory や Logic 用途で主流である Via を表面より形成するプロセスでは、エッチングストッパ層がなくブラインドエッチングとなってしまう事が、計測を必要とされている理由の一つである。

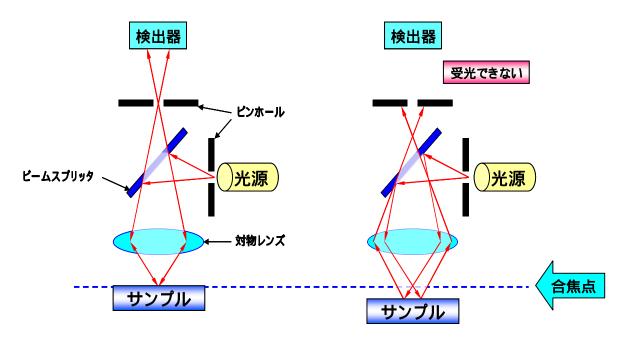

通常、構造物の高さや深さを通常の光学系を用いて測定する場合、反射光の輝度情報を利用し、焦点が合って輝度が一番高くなる高さを試料面と認識する。ところが貫通電極の様な小さく深いではの場合、 Viaの底部分からの反射光強度が微弱で、且つ 迷光(計測に必要とされない有害な光)が大きいという問題があり、通常の光学系では深さの計測が困難となってしまう。この問題を解消するため、コンフォーカル光学系と白色干渉計の組み合わせを採用し、深さ計測専用のコンフォーカル光学系で迷光の排除を行い、底部分からの微弱な反射光を捉え、同時に白色干渉計の高い分解能を活かした深さ計測手法の紹介がレーザーテック株式会社よりあった。これにより、現在多く見受けられる開口径が数umから50umでアスペクト比が高いではも、0.1um以下という高精度で深さ測定を実現しているとのことである。

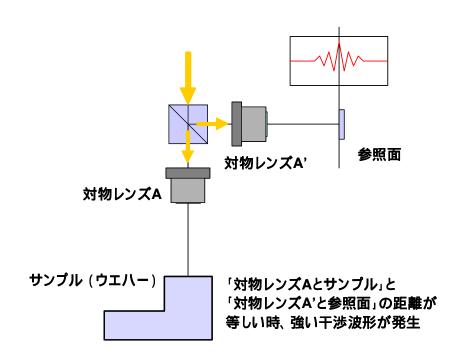

一般的な白色干渉の基本原理を図表 12-9 に示す[1]。白色干渉は、ビームスプリッターによって参照面と試料面に分割された光の光路長が一致した時、すなわちこの図では「対物レンズとサンプル」と「もう一つの対物レンズと参照面」の距離が等しい時に最も強い干渉波形が発生する。この原理より、上下方向に走査を行いそれに伴い発生した干渉信号の距離の差より、段差や突起物、また深さを計測するものである。

図表 12-8 コンフォーカル光学系の基本原理

資料提供:レーザーテック株式会社

図表 12-9 白色干渉の基本原理

資料提供:レーザーテック株式会社

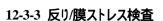

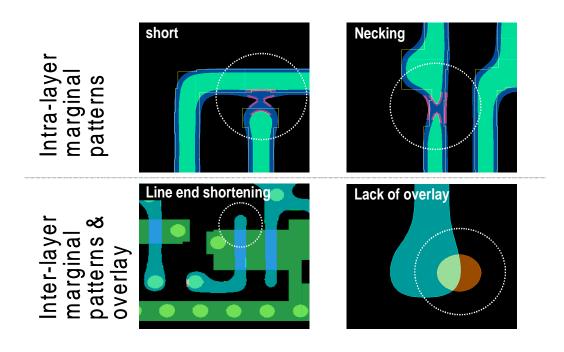

微細化の進展や eSiGe+ミリセックアニール等の新しいプロセスの導入にあたり、Non-visual Defects の一種であるストレスの検査に高い注目が集っている。一概にストレス検査といっても、歪技術に使用されるストレスライナー膜のように、故意に高いストレスをかけて設計通りにストレスがかかっている事を検査する場合と、アニール工程等で物理的にストレスが発生してしまうような、本来ストレスをかけたくない工程を検査する場合の、正反対の目的のための計測がある。

ITRS2007 年版 Yield Enhance の 1 ページ目には歩留まり低下の一例として、ストレス、Crack、Overlay がピックアップされているが(図表 12-8)、本来ストレスが発生しないプロセス設計において、高い膜ストレスがかかったために Crack 発生の一因となったり、ストレスによりウェーハに大きな反りが発生し Overlay Error を引き起こす様な事も、特定のレイヤーでは懸念されている。但し同ページに記載があるように、"必ずしも全ての欠陥がデバイス特性を変動させたり、集積回路の不良を引き起こすわけではないため、欠陥と歩留まりの関連付けは非常に重要である"との内容と同じく、ストレスの影響はレイヤーやデバイスによって全く異なるものとなる。そのため、ストレスの集中やバラツキを単純に欠陥と捉えるのではなく、ストレスを可視化し歩留まりへの影響を追求する事が非常に重要と思われる。

今までの膜ストレス検査は、パターン上では正確に測定できない事や、測定時間が十分に早くないために、Blanket ウェー八を使用し、X/Y 方向の一ラインや面内数十点を測定するのが主流であった。但し、この場合、Blanket ウェー八と(パターン付きの)プロダクションウェーハの挙動が大きく異なる問題があり、また測定点が十分でないため局所的なストレス集中やエッジ部分に向かい徐々にストレスが変化する現象等を捉える事が出来なかった。ITRS2007 年版 Metrology の Figure MET3(図表 12-9)には、Die 及び Wafer のストレスを測定する一つの手法として光干渉方式が記載されている。一方、光干渉を用いない測定方法として、表面の反射率が大きく異なった場合においても安定したデータ取得ができ、水平分解能(測定ポイント)が可変で解析/量産の双方に対応できる測定方法について、レーザーテック株式会社から紹介があった。

ストレスの計算方法は、プロセス前後の形状を比較しプロセスより発生する変形量を求め、以下の Stoney の式を使用し求められる。

$$_{film} = \frac{E_{Si} h_{Si}^2}{6(1 - v_{Si})t_{film}} k$$

$(m_{film}: 膜のストレス(応力)、<math>E_{Si}: Si$ 基板のヤング率、 $v_{Si}: Si$ 基板のポアソン比、 $h_{Si}: Si$ 基板の厚さ、 $t_{film}: 薄膜の厚さ、<math>k:$ 基板の曲率)

この場合、低い次数でフィッティング(形状の追従)を行うと、ストレスの分布やバラツキが把握できないこととなる。正確にストレスの分布を捉えるためには、プロダクションウェーハ面内において十分なポイント数を測定し、それを適切にデータ処理する必要がある。

図表 12-10 歩留まり低下の一例

| Area of Interest | Measurement<br>Method                                                               | Sensitivity M<br>Stress Strain |                | Measuremei<br>Area         | nt Sample<br>Thickness                                                                                                                        |  |  |

|------------------|-------------------------------------------------------------------------------------|--------------------------------|----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Transistor Level |                                                                                     |                                |                |                            |                                                                                                                                               |  |  |

| do               | - CBED                                                                              | 20 MPa                         | 0.02%          | 10-20nm                    | <100nm Destructive                                                                                                                            |  |  |

| SiGe SiGe        | - NBD                                                                               | 100 MPa                        | 0.1%           | ~10nm                      | <300nm Destructive                                                                                                                            |  |  |

|                  | - TERS                                                                              | 50 MPa                         | 0.05%          | <50nm                      | Destructive<br>Non-Destructive                                                                                                                |  |  |

| Micro-Area Level | - <u>Confocal</u> Rama<br>- XRD<br>- Photoreflectand                                | 10 MPa                         | 0.05%<br>0.01% | ~150nm<br>100um            | Non-Destructive                                                                                                                               |  |  |

|                  | Spectroscopy                                                                        | ***                            |                |                            | Handling Area of ITRS                                                                                                                         |  |  |

| Die              | <ul><li>Die level flatnes</li><li>Laser Interferor</li><li>Coherent Gradi</li></ul> | netry                          | g              |                            | Non-Destructive                                                                                                                               |  |  |

| Wafer            | - Laser<br>Interferometry<br>- Coherent                                             | 10 MPa                         | 0.0019         | % wafer                    | Non-Destructive                                                                                                                               |  |  |

|                  | - Conerent Gradient Sensing  * Stress – Strain relation : need to be clarified      |                                |                | CBED (Conve<br>NBD (Nano B | TERS (Tip Enhanced Raman Scattering) CBED (Convergent Beam Electron Diffraction) NBD (Nano Beam Electron Diffraction) XRD (X-ray Diffraction) |  |  |

図表 12-11 ITRS2007 Metrology の Figure MET3 抜粋

### 12-5 2008 年度のテーマとしてエコの観点からの計測の位置づけ

従来からの計測とアリング活動のデータベースを基に、2008 年度の STRJ Workshop のテーマとして掲げられたエコについて、計測のあり方を考察した。本内容は、2009 STRJ Workshop で発表したスライド原稿を基に解説したものである。まず、計測におけるエコについて、考えると、以下の様に計測の直接的、間接的エコが考えられる。

#### 直接的

・計測機の製造にともなうエネルギーコスト、ランニングコストの抑制(ベンダー側の対応)

#### 間接的

・計測サンプリングの適正化による歩留まり(欠陥歩留まり、特性歩留まり)の向上 減耗ウェーハ、チップの抑制

そのための手法として、

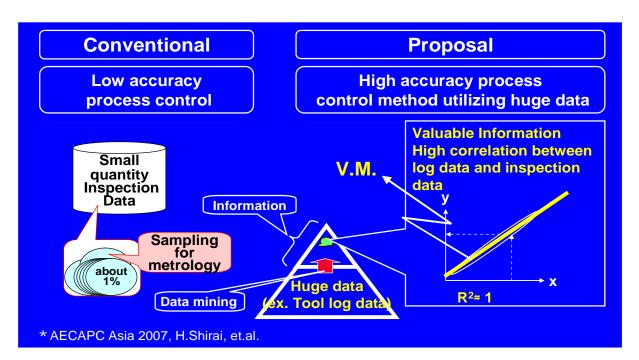

- 1.最適サンプリングによる Parametric な制御精度(for APC)の向上 特性歩留まりの向上。Process Compact Model の活用による feed forward 制御の活用(複数工程間連携の APC)

- 2 . 装置起因の Excursion の抑制による歩留まり向上と、計測サンプリングの抑制(FDC) 装置情報(log)とテスター情報 and/or Actual Metrology 情報との相関

- 3 . Virtual metrology の活用 装置情報(センサー情報 and/or log)と Actual metrology との相関探索 最終的にプロセス装置へ feedback

- 4 . Simulation 予測による製造の Systematic error(defects: hot spot)の抑制による歩留まり向上と、計測サンプリングの抑制

- 5. 欠陥 review の重み付け sampling(filtering)による効率化\*計測情報の活かし方(特性歩留まり、欠陥歩留まり)が重要!

計測における直接的エネルギー消費は、計測機を製造するすべての過程において消費されたエネルギーであり、ランニングによるエネルギー消費に関しては、計測機の運用に伴う全エネルギーである。計測機は半導体のプロセス装置に比べ、直接的な製造に関わるわけではなく、そのオペレーションにおいてもエネルギー消費は非常に小さいものである。したがって、計測機のエコを半導体産業の中で捉えた場合、その中における改善自体の寄与も非常に小さいことは自明である。しかしながら、上記に掲げた間接的なエネルギー消費の抑制を考えた場合は、直接的な抑制に比べはるかに大きく、意味のあることだと考えられる。つまり、最適な計測手法によって、ロット全体の品質を正確に把握することによって、欠陥歩留まり、特性歩留まりを抑制する効果である。また最適な計測手法とは、目的以上に不必要な計測機器を必要としない、あるいは使用しない、必要最低限の運用であるわけなので、ある意味でエコそのものであろう。

1項の最適サンプリングによる Parametric な制御精度(for APC)の向上とは、各プロセス装置のレシピには、プロセスを制御するパラメータが記述されており、そのパラメータが適切であれば、プロセス後の出来上がりを表現する計測結果は、プロセスの出来上がり目標値に近いことが期待されるわけである。この制御パラメータを正確に予測するために必要なことは 2 つある。一つは、プロセスの制御レベル(制御の最小単位)を決めて、その制御パラメータを正確に予測することであり(予測手法)、2 つ目はその予測の基となる、過去のロットが正確に計測されていることである(ロットの状態、例えば、プロセス管理すべき項目の平均値と分布等の正確な計測)。ここで言うプロセス制御は、個々のプロセスの出来上がりを改善するための制御であり、結果プロセス全体のバラツキが抑制され、特性バラツキも小さくなるというものである。Process Compact Model を用いたプロセス制御は、デバイスの電気特性が各プロセスの出来上がりの計測値を用いた式(関数、モデル)で表現される場合、前工程の出来上がりの目標値からのずれによる特性の変動を後工程で補正するためのモデル式として活用する

ものである。

2 項の装置起因の Excursion の抑制による歩留まり向上と、計測サンプリングの抑制(FDC)とは、装置のセンサー情報を含むログデータを監視し、計測サンプリングをすり抜けてしまう、異常な分布を早期に検知し、対処することにより、歩留まりの低下要因となる不良の拡大を抑えることである。(サンプリングの補間あるいは補完技術)一般的にはあまり知られていないが、ITRS の計測では、integrated metrology として装置内のセンサーも広義に包含されており、これらの情報のハンドリングも非常に重要に成ってきている事に留意が必要である。

3項のVirtual metrologyの活用とは、実際の計測値と相関のある情報を、装置のセンサー情報を含む装置口グから導き出し、実際の出来上がり(計測値)を予測したり、計測サンプリングと併せて、非計測ウェーハの計測値を推定し、ロット全体を把握する行為であり、実際の計測に変わりうる計測として注目されている技術である。(サンプリングの補間あるいは補完技術)

4項の Simulation 予測による製造の Systematic error(defects: hot spot)の抑制による歩留まり向上と、計測サンプリングの抑制とは、通常の計測では不可能な、チップ内の全パターンあるいは、全領域の出来上がりを推定する手法である。代表例としては、光学シミュレーションによるリソグラフィープロセスのチップ内全パターンのレジスト像の出来上がり状態の予測がある。(実計測を伴わない出来上がりの予測および補正技術)

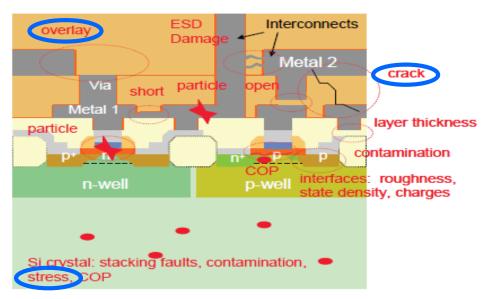

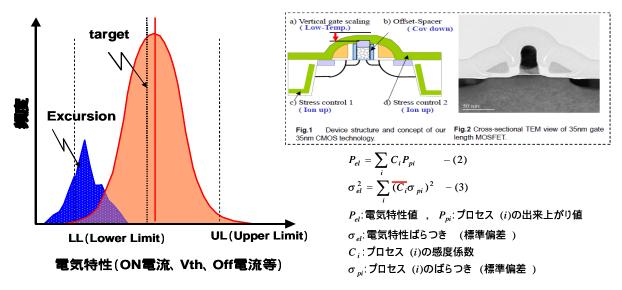

まず、計測サンプリングの重要性を理解する上でプロセスバラツキ、特性バラツキについてレビューをしてみる。図表 12-12 に示したのは、あるプロセス管理項目の全チップ変動の分解図である。全チップ変動というのは、処理した全てのロット、全てのウェーハの中のチップの出来上がりのバラツキ度合いである。もちろん実際には、複数の時期に、それぞれ所定の時間内の複数のロットの全チップ変動を定義して、その時期的な平均をとって全チップ変動の期待値(上付きバーで表記)とし、母集団足る全チップ変動としているわけである。

デバイスのスケーリングはプロセスバラツキのスケーリングであり、同時に計測精度のスケーリングである。枚葉制御も32 nm node以降critical layerで必然性になると予想される。Criticalで無い場合。あるいはcriticalの度合い、およびプロセス変動の時間軸の変化に対応したsamplingが効率的

図表 12-12 計測のサンプリングの説明図

図中では各変動を分散の関係式で表現しているが、分散とは標準偏差( )の 2 乗であり、統計的には、正規分布に従う独立な分布の中から取り出したものを足し引きした分布の分散は個々の分散の和として表現され

る。例えば、図表 12-12 がある ASIC デバイスのゲートの寸法と仮定すれば、あるロットの平均線幅を L<sub>(lot)</sub>、そのロット内の、ウェーハの平均線幅の標準偏差を inter-wafer とすれば、ウェーハの平均線幅は、L<sub>(lot)</sub>を中心に(正規)分布をしているわけであり、L<sub>(lot)</sub>±3 inter-wafer の中に 99.75%が収まることが期待される。さらに、ウェーハ内のチップの平均線幅の標準偏差を inter-chip とすれば、そのロット内のチップの平均線幅は L<sub>(lot)</sub>±3( <sup>2</sup> inter-wafer + <sup>2</sup> inter-chip) <sup>1/2</sup> の中に 99.75%が収まる事になる。このようにして全てのロットに関して全チップの分布を考えると、全チップ変動は、( <sup>2</sup> inter-lot + <sup>2</sup> inter-wafer + <sup>2</sup> inter-chip) となり、L<sub>(all)</sub>±3( <sup>2</sup> inter-lot + <sup>2</sup> inter-wafer + <sup>2</sup> inter-chip) <sup>1/2</sup> の中にチップ平均の 99.75%が収まるという事になる。ちなみに、ウェーハプロセスの分布にはシステマティックな分布が内在し、正規分布とは言えない場合が多いが、中心極限定理より、システマティックな成分が重畳されれば、その平均あるいは和は正規分布に近づくことが知られている。このため正規分布をマクロな挙動に対して近似的に利用してチップ分布の信頼限界を議論しているわけである。

ここで重要なことは、チップの全変動がロット間変動、ウェーハ間変動、チップ間変動で表現されるということである。そして、その統計量としての平均値や、分布を表現する標準偏差等を正確に求めること、すなわち、最適サンプリングは、最終的なチップの特性歩留まりを向上させる上で非常に重要なことであることが判る。

ここで、プロセス設計(特性分布を基にしたプロセスの管理・制御設計)について考えてみる。図表 12-13 に示したように、製造プロセスで管理、制御するプロセスパラメータの範囲は基本的には非常に小さいのが常である。特性変動は、プロセス制御が狭い製造プロセスにおいては、リニアに近似することができよう。すると、特性変動は、一次近似としては、プロセス変動とその特性に及ぼす感度係数の積の線形和で表現され(図中式 2)、同様に分散についても式 3 で表現される。

\*Tr特性歩留まり100%であるためには、少なくとも特性ばらつきを規格値内で制御する必要がある。(ここではランダム欠陥は 考慮しない) 例えば、Cp = Cpk = 1.00であれば、歩留まり99.75%に相当。

\*Tr特性はリニアスケールで正規分布とは限らないが、例えばCpk値として目標設定を行う。 Cp=6σ/(UL-LL), Cpk=3σ/min{UL-bias, bias-LL}

\*Tr特性は、ゲート長、サイドウォール幅、エクステンション、HALO、アニール等のばらつきの影響を受ける。ある狭い制御範囲の中では、Tr特性は、これらのプロセス計測量の線形和で表現でき、そのバラツキは、互いに独立で上式(1)で表現できる。

\*感度解析からCiを求め、piを実績から算出し、電気特性をどこまで押さえ込めるか検討を行う。

\*Tr特性のばらつきとしてはチップ内ばらつきとチップ間ばらつきがあり、APCで議論するのは主に全チップ間ばらつきである。

\*AECはexcursionの抑制を主なる目的としている。

#### 図表 12-13 特性バラツキとプロセスバラツキの関係

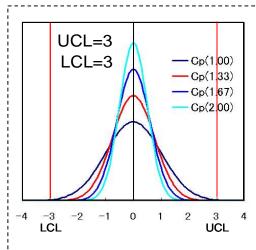

製造ラインで重要なのは欠陥による歩留まり低下の抑制と、特性分布から外れることによる特性歩留まりの 劣化の抑制にある。後者に関しては、所定の特性変動(複数: Ion, Ioff, Vth, etc.)に押さえ込むために、特性と

プロセスの関係式、および、個々のプロセス装置の加工精度、管理(運用&制御)精度より、個々のプロセス規 格値が決定される。(この一連の作業がプロセス設計である) そしてこの規格値に対して、如何にプロセスの出 来上がり平均値を目標に近づけ、かつ、プロセスの出来上がりの分布を小さくするかが、特性歩留まりに直結 する重要な技術課題となる。このためのプロセスの精度の評価尺度として工程能力 Cp, Cpk が定義されている。 Cp, Cpk の説明は、図表 12-14 に示したが、工程能力 Cp, Cpk を用いて、確率的な歩留まりを表現できることが 特徴である。 特性とプロセスとの関係式は、プロセスが fix した後に実験計画法に基づき感度解析を行うことで、 必要とされる線形式まで取得することができる。

また、TCAD の calibration の精度を上げることで、高次のモデル式を形成することも可能な状況になりつつ ある。TCAD を上手〈活用することで、 最終的な特性歩留まりを正確に予測したり、 後述する feed forward な制 御に応用することで歩留まりの改善を図るといった試みもなされようとしている。

(a) 分布の中心が目標値の場合

(b) 分布の中心が 1 ずれている場合

図表 12-14 工程能力 Cp, Cpk の説明

$$C_p = \frac{Min($$

上限規格値 $UCL-$ 目標値,目標値-下限規格値 $LCL)$   $= \frac{規格幅}{3 \times J}$ ロセスバラツキ $(= 標準偏差\sigma)$

$$C_{pk} = \frac{Min(上限規格値UCL - 平均値, 平均値 - 下限規格値LCL)}{3 \times プロセスバラツキ(=標準偏差 $\sigma$$$

- \* 正規分布を仮定すれば、工程能力 Cp, Cpk を用いて、確率的な歩留まりを表現できるこ とが特徴である。

- \* 正規分布の確率 P(x)とし、出来上がリー から  $x_0$ までの比率  $P(x<x_0)$ は、以下の式で表現 される。

$$P(x < x_o) = \int_{-\infty}^{x_o} P(x) dx = \int_{-\infty}^{x_o} \frac{1}{\sqrt{2\pi}\sigma} e^{-\frac{(x-\mu)^2}{2\sigma}} dx$$

x:セス出来上がり x<sub>o</sub>: 所定のプロセスの出来上がり

$\mu$ : プロセスの出来上がりの平均値、 $\sigma$ : プロセスの出来上がりの標準偏差

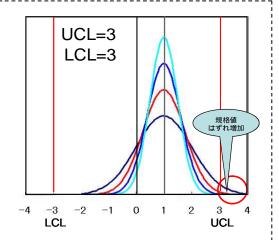

### 12-14 最適サンプリングによる Parametric な制御精度(for APC)の向上

それでは、具体的に1項の最適サンプリングによる Parametric な制御精度(for APC)の向上についての計測サンプリングについて詳細に説明を行ってゆく。図表 12-15 に示したのは、ゲートのエッチングプロセスと、エッチング後のゲート線幅をより目標値に近づけるための APC の制御フローである。ここでは、ロット単位で制御していると仮定する。つまり、ロット毎に共通のエッチング時間を予測し、エッチングを実行するということである。ここでの APC には2 つの機能があり、まず、リソグラフィー工程におけるレジスト寸法を CD-SEM 等で計測し、その計測結果に基づき、現時点で最も適切なエッチングレートを予測し、両者から最適なエッチング時間を計算し、エッチング装置に指示する行為と、エッチングした結果を CD-SEM 等で計測を行い、その計測の平均値と目標値との乖離から、最新のエッチングレートを更新する行為である。前者を feed forward 制御と呼び、後者を feed back 制御と呼んでいる。この APC の機能は従来の SPC に比べて、モデル式に基づく制御が働くことにより、確実にバラツキの分布が改善されることが期待できる手法であり、広く製造ラインで適用されている。

図表 12-15 APC の説明(feedback, feed forward 制御)

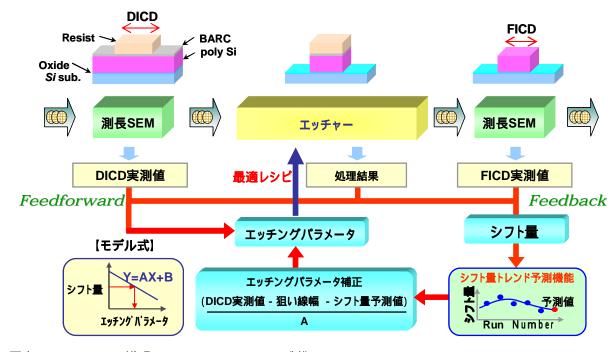

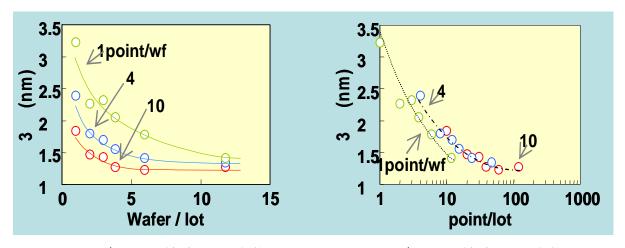

この APC の仕組みの中では、ゲートのレジストの寸法とエッチン後の寸法が、必要な情報として取り込まれているわけであるが、この際の計測のサンプリングが不適切であるとどのような事が生じるのか考えてみる。図表 12-16 (a) に示したのは、計測ウェーハ枚数に対する APC 制御後のロット間バラツキを示している。図中のパラメータはウェーハ内の計測ポイント数である。この図が示すことは、ウェーハ枚数の増加によってロット間バラツキが改善する、ウェーハ内計測数の増加によってロット間バラツキが改善するということである。右図は、横軸にトータルの計測ポイント数を取ったもので、log スケールで表現をしている。これからも、計測ポイント数の増加によってロット間バラツキが向上していることが同様に伺える。一方、ロット内ウェーハ 4 ポイント計測と、ウェーハ 10 ポイント計測ではほぼ同じ傾向の曲線に載っているが、ウェーハ 1 枚ではその傾向がシフトしていることがわかる。

本図からは、ウェーハ内 1 ポイント計測でウェーハ枚数を増加させた方が APC 制御後のロット間変動としては一番経済的だということになるように見えるが、もう一つ大切な評価尺度として、ロット全体の平均値がウェーハ内 1 ポイント計測で代表できているかどうかということである。 つまりこれに乖離があれば、ロット間変動が小さくなってもロットの平均値と目標値との間に乖離が存在することになってしまうからである。 (図表 12-14 の(b)参

照)特にウェー八間、あるいはウェー八内にシステマティック分布が内在する場合、正規乱数的な分布を仮定し た場合のように、測定点数だけではロットの真の平均値を正確に推定できない。ちなみに、正規乱数の場合は、 ロット平均の推定誤差は±3( <sup>2</sup> inter-wafer /N\_wafer + <sup>2</sup> inter-chip /N\_chip) <sup>1/2</sup> @両側 99.5%信頼区間であるが(N\_wafer) N chip は、それぞれ計測ウェーは枚数、計測チップ数である)、実際のロットの真の平均値は不十分な計測情報 から推定することはできないので注意が必要である。つまり、プロセス処理環境・状態に関連して測定ウェーハ 番号あるいは、測定ウェーハの場所の依存性が顕在化するからである。この様なことを考慮して、図表 12-16 の縦軸の尺度として、工程能力 Cpk(目標値と出来上がり平均値との乖離を考慮)で計測ポイントとの最適化を 測ることが本来重要である。今回はあくまでも特定の事例での説明、解釈であるのでこの点は留意されたい。 今回ロット間変動を行った場合のサンプリングの説明を行ったが、先に述べたプロセス設計においてプロセス の規格値が決まることで、式(1)の各変動要因の目標値も決まり、それに対応して APC の制御レベル(ロット単 位制御、ウェーハ枚葉制御、ウェーハ内制御)が決まり、同時に最適なサンプリングプランが必要になるというこ とである。

(a) ロット間バラツキ vs 計測ウェーハ毎数 図表 12-16 計測サンプリングと APC の予測精度との関係

(b) ロット間バラツキ vs 計測ウェーハ毎数

次に Process Compact Model をベースにした APC 制御について触れる。APC は基本的に所定のプロセスに 対して制御を行い、プロセスバラツキを改善するシステム(機能)であるが、図らずしも期待したプロセス分布か ら外れてしまうケースの対応や、積極的に特性バラツキを低減したい状況も想定される。そのような場合、プロ セスの出来上がりと特性との関係式(モデル)が明確に定義できている場合、所定のプロセスにおける分布の端、 あるいは分布はずれを後工程で修正するといったことも可能性が有り得る。

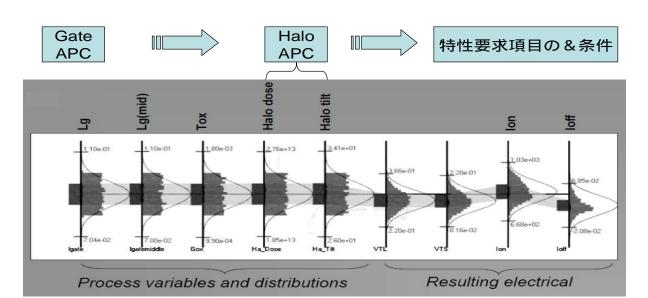

そのためには、図表 12-17 に示すような特性とプロセスとの関係式を正確に構築しておく必要がある。このよ うなモデル式を実験で導出するのは、実験規模や実験誤差を考えると非常に困難であるため、TCAD の calibration を正確に行い、その TCAD を用いたモデル式を利用するのが良いと考えられている。このように APC、PCM を用いてプロセスのバラツキを抑制し、特性分布を向上させ特性歩留まりを向上することが今後 益々重要であり、そのためにも正確な計測情報を取得するための計測サンプリングが重要となることが判る。

図表 12-17 Process Compact Model によるプロセス出来上がりと特性との関係

提供 Synopsis

#### 12-5-2 装置起因の Excursion の抑制による歩留まり向上

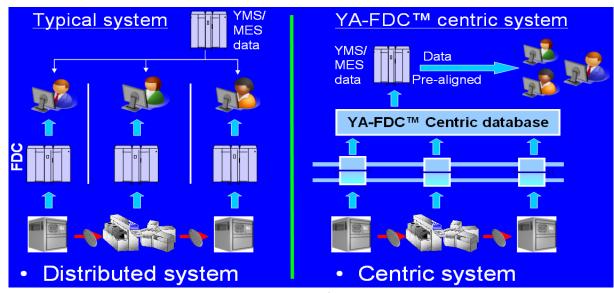

装置起因の excursion とは、プロセス装置が何らかの原因で非定常的な挙動をすることによって、通常のプロセス出来上がり分布から大きく外れた分布(excursion)をすることを指している。(図表 12-13 参照)これにより特性 歩留まりの劣化や、不良に繋がることが多い。したがってこの excursion を早期に捕らえて対応することが非常に重要な技術となっている。一般的には、製造ラインで FDC(Fault Detection and Classification)というシステムで装置状態を監視、異常の分別、分析して対応するものであるが、FDC システムと、エンジニアの役割分担については、各社まちまちのところがある。ここで言う fault とは、欠陥や不良につながる装置上の制御因子等の変動と解釈するとよい。図表 12-18[2]の左側は、従来の FDC の位置づけであり、エンジニアが、FDC からのfault 検知の alarm を見て判断をしたり、FDC の装置ログデータと YMS(Yield Management System)やMES(Manufacturing Execution System)内のデータを活用して、解析を行い、fault 検知するための条件を検討するといった構図を示している。一方、右図は、装置からのデータを一元管理し、歩留まりとの関係の強い装置パラメータを抽出し、特性や歩留まりの予測まで行うための FDC の提案である。

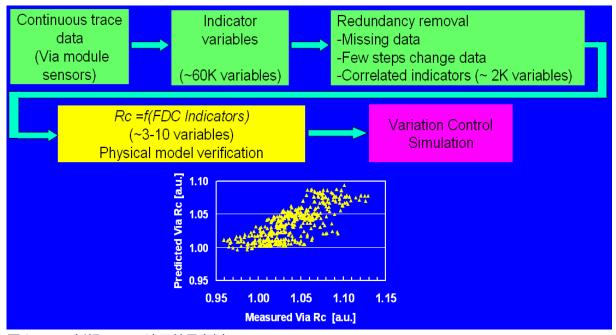

図表 12-18 従来の FDC と歩留まりや特性との相関モデルをベースとした FDC のシステム比較

この新規 FDC システムを導入した効果が図表 12-19 に示すように報告されている[2]。本事例では、バックエンドのビア形成工程(エッチング)において、エッチングチャンバーに取り付けられているセンサーの情報(60K変数)を基に、冗長な情報の除去、欠損データの補間、データの修正、相関データの抽出を経て、コンタクト抵抗の出来栄えを相関度の高い3~10の変数でモデル化を行い予測するものである。FDC システムでは処理した結果の情報を基に予測が出来るわけであるが、一般的にはモデル化因子は uncontrollable な場合がほとんどである。したがって、該当するプロセス装置に対して何らかの対処をしなければならないことになる。もしモデル化因子がプロセス装置の外部制御可能なパラメータであれば、APC でハンドリングすることも可能であり、12-5-3 章で述べる Virtual metrology としてプロセスを安定化させることが可能となるわけである。本ケースにおいては、例えば、エッチング後の出来上がり寸法が同じであるにも関わらず、コンタクト抵抗が異なることを説明するモデルだと捉えられる。このように FDC により、装置起因の異常の発生を早期に捕捉し、対応することで被害の拡大と共に、不良となる確率の高いロットあるいはウェーハの適切な処理(scrap 等)により損失の拡大を食い止めると同時に、顧客対応として適切なバックアップロットのインプットの判断も可能になる利点がある。

図表 12-19 新規 FDC の適用効果事例

# 12-5-3 Virtual metrology の活用

最適な計測サンプリング、あるいは検査サンプリングで特性歩留まり、欠陥歩留まりを最大化する計測の効果をエコとして議論をしてきたが、実際の計測をせずに、あるいは実際の計測と併せて、非計測ウェーハあるいはロットの計測を推定できれば、計測コストを抑えられると同時に歩留まりをさらに改善できる可能性がある。12-5-2 章の FDC でも触れたが、装置のセンサーデータや、制御データ、環境データ等を含む装置ログデータから実際の計測データとの強い相関が抽出できれば、virtual な metrology が成立すると考えられる。そのために重要なことは如何に計測と相関の強いデータを抽出し、モデル式を構築できるかに掛かっている。この点では先の FDC と同様な技術が必要とされる。

図表 12-20 データマイニングによる Virtual metrology の提案

図表 12-20 に示したのは、膨大なデータから意味のあるデータ(情報と呼ぶ)を取り出す手法としてデータマイングを例に示している。この情報の中から高い寄与率で表現できるモデル式を構築できれば良いわけである。一般的には、パラメータ変数を多数とれば寄与率は高くなるため、自由度調整済み寄与率で最適なパラメータ数を決定する。

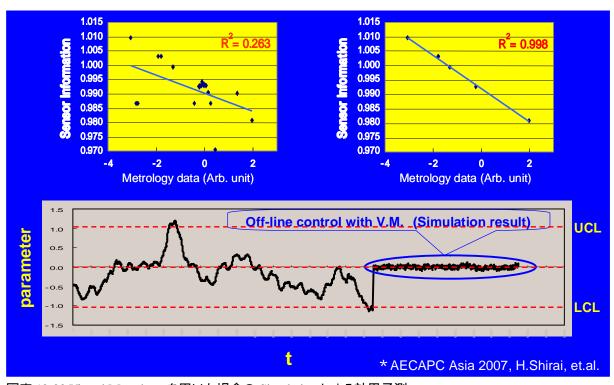

実際問題にデータマイングを行う場合、相関をとるためにデータの領域(図中 Parameter size)が定義されるが、この中にはバックグラウンド変動や、異常な値が含まれる場合が多く、有効なデータの抽出の妨げとなる。図表 12-21 に示したのは、これを回避するための手法の提案として、Parameter size を複数のサイズ領域に分割し、分割した size 毎にデータマイニングを行うものである。これにより、従来のデータマイニングより有効な情報を抽出する確率が向上したというものである[3]。

図表 12-21 Virtual Metrology のための新規データマイング手法の提案

図表 12-22 に示したのは、従来のデータマイニングと新規手法によるデータマイニングの比較である。右図が新手法によって抽出された計測データと非常に強い相関(寄与率  $R^2$ =0.998)を示すパラメータであり、従来手法で行った場合は、寄与率が  $R^2$ =0.263 であるから抽出できていないことが判る。図表 12-22 の下段に示したグラフは、計測データと相関のあるパラメータのデータを計測として代用し、それを APC(feed back 制御)として適用した際の効果のシミュレーションである。

一方 Virtual metrology の大きな問題点は、データ抽出方法が優れていても、膨大なデータの中に意味のある情報がそもそも存在しなければ Virtual metrology は成立しないということである。したがって、プロセス装置に求められる事として、センサーデータ、制御データ、環境データ等を網羅してオンラインで提供する仕組みと、Virtual Metrology の可能性を意識した、データの出力フォーマットを定義することである。プロセス装置は完全ではなく、その不完全さを如何に捕捉して、一時的に Virtual metrology で出来上がりの予測しうるかは、微細化のトレンドに迅速に対応するために必要不可欠なことだと考えられる。そしてプロセス装置の不完全さが捕捉されれば、最終的にはプロセス装置にフィードバックして内的制御が行われる事が期待できるわけでもある。このように膨大なデータから価値のある情報を抽出する技術は今後益々重要になってくるものと考えられる。

図表 12-22 Virtual Metrology を用いた場合の Simulation による効果予測

# 12-5-4 Simulation 予測による製造の Systematic error(defects: hot spot)の抑制による歩留まり向上と、計測サンプリングの抑制

製造ラインにおける計測は基本的にはサンプリングであるため、問題にしているのは、サンプリングの結果としての平均値や分布(ばらつき;標準偏差、レンジ等々)である。そしてそれらは、母集団の平均値、分布を所定の信頼限界で推定したいと期待しているわけである。サンプリングに関しては、正規分布することを前提にすれば問題はないが、現状の歩留まりを決定付ける大きな要因としてのシステマティック欠陥に関しては、正規分布前提のサンプリングの概念は適用できない。また、製造ラインにおいてサンプリングでシステマティック欠陥を定常的に計測すること自体非効率な話である(計測数が膨大になるため)。したがって、システマティック欠

陥を製造ラインのプロセス以前に抑制する技術が必要である。前述のプロセス変動の説明は、全チップ変動 (チップの平均的な出来上がりの変動)として、ロット間変動、ウェーハ間変動、チップ間変動(ウェーハ内分布) を用いて説明を行ってきたが、チップ内変動では、システマティック要因の寄与が大きい事や、チップの特性 を表現する観点から、全チップ変動とは分けて議論する。

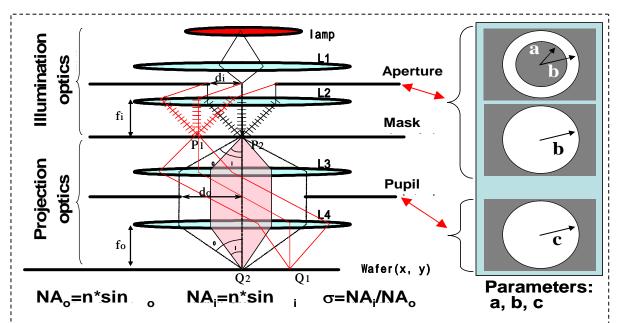

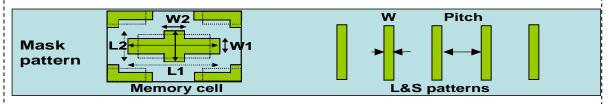

チップ内変動の代表は、パターン間変動であり、設計データ(GDS)上で同じ寸法で記述されているのにも関わらず、露光装置の照明、投影光学系を経て設計データ(マスクデータ)がウェーハ上で変換され、寸法あるいはパターン形状が設計データと乖離する現象がある。これは近接効果と呼ばれ、光の干渉性による光学原理に基づく不可避な現象である。このため、その補正として光近接効果補正(OPC:Optical proximity Correction)という技術が開発され、露光装置の光学系を通して受ける変化を、マスクパターンに修正を行い、ウェーハ上に転写されたレジストパターンとして設計データになるようにするものである。これにより、レジストの出来上がりのパターン間変動を大きく抑制するが可能となっている。現在では、エッチングプロセスによるパターン環境変動も取り込んで、OPC と併せてマスクパターン補正されている状況である。

従来の OPC の処理フローは、図表 12-23 に示すように光学的にデバイスを代表するであろうと考えられる critical なパターン群(設計図形の確定したメモリーセル群、ランダムパターンを代表する複数線幅のスルーピッチパターン群等々)を用い、露光量変動やフォーカス変動といったリソグラフィーのプロセスマージンを考慮した光学条件の最適化が行われていた。そして、この代表パターンによって最適化された光学条件で設計パターン全面に渡る OPC(Optical Proximity Correction: 光近接効果補正)処理がなされていた。この OPC という技術は論理的に優れた技術であるが、実際の運用にあたっては以下の大きなリスクを抱えていた。

- 1. 光学条件の最適化は、事前に critical だと想定されたパターンでのみ実施され、**漏れがある可能性**がある。 (もともと、全パターンで光学条件を最適化する必然性は無く、critical pattern を代表させて、光学条件の最適化を行うこと自体は理に適った手法である)

- 2. OPC の処理時間は、形状最適化すべきパラメータ数(パターンエッジの分割数)に依存するために、コンピュータの処理能力によってパターン分割エッジ数が制限される。このため、荒い分割の代表点で最適化された中に**マージンが減少する箇所が存在する可能性**がある。

- 3.また、たとえ分割サイズが論理的に有効な範囲で小さくできたとしても、マスク描画の際の EB 露光用データ 処理時間や、EB パターン描画精度、EB パターン描画時間、さらにはマスクの検査精度の制約も大きく、マスク の出来上がりの検証や保証もできない。

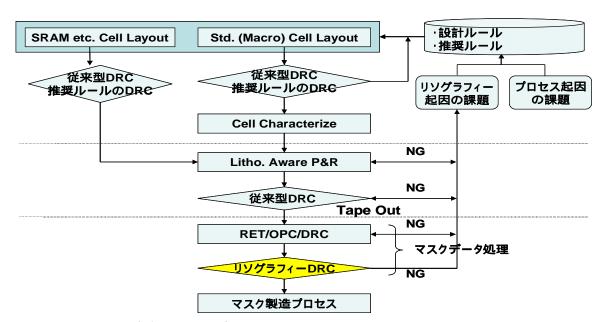

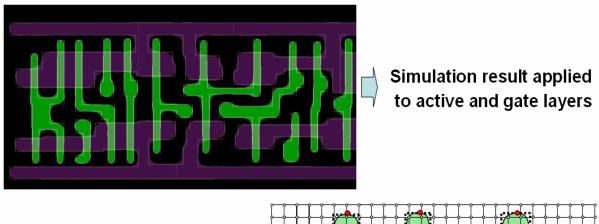

このようなリスクは理解されつつも、従来の設計データからマスク製造に至る設計データ処理の流れには、OPC のリスクの検証はなかった。現在では、リソグラフィーのシミュレーション技術の高速化により、図表 12-25 に示すように、黄色の背景色で塗られたリソグラフィーDRC(Design Rule Check)の工程が導入された。これにより、従来の手法で行われたOPCのリスク要因がHot Spot(危険箇所、リスク要因、致命的欠陥等)として検知され解消されるようになった。リソグラフィーDRC で行っている作業は、図表 12-25 に示すように、従来、赤丸()をOPC の分割エッジの代表点として、最適露光量&最適フォーカス条件で設計データに近づける作業を行っていたが、リソグラフィーDRC では、全グリッドにおいてプロセスのコーナー条件(最大 or 最小露光量)&(最大 or 最小デフォーカス)において2次元形状を計算し、さまざまな不良箇所の抽出を行っている。これによって従来のOPC 手法のリスクが洗い出されるわけである。

# (a) Optics of scanner

a, b, c は光学系最適化パラメータ例(近年照明系は grid ベースの最適化がなされる)

## (b) Floating parameters for OPC

形状の固定したメモリーセル図形(左図)、ランダムパターンの代表として Critical な寸法 W のピッチ振りパターン群(右図)に対して、形状パラメータ(光学像計算の際の floating parameter: W1, W2, L1, L2 等)と、計算ポイントを定義し、設計規格値を満たす defocus および露光量マージンが最も大きな光学条件を求める最適化を行う。図(b)メモリーセル内点線は設計形状

図表 12-23 OPC および最適光学条件の floating parameter の説明

図表 12-24 ロジックデバイスの設計データ作成からマスク作成までのフロー

\* 黄色がリソグラフィーシミュレーション

DRC: Design Rule Check(パターンレイアウトの設計ルールの整合性チェック) P&R: Place and Router(セルの配置と配線:チップ全体のパターンレイアウト生成)

RET: Resolution Enhancement Technology(解像度向上技術)

Conventional sampling for OPC (●)and grid- base simulation for hot spot detection (○)

図表 12-25 グリッドベースのリソグラフィーシミュレーションによるパターン形状検証

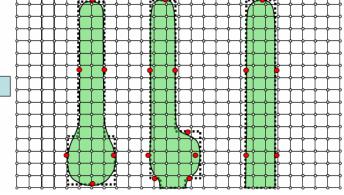

リソグラフィーDRC による Hot Spot の検出事例を図表 12-25 に示した。defocus と露光量の変動のコーナー条件におけるパターンとパターンのショート(a)、パターンの局所細り(b)、ライン端の後退(c:活性領域を考慮)、前工程パターンとのコンタクト面積の減少(d:位置ズレの規格値考慮)が、効率よく抽出されていることが判る。リソグラフィーDRC の技術によって intra-chip の CD(Critical Dimension)制御と Hot Spot の抑制が可能となったわけである。

このように、歩留まりの根源である Hot Spot をデバイスプロセスのより上流側から、実際の計測技術を用いずシミュレーションによって全チップ領域に渡って食い止めていく事が可能となり、リソグラフィーに関連したシステマティック不良の大半が解消されるに至っている。リソグラフィーDRC によって検出された Hot Spot の処理はその状況に応じて、修正のフィードバックが異なる。図表 12-24(右側)は、その修正のフローを示したものであるが、このように設計パターンを含めてその対応を取る手法は Design for Manufacturing(DFM)と呼ばれ今日広く適用されている技術となっている。Hot Spot は、その状況において簡便な修正が掛けられるものと、設計変更を伴うものが存在する。後者に関しては、経験として蓄積され、以降のデザインルールにフィードバックがなされて習熟してゆくことによって、発生確率を 0 に近づける努力がなされている。

リソグラフィーDRC に代表されるモデルによる検証は計測のサンプリングでは不可能な領域をカバーし、製造前段階で Hot Spot を抑止できるという非常に大きな効果をもたらす。これによって歩留まりへの貢献と同時に、製造ラインにおける計測のサンプリングの妥当性(システマティックな影響の排除によるサンプリング付加の軽減)が意味づけられることになる。

図表 12-26 シミュレーションによる最大想定プロセス変動時(露光量、デフォーカス、重ね合わせズレ、マスクの線幅(mean to target))の際の欠陥予測

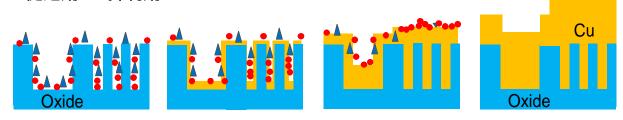

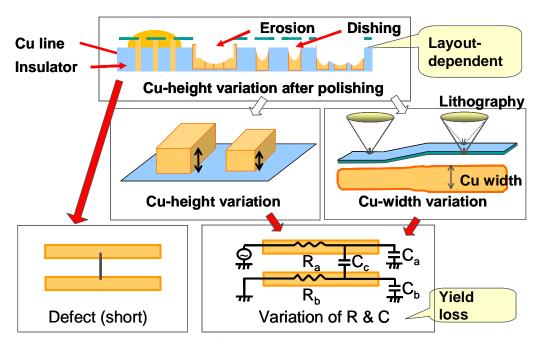

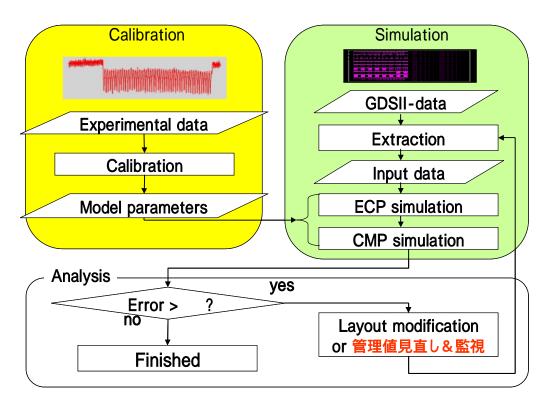

他方、フォトリソグラフィープロセスにおけるリソグラフィーDRC と同様のことが、ECP(Electrical Chemical Plating)、CMP(Chemical Mechanical Polishing)プロセスでも最近行われるようになっている。これは、簡便なメッ

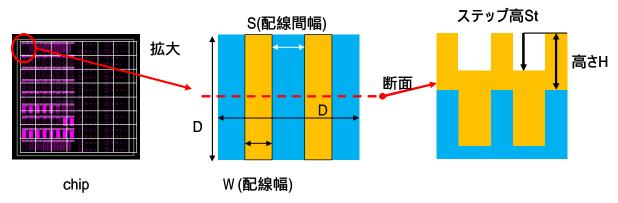

キ積層(堆積)モデル、エッチングモデルを用い、出来上がりのウェーハ表面(チップ表面)の段差状況を予測するものである。ECP、CMPのプロセスの最適化自体は、TEG等を使用して実験的に行われるが、実際の製品のレイアウト依存で発生しうる Hot Spot(残渣、erosion、ローカル段差 リソグラフィーDRC へのインプット)に関しては、事前に予測することは困難である。ここで ECP、CMP のシミュレーションについて補足を行っておく。ECP は電解メッキであり、図表 12-27 に示すようにメッキ液の中には、Cu イオンの他に促進剤、抑制剤が含まれており、促進材は、表面への吸着力が強く側壁の比率が大きい微細な溝で密度が高くなるため Cu が埋め込まれやすい特徴がある。 ECP のモデルを厳密に行うことは容易ではないことと、実用的なレベルで簡便な手法として図表 12-28 に示すような MIT モデルがある[4]。ここで考慮されているのは、対象としている D×Dの領域のスペース幅(S)と配線幅(W)のみである。複雑なパターンでは近似的に等価なライン&スペースパターンに置き換える等を行う。これを実験的に行って実験によるフィッティングのモデル式を作成するものである。MIT はシンプルであるが精度面で問題があるために Luo's model[5]や Refined Luo's model[6]などが提案されている。

# ●促進剤 ▲ 抑制剤

図表 12-27 ECP の説明図

# **MIT Model**

St =  $a_sW + b_sS + c_sW + d_sW^2 + e_sW^{3*}S + Const_s$ H =  $a_AW + b_AS + C_AS^2 + d_AS^3 + e_AW^*S + Const_A$

\*物理化学モデルの考慮無し

図表 12-28 ECP の実験フィッティングによるモデル式

CMPのシミュレーションに関しても、ECP同様に簡易的な実験とのフィッティングモデルによる段差形状推定が行われている[6]。 CMP のシミュレーションでは、ECP 後のチップ内の段差をメッシュ単位で計算する。

ECP、CMP のシミュレーションを行うことで、製品に対応した、Hot Spot あるいはその候補を抽出することが可

能となり、従来のモニターパターンによるプロセス管理に加えて、管理ポイントを追加して監視したり、事前に発生しうる現象に対応してプロセスの管理目標値や、管理規格を厳しくて Hot Spot の発生を抑制することも行われている。大きなリスクのある Hot Spot に関しては、必要に応じて設計データに変更をかけることも可能である。図表 12-29 に CMP 後の段差不良リスク要因を示し、図表 12-30 にシミュレーションの運用フローを示した。図表 12-29 では、リソグラフィーのフォーカスバジェットに影響を及ぼすローカル段差の予測も示されているが、Hot Spot は、単に現工程だけで発生するものだけが対象ではなく、他のプロセスへの影響も連携して考慮する必要がある。

このように、シミュレーション技術を用いて事前にシステマティック欠陥の可能性を捕獲し修正することで、製造ラインの計測および検査で補足することが困難な欠陥を、事前に抑制すると共に、製造工程におけるバラッキを、よりランダムで正規分布に則る状況に誘導することが、製造工程における計測のサンプリング数を抑制することに繋がると考えられる。このため、シミュレーション技術は、従来の計測、検査技術を補完する技術として益々重要になると考えられる。

図表 12-29 CMP 後の欠陥要因および、配線抵抗容量変動要因事例

\*ローカル段差はリソグラフィーのフォーカスバジェット想定以上が存在する場合、リソグラフィーDRC へ情報のインプットを行う。

図表 12-30 ECP と CMP のキャリブレーションと運用フロー

\*シミュレーションで予測された情報の程度によって、設計変更あるいは、プロセス監視点対象とし対応する。

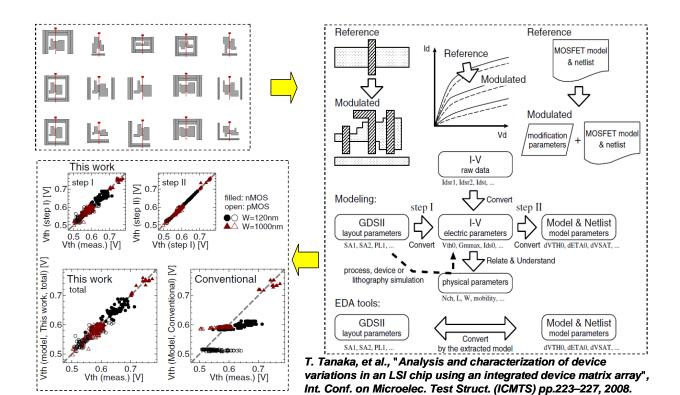

さらに、Tr性能を向上させる手段として歪技術の導入(45 nm node ~ )が行われているが、現在 Trのチャネル部の歪を非破壊で正確に測る手法が確立されていない。このため、様々な Tr 形状に対して、その特徴となる形状パラメータを定義し、Tr 特性との相関から(線形)モデル式を実験的に求め、SPICE parameter にフィードバックすることも行われている。(図表 12-31)

実際問題、歪み以外の他の要素も取り込まれるわけであるが、Tr 特性を正確に予測する必要性から Empirical な実験 Model を暫定的に使用することも必要性に迫られた対応である。歪みの計測技術の確立とと もに応力のシミュレーションのキャリブレーションにより、早期に Empirical Model から物理モデルで置き換えて ゆく事が望まれる。図表 12-31 では、左上破線ブロック図のような Tr 形状を準備し、参照 Tr との特性変動を Tr 構造を特徴付ける形状パラメータの多項式で近似し、さらに SPICE パラメータに変換する作業フローが記述されている(右破線ブロック図)。これにより、より正確な回路シミュレーションが可能となるわけである。左下破線ブロック図は、Tr 形状パラメータのフィッティング精度を示している。従来、チャネル長とチャネル幅が同じであれば、Tr の他の形状がことなっても同じ特性(ここでは Vth)が得られることになっていたが(Conventional)、形状パラメータの導入により、より正確に Tr 特性を予測することができている事が判る(This work)。Step は特性変調の SPICE パラメータへの変換精度を表している。

図表 12-31 Tr 形状パラメータを用いた Tr 特性予測および SPICE パラメータへの変換

以上述べてきたように、シミュレーションは、主に、チップ内のシステマティックな変動を捕捉する技術であり、 実計測は、主にチップ間変動を、サンプリング手法を用いて推定する手法である。前者はシミュレーションでし か達成し得ない領域であり、明確な物理モデル(暫定的には実験ベースのフィッティングモデル)に基づくため、 不良の原因系の理解を同時に行うことができる。さらに、製造前の設計データにおいて対応ができるために製 造ラインにおける負荷が無く、理想的な出来上がりの手法である。一方、実際の計測は計測でチップ間変動を 管理・制御する上で必要不可欠である。また、シミュレーションの広範なプロセスへの展開は、システマティック な欠陥の抑制が可能になるために、より理想的なサンプリング計測が可能になるということで、シミュレーション技術のもたらす、実計測への効果も非常に大きい事がわかる。シミュレーションは計測および計測のもたらす効果においても最も効率的なエコかもしれない。

#### 12-5-5 欠陥検査

欠陥検査も製造ラインで重要な広義の計測である。欠陥検査は、ITRS では YE(Yield Enhancement: 歩留まり改善)の領域に含まれ、その要求項目、要求値が記述されている。欠陥検査では、R&D(研究開発段階)、Yield Ramp(歩留まりの立ち上げ段階)、Volume production(量産)で 300mm ウェーハの時間当たりのスループットと、その際の検出感度(最小検出粒径)が記載されている。これは各段階で検出すべき欠陥の性質が異なるからである。R&D では時間がかかっても欠陥の原因系を網羅したい要求があり、電子線によるスループットを犠牲にした網羅的な欠陥検査が主体となっている。プロセスが改善され、量産時に検出すべき欠陥は、excursion(突発的な原因系による欠陥で通常の欠陥分布とは乖離した分布)が中心となる。Excursion は、ある程度の大きさを対象とする検出感度で、できるだけ多くのウェーハ枚数の表面を網羅して検査したい要求があるため、光による検査が主体となっている。ITRS 2007 年度版 ([7]の表 YE6)を参照すると、図表 12-33 で示されるように、各段階においても検出感度が赤色の状態であることがわかる。

Table YE6

| Table 1E0                                                                   |                 |                  |                  |                | •       |

|-----------------------------------------------------------------------------|-----------------|------------------|------------------|----------------|---------|

| Year of Production                                                          | 2009            | 2010             | 2011             | 2012           | 2013    |

| Patterned Wafer Inspection, PSL Spheres * at 90% Capture, Equ               | ivalent Sensiti | vity (nm) [A, B] | i                |                |         |

| Process R&D at 300 cm <sup>2</sup> /hr                                      | 20              | 18               | 16               | 14             | 12.5    |

| (0,4 "300 mm wafer"/hr)                                                     |                 |                  |                  |                |         |

| Process R&D at 300 cm2/hr                                                   | 12              | 10.8             | 9.6              | 8.4            | 7.5     |

| with 50 % Capture rate [Q]                                                  |                 |                  |                  |                |         |

| Yield ramp at 1200 cm <sup>2</sup> /hr                                      | 32              | 28.8             | 25.6             | 22.4           | 20      |

| (1,7 "300 mm wafer"/hr)                                                     |                 |                  |                  |                |         |

| Volume production at 3000 cm <sup>2</sup> /hr                               | 40              | 36               | 32               | 28             | 25      |

| (4,3 "300 mm wafer"/hr)                                                     |                 |                  |                  |                |         |

| Speed [wafer/hrs]at volume production (1xDR) on Brigthfield                 |                 |                  |                  |                |         |

| tools [R]                                                                   | 5               | 5                | 5                | 6              | 6       |

| Tool matching (% variation tool to tool) [C]                                | 5               | 5                | 5                | 5              | 5       |

| Defect coordinate precision [μm] note                                       | 1.75            | 1.575            | 1.4              | 1.225          | 1.12    |

| Defect coordinate precision [µm] note                                       | 1.4             | 1.26             | 1.12             | 0.98           | 0.875   |

| Wafer edge exclusion (mm)                                                   | 2               | 2                | 2                | 2              | 2       |

| Cost of ownership (\$/cm <sup>2</sup> )                                     | 80.0            | 80.0             | 0.08             | 80.0           | 80.0    |

| E-beam inspection Inspection: Defects other than Residue, Equiv             | alent Sensitivi | ty in PSL Diame  | eter (nm) at 90% | % Capture Rate | *[D, E] |

| Sensitivity for voltage contrast application without speed                  |                 |                  |                  |                |         |

| requirement (nm)                                                            | 50              | 45               | 40               | 35             | 32      |

| Sensitivity for physical defect detection (nm)                              | 20              | 18               | 16               | 14             | 12.5    |

| speed for voltage contrast applications                                     | 100             | 100              | 300              | 300            | 300     |

| Speed for physical defect detection                                         | 50              | 50               | 50               | 50             | 50      |

| CoO HARI (\$/cm <sup>2</sup> )                                              | 0.388           | 0.388            | 0.388            | 0.388          | 0.388   |

| Backside cleaniness for inspection tools                                    |                 | -                | -                | -              | -       |

| Critical Defect Size (µm) for large defects                                 | 20              | 20               | 10               | 10             | 10      |

| Backside Particle per Wafer pass (PWP) Budget (defects/m²) for              |                 |                  |                  |                |         |

| large defects                                                               | <1              | <1               | <1               | <1             | <1      |

| Critical Defect Size (nm) for total defects                                 | 250             | 225              | 200              | 175            | 160     |

| Backside Particle per Wafer pass (PWP) Budget (defects/m <sup>2</sup> ) for | 0500            | 0500             | 0500             | 0500           | 0500    |

| total defects                                                               | 2500            | 2500             | 2500             | 2500           | 2500    |

図表 12-32 YE の Inspection 要求

検出感度はスループットとトレードオフの関係にあり、現状の検出感度が所定のスループットを前提に定義されているために、空間分解能より大きいサイズの検出領域では、スループットを挙げる事でロードマップ上の検出感度を上げることができるわけである。電子線の場合のスループットの改善は、既存のオーバーヘッドを削減する事、センサーの感度を上げることで、45 nm ノードから 32 nm ノードのスケーリングは実現可能ではないかと思われる。ビーム電流を挙げて、スキャンレートを高くする事や、マルチビーム、マルチカラム化も、マスクレスの露光技術開発のインフラとして更に先のテクノロジーノードには対応できるかもしれない。

光検査に関しては、センサー感度の向上やマルチビーム化は、電子線よりも容易な技術であり、現在既に 実現されている技術でもある。この延長線上で 32 nm ノードのスケーリングは十分可能な領域だと考えられる。 光検査の分解能に関しては、さらに短波長化が可能な状況である。

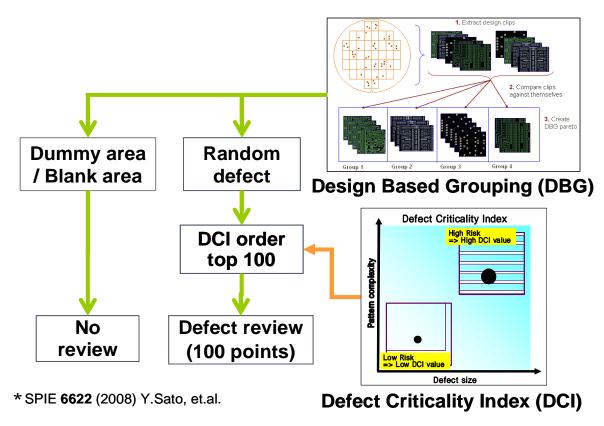

Inspection(欠陥検査)は、続いて行われる欠陥 review、分類、分析において、原因系を特定する一連の連携作業の初期検査にあたる。Inspection における高感度化は、欠陥の検出数の増加につながるため、サンプリングが必要不可欠な技術になっている。この対応として、効率的な欠陥 review のための Inspection 情報のサンプリング(or filtering)が提案されている[8]。具体的には、図表 12-33 に示すように、Inspection によって得られた欠陥の大きさと場所の情報を元に、欠陥の発生した場所に対応する設計データを抽出して、設計データのパターン毎に欠陥の分別を行い、同時に、設計パターンの Critical Area Analysis(CAA)を行い、欠陥の危険度の順にしたがって欠陥を Review する方法である。従来、Critical Area は、random 欠陥の粒径(r)に対する存在確率分布 P(r)、粒径(r)がチップ上(設計データ上)に存在した際に致命欠陥となる領域の面積を  $S_{CA}(r)$ として式2で表現される。 $S_{CA}(Critical Area) \times Do(単位面積あたりの欠陥個数)は、チップ当たりの致命欠陥個数(期待値)となる。ポアソン分布を仮定すれば(<math>\lambda^x e^{-\lambda}/x!$ )、欠陥が O(=x)個である確率として式(3)が該当する工程歩留まりとなる。この概念を基に欠陥の大きさとその背景のデザインの Pattern complexity( $\sim$  critical area)から Defect Criticality Index(DCI)を定義して review すべき欠陥のサンプリングを行うものである。

Critical Area =

$$S_{CA} = \int S_{CA}(r) * P(r)dr$$

(2)

工程歩留まり =

$$e^{-\lambda}$$

=  $e^{-S_{CA} \times D_0}$  (3)

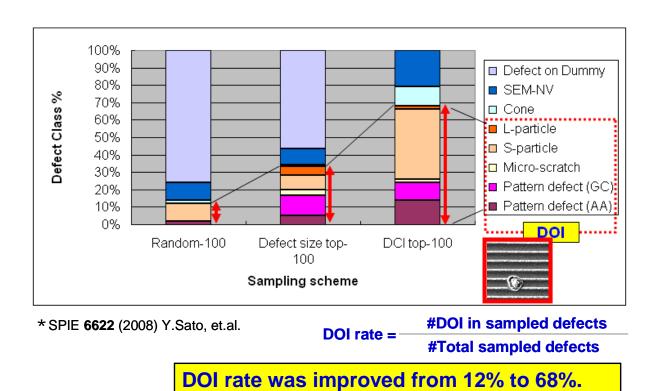

図表 12-34 には、検出された欠陥の中から 100 個の review を行った際の、review の方法と review した欠陥の要因の内訳を示している。

図表 12-33 欠陥検査後の review のサンプリング手法

図表 12-34 欠陥 review のサンプリングの違いによる致命欠陥の検出率の差

図表 12-34 中の赤色破線で囲まれた致命欠陥の比率から見ると、ランダムなサンプリングでは致命欠陥を10%強しか捕捉できておらず、欠陥サイズの Top100 でも 30%強に止まっていることが分かる。一方 DCI で抽出した Top100 は、致命欠陥(DOI は致命欠陥、あるいは致命欠陥となりうる原因系が含まれている欠陥)を70%弱も捕捉できている。このように同じ量の欠陥 review を行うにあたっても、そのサンプリングにおいて価値の重み付けをすることが如何に重要かを明確に提示している事例である。

このようなサンプリングは、従来感度を調整して review する欠陥の数を絞る手法と異なり、適切な感度において、インパクトのある欠陥をサンプリングするため、歩留まりの主要因を効率よく捕捉することができる手法として期待されている。 また今後の微細化において、サンプリング技術がコストと計測精度を最適化する重要な技術になることを示唆している一例である。

#### 12-5-6 まとめ

2008 年度はエコをテーマとして取り上げ、計測の最適化によってもたらされる効果に着目して検討を行った。デバイスのスケーリングに対応して分解能を向上させることは計測の命題ではあるが、いくら計測精度を向上させてもロットの平均値、バラツキの分布を正確に把握し、プロセス管理あるいは制御をしなければ、特性歩留まりを向上させることはできない。そこで、正確なプロセス制御(APC)にとってのサンプリングの重要性を述べた。また実際にプロセス中では計測できないプロセスの出来上がり状態を特徴付ける装置ログデータ((制御・シークエンスデータ、センサーデータ等))と特性との間に強い相関を見出し、特性予測をする手法がFDCをベースに発展しており、既存のデータから、如何に重要な情報を計測に足る情報として活用するかが、計測を広義で捕らえた場合、非常に大きなエコとなりえるのではないかと考えられる。Virtual metrology は、前述のFDCのより、更に実際の計測情報と同程度の価値のある情報を見出すもので、情報の抽出手法は FDC と近いものがある。Virtual Metrology と FDC は、その目的は異なるが、FDC は不良に関わる大きな変動に関する情報の抽出のため、既存データにおいても Virtual metrology よりも成立する可能性は高い。

FDCも Virtual Metrology もそうであるが、既存データに意味のある情報が存在しない場合は成立しないため、 プロセス装置ベンダーに対して、今後価値のある情報の出力(提供)を啓蒙しなければならない。

他方チップの中のシステマティックなプロセスバラッキの抽出に関しては、チップ内全パターンを把握する必要性からインラインの計測では、スループットの観点からそもそも不可能である。またその原因系を辿る手法も別途必要となる。このような状況に対応する手法としてシミュレーション技術が発展してきた。実際の出来上がりの計測においては、シミュレーションで予測できる論理的な誤差の他に、unknown な要素もあることは事実であるが、少なくとも事前予測される論理的な誤差について予測し、設計段階で修正することは、製造ラインにおける不良のリスクを最も安価に抑制できる手法であると考えられる。シミュレーションはある意味ではその予測精度においては計測足る、あるいはその計算スピードの観点から最も経済的な広義の計測であると言える。シミュレーション技術はリソグラフィーへの導入から始まり、ECP、CMP、Stress (Strain)へとその展開が加速している。Stress (Strain)に関しては校正(calibration)を行うための計測技術が現在壁となっておりその取り組みが行われている最中である。

さらにサンプリングのもたらす効果を如実に表す事例として、欠陥検査後の欠陥 review のサンプリングについて紹介したが、単に欠陥の大きさだけでなく、その存在する場所における影響度を考慮するといったアイディア(工夫)によっても大きな効果が得られることが示された。このように従来の計測精度やスピードだけに囚われず、その活用方法が大きな鍵を握っている事を再認識させられた良い事例である。

## 12-6 今後

国際会議における活動、和訳等の隔年の定常的な活動は従来通りで行ってゆく予定であるが、2009年度からは、テーマを絞ったヒアリングを行い、計測技術の深堀も行い、読み手にとってより多くの価値を見出せる内

容にしてゆきたいと考えております。2009年度の計測とアリングは X 線全般について行う予定です。

# 参考文献

- [1] 佐藤 敦; 白色干渉法を利用した最新の表面形状評価技術 , 表面技術, Vol. 57, p.554 (2006) http://cweb.canon.jp/indtech/zygo/lineup/newview/principle.html

- [2] ISSM 2008, H.Matsuhashi

- [3] AECAPC Asia 2007, H.Shirai, et.al.

- [4] T. H. Park, "Characterization and Modeling of Pattern Dependencies in Copper Interconnects for Integrated Circuits", Ph.D. thesis, Massachusetts Institute of Technology, 2002.

- [5] J. Luo, Q. Su, C. Chiang, and J. Kawa, "A Layout Dependent Full-Chip Copper Electroplating Topography Model", International Conference on Computer Aided Design, pp. 133-140, 2005.

- [6] D. Fukuda, T. Shibuya, N. Idani, and T. Karasawa, "Full-Chip CMP Simulation System", International Conference on Planarization/CMP Technology, 2007.

- [7] http://strj-jeita.elisasp.net/strj/ITRS07/Roadmap-2007.htm のYEの章の表YE6

- [8] Y. Satoya, et al., "Defect Criticality Index (DCI): A new methodology to significantly improve DOI sampling rate in a 45nm production environment", Proc. SPIE 6922 (2008) 6922