## 第7章 WG6 PIDS (Process、Integration、Device、and Structures)

## 7-1 はじめに

WG6(PIDS: Process Integration、Devices、and Structures)のカバーする技術領域は、ロジックデバイス、メモリデバイス、RF(Radio Frequency) & AMS(Analog Mixed Signal)である。2009 年度の主な活動として、1)ITRS2009の作成、2)ITRS2010に向けた現状調査、3)ゲート長が16nm以下のLong-term years に必要とされる技術調査を行った。

ITRS2009 では、ロジックデバイスの HP(High-performance)、LOP(Low Operation Power)、LSTP(Low Standby Power)のゲート長スケーリングについて、実態に合わせ ITRS2008update よりも 1 年遅らせることになった。ITRS2008update では、HPとLOP のゲート長スケーリングを ITRS2007 よりそれぞれ 3 年、2 年遅らせており、ITRS2009 で HP のスケーリングの鈍化が更に大きくなってきている。ロジックデバイスでは、単純な繰り返しの回路パターンが少なく、ダブルパターニングといった微細化手法を使うことが難しく、スケーリングがリソグラフィ装置の性能(波長)に強く依存しているため、ArF リソグラフィ装置の延命とともにスケーリングが鈍化してきている。

メモリデバイスについては、各社への聞き取り調査と製品情報から改定を行った。NAND フラッシュに代表されるように、繰り返しパターンのメモリ部では、リソグラフィ装置に依存しないダブルパターニングなどの微細化手法を導入しやすく、ロジックデバイスとは逆に微細化が加速している。NAND フラッシュでは、32nm が2010年とITRS2007と比べ、1年前倒しとなった。また、DRAMは縦型デバイスを用いた4F2セルが2011年に市場投入との発表があった。今後もNANDフラッシュの微細化が更に進むことが考えられることや、DRAMの4F2セルの確認ため、ITRS2010に向けて各社への聞き取り調査を再度行う予定である。

RF&AMS では、10GHz 以上のミリ波デバイスが大きく伸びていることにより、デバイスの分類が 10GHz の 周波数を境に二分された。RF&AMS CMOS のスケーリングはロジックデバイスに整合させて遅らせている。

ゲート長が 16nm 以下の Long-term years に必要とされる技術として、Ge チャネルデバイスに関するヒアリングを実施した。WG6 会議は今年度は隔月で実施され、図表7-1 に示す議題のディスカッションや各分野の専門家による次世代技術に関するヒアリングを実施した。講師をしていただいた皆様に深く感謝する。

| 開催    | 開催日        | テーマ                  | 講師                                              |

|-------|------------|----------------------|-------------------------------------------------|

| 第109回 | 2009.6.24  | High-k/Metal Gate    | ルネサス 井上氏                                        |

| 第110回 | 2009.8.26  | ソフトエラー対策、技術動向        | 富士通マイクロ 上村氏                                     |

| 第112回 | 2009.12.17 | Ge-チャネル<br>FD-SOIの現状 | NEC 多田氏<br>金沢工業大学 井田教授                          |

| 第113回 | 2010.2.24  | 2009IEDM 報告          | NECエレ 今井氏<br>広島大学 芝原准教授<br>東京大学 高木教授<br>TEL 赤坂氏 |

図表 7-1 2009 年度 WG6 会議 議題およびヒアリングテーマ

## 7-2 ロジックデバイス

## 7-2-1 ITRS2009 におけるロジックデバイスの主な改訂内容

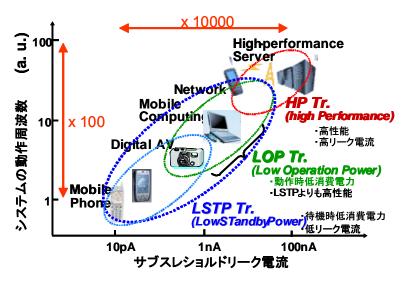

ロードマップで扱うロジック CMOS 用テクノロジは、用途別に 3 種類に分類されている。高速性能が要求される用途向けに HP(High Performance) テクノロジ、動作時の低消費電力が要求される用途向けに LOP(Low Operation Power) テクノロジ、待機時の低消費電力が要求される用途向けに LSTP(Low STandby Power) テクノロジである。ところが、ここ 1、2 年、Smart Phone といったモバイル機器の高性能化により、LSTP の範囲が LOP の領域まで広がりつつある(図表 7-2)。 更に、HP のスケーリングの鈍化から HP と LSTP のゲート長の差が 小さくなってきている。 今後、実態に合わせ、デバイスの分類についての見直すことが必要である

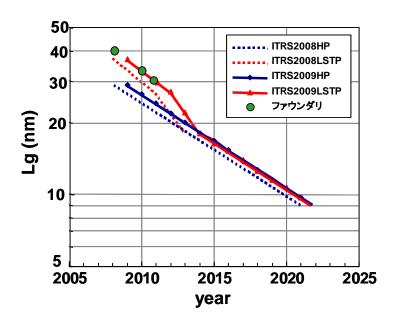

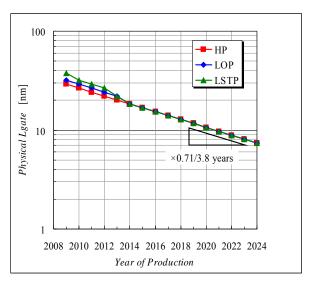

図表 7-3 に示すように ITRS2009 では、ロジックデバイスの HP、LOP、LSTP のゲート長スケーリングについて、LSTP の実態に合わせて ITRS2008update よりも 1 年後退させた。ITRS2008update では、LSTP のゲート長スケーリングは、ITRS2007 と同じにしたが、HP と LOP のゲート長スケーリングは ITRS2007 より、それぞれ 3 年、2 年遅らせており、ITRS2009 の改定で HP のスケーリングの鈍化が更に大きくなってきている。その結果 HP と LSTP のゲート長差が詰まり、2014 年には、LSTP のゲート長は HP と同じ 18nm になり、2014 年以降、HP、LSTP 共に同じゲート長で推移すると予想している。また、見直しの結果、CMOS のゲート長が 10nm に達する時期は、2021 年になると予想される。

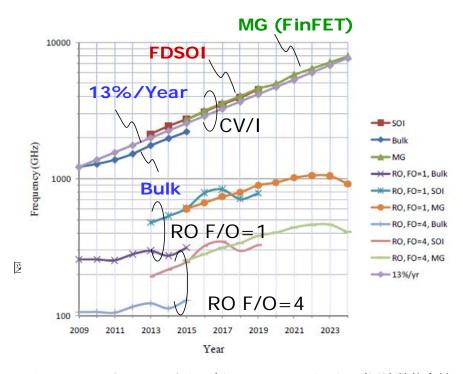

図表 7-4 に ITRS2008update と ITRS2009 のロジックテーブルの比較表を示す。メタルゲートが使われるようになり、ポリゲート空乏層は、テーブルから削除された。サブスレショルドリークも、HP/LOP/LSTP でそれぞれ、100/5/0.05 nA/μ n と年度に寄らず一定値とし削除された。移動度改善係数、Ids 改善係数も一定値のため削除された。新しく、チャネル濃度、接合深さがテーブル化された。バリスティック効果係数は、デバイス構造に寄らず一元化され、新たにソース端でのキャリア注入速度がテーブル化された。また、HP のテーブルのみであるが、PMOS のドレイン電流が NMOS のドレイン電流値との比で表記され、実回路のスピード指数として F.O.=1 と F.O.=4 のリングオシレータのスイッチング時間も表記された。

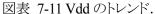

図表 7-5 に示すように、電源電圧は Planar Bulk、UTB FDSOI(Ultra Thin Body Fully Depleted SOI)、MG(Multi Gate)が混在するときでも同じ電圧に統一され、低電圧化が進むと予想している。逆に電気的なゲート絶縁膜厚 EOT の薄膜化が鈍化してきている。また、HP、LOP、LSTP とも 2013 年から UTB FDSOI を導入、2015 年から Double Gate 導入となっている。

図7-6にCV/Iのゲート遅延時間とリングオシレータのスイッチング周波数を示す。スケーリング鈍化に伴いゲート遅延時間も年率17%改善から13%改善に低下する。この場合のリングオシレータ F.O.=1 と F.O.=4 のスイッチング周波数も示している。なお、スイッチング速度は、解析シミュレータ MASTAR を用いて計算している。

図表 7-2. ITRS2009 におけるロジックトランジスタの分類

図表 7-3. ITRS2009 における HP、LSTP のゲート長スケーリング

| 2008                         | <br>年度版    | 2009:                        | 年度版         |

|------------------------------|------------|------------------------------|-------------|

| Lg                           |            | Lg                           | 2008年より1年遅れ |

| EOT                          |            | EOT                          | スケーリング鈍化    |

| Gate poly depletion          | ⇒削除:メタルゲート | channel dope                 | 新           |

| EOT ele                      |            | junction depth               | 新           |

| Jg                           |            | EOT ele                      | スケーリング鈍化    |

| Vdd                          |            | Cg ideal                     | 見直し         |

| Vtsat                        |            | Jg                           | 見直し         |

| lds leak                     | ⇒削除        | Vdd                          | 一元化。低電源化加速。 |

| lds sat                      |            | Vt sat                       | +100mV      |

| µ enhancement factor         | ⇒削除:一定値    | Ballistic factor             | 一元化         |

| lds enhancement factor       | ⇒削除        | Rsd                          | ×0.8 低抵抗加速  |

| Ballistic factor             |            | lds sat                      | 見直し         |

| Rsd                          |            | vinj                         | 新           |

| Cg ideal                     |            | Cg fringing                  | 新:見直し要      |

| Cg total                     |            | Cg total                     | 見直し         |

| $\tau = CV/I \text{ (NMOS)}$ |            | $\tau = CV/I \text{ (NMOS)}$ | 見直し         |

| 1/τ (NMOS)                   | ⇒削除        | PMOS Ionn/Ionp               | 新           |

|                              | _          | R.O. F.O=1                   | 新           |

|                              |            | R.O. F.0=4                   | 新           |

図表 7-4. ITRS2009 ロジックテーブル変更点

| Year of | fproduction            | 2009 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 | 2021 |

|---------|------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Metal1  | ½ pitch (nm)           | 54   | 45   | 38   | 32   | 27   | 24   | 21   | 18.9 | 16.9 | 15   | 13.4 | 11.9 | 10.6 |

|         | Lg (nm) 1 year delay   | 29   | 27   | 24   | 22   | 20   | 18   | 17   | 15.3 | 14   | 12.8 | 11.7 | 10.7 | 9.7  |

|         | Vdd (V) for PB, FD, DG | 1    | 0.97 | 0.93 | 0.9  | 0.87 | 0.84 | 0.81 | 0.78 | 0.76 | 0.73 | 0.71 | 0.68 | 0.66 |

|         | EOT(nm)                |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HP      | Planar Bulk            | 1    | 0.95 | 0.88 | 0.75 | 0.65 | 0.55 | 0.53 |      |      |      |      |      |      |

|         | UTB FDSOI              |      |      |      |      | 0.7  | 0.68 | 0.6  | 0.57 | 0.57 | 0.54 | 0.5  |      |      |

|         | Double Gate            |      |      |      |      |      |      | 0.77 | 0.7  | 0.67 | 0.64 | 0.62 | 0.59 | 0.57 |

|         | IdsatN / IdsatP new    | 1.3  | 1.29 | 1.27 | 1.26 | 1.25 | 1.24 | 1.22 | 1.21 | 1.2  | 1.19 | 1.18 | 1.16 | 1.15 |

|         | Lg (nm) 1 year delay   | 32   | 29   | 27   | 24   | 22   | 18   | 17   | 15.3 | 14   | 12.8 | 11.7 | 10.7 | 9.7  |

|         | Vdd (V) for PB, FD, DG | 0.95 | 0.95 | 0.85 | 0.85 | 0.8  | 0.8  | 0.75 | 0.75 | 0.7  | 0.7  | 0.65 | 0.65 | 0.6  |

| LOP     | EOT(nm)                | •    | •    |      |      |      |      |      |      |      |      |      |      |      |

| LOP     | Planar Bulk            | 1    | 0.9  | 0.9  | 0.85 | 0.8  |      |      |      |      |      |      |      |      |

|         | UTB FDSOI              |      |      |      |      | 0.9  | 0.85 | 0.8  | 0.75 | 0.7  |      |      |      |      |

|         | Double Gate            |      |      |      |      |      |      | 0.8  | 0.8  | 0.75 | 0.73 | 0.7  | 0.7  | 0.65 |

|         | Lg (nm) 1 year delay   | 38   | 32   | 29   | 27   | 22   | 18   | 17   | 15.3 | 14   | 12.8 | 11.7 | 10.7 | 9.7  |

| LSTP    | Vdd (V) for PB, FD, DG | 1.05 | 1.05 | 1.05 | 1    | 0.95 | 0.95 | 0.95 | 0.85 | 0.85 | 0.85 | 0.85 | 0.75 | 0.75 |

|         | EOT(nm)                | •    | •    | •    | •    |      |      |      |      |      |      | •    |      | •    |

|         | Planar Bulk            | 1.2  | 1    | 1.2  | 1    | 0.9  |      |      |      |      |      |      |      |      |

|         | UTB FDSOI              |      |      |      |      | 1.0  | 0.95 | 0.9  | 0.85 | 8.0  |      |      |      |      |

|         | Double Gate            |      |      |      |      |      |      | 1.1  | 1.1  | 1.0  | 1.0  | 0.9  | 0.9  | 0.8  |

Manufacturable solutions exist, and are being

Manufacturable solutions are known

Manufacturable solutions are NOT known

図表 7-5. パラレルパス導入とLg、Vdd、EOT のトレンド

図表 7-6. トランジスタ CV/I とリングオシレータのスイッチング周波数依存性

## 7-2-2 メタルゲート/ハイkの動向

## 7-2-2-1 メタルゲート/ハイk 技術のロードマップ

ITRS2009ではロジック用トランジスタのゲート長ロードマップが、ITRS2007から3年から4年も後倒ししたことに伴い、EOT 膜厚(SiO<sub>2</sub> 換算膜厚)に対しての要求が緩和された。図表 7-7 に MPU/ASIC の EOT の、ITRS2007からの変遷を示す。バルク MPU の場合、2010年で0.95nmである。この値は後述する学会で発表された MPU の EOT と同様の値となっている。図表 7-7 では、EOT が 0.9nm 以下でテーブルは黄色に、0.7nmを下回ると赤色となる。EOT で 0.7nm 以下が、学会発表などでも満足のいく解が見出されていないことに対応している。最もゲート長スケーリングが緩やかな LSTP (Low STanby Power)のメタルゲート/ハイk 導入も後倒しされ、HP(High Performance)の2年遅れの2011年からとなった。これは、ITRS2008update 版から更に3年も後倒しとなったことになる。

|          | Year of Production        | 2009 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 |

|----------|---------------------------|------|------|------|------|------|------|------|

| ITRS2007 | EOT for bulk<br>MPU/ASIC  | 0.75 | 0.65 | 0.55 | 0.5  |      |      |      |

| ITRS2008 |                           | 1    | 0.95 | 0.88 | 0.75 | 0.65 | 0.6  | 0.53 |

| ITRS2009 | W 07 7 0.0                | 1    | 0.95 | 0.88 | 0.75 | 0.65 | 0.6  | 0.54 |

| ITRS2007 | EOT for FDSOI<br>MPU/ASIC |      | 0.7  | 0.6  | 0.55 | 0.5  | 0.5  | 0.5  |

| ITRS2008 |                           |      |      |      |      | 0.7  | 0.65 | 0.58 |

| ITRS2009 |                           |      |      |      |      | 0.7  | 0.68 | 0.6  |

| ITRS2007 | EOT for multi-            |      |      | 0.8  | 0.7  | 0.6  | 0.6  | 0.6  |

| ITRS2008 | gate                      |      |      |      |      |      |      | 0.77 |

| ITRS2009 | MPU/ASIC                  |      |      |      |      |      |      | 0.77 |

図表 7-7 MPU/ASIC の EOT の変遷 (ITRS2007 → ITRS2009)

#### 7-2-2-2 メタルゲート/ハイk 技術開発状況

MOSFET の微細化を推し進めていくためには、比誘電率の高いハイ k ゲート絶縁膜とメタルゲート電極を組み合わせたメタルゲート/ハイ k 構造が求められている。WG6 では、著名な研究、開発者からのヒアリングや、最新の研究成果が発表される IEDM (International Electron Devices Meeting)などでのメタルゲート/ハイ k 技術動向を調査した。

メタルゲート/ハイ k 構造を実現するプロセスとして、FET の性能を安定させ易いゲートラスト方式(一部の企業で45nm 世代から量産されている。シリサイド形成が終わった後、ダミーのポリ Si ゲートを除去し、メタルゲートを埋め込むプロセスフロー)と、従来のポリ Si ゲートと同様の工程にできるゲートファースト方式(ポリ Si ゲート/SiON のトランジスタ作成フローをメタルゲート/ハイkに置き換えたもの)がある。ゲートラスト方式のメタルゲート/ハイk 構造は、2007 年に45nm 世代製品で量産が開始された。

一方、従来のプロセスフローに近いゲートファースト方式は、2010年に量産が始められる 32nm 製品で採用される可能性がある。実用化に向けた最大の課題は、しきい値制御である。ハイk 膜とメタルゲート電極の形成後に、ソース/ドレインを活性化させる熱処理が必要になるが、この熱がハイ k 膜とメタルゲート電極に影響し、しきい値が変化してしまう。この課題を解決する方法として、「キャップ法」がここ 2、3 年積極的に研究されてきた。NMOS と PMOS でハイ k 膜の上層または下層に別々の材料のキャップ層を形成して、しきい値を所望の値に変化させる技術である。ハイk 膜の上層または下層に金属酸化膜を形成しておき、熱処理時に金属原子をハイ k 膜中に拡散させるというものである。この結果、実効的なゲートの仕事関数が変化する。拡散させる金属の種類や濃度を NMOS と PMOS で個別に最適化することで、それぞれに所望のしきい電圧を得ることがで

きる。拡散させる金属は、NMOS には La、PMOS には Al を使うことが多い。

2009年12月に開催されたIEDMにおける最新のゲートラスト/ゲートファースト方式関係の論文から、メタルゲート/ハイk技術動向を以下に紹介する。

第二世代のメタルゲート/ハイk 技術を使った、32nm 世代向け HP および LP プラットフォーム技術をインテルが発表した。ゲートラスト方式を継承しているが、フローに変更が加えられている。45nm 世代向けゲートラスト方式では、ALD(Atomic Layer Deposition)法によるハイk ゲート絶縁膜の形成、ダミーポリ Si ゲート形成、高温のソース/ドレインアニール、シリサイド形成、ダミーポリ Si ゲート除去、メタルゲート形成、というフローであった。32nm 世代向けの第二世代メタルゲート/ハイk のフローは、ハイk ゲート絶縁膜もダミーゲート除去後に形成して熱工程の影響を回避した点である。32nm 世代の LP(Low Power)プラットフォーム向けテクノロジでのゲート絶縁膜の EOT は、2009 年版ロードマップと同様の 0.95nm である。その他の大きな特徴は、ハイk ゲート絶縁膜とメタルゲート技術を採用した3種類の異なるトランジスタを、同一チップ上に混在させることができる点である。3種類のトランジスタの内訳は、(1)高性能トランジスタ、(2)低消費電力トランジスタ、(3)高電圧入出力用トランジスタである。高性能トランジスタの性能は極めて高い。NMOS のオン電流は

1.53mA/μm(Ioff=100nA/μm、電圧は 1V)、PMOS のオン電流は 1.23mA/μm(Ioff=100nA/μm、電圧は 1V)である。低消費電力トランジスタは、常に電源をオンしておく回路や低い待機電流値が求められる回路に向けたトランジスタである。ハイk の採用により、ゲートリーク電流を極めて低く抑えられている。(3)の高電圧入出力用トランジスタは、電圧 1.8V あるいは 3.3V を選べる。

ゲートファースト方式の陣営からは、28nm 世代向けのメタルゲート/ハイk ベースのLP プラットフォーム技術の発表があった。ゲートファースト方式では、トランジスタのしきい値の制御を、ダイポールを生成する、非常に薄い Al(PMOS 用)や La(NMOS 用)系のキャップ層に依存している。ゲートファースト方式の課題はしきい値調整や PMOS での移動度劣化である。更に、ゲートラスト方式のようにダミーゲートを除去した後にチャネルに誘起されるひずみによる性能アップの効果がない。利点は、設計ルールの制限が弱い、プロセスがゲートラスト方式よりシンプルなことなどが言われている。しかし、設計ルールの強い制限、例えばゲートを一方向に揃えるなどは、リソプロセスからの要求で、ゲートラスト方式に限らず当たり前のルールになりつつある。

上記の二方式の得失の結論がつかない中、ファンドリー企業からゲートラスト方式を支持するアナウンスが 2009 年にあった。2010 年量産開始予定の 28nm 世代の LSI において、高性能向けプロセスはゲートラスト方式のメタルゲート/ハイk 構造を採用するという。

また、同じIEDM において、NMOS をゲートファースト、PMOS をゲートラストで行う、ハイブリッドメタルゲート/ハイk 技術といった、第三の方式の発表もあった。

## 7-2-2-3 今後の技術動向

2010 年は複数メーカーから、メタルゲート/ハイk 構造を採用した 32-28nm 世代 CMOS の量産が予想される。その時の作製プロセスは、45nm 世代で量産実績のあるゲートラスト方式に加えて、従来プロセスとの整合性の良いゲートファースト方式で量産する企業も現れると予想される。その次の 22nm 世代のメタルゲート/ハイk 構造がどのように進むかであるが、32nm 世代の EOT で 0.9nm 程度のゲート絶縁膜の更なる薄膜化(高 k 材料導入、界面層の薄膜化やハイk 化などによる)と、キャップ/添加材料の改良による仕事関数の最適化などが考えられる。

## 7-2-3 Strain 技術の動向

CMOS ロジックにおいては、既にゲート長シュリンクによる駆動力改善は期待できない状況に陥っている。そ のため、スイッチング性能(CV/I)改善のトレンドを維持するには、Strain を用いてキャリア移動度を向上させる技 術が必須の Booster となっている。しかしながら、Strain 技術によるドレイン電流改善率は、素子スケーリングに より低下する。すなわち、スケーリングによりゲートピッチが狭くなると、コンタクトエッチストッパー膜厚を厚くす ることが出来なくなり、ソースドレイン部分の面積縮小により SiGe の選択エピ成長体積が小さくなるため、局所 ストレスによる移動度改善効果が弱くなってしまう。従って、素子のスケーリングを進めつつ、電流改善率を維 持するためにはより薄い膜厚、少ない体積で強い歪を導入できる技術が必要となる。ITRS2008update までは、 Strain による移動度向上率(enhancement factor)とドレイン電流向上率(Ids enhancement factor)が併記されており、 2008 年まではそれぞれの数値が増加しているものの、2008 年以降の電流改善率は僅かずつ減少傾向になっ ており、一部では黄色に識別して改善率の維持が困難なことを示していた。これに対して、ITRS2009 では、電 流向上率の表記は削除され移動度向上率のみを表記するようになった。そして、この移動度向上率は全ての デバイスカテゴリ(HP、LSTP、LOP)、デバイス構造(Bulk、UTB FD (Ultra-Thin Body Fully Depleted SOI)、 MG (Multi-Gate MOSFETs))において「1.8」と定めている。これは、Strainによる移動度向上率の限界値が「1.8」 であることから決定されており、ロードマップとして示したデバイススケーリングとデバイス性能トレンドを達成す るためには、全ての世代において限界までStrain技術を活用する必要があるということを示している。トレンドテ ーブルの色分けとしては、2013年が黄色、2013年以降が赤色で、Bulk 構造から UTB FD や MG 構造に移行 するに従い、十分に Strain を与える技術開発が同時に必要とされている。このように、Strain 技術による Booster は 2009 年において既に限界値に達しており、今後のデバイス性能の向上への期待はできない。他方、チャネ ル長が短くなることにより見込まれるバリスティック輸送によるドレイン電流改善率は 2013 年以降除々に数値を 向上させるシナリオとなっており、他の Booster 効果の飽和傾向を補うシナリオとなっている。

ハイ k/メタルゲートと Strain 技術との組み合わせでは、ゲートラストプロセスにおいて大きな進展が見られている。従来ゲートファーストプロセスに用いられていたストレス膜やソース/ドレインエピ技術をゲートラストプロセスと組み合わせると、ダミーゲートを除去する工程において大きなチャネル歪を発生させることが明らかになった。特に PMOS におけるホール移動度の向上が著しく、ゲートラストプロセスは PMOS の性能向上に特に効果的である[1]。その結果、ドレイン電流の NMOS/PMOS の比率は従来と大きく異なってきており、従来の回路要求から見たデバイストレンドもゲートファーストとゲートラストでは分けて考える必要性も出てくる可能性がある。

また、デバイス構造の観点で見ると 2013 年には UTB FD が、2015 年には MG 構造の実用化が見込まれており、それぞれの構造における Strain 技術の開発を行う必要がある。SOI 基板の薄膜化や三次元構造の影響により従来とはチャネル部への歪の導入され方が異なってくることが分かっており、微小な構造でのチャネル歪発生機構の解析と、それを踏まえたプロセス、構造双方の最適化が必要になる。これに対しては、歪を扱うコンパクトモデルも提案されており、解析技術とシミュレーション技術の更なる発展に期待したい[2]。また、より移動度の高い Si、 Ge、GaAs などの高移動度チャネルとなる新材料の実用化にも期待がかかる。Ge チャネルにおいては、Ge 酸化膜と Ge 基板との界面特性が長年の懸念であったが、最近になって、界面準位の非常に少ない界面酸化膜形成プロセスが提案されており[3]、デバイス性能も飛躍的に向上してきている。他方、GaAs 基板を用いた実験では、電子移動度は 2 軸(Biaxial)の tensile stress が有効であるのに対し、ホール移動度に対しては1軸(Uniaxial)の compressive stress が有効であり、PMOS 性能がシミュレーション予測を大きく超えて向上したという報告もあり[4]、FinFET のような三次元構造とIII-V チャネルの組み合わせにも期待したい。

- [1] S. Mayuzumi, et. al., *IEDM*, p.457, 2009.

- [2] C. H. Lee, et. al., *IEDM*, p.293, 2007.

- [3] Chi-Chao Wang, et. al., SISPAD, p.1, 2009.

- [4] S. Suthram, et. al., VLSI Symposium on Technology, p.182, 2008.

### 7-2-4 新構造デバイス(UTB-FDSOI、MG)の動向

#### 7-2-4-1 新構造デバイスのロードマップ

ITRS2009では、ITRS2008update を反映し UTB(Ultra Thin Body)-FDSOI は 2013年から、MG(Multi Gate、Fin 型など)は 2015年から導入とした。さらに、HP、LOP、LSTPともに導入時期を同じとしている。これらは、ITRS2007に比べて3年から4年、後ろ倒しにしたことになる。ただ、次世代の22nm、15nm世代に向けてこれら新構造デバイスもメインストリームデバイスのオプションの一つとして主要な研究機関での研究は活性化している。さらには、シリコンCMOSの究極の構造とも言えるNanoWire構造の研究も、そのプレーヤが増加している。特に、UTB-SOIについては、2007年まではBulkから直接Fin型に移行し、出番が無いとする意見も多い状況だったが、ここ 1、2年、次節で述べる発表もありプロセスの完成度が向上し、パラレルパスの候補として、再度、注目されている。この動向によってはUTB-SOIの導入時期が早まる場合も有りえ、継続議論の課題である。

### 7-2-4-2 新構造デバイスの技術開発状況

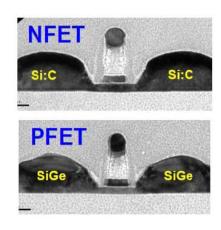

UTB-SOI は、ここ 1-2 年で、プロセス技術の進展が見られた。ソース/ドレイン周りの不純物をインプラでなく 固相拡散で導入しダメージフリーにすることで活性化率が大きく向上し抵抗を下げるプロセスが提案された (VLSI2009、IBM)。 さらに、バルクで進展したメタルゲート/ハイ k を適用し LOP/LSTP 狙いではチャネルに不 純物を導入しない本来の FD(full Deplation)が可能となる。 Avt=1.25mV・μ m と小さいことも実証された。 さらに、 UTB で最大の課題であった SOI ウエハーの Si 膜厚のばらつきについても 0.5nm 以内に制御できるとの報告 があった。 これら3要素から UTB-SOI デバイスは特に LOP/LSTP 向けでバルクデバイスのトレンドと遜色のない Ion が得られている。 図表 7-8 に発表された最新の構造を示す (IEDM 2009、3-2)。 リークの制御性はバルクデバイスより優れるため、特に LOP/LSTP 対応としては次世代の 22nm クラスから使われる可能性も出てきた。

MG、Fin 型も主要な研究機関で研究が継続している。寄生抵抗、ラフネス、モビリティーエンハンスメントなどの課題克服に向け種々の取り組みが継続している。ただ、現状は、まだ、改善が必要と想定される。2009 年の注目としては、これまで報告のなかった最大手ファンダリから初の報告が出た点である(IEDM 2009、12.2)。SOIでなくバルクをベースにしたFin型での結果であった。Finの高さ制御の課題はあるがプレーナバルクデバイスとの混載容易性では、方向性として注目さる。

設計資産の継続性を考慮すると 3 次元 Fin 型の実用化はハードルが高いとの議論がある。UTB FD-SOI はプレーナ型でありこの点のハードルは小さい。

究極の構造である Nano-Wire については、研究するプレーヤが増加している。これまでも報告があったが、 デバイスの一番の基本特性である SCE(Short Channel Effect)制御性がプレーナ型に比べ優れるとの系統的な 結果が出た。図表 7-9 にその結果を示す(iedm2009、12.3)。

図表 7-8 UTB-SOI の構造(iedm 2009、3-2)

図表 7-9 Nano-Wire の SCE (iedm 2009、12.3)

# 7-2-5 新スケーリングコンセプト Lg、Vdd、EOT 7-2-5-1 ゲート長 Lg のスケーリングトレンド

ITRS2009 では、ゲート長のスケーリングをITRS2008updateから更に 1 年遅らせた。図表 7-10 に、ゲート長の推移を示す。これまで、ゲート長のスケーリングはHP (High Performance) が先行し、LOP (Low Operating Power) がそれより遅れ、LSTP (Low Stand-by Power) はさらに遅れるという設定になっていた。ITRS2009 では、これら 3 者が 2014 年の 18nmで一致し、以降 1 世代 ( $1\sqrt{2}$  に縮小) が 3.8 年に相当するペースで縮小が進むように設定した。2014 年はUTB FD採用の年であり、デバイス構造面でゲート長のスケーリングがBulkよりも容易になることを想定している。

図表 7-10 ゲート長のトレンド.

#### 7-2-5-2 Vdd のスケーリングトレンド

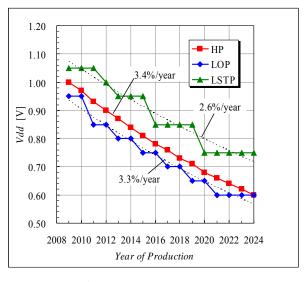

図表 7-11 は、電源電圧 Vdd のトレンドである。Bulk、UTB FD および MG というデバイス構造によらず同一の Vdd が設定されている。ITRS2008update との比較では、HP は 2 年程度の加速、LOP および LSTP はそれぞれ 2 年および 1 年程度の減速になっている。HP は ITRS2008update では階段状の低減であったが、今回は年率 3.4%で毎年変更するというトレンドである。LOP および LSTP はそれぞれ 2 年および 3~4 年横ばいの階段状になっており、それぞれ年率 3.3%および 2.6%の低減となっている。HP と LOP は動作時の消費電力をスケーリングするため同程度の低減率で Vdd を下げる必要がある。LSTP は小さなサブスレショルドリーク電流を維持する必要性から Vt が高く設定されており、Vdd の低減率を小さくしてゲートオーバードライブを確保する必要があるため低減が緩やかになっている。

図表 7-12 は、Vdd と Vt から計算したゲートオーバードライブのトレンドである。UTB FD および MG は Bulk と比較してサブスレショルドスロープを小さくできるため同一のサブスレショルドリーク電流に関して Vt が低くでき、結果としてオーバードライブを大きくできる。前述したような Vdd の低減により、ゲートオーバードライブの低減率は年率 5~6%となっており、MOSFET の特性ばらつきに与える影響が大きくなってくる。

図表 7-12 ゲートオーバードライブのトレンド.

### 7-2-5-3 EOT のスケーリングトレンド

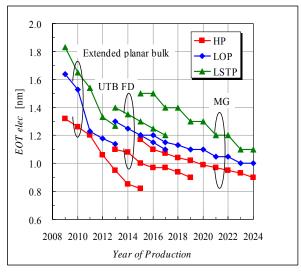

図表 7-13 に EOT(Electrical Oxide Thickness)で表したゲート絶縁膜厚のトレンドを示す。Bulk から UTB FD、 MG と推移するごとに 0.1~0.2nm 厚くするというコンセプトで設定している。Bulk の場合、CV/I の年率 13%向 上を達成するためにゲート容量を大きくする必要があり、EOT の低減率を年率 9%程度と大きくしている。UTB FD および MG では、EOT の削減率は年率 3%程度である。

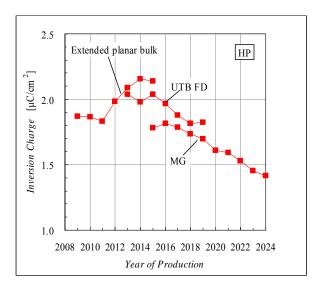

図表 7-13 に示したようなスケーリングを行うと、反転層電荷密度(簡易的に計算)が長期的には年々低下す るという結果になる。 図表 7-14 に HP の場合を示す。 UTB FD と MG において、EOT を薄くして反転層電荷密 度の低下を防ぐという考え方もあり、今後検討していく必要がある。

図表 7-13 電気的 EOT のトレンド.

図表 7-14 反転層電荷密度のトレンド. (HP のみ図示)

## 7-3 メモリデバイス

#### 7-3-1 ITRS2009 における主な改定内容

ITRS2009 では DRAM、及び NAND フラッシュメモリに関しては内外大手メーカーに日本 PIDS が主導しサーベイを行い更新した。また、NVM では NOR、PCRAM についても現状に合わせて更新した。

## 7-3-2 DRAM に関する動向

## 7-3-2-1 ITRS2009 の DRAM ロードマップの要点

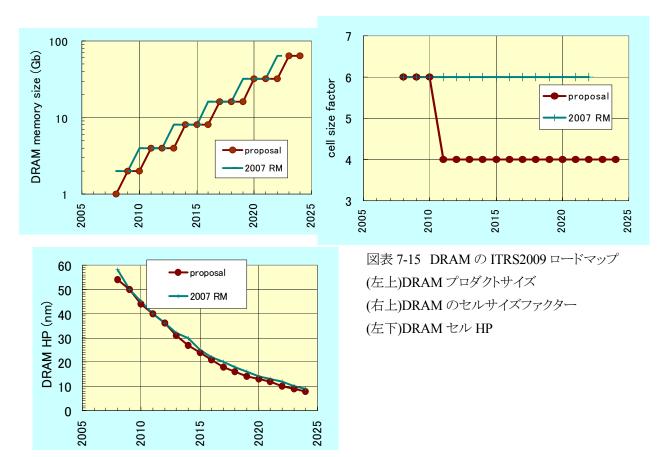

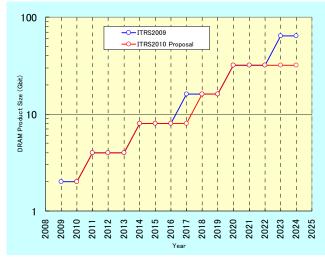

ITRS2009 では DRAM のセルサイズファクターについて 2 社が 2011 年から 4F2 の移行を表明した点が、 非常に大きな変更となっている。しかしながら、DRAM Half Pitch については ITRS2007 以降変更のない結果 であった。製品容量も増大も一年遅れの結果となっている。

## 7-3-2-2 ITRS2010 DRAM ロードマップ向けサーベイ項目並びにサーベイ結果、並びに DRAM の動向

ITRS2010 作成のためのアンケート調査を行った。DRAM 各社とも需要が増大し、2010 年に入ってから多数の DRAM 微細化におけるプレスリリースがなされている中でのサーベイとなった。サーベイの送付先は、大手4 社であり、本年度は Qimonda 社には送付していない。

#### 7-3-2-3 アンケート項目

ITRS2010 向けに実施したアンケート項目を図表 7-16 に示す。緑、赤、青の印で、Overall、PIDS 及び FEPのテーブルに記載のある項目を示した。

Overall Table

PIDS Table

FEP Table

- 1. DRAM half pitch (minimum feature size : F)

- • 2. Cell size : Acell

- • 3. Cell size factor :  $a [Acell = a F^2]$

- 4. DRAM Product (bit): b

- 5. Chip size : Achip

- 6. Area factor [ = Acell x b / Achip]

- 7. Retention time

- 8. Storage Capacitance : Cs

- 9. Voltage of capacitor

- 10. Gate oxide thickness of cell transistor

- 11. Maximum word-line level

- 12. Effective electric field of gate insulator

- 13. Negative word-line use

- 14. Capacitor structure

- 15. Capacitor insulator material

- 16. Effective capacitor insulator thickness

- 17. Physical capacitor insulator thickness

- 18. Support FET (EOT, Ion, Vt)

- 19. Array FET structure

図表 7-16 アンケート項目及びロードマップの項目

## 7-3-2-4 ITRS2010 向けサーベイ結果と技術動向

## 1) DRAM Half Pitch (HP)

アンケートを実施した各社の DRAM の Half pitch を図表 7-17 に示す。2009 年までの傾向とは一転し、2014 年までの期間は一年前倒しでスケーリングが進む。従って2010 年の技術ノードは42nmHP となる。また本年になって米国マイクロン社はプレスリリースで 42nmDRAM 量産を発表した。一時期停滞していたスケーリングの加速はダブルパターニング等の解像度加速技術のDRAMへの導入が進み始めているためと考えられる。

#### 2) DRAM のビット容量

DRAM の容量は、ほぼ ITRS2009 を追従しているが、2016 年以降において、少し集積化が沈滞する。

#### 3) DRAM $\mathcal{O}$ cell size factor

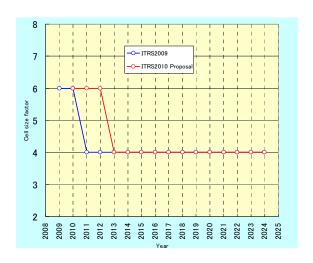

DRAM のセルサイズファクターの推移を図表 7-19 に示す。ITRS2009 では 4F2 への移行を 2 社が 2011 年と表明していたが、ITRS2010 では 2 年遅れ、2013 年に 4F2 化となる。二年後ろ倒しの理由は、縦型トランジスタをはじめとする困難な課題の解決方法の量産レベルへの到達が遅れたことが原因と推測される。

図表7-17 2010 年度版DRAMのHP案

図表7-18 2010 年度版DRAMのビット容量案

図表 7-19 2010 年度版 DRAM の cell size factor 案

### 7-3-3Flash メモリの動向

## 7-3-3-1 NAND Flash の ITRS2009 NAND フラッシュロードマップの要点

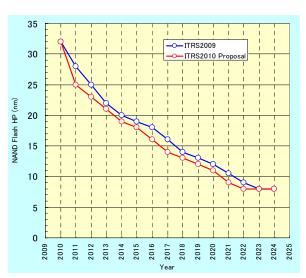

ITRS2009 より、大手各社が一斉にダブルパターニングに代表される解像度加速技術の採用を始めたこと で、露光装置に制約されないスケーリングが可能になり、ハーフピッチのスケーリングが加速した。また 3bit/Cell の実用化も始まり、その先の NAND セルの 3D 化も 2014 年とロードマップの全体の方向性が見えて きた。 一方、通常の浮遊ゲート型 NAND セルの縮小が限界に達した後は上記のように 3D 化されると考えられ るが、各社、詳細部分での技術/方向性は異なっており ITRS2010/2011 ではより方向性を確実に示すことが課 題となった。

なお、ITRS2009の3bit/cell 並びに34nmHPの実現は各社実現しており、ロードマップの検証は行われた。

#### 7-3-3-2 NAND Flash の ITRS2010 に向けたサーベイと技術動向予測

ITRS2010 への改定に当たり、2010年2月より日本 PIDS 主導で大手メーカー4 社のサーベイを実施した。 一番の着目点であるハーフピッチは、2010年の予測では32nmと同じであるが、2011年以降、ITRS2009より1 年前倒しで微細化が進む。技術動向については、2012 年から 2014 年までの間は、浮遊ゲート型とチャージト

ラップ型が混在し、3D化へはITRS2009より一年後ろ倒しとな り 2015 年である。多 Bit/Cell 技術については今回のサーベイ から、4bit/Cell 化への移行を行わない会社が増えており、 3bit/cell が継続していく見込みとなる。4bit/Cell では Vth ウイ ンドウ中に24=16 個の閾値を書込み読み出すために、性能 の劣化が顕著になり、各社ともにメインストリームメモリとしての 4bit/cell 化は難しいと考えていると推測される。

これらの、サーベイ結果と共に、詳しくは今後の各社のプレ スリリースの状況に着目し、数年先までは各会社のプレスリリ ースを考慮、中長期的にはサーベイ結果を勘案したロードマ ップを作成する。また、来年度は ITRS2011 に向けて、 NAND-Flash に関してはサーベイを準備し実施していく。

図表7-20 NANDFlash の 2010 年版の HP 案

#### 7-3-3-3 NOR Flash 動向

NOR Flash に関しては、技術の進展速度が遅くなっており、ITRS2009 では 2010 年の Gate 幅を 90nm から 110nm とし、スケーリングを大きく減速している。90nm の Gate 幅到達は 3 年遅れ 2013 年とした。

#### **7-3-4 FeRAM**

FeRAM は強誘電体キャパシターの極性を変化させ読み取ることで不揮発性を維持している。強誘電体材料は通常の CMOS プロセスにとっては異質であり、特に高温のアニールに耐えられないので微細化を妨げる要因となっている。事実 FeRAM は NOR 及び NAND フラッシュよりも数世代遅れたプロセス世代で製造されており、かつ多値化が実現できない。従って近い将来 NOR あるいは NAND フラッシュを置き換えるということは望めないであろう。しかしながら FeRAM は高速読出し/書換え、低電圧、低消費電力であり、それらの卓越した特性により RFID、スマートカードや他の混載のアプリケーションに最適である。今後の微細化によってアプリケーションに適した大容量化を達成するためにはセル間の分離特性を維持したまま、セルサイズを縮小することが必須である。近年の研究成果からは強誘電体膜の薄膜化が可能であり、更に近い将来2次元型のセル構造が実現されるであろう。それでもなお3次元型のセル構造にはさらなる研究開発が必要である。

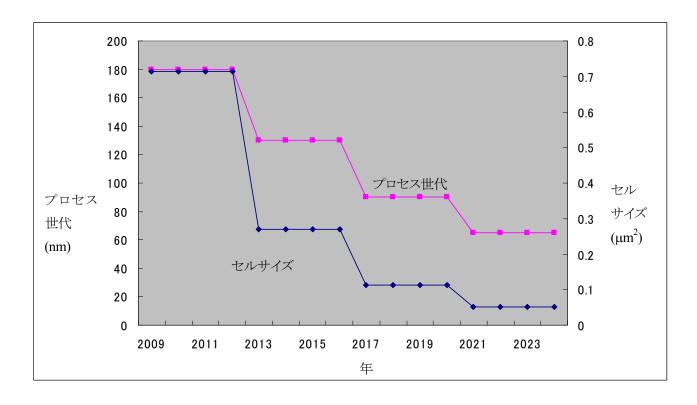

図表 7-21 に FeRAM のプロセス世代とセルサイズの推移を示す。現行の FeRAM の製品のプロセス世代は 180nm である。以降 4 年毎に世代をスケーリングしセルサイズを縮小するという微細化ルールになっている。セル構成は一環して 1T1R 構成であり、セル面積ファクター(F値)を 10 以下にすることは難しい。これは DRAM とは異なりキャパシター面積の縮小が難しいからである。キャパシター構造の点では 2016 年までが積層構造、2017 年からは 3D 構造となっている。このキャパシターの製造方法及び構造がセルサイズを決める重要な要因になっている。用途によっては極めて重要である低電圧化はキャパシターに印加される電圧で決まる。これはキャパシターの膜厚などと密接な関係があり、今後の大きなチャレンジである。FeRAM は破壊読出しであり、読出しサイクルは読出しと書込みの合計時間である。今後 FeRAM が DRAM や SRAMの置換えを狙うためには 1E15 回以上の書換えサイクルが必要である。

図表 7-21 FeRAM のプロセス世代とセルサイズの推移

#### **7-3-5 PCRAM**

PCRAM はカルコゲナイト材料のアモルファスと結晶の抵抗の違いを用いて、"0"と"1"状態を蓄積するメモリである。カルコゲナイト材料には通常 Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>(GST)が用いられている。セルのデバイスは上部電極とカルコゲナイドの相変化層と下部電極の構成である。相変化素子と直列に接続されるトランジスタでリーク電流を遮断する。相変化の書込み動作は、(1)RESET 動作:短いパルス電圧でカルコゲナイド材料が一旦溶解し、素早く高抵抗のアモルファス状態に変異する、(2)SET 動作:100ns 程度のより長いパルス電圧を印加し、材料をアニールすることにより低抵抗の結晶状態にする。1T1R あるいは 1D1R のセル構造は MOSFET かBJT(Bipolar Junction Transistor)が使われるのかによって、NOR フラッシュと比較してセルサイズが小さくも大きくもなる。またこのデバイスは前の状態を消去することなく、"0"と"1"どちらの状態にも書き込めるので高速書込みが可能である。さらに抵抗膜の単純な構造と低電圧動作が混載用途としての PCRAM の魅力である。PCRAM の主な課題は相変化素子をリセットする際の mA オーダーの高電流とセット時間が長いことである。相変化材料の体積は微細化によって縮小することから、上記の2つの課題は微細化の進展に伴い解決される方向である。相変化材料と電極の相互作用は長期信頼性に影響を与え書換え回数を制限するので今後の PCRAM の大きな課題である。PCRAM はページモードを必要としないため DRAM のような真のランダムアクセスメモリである。この特性が特殊な用途を拓くことができるかもしれない。

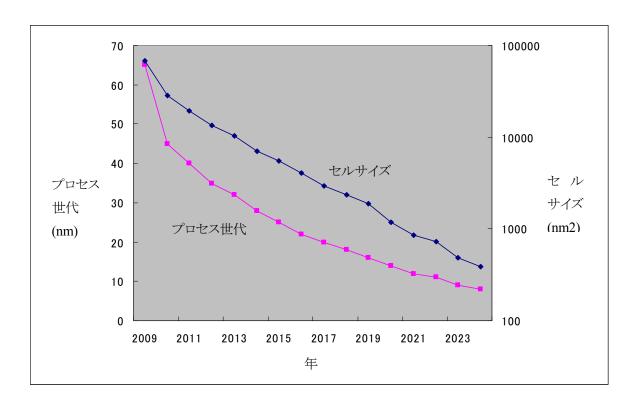

図表 7-22 に PCRAM のプロセス世代と NMOS セルトランジスタを仮定した場合のセルサイズの推移を示す。現行世代は 65nm であり、以降、2 年毎に 1 世代という CMOS と同じシナリオで微細化することが期待されている。これは FeRAM とは異なり抵抗素子の縮小が比較的容易であり、かつ抵抗素子の微細化により性能もスケーリングされ向上することが大きな理由である。セル面積ファクター(F値)は将来的には DRAM 並みの 6 を目指す。 さらに PCRAM はアモルファスと結晶の抵抗値の差が 100-1000 あることからが多値化が可能である。図表 7-22 のセルサイズは面積を単純に表したものであるが、2011 年から 2bit/cell が導入される予定になっており、面積を bit あたりで考えるとこの 1/2 になることで競争力が高まることが期待される。

図表 7-22 PCRAM のプロセス世代とセルサイズの推移

#### 7-3-5 MRAM

ITRS2009 での MRAM ロードマップは、テーブル構成と記載数値が ITRS2008update から大きく変更になった。実際に製品化されている磁界書込み方式 MRAM と将来の微細化世代で製品化が期待されるスピン注入書込み方式(STT: Spin Transfer Torque)MRAMに分けて、2 つのテーブル構成となった。ITRS2009 の製品化されているMRAM数値は、現製品の実態およびアナウンスされている製品化計画を反映させて精度を上げている。MRAM製品事業を行っている EVERSPIN 社は、既に製品化されている磁界書込み方式による汎用MRAM製品群 256kb、1Mb、2Mb、4Mbに加えて、2010 年には 130nm 世代技術を用いた 16MbMRAMの製品出荷を計画している。磁界書込み方式 MRAMは、今後、更なる大容量化に向けて 90nm 世代さらに65nm 世代へと微細化の進展が期待されるものの、65nm 世代に於いて技術限界に到達すると考えられる。

図表 7-23 に示すように STT-MRAM は、磁界書込み方式の 65nm 世代での技術限界を打破する技術として期待されている。スピン注入書込み方式では素子が微細化されると書込み電流が原理的に減少するため、データ保持における熱安定性の向上などに適した方式である。 STT-MRAM の製品化アナウンスは未だないものの、大容量化およびシステム LSI 混載に向けて研究開発は着実に進展している。 国際学会 VLSI Circuits 2009 において、32Mb STT-MRAM [1]や MRAM 基本素子である MTJ(Magnetic Tunnel Junction)の自由層を積層フェリ構成にすることにより、150℃における熱擾乱係数  $Ek_BT$  を64 へ向上させた報告[2]があった。 IEDM 2009では、1T-1R セルで選択トランジスタとMTJの接続を従来と反対の自由層側に接続することで動作マージが拡大し、セル面積  $0.1026 \mu$  m² の 45nm Low Power CMOS ロジック向けの最大 32Mb 混載 STT-MRAM が報告された[3]。また、ISSCC 2010では、130nm 世代技術を用いた 16kb STT-MRAM で負抵抗読出し書込み方式によって、読出し時間/書込み時間が 10sec 以下を達成したという報告[4]や 65nm 世代技術を用い垂直TMR(Tunnel Magneto-Resistance)方式の適用により、書込み電流を大幅に低減してスイッチングトランジスタのサイズを縮小し、汎用メモリレベルのチップ面積 47.124 mm²を実現した SRAM 互換の 64Mb STT-MRAM の報告 [5]もあった。 STT-MRAM による、Gbit級の大容量不揮発RAMの実現が期待される。

- [1] R. Takemura, et. al., Symp. VLSI Circuits Digest of Technical Papers, p.84, 2009.

- [2] K. Ono, et. al., Symp. VLSI Technologys Digest of Technical Papers, p.228, 2009.

- [3] C. J. Lin, et. al., IEDM Technical Digest, p.279, 2009.

- [4] D. Halupka, et. al., ISSCC 2010 Digest of Papers, p.256, 2010.

- [5] K. Tsuchida, et. al., ISSCC 2010 Digest of Papers, p.258, 2010.

| Year of Production                  | 2009  | 2010  | 2011             | 2012             | 2013             | 2014             | 2015             | 2016  | 2017  | 2018  |

|-------------------------------------|-------|-------|------------------|------------------|------------------|------------------|------------------|-------|-------|-------|

| Technology node F (nm)              | 130   | 130   | 90/65            | 90/65            | 65/45            | 65/45            | 65/45            | 32    | 32    | 32    |

| Cell 構造                             | Field | Field | Field/<br>STT    | Field/<br>STT    | Field/<br>STT    | Field/<br>STT    | Field/<br>STT    | STT   | STT   | STT   |

| cell size area factor               | 45    | 45    | 45/20            | 45/20            | 45/15            | 45/15            | 45/15            | 10    | 10    | 10    |

| cell size (um2)                     | 0.76  | 0.76  | 0.36/<br>0.08    | 0.36/<br>0.08    | 0.19/<br>0.03    | 0.19/<br>0.03    | 0.19/<br>0.03    | 0.010 | 0.010 | 0.010 |

| switching field (Oe)                | 35    | 35    | 55/NA            | 55/NA            | 70/NA            | 70/NA            | 70/NA            | N/A   | N/A   | N/A   |

| switching current (uA)              | N/A   | N/A   | NA/250           | NA/250           | NA/150           | NA/150           | NA/150           | 50    | 50    | 50    |

| write energy (pJ/bit)               | 150   | 150   | 105/2.5          | 105/2.5          | 80/1.5           | 80/1.5           | 80/1.5           | 0.3   | 0.3   | 0.3   |

| active area per cell (um2)          | 0.1   | 0.1   | 0.1/<br>0.015    | 0.1/<br>0.015    | 0.07/<br>0.007   | 0.07/<br>0.007   | 0.07/<br>0.007   | 0.004 | 0.004 | 0.004 |

| resistance(Kohm-um2)                | 1.3   | 1.3   | 1.3/0.0<br>15    | 1.3/0.0<br>15    | 0.9/0.0<br>1     | 0.9/0.0<br>1     | 0.9/0.0<br>1     | 0.01  | 0.01  | 0.01  |

| magnetoresistance ratio (%)         | 45    | 45    | 120              | 120              | 150              | 150              | 150              | 150   | 150   | 150   |

| data retention (years)              | >10   | >10   | >10              | >10              | >10              | >10              | >10              | >10   | >10   | >10   |

| endurance (read/write cycles)       | >3e16 | >3e16 | >3e16 /<br>>1e12 | >1e15 | >1e15 | >1e15 |

| tunnel junction reliability (years) | >10   | >10   | >10              | >10              | >10              | >10              | >10              | >10   | >10   | >10   |

図表 7-23 スピン注入書込み方式(STT: Spin Transfer Torque)MRAM

## 7-4 RF/Wireless 関連デバイス

Radio Frequency and Analog/Mixed-signal Technologies for Wireless Communications の章は、ITRS2005からPIDS の章から独立し、2007年を経てITRS2009で、2度目の大幅な改訂を行った。そこで、テーブルだけでなく全体の構成についても議論し、改訂を行った。ITRS2007策定時、従来のロードマップが、アプリケーションを主体としていたため、デバイステクノロジーの方向を診るのに不都合と考え、CMOS や bipolar といったデバイス主体に整理を行った。しかし、RF/wireless 分野では、アプリケーションに触発される形で、活発な新デバイスの開発が行われるため、デバイス毎に括ることが困難なことがわかってきた。例えば、ITRS2007では AMS CMOS のテーブルに、新たにミリ波 CMOS を加えることにした。しかし、~10GHz 帯を目指す従来の CMOS デバイスと並べる意味は少なく、ミリ波応用デバイス同士を比べる必要がある。そこで、ITRS2009では、基本的構想として、再びアプリケーションを主体としたものにシフトした構成を目指した。また、ITRS2008の修正で初めて加筆した、RF/Wireless 関連デバイスの幾つかのテーブル策定において、ロードマップの、いわゆる ITRSの"製品(量産)"ではなく、プロトタイプを基にしたことを、本文中に明記し、明確なものにしている。

構成の変更としては、ITRS2007 で More than Moore として取り上げていた MEMS をサブ WG の一つに格上げし、AMS CMOS、AMS bipolar、Power Amp、Passive、ミリ波、MEMS の6サブ WG のテーブルとしたこと、また More than Moore の節では MEMS に代えて、heterogeneous integration の検討を行ったことが挙げられる。RF/Wireless 分野のアプリケーションを考えた場合、チップに異種デバイスを集積することが求められるものと考えられる。そのため、More than Moore としてこの記述を行ったことは、2度のメジャー改訂を行うことで、RF/Wireless 関連デバイスのロードマップ策定上の課題が、はっきりと認識されるようになってきた証とみることができる。以下、各サブ WG の ITRS2009 における改訂のポイントについて記す。

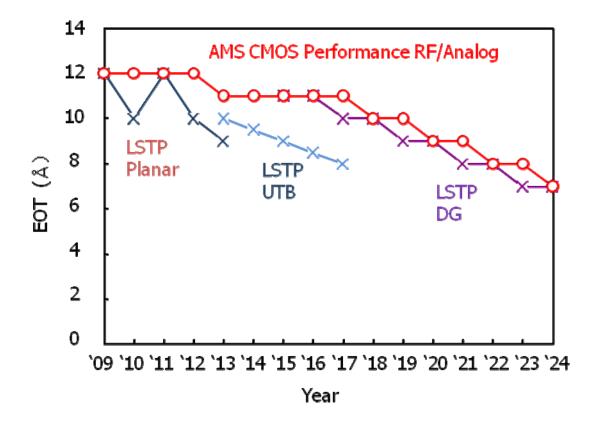

AMS CMOS のテーブルの特長は、ITRS2007でテーブルに加えたミリ波 CMOS を、ミリ波 WG のテーブルに集約し、CMOS のテーブルから削除したことが挙げられる。また、従来、PIDS の LSTP デバイスに対して 1 年遅れとして設定していた Performance RF/Analog CMOS についても、基本的には、従来の LSTP に対して 1 年遅れを踏襲しつつ、RF 応用においては、デバイスのパラレルパスが現実的ではないものと考え、独自のテーブルを策定することとなった。PIDS のテーブルに比べ、ゲート絶縁膜のスケーリングを、緩やかなものとしている(図表 7-24 参照)。またメタルゲート/ハイk の導入が RF 特性に与える影響についてまだ十分な知見が得られていないとの認識から 2012 年の導入時期に合わせ全ての項目を黄色の表示とし、Double gate の導入(2015年)については、更に検討が必要との認識から、全ての項目で赤色での表示を行っている。この様子について、PIDS との比較を行い、図表 7-25 に示した。

また、CMOS テーブルの特長として、availability optional analog/high-voltage FETs の項を加えたことが挙げられる。これまで、RF での実用的なチップを考えた場合、RF 回路部では、IO 系などで用いる高耐圧系素子を援用してきたが、Core 系に High-K/metal gate や Double gate を持ったデバイスを用いた場合に、同じ手法が用いることができるか、極めて疑問に思えるためである。そこで、技術課題として optional device の混載を挙げることにしたものである。

Bipolar では従来通り SiGe HBT LSI を対象としている。ITRS2008update では High-speed (HS) NPN、High-Voltage (HV) NPN、Power Amplifier (PA) NPN のロードマップを示したが、HV-NPN をテーブルからはずし、High-speed (HS) PNP を新たに加えたことが ITRS2009 の大きな変化点である。

HS NPN のトレンドを決めるアプリケーションは 60 GHz WPAN、77-79 GHz 車載レーダー、94 GHz イメージング、さらにはギガビットイーサといったミリ波応用の製品である。HS PNP のアプリケーションは HDD、DVD、TFT ドライバ、高精細ビデオ、DAC/ADC などであり、これらには特性がほぼマッチした NPN と PNP を組み合わせた Complimentary BiCMOS 技術が必要となる。C-BiCMOS の必要性を述べている点が ITRS2009 の特徴である。 PA NPN のアプリケーションは従来通り WCDMA や GSM と言った 0.9 – 2 GHz 帯の RF トランシー

バーモジュールである。

現在 HS-BiCMOS で使われる CMOS の世代は 180 nm から 130 nm であり、最先端 CMOS とは 3 から 4 世代遅れたものである。これは最先端 CMOS による高密度ロジック LSI を必要とする BiCMOS プロダクトが無いことと、最先端 CMOS を混載するコストメリットが少ないためである。しかしながら、ピュア CMOS では実現できないような、ミリ波向け SOC として 65 nm あるいは 45 nm BiCMOS が近い将来必要になると思われる。 C-BiCMOS あるいは PA-BiCMOS については、HS-BiCMOS よりもさらに古い世代の CMOS で十分であり、この場合はコストが最優先となる。

ミリ波では、fT が最大となるピーク電流値をテーブルから削除した。これはデバイスデザインやアプリケーションで決まるものではないためである。さらに SiGe HBT デバイスの Maximum Available Gain (MAG)の値を追記し、ミリ波 GaN Power HEMT の生産を 2010 年から、としてロードマップを作成した。従来からの傾向として、ミリ波向けデバイスはどの周波数においても、ある限られたデバイスが最適である、という状況にはならず、材料は GaAs、InP、GaN、Si、SiGe、デバイスはバイポーラと FET と多様なロードマップが引かれている。しかしながら、GaAs PHEMT は InP HEMT あるいは GaAs MHEMT に、GaAs Power MHEMT は GaN power MHEMT にとって変わられる、と予想している。RF CMOS は ITRS 2007 からミリ波に加えられた。そのトレンドは PIDS の High performance デバイスに準拠している。

オンチップ受動素子は従来通り、Analog、RF、Power Amplifier の 3 つのアプリケーションに対して容量、抵抗、インダクター、バラクターのテーブルを載せている。RF 容量に Metal-oxide-metal (MOM)を加えた点が変化点である。

オフチップ受動素子は、有機及び無機材料基板に対し、抵抗、容量、インダクターのトレンドと、密度、信頼性、温度特性、共振周波数及び耐圧の項目を載せている。

パワーアンプはハンドセット用とベースステーション用のロードマップを示している。ハンドセット向けのテーブルには、従来の nominal 電源電圧に加え、end-of-life 電源電圧をロードマップに示した点が変更点である。 バイアス回路や、オンチップスイッチの集積化に向けて FET と HBT の集積化を予想しているが明確なロードマップは描けていない。 ベースステーション向けは、GaAs のロードマップを削除した点が大きな変化点である。 これは、高周波特性、パワー密度、トータル RF パワーで優れる GaN 技術にフォーカスしたためである。

MEMS は、ITRS2007では、More than Moore の項として、初めてテーブル化したものを、今回の改訂で、サブ WG の一つとして格上げを行った。そのため、「Require Table」だけでなく、「challenge」など、すべての項目に MEMS について記述を行っている。ファウンダリにおいても MEMS がメニューとして提供されるようになり、多数の実製品が市場に登場するようになったことが背景にある。しかし、2007年版同様、ある程度製品の見えている4種の特定デバイス(BAW、Resonator、Capacitive contact Switch、metal contact Switch)を取り上げ、Design tools、Performance Driver、Cost Driverの項目からロードマップテーブルを策定している。また、これらの項目について、現状に合わせたアップデータを行っている。サブ WG に格上げしても、大幅な改訂をすることができなかったことは、MEMS のように、アプリが多岐にわたる場合、技術開発のための方向性を、テーブルにより表現することの難しさが、改めて明らかになったものと考えられる。

RF/Wireless は、ITRS2007の MEMS を導入するなど、More than Moore(MtM)について、最も注目され、かっ活発に活動している WG である。ITRS2009では、サブ WG に格上げした MEMS に代えて、Heterogeneous Integration を、MtM として記載している。RF/Wirelessのアプリを考えた場合、シリコンと化合物系半導体などの、異種デバイスの集積というのは、極めて現実的かつ重要な項目として考えることができる。記述された内容は、テクノロジ的な予測というより、アプリ側からの希望を述べたレベルに留まっている。しかし、MtMを考えたとき、重要なポイントを追加したものと考えている。

図表 7-24 PIDS LSTP と AMS CMOS のゲート絶縁膜のテーブル比較

|                                                 |               |         |        | HK/M   | G導入  |      | UTB/[ | OG導入 |

|-------------------------------------------------|---------------|---------|--------|--------|------|------|-------|------|

| Year of Production                              | 2009          | 2010    | 2011   | 2012   | 2013 | 2014 | 2015  | 2016 |

| Performance RF/Analog                           |               |         |        |        |      |      |       |      |

| Supply Voltage (V)                              | 1.1           | 1.05    | 1.05   | 1.05   | 1.0  | 0.95 | 0.95  | 0.95 |

| Tox (nm)                                        | 1.2           | 1.2     | 1.2    | 1.2    | 1.1  | 1.1  | 1.1   | 1.1  |

| Gate Length (nm)                                | 38            | 38      | 32     | 29     | 27   | 22   | 18    | 17   |

| gm/gds at 5Lmin-digital                         | 30            | 30      | 30     | 30     | 30   | 30   | 30    | 30   |

| 1/f-noise (μV <sup>2</sup> μm <sup>2</sup> /Hz) | 100           | 90      | 80     | 70     | 70   | 60   | 50    | 50   |

| Precision Analog/RF Driver                      |               |         |        |        |      |      |       |      |

| Supply Voltage (V)                              | 2.5           | 1.8     | 1.8    | 1.8    | 1.8  | 1.8  | 1.8   | 1.8  |

| Tox (nm)                                        | 5             | 3       | 3      | 3      | 3    | 3    | 3     | 3    |

| Gate Length (nm)                                | <u> </u>      | 180     | 180    | 180    | 180  | 180  | 180   | 180  |

| 新規注                                             | <b>旦川</b><br> | 160     | 160    | 160    | 160  | 160  | 160   | 160  |

| 1/f-noise (μV²μm²/Hz)                           | 1000          | 360     | 360    | 360    | 360  | 360  | 360   | 360  |

| Availability of optional analog /               | limited       | limited | common | common | wide | wide | wide  | wide |

| CMOS NFET [1 HP CMOS lag 2 yrs]                 | ■HP (         | MOSを    | mm-Wa  | veに集   | 約 削除 |      |       |      |

図表 7-25 2009 年版 AMS CMOS テーブルの概要

## 7-5 まとめと今後の課題

ロジックデバイスでは、HP、LOP、LSTPのゲート長スケーリングがITRS2007よりそれぞれ、4年、3年、1年と大きく後ろ倒しされ、ロジックデバイスのゲート長スケーリングの鈍化が徐々に進みつつある。また、HPのスケーリングの鈍化が大きく、ゲート長だけ見るとHP、LOP、LSTPの差が小さくなってきている。一方、メモリデバイスでは、NANDフラッシュは、1年前倒し、DRAMは、メモリセルファクター4F2の微細セルの登場など、スケーリングが加速してきている。特にNANDフラッシュでは、更に微細化が加速する傾向にある。微細化でリソグラフィ装置に依存しないダブルパターニングやトリプルパターニングなどの微細化手法が開発され、繰り返しパターンが多く、この微細化手法を導入しやすいメモリの微細化は進み、ランダムパターンが多いロジックでは、この微細化手法が使えずに、スケーリングが鈍化してきている。今後、リソグラフィ装置の進展具合によっては、ロジックデバイススケーリングの鈍化とメモリデバイススケーリングの加速が、更に進むと予想される。

ロジックデバイスにおけるデバイスの分類も検討が必要となってきている。従来、携帯電話に代表されるモバイル機器は、待機時の消費電力の少ない LSTP が主流であった。ところが、ここ 1、2 年で Smart Phone といったコンピュータに匹敵する性能を持ちインターネットが行えるモバイル機器が主流になりつつあり、LSTP でも LOP の性能、或いは、1.5GHz 近くで動作する HP に近い性能が必要となってきている。微細化の進展で HP、LOP、LSTP のゲート長差が小さくなってきていることと相まって、今後、これら HP、LOP、LSTP の区別が無くなっていくものと考えられ、HP、LOP、LSTP といったデバイスの分類の見直しが必要となってきた。

ITRS2009 では、HP のみではあるが、今までのトランジスタの遅延時間 CV/I に代わる新しい指標としてリングオシレータのスイッチング速度を追加し、回路レベルでトランジスタ性能も評価する試みがなされた。ロジックデバイスのロードマップは、ゲート長の微細化に比例して CV/I の改善率を一定に保つように作成されており、今後も一定の CV/I の改善率を維持するには、微細化の鈍化に対応したゲート長以外のこのような新しいスケーリングコンセプトを構築してゆく必要がある。現在、ITRS2010 に向けて、EOT と Vdd のスケーリングに着目した新しいスケーリングコンセプトを検討している。

ハイk/メタルゲート導入に関して、最もゲート長スケーリングが緩やかな LSTP でも 3 年も後倒しされ、HP の 2 年遅れの 2011 年からとなった。2010 年後半には、複数メーカーから、ハイ k /メタルゲート構造を採用した 32-28nm 世代 CMOS のサンプルが出荷されると予想される。この世代では、45nm 世代で量産実績のあるゲートラスト方式に加えて、従来プロセスとの整合性の良いゲートファースト方式で量産する企業も現れるであろう。 次の 22nm 世代に向けては、更なる薄膜化と、キャップ/添加材料の改良による仕事関数の最適化が必要と考えられる。

性能改善に向けた Strain 技術に関しては、2009 年に於いて Strain による移動度改善は既に限界値に達しており、今後、微細化と伴にバリスティック輸送によるドレイン電流改善率が除々に増え、他の Booster 効果の飽和傾向を補うシナリオとなっている。一方で、ストレス膜やソース/ドレインエピ技術をゲートラストプロセスと組み合わせると、ダミーゲートを除去する工程で大きなチャネル歪を発生させることが明らかになっており、特にホール移動度の向上が著しく、PMOS の駆動能力が大きく伸び、従来のデバイストレンドと異なっている。今後は、ゲートファーストとゲートラストでは分けて考える必要性も出てくる可能性がある。

DRAM に関しては、ITRS2009 では DRAM のセルサイズファクターについて 2 社が 2011 年から 4F2 の移行を表明した点が、非常に大きな変更となっている。しかしながら、ITRS2010 に向けて新たにサーベイを行った結果、4F2 化は、2 年遅れの 2013 年となる模様である。4F2 化には、縦型トランジスタなど難題が山積しており、量産にはもう少し時間が掛かるものと思われる。ハーフピッチのスケーリングは、ITRS2010 では、ITRS2009とは一転し、ダブルパターニング等の解像度加速技術の導入が進み 2014 年まで一年前倒しでスケーリングが進むと予想される。

NAND Flash に関しては、ITRS2009 では、ダブルパターニングの解像度加速技術により、ハーフピッチのスケーリングが加速し、1 年前倒しされた。ITRS2010 に向けたサーベイでは、更に 1 年前倒しとなっており、スケーリングが加速する傾向にある。2012 年から 2014 年までの間は、浮遊ゲート型とチャージトラップ型が混在し、3D 化へは 2015 年である。また、ITRS2010 のサーベイでは、多 Bit セル化(4bit/Cell 化)への移行を行わない会社が増えており、3bit/cell が続く見込みである。4bit/cell 化では、小さい Vth ウインドウ中に 2<sup>4</sup>=16 個の閾値を書込み読み出すために、性能の劣化が顕著になり、各社ともにメインストリームメモリとしては難しいと考えていると推測される。

FeRAM は強誘電体材料の耐熱性の課題から微細化が困難なため、スケーリングは NAND フラッシュよりも数世代遅れている。現行世代は 180nm であり、4 年毎に世代をスケーリングする。しかしながら FeRAM は高速読出し/書換え、低電圧、低消費電力であり、RFID、スマートカードや他の混載のアプリケーションに最適である。セルは 1T1R 構成であり、キャパシター構造は 2016 年までが積層構造、2017 年からは 3D 構造となっている。今後、DRAM や SRAM の置換えを狙うためには 1E15 回以上の書換えサイクルが必要である。

PCRAM の現行世代は65nmであり、2年毎に1世代というCMOSと同じシナリオで微細化することが期待されている。抵抗素子の縮小が比較的容易であり、微細化により性能も向上することが大きな理由である。セル面積ファクター(F値)は将来的にはDRAM並みの6を目指す。さらにPCRAMはアモルファスと結晶の抵抗値の差が100-1000あることから、多値化が可能で2011年から2bit/cellが導入されると予想される。

MRAM は、実際に製品化されている磁界書込み方式 MRAM と将来のスピン注入書込み方式(STT: Spin Transfer Torque)MRAMに分けて、2 つのテーブル構成となった。EVERSPIN 社は、磁界書込み方式のMRAM製品群 256kb、1Mb、2Mb、4Mbに加えて、2010年には130nm世代技術を用いた16MbMRAMの製品出荷を計画している。この磁界書込み方式 MRAMは、65nm世代において技術限界に到達すると考えられる。次に来ると考えられるスピン注入書込み方式のSTT-MRAMの製品化アナウンスは未だないものの、大容量化およびシステムLSI 混載に向けて研究開発は着実に進展しており、多くの学会発表が行われている。

RF & A/MS は、再びアプリケーションを主体とした構成になった。スケーリングは基本的には、LSTP に対して 1 年遅れで、ゲート絶縁膜のスケーリングはロジックよりも、緩やかなものとしている。アプリケーションは、AMS CMOS、AMS bipolar、Power Amp、Passive、ミリ波、MEMS の6種類である。MEMS が More than Moore から格上げされたのは、多数の実製品が市場に登場するようになったことが背景にあるが、アプリケーションが多岐に渡り、テーブルに表現することが難しく、格上げしても、大幅な改訂をすることができなかった。今後の課題として、更なる細分化などの検討を続ける。

More than Moore の節では MEMS に代えて、heterogeneous integration の検討を行っている。RF/Wireless のアプリを考えた場合、シリコンと化合物系半導体などの異種デバイスの集積(Heterogeneous Integration)というのは、極めて現実的で、かつ重要な項目と考えている。