# システムドライバ

## 概要

将来の半導体の生産能力および設計技術は、世界の半導体産業を牽引するドライバ商品からの要求に応じて開発されている。ITRS は、そのビジネスおよび機械設備の改善を行うサイクルが半導体領域をドライブする製品分野のための技術的要求がどのように発生するかを把握する必要がある。2001 年までは、ITRS 報告書で、マイクロプロセッサ(MPU)、ダイナミック・ランダムアクセス・メモリ(DRAM)および特定用途向け IC(ASIC)の各製品分野に注目し、システム・オン・チップ(SOC)およびアナログ・ミックスド・シグナル回路にも触れた。暗黙の仮定として、継続的な技術進歩が全ての半導体製品に対して展開するだろうと考えられたため、個々の製品分野(たとえば MPU あるいは ASIC)の詳細に関しては触れなかった。今日、各商品はそれぞれ異なった技術の組合せを要求するため新しい技術導入はますます応用製品がドライブする傾向にある。パソコン用の汎用マイクロプロセッサとともに無線通信や組込み応用のためのミックスド・シグナル・システムもこのようなドライバとなっている。テクノロジ・ドライバは、今や据え置き型サーバよりは、むしろバッテリ駆動のモバイル・デバイスに移っている。従来組織内だけで行われてきた、シングルソースのチップ設計は、マルチソースからのビルディングブロック方式の設計スタイルによる SOC やシステム・イン・パッケージ(SIP)の設計によって取って代わられている。

2005 年版 ITRS システム・ドライバ章では、以前の ITRS 報告書で議論したシステム・ドライバを更新し、より明白な定義付けを試みている。全般的なロードマップ技術特性と一緒に、システム・ドライバの章は、それぞれの ITRS 技術領域と ITRS の 15 年の期間を通じた技術的要求のための首尾一貫したフレームワークおよび動機づけを提供している。この章の主要な目的は、将来の技術へ外挿でき、将来の技術開発にもっと滑らかに適合するシステム・ドライバの、定量的で内部に自己矛盾がないモデルを構築することである。私たちは次の4つのシステム・ドライバに注目する: システム・オン・チップ(SOC)、マイクロプロセッサ(MPU)、アナログ・ミックスド・シグナル(AMS)、および、混載メモリである。まず、これらのシステム・ドライバについて述べる前に、半導体製品の主要なマーケット・ドライバについて概観する。また、読者は International Electronics Manufacturing(iNEMI) roadmap (http://www.inemi.org)も参照いただきたい。

## マーケット・ドライバ

Table 8 では製造規模、ダイサイズ、複合技術の集積、システムの複雑さ、タイムトゥマーケットのような要因によって半導体製品市場を対比している。この表で、各分野における SOC、AMS、MPU への影響が示されている。 <sup>1</sup>

-

<sup>&</sup>lt;sup>1</sup> The market drivers are most clearly segmented according to cost, time-to-market, and production volume. System cost is equal to Manufacturing cost + Design cost. Manufacturing cost breaks down further into non-recurring engineering (NRE) cost (masks, tools, etc.) and silicon cost (raw wafers + processing + test). The total system depends on function, number of I/Os, package cost, power and speed. Different regions of the (Manufacturing Volume, Time To Market, System Complexity) space are best served by FPGA, Structured-ASIC, or SOC implementation fabrics, and by single-die or system-in-package integration. This partitioning is continually evolving.

*Table 8* Major Product Market Segments and Impact on System Drivers

| Market Drivers                                                                                                                                                                                            | SOC                                                                                                                                                                                                      | Analog/MS                                                                                                                                                                                                           | MPU                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I. Portable/consumer                                                                                                                                                                                      |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                               |

| 1. Size/weight ratio: peak in 2004 2. Battery life: peak in 2004 3. Function: 2×/2 years 4. Time-to-market: ASAP                                                                                          | Low power paramount  Need SOC integration (DSP, MPU, I/O cores, etc.)                                                                                                                                    | Migrating on-chip for voice<br>processing, A/D sampling, and<br>even for some RF transceiver<br>function                                                                                                            | Specialized cores to optimize processing per microwatt                                                                                                                                        |

| II. Medical                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                               |

| 1. Cost: slight downward pressure     (~1/2 every 5 years) 2. Time-to-market: >12 mos 3. Function: new on-chip functions 4. Form factor often not important 5. Durability/safety 6. Conservation/ ecology | High-end products only. Reprogrammability possible. Mainly ASSP, especially for patient data storage and telemedicine; more SOC for high-end digital with cores for imaging, real-time diagnostics, etc. | Absolutely necessary for physical measurement and response but may not be integrated on chip                                                                                                                        | Often used for programmability especially when real-time performance is not important.  Recent advances in multi-core processors have made programmability and real-time performance possible |

| III. Networking and communication                                                                                                                                                                         | ons                                                                                                                                                                                                      | T                                                                                                                                                                                                                   |                                                                                                                                                                                               |

| 1. Bandwidth: 4×/3–4 yrs.<br>2. Reliability<br>3. Time-to-market: ASAP<br>4. Power: W/m³ of system                                                                                                        | Large gate counts High reliability More reprogrammability to accommodate custom functions                                                                                                                | Migrating on-chip for MUX/DEMUX circuitry  MEMS for optical switching.                                                                                                                                              | MPU cores, FPGA cores and some specialized functions                                                                                                                                          |

| IV. Defense                                                                                                                                                                                               |                                                                                                                                                                                                          | T                                                                                                                                                                                                                   |                                                                                                                                                                                               |

| Cost: not prime concern     Time-to-market: >12 mos     Function: mostly on SW to ride technology curve     Form factor may be important     High durability/safety                                       | Most case leverage existing processors but some requirements may drive towards single-chip designs with programmability                                                                                  | Absolutely necessary for physical measurement and response but may not be integrated on chip                                                                                                                        | Often used for programmability especially when real-time performance is not important  Recent advances in multi-core processors have made programmability and real-time performance possible  |

| V. Office                                                                                                                                                                                                 |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                               |

|                                                                                                                                                                                                           | Large gate counts  High speed  Drives demand for digital functionality  Primarily SOC integration of custom off-the-shelf MPU and I/O cores                                                              | Minimal on-chip analog  Simple A/D and D/A  Video i/f for automated camera monitoring, video conferencing  Integrated high-speed A/D, D/A for monitoring, instrumentation, and range-speed-pos resolution           | MPU cores and some specialized functions  Increased industry partnerships on common designs to reduce development costs (requires data sharing and reuse across multiple design systems)      |

| VI. Automotive                                                                                                                                                                                            |                                                                                                                                                                                                          |                                                                                                                                                                                                                     |                                                                                                                                                                                               |

| Functionality     Ruggedness (external environment, noise)     Reliability and safety     Cost                                                                                                            | Mainly entertainment systems.  Mainly ASSP, but increasing SOC for high end using standard HW platforms with RTOS kernel, embedded software.                                                             | Cost-driven on-chip A/D and D/A for sensor and actuators  Signal processing shifting to DSP for voice, visual  Physical measurement ("communicating sensors" for proximity, motion, positioning).  MEMS for sensors |                                                                                                                                                                                               |

DEMUX—demultiplexer

FPGA—field programmable gate array

2005

i/f—intermediate frequency

DSP—digital signal processing I/O—input/output HW—hardware

MEMS—microelectromechanical systems

MUX—multiplex

RTOS—real-time operating system

## システム・オン・チップ・ドライバ

SOC は今後も発展の見込める製品分野および設計スタイルである。重要なことは、SOC は他のシステム・ドライバ分野(MPU、混載メモリ、AMS、そして、プログラマブル・ロジック)からの技術や設計要素を統合して、広範囲で高度な複雑さおよび高付加価値の半導体製品に対応していることである。SOC の生産および設計技術は、一般的に専用製品向けとして元々開発されたものである。SOC ドライバは ASIC に最も似ており、また低設計コストおよび高レベルのシステム・インテグレーションがその主要なゴール<sup>2</sup>であることから、ASIC から最も直接的に発展してきた。ASIC 設計との主要な差は、SOC 設計では、そのゴールが既存ブロックあるいは「コア」の再利用率を最大にするということであり、新規に設計されるチップの規模を最小限にするものである。SOC 中の再利用されるブロックは、アナログおよび既に量産されている専用コアばかりではなく、ソフトウエア・ブロックも含んでいる。そのキー・チャレンジは、SOC 設計者。に役に立つ再利用可能なブロックあるいはコアを企画、作成しメンテナンスすることである。SOC の有用性は、再利用ベースの SOC 設計のバリデーションが「スクラッチからの設計」よりも容易かどうかにも依存する。

SOC は、いくつかの方法でこれまでの製品分野を統合してきている。上に述べたように、SOC は他のシステム・ドライバ分野からブロックを統合し、ASIC 商品カテゴリをも包括している。フルカスタムおよび ASIC/SOC 間の品質ギャップは低減している。それは、(1) 2001 年 ITRS では ASIC および MPU ロジック密度を等しいとしてモデル化している。(2)そして、「ASIC スケジュールでのカスタム設計並みの性能」はオンザフライ(「リキッド」)あるいは最適化再生成のスタンダード・セル設計手法によって次第に達成されている。最終的には MPU は SOCへ発展してゆく。つまり、(1) MPU は次第に SOC に使われるコアとして設計されるようになる。(2)その再利用性と設計生産性を改善するために MPU それ自身も SOC として設計されて行く。(後で議論されるように ITRS のMPU モデルは複数の演算処理コアを持っており、構成は SOC に似ているかの最も基本的な SOC の挑戦はインプリメンテーションの生産性および製造原価である。それはより大規模な再利用ばかりではなく、プラットフォームに基づいた設計、シリコン・インプリメンテーションの規則性あるいは他の斬新な回路およびシステム・アーキテクチャ・パラダイムも要求する。別の挑戦は多数のインプリメンテーション要素(たとえば、リプログラマブル・デバイス、メモリ、アナログ、無線周波(RF)、MEMS、ソフトウェア)からの異種なコンポーネントのインテグレーションである。

SOC ドライバ分野は、設計生産性を改善する知的資産(IP)の多くの再利用と、そして、異種な技術を潜在的に包含するシステム・インテグレーションによって特徴づけられる。SOC は低コストおよび高集積化を提供するために存在する。コストの考察は、速いターンアラウンドタイムのデザイン方法論に伴う、ローパワー・プロセスおよびローコスト・パッケージング・ソリューションの展開へと導く。後者は、順番に、IP記述、IPテスト(内蔵自己テスト(BIST)および自己修復を含む)、ブロック・インターフェイス合成等の新しい基準および方法論が必要である。統合の考察は、チップ・パッケージ共通最適化の必要性と同様に特定のシステム・コンポーネント(メモリ、

<sup>&</sup>lt;sup>2</sup> Most digital designs today are considered to be ASICs. ASIC connotes both a business model (with particular "handoff" from design team to ASIC foundry) and a design methodology (where the chip designer works predominantly at the functional level, coding the design at Verilog/very high description language (VHDL) or higher level description languages and invoking automatic logic synthesis and place-and-route with a standard-cell methodology). For economic reasons, custom functions are rarely created; reducing design cost and design risk is paramount. ASIC design is characterized by relatively conservative design methods and design goals (cf. differences in clock frequency and layout density between MPU and ASIC in previous ITRS editions) but aggressive use of technology, since moving to a scaled technology is a cheap way of achieving a better (smaller, lower power, and faster) part with little design risk (cf. convergence of MPU and ASIC process geometries in previous ITRS editions). Since the latter half of the 1990s, ASICs have been converging with SOCs in terms of content, process technology, and design methodology.

<sup>&</sup>lt;sup>3</sup> For example, reusable cores might require characterization of specific noise or power attributes ("field of use," or "assumed design context") that are not normally specified. Creation of an IC design artifact for reuse by others is substantially more difficult (by factors estimated at between  $2 \times$  and  $5 \times$ ) than creation for one-time use.

<sup>&</sup>lt;sup>4</sup> The corresponding ASIC and structured-custom MPU design methodologies are also converging to a common "hierarchical ASIC/SOC" methodology. This is accelerated by customer-owned tooling business models on the ASIC side, and by tool limitations faced by both methodologies.

#### 4 システムドライバ

センサ等)がインプリメントされる異種混合の技術(フラッシュ、DRAM、アナログ、RF、MEMS、強誘電体RAM(FeRAM)、磁気抵抗 RAM(MRAM)、化学センサ等)の必要性へと導く。このように、SOC は同一システム・パッケージだけでなく、同一製造プロセス上で複数の技術を集積するためのドライバである。本章は、複合技術統合(MT)、高性能(HP)およびローパワーと低コスト(LP)によって各々ドライブされる3つの形態に関して、SOC の性質および発展を議論する。この分割は、解体の意味でなく、むしろ主要な考えの各々を分けること意味する(例えば、低消費電力設計は高性能設計ですが、同時にパッケージ・コストおよびシステム・コストを削減しなければならない)。

## SOC/SIP 複合技術(SOC-MT)

異種システムを単一チップ上に構築する必要性は、構造的な要因や、コネクションの負荷とスピードの関係、或いは信頼性等のコスト意識によってもたらされる。そのためプロセス技術者は、MEMS やその他のセンサと CMOS の融合を模索して来た。単一チップ上に複数の技術を集積することは、より複雑なプロセスを要求し、この複雑度が複合技術 SOC の主なコスト要因と成る。将来の新材料やプロセスの複合に関して、総合的なコスト予測をすることは困難である。しかしながら、コスト制約によって或 SOC に集積できる技術の数は制限される。標準低消費電力ロジックプロセスにフラッシュメモリが混載されるように、プロセスのモジュール化が進んだとしても、一般的にはモジュールは積重ね可能ではない。他の技術と統合する必然性や大量生産の必然性が無くとも、標準 CMOS プロセスと各々の技術を集積することには、今後も発展する可能性が有るであろう。最近の(電気・光、電気・生物)技術と CMOS の集積は、単に技術的優位性だけではなく、複数チップによるシステム・イン・パッケージの代案よりもコスト効率が優位でなければならない。今日、幾つかの技術(MEMS、GaAs)では、各々の製品(Flash や DRAM)の面積やピン数の制約に依存して、同一モジュール内でフリップして重ね合わせるか、シリコン上に隣り合わせに集積することでコスト効率が向上出来ている。特にセンサの単一ダイへの集積の必要性は、システムの物理的大きさ(耳と口:例えば自動車内でのスピーカとマイクの分離)等に影響されている。

### SOC ハイ・パフォーマンス(SOC-HP)

SOC-HP(High-performance)の例としては、ネットワーク・プロセッサやハイエンド・ゲーム・アプリケーションが挙げられる。それは MPU-SOC の反映なので、MPU のトレンドに追従し、ここでは単独のモデル化はしない。高速通信網の分野におけるチップ外への入出力信号に対する要求に関しては、SOC-HP の特徴として議論することが出来る(それは、テスト、アセンブリ、パッケージング、設計への重要な技術チャレンジを生み出す)。歴史的に見ても、チップの入出力速度(ピン当たりのバンド幅)は、チップ内部のクロック周波数に比べ、スケーリングが遅れて来た。これには、既存の遅い入出力標準に適合させると言う理由も一面あるが、主な制約は、終端されていない CMOS 信号のプリント配線基板上での安定化時間が長く、100MHzを大きく越える信号の伝送が困難であることに因る。この十年では、長距離通信用に開発された高速リンク技術が、他の応用にも適用されて来た。この高速入出力は、基板の信号安定化時間の問題を、1対1接続と配線を伝送線路として扱うことで回避して来た。今日では、これらのシリアル・リンクで最速の物は、1 ピン当たり 10Gbit/秒で動作させることが出来る。

高速リンクは主に 4 つの部分から成る:1)bit を基板配線へ伝達する電気信号に変換する送信機、2)配線自体、3)配線末端の電気信号から bit を復元する受信機、4)配線による遅延を補償し、配線上の信号から正しい データを抽出するための時間を再現する、タイミングリカバリ回路。この様なリンクは、受信機、送信機、タイミングリカバリ回路が全てアナログブロックを必要とするため、本質的にミックスド・シグナル設計に成る(例えばミックスド・シグナル・ドライバの部分で議論する電圧制御発信機(VCO)は、タイミングリカバリ回路の主な構成要素である)。一般的に言えば高速リンクは、光システムやチップ間接続、バックプレーン接続で使われる。

光リンクは普通少ない光信号から成り、比較的複雑で電力制約が厳しいにも係わらず、通常最も性能の良いリンクと成る。今日では、光リンクは 1 ピン当たり 10Gbit/秒で動作し、テストの章(高速シリアルリンクに関する議論)で示されるように、引続き周波数のスケールアップが期待されている。最初これらのリンクは、CMOS では要求される高速性を実現出来ないと考えられたため、non-CMOS 技術の回路で構成された。しかしこの 5 年で、多くの研究者が 10Gbit/秒で動作する回路を開発して来た。幾つかの論文では、1bit 当たり 4 ファンアウト (FO4)1 段分の遅延時間で動作することが示されたが、多くのリンクは 1bit 当たり FO4 の 2-4 段分の遅延時間で動作し、180nm 世代で 10Gbit/秒を実現している。回路の側面からは持続的なリンク速度のスケーリングは可能と思われるが、寄生効果やパッケージの影響で困難に成ると思われる。この速度の信号は経路に在る不連続性に非常に敏感である。インピーダンスを制御したパッケージを使用したとしても、パッケージや基板のビアでインピーダンスの変化が生じ、信号の劣化を引き起こしてしまう。静電放電(ESD)用のデバイスによる 1-2pF の寄生容量によっても、非常に大きな信号劣化が発生する。従って、持続的な性能のスケーリングには、ESD やパッケージ、基板設計に、重要な作業を要求する。

同じ基板上に配置する2チップ間の情報交換を行うチップ相互接続は、通常互いに近接して行われる。チップ間に複数のリンクをパラレルに接続することが可能であるため、これらのリンクを設計する際の主な指標はGbit/秒には成らない。例えば、2 倍の速度を実現するために10 倍の面積と10 倍の電力が必要ならば、2 本のパラレルなリンクを使う方が良いであるう。これらのリンクは、性能ばかりでなく性能とコストの両方を最適化するからである。一般的に、最高速のチップ間リンクは、最高速の光リンクの2-4 倍の遅さに成っている。これらのリンクのbit 時間は大変多様で、今日可能な1 対1 リンクのbit 時間の幅は、2.5n 秒(400Mbit/秒)から0.4n 秒(2.5Gbit/秒)まである。こうした性能範囲の幅広さは、要求されている入出力の数(数が増えれば速度は低下する)と、設計者が取ろうとするリスクの度合いと、ある場合には既存の入出力標準を反映した結果である。強靭で高速な入出力の設計は依然としてミックスド・シグナル問題であり、現行のツールでは自動化や検証が出来ない。そのため今でも、多くの設計チームが入出力のレートを選択する際は保守的である。テクノロジ・スケールや設計ツールがより強靭に成れば、bit 時間は FO4 遅延の4-8 倍に近付くが、このことはパッケージその他の寄生効果を補償する追加回路を必要とすることであるう。

高速リンクの最後の主な応用は通信網で、異なった基板上に実装されたチップ間の通信である。信号の経路は同じように 1 対 1 であるが、まず一方のチップのパッケージを通ってローカルな基板へ伝播し、コネクタを通して別の基板へ伝播し、さらに目的の基板へコネクタを通して伝播し、受信機のパッケージを通してチップへ伝播する。高いバンド幅のため、各々のチップは一般に多くのリンクを持ち、単価当たりの性能が重要と成る。チップ間接続との主な違いは、両チップ間"配線"の電気的特性が劣悪であることである。配線問題は、90nm世代で実現される 10Gbit/秒を超える速度に成ると、より深刻な懸念事項となる。これら入出力の重要性は、高速領域における SOC と SIP の実装法のトレードオフをも示すことになる。

#### **SOC Power-Efficient (SOC-PE)**

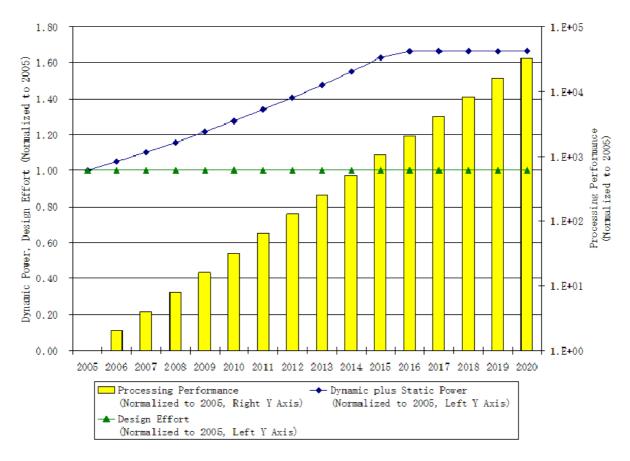

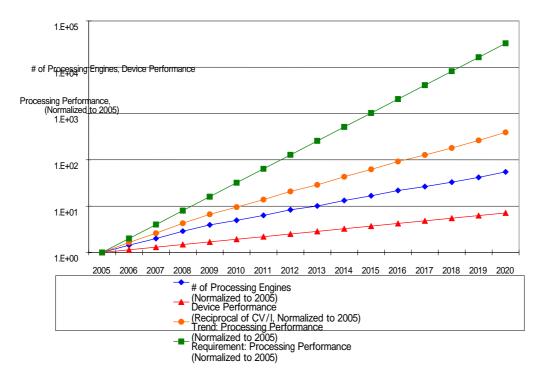

SOC に占める PE(Processing Engines)の割合は、SOC 設計において益々増加している。それは高性能なメディア対応電話やデジタルカメラチップのような携帯用ワイヤレスアプリケーションだけでなく、高性能コンピューティングや企業用アプリケーションのような他の処理目的のチップを含む。Figure 11 は、Japan Semiconductor Technology Roadmap Design Working Group によって作成されたモデルに一部基づいた、消費者主導の、おそらくマルチメディアを処理する能力を持ったワイヤレスデバイスの電力効果の多様な特質に対する必要条件を表している。モデルの鍵となる局面は以下のとおりである。

- ・ 代表的なアプリケーションの分野は、「Mobile Consumer Platforms」に分類される電子機器である。なぜならこの分野は、近い将来において、半導体のどの技術世代でも、急速に発展するからである。

- ・ この種の SOC(Mobile Consumer Platforms)の典型的必要条件は、バッテリ寿命のある上限の下で、爆発的な処理力の増加が要求される。

- ・ 結果として、必要とされる処理力は、今後10年間で、1000倍となる。一方で、動的な電力消費は顕著に

#### 変わらない事が要求される。

Mobile Consumer Platform 製品の寿命は短く、かつ将来的にも短いままだろう。したがって、設計効率の向上は見込めない。近い将来にわたって、現在のレベルに留まるだろう。

Figure 11 Several Trends for SOC-PE Driver

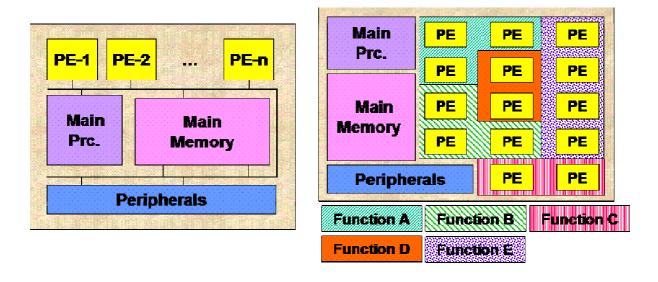

Figure 12 で示すとおり、典型的な電力効率の高い SOC は、Mobile Consumer Platform アプリケーションの仕様テンプレートでみることができる。 SOC は高度に並列したアーキテクチャを特徴とし、メインプロセッサー、いくつかの PE(Processing Engines)、周辺機器とメモリで構成されている。

Figure 12 SOC-PE Architecture Template

PE(Processing Engine)は、特定機能のためにカスタマイズされたプロセッサである。大規模で非常に複雑な構造を持った機能ブロックは、複数の PE のセットとして実装されるであろう。この機構では、並列処理と特定機能をもったハードウェアの実現によって、SOC の高い処理パフォーマンスと低消費電力の両立を可能にする。将来の SOC 構造の特長は、PE が非常に多いことである。

提示されたアーキテクチャは、特別なプロセッサ配列構造や対称プロセッサを必要としない点に注目していただきたい。このアーキテクチャの本質的な特徴は、要求機能を実現するために、SOC 内に多数の PE を実装したことである。

#### SOC-PE における設計複雑度の傾向

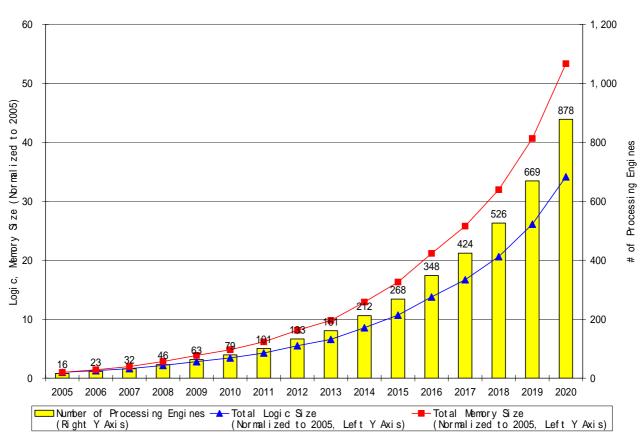

この仕様テンプレートに基づくと、SOC-PE ドライバのための設計(定量化された設計)の複雑さの傾向は、Figure 13 にみられる通りになる。もっとも興味深い点は、PE の数と、メインメモリのサイズである。特に、PE の数は今後急速に増加するだろうと思われる。

以下は、これらの設計の複雑性の傾向に基づいた一般的な仮定である。ほぼ一定の複雑性を持った1つのメインプロセッサーがあるとする。周辺回路は、同じ複雑性を保つ。PE に関しては、回路の複雑さの平均は一定で保たれるが、ダイサイズが 64mm2 近辺なら、PE の数は増え続ける。最後に、メインメモリの数は、PE の数に比例して増加する。

Figure 2 SOC Complexity Trends

Figure 13 SOC-PE Design Complexity Trends

以下は、再利用率とハードウェアの設計効率のような特定事項のために作られた仮定である。要求される設計効率は一定とみなす。設計効率は単純に、論理回路部分のサイズに比例すると仮定している。再利用された論理回路に対する設計効率は、同サイズの新規設計のために必要な効率の半分とする。再利用しても設計

効率は、決してゼロではなく、そのオーバヘッドは 50%としている。論理回路の再利用は、機能改善や、実装設計や、最終的な物理検証を行う事が必要となる。メモリや純粋なアナログのような非論理的回路においては、設計の再利用のための作業は無い。再利用率はそれぞれ 2005 年には 30%、2020 年には 90%である。2005年から 2020 年までの各年の再利用率は、線形補間で決まる。

上記仮定によると、2016年までの10年間に新しく設計する回路に対して、設計効率を一定に保つためには10倍の設計生産性の向上が必要とされるということになる。

この挑戦的な生産性向上を解決するために、いつくかのアプローチを組み合わさなければならない。最初に、設計の抽象レベルを上げなければならない。次に、自動化のレベル、特に設計検証やインプリメンテーションにおける自動化レベルを上げなければならない。最後に、再利用率の増加は、真に解決の鍵となる。しかしながら、再利用率の増加だけでは、不十分である。再利用のための設計のオーバヘッドもまた、効率向上の対象としなければならない。

|                                                                                                           | 2005 | 2006 | 2007 | 2008 | 2009 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015  | 2016  | 2017  | 2018  | 2019  | 2020  |

|-----------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|-------|-------|-------|-------|-------|-------|

| Trend: SOC total logic size (normalized to 2005)                                                          | 1.00 | 1.27 | 1.62 | 2.15 | 2.81 | 3.42 | 4.27 | 5.50 | 6.58 | 8.54 | 10.69 | 13.77 | 16.69 | 20.62 | 26.12 | 34.15 |

| Requirement % of reused design                                                                            | 30%  | 34%  | 38%  | 42%  | 46%  | 50%  | 54%  | 58%  | 62%  | 66%  | 70%   | 74%   | 78%   | 82%   | 86%   | 90%   |

| Requirement productivity for<br>new designs (normalized to<br>2005)                                       | 1.00 | 1.24 | 1.54 | 2.00 | 2.54 | 3.02 | 3.67 | 4.59 | 5.34 | 6.73 | 8.18  | 10.2  | 12.0  | 14.3  | 17.5  | 22.1  |

| Requirement productivity for<br>reused designs (normalized to<br>productivity for new designs<br>at 2005) | 2.00 | 2.48 | 3.08 | 4.00 | 5.09 | 6.04 | 7.33 | 9.19 | 10.7 | 13.5 | 16.4  | 20.4  | 24.0  | 28.6  | 35.0  | 44.2  |

Table 9 SOC-PE Design Productivity Trends

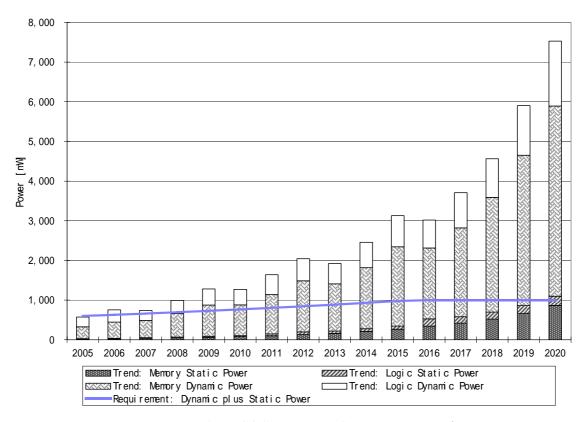

#### SOC-PE における消費電力の傾向

デザインの複雑性は重要な傾向である。しかし、消費電力は、SOC-LP チップの設計と同様に重大な要素と言える。Figure 14 は、PIDS requirements table のトランジスタ性能パラメータと、*interconnect chapter* の "Interconnect Technology Requirements "のインターコネクト性能パラメータと、上記の" Design Complexity Trends "の回路の複雑性パラメータを使用し、総合的なチップ消費電力の傾向を表している。図に示された傾向を、よりよく理解するために、以下の点に注意する。

- · ここで適用されるモデルは、単純に現在の最高水準の技術レベルを想定しており、したがって、消費電力は要求水準をかなり上回る。

- ・ 解決策候補は、design chapter の中で議論され、示される。SOC-PE の具体的な解決は、設計の高位段階における消費電力解析に基づく、構造最適化や、カスタマイズされた PE の実現を含む。

- ・ 電圧供給が、将来非連続的に推移するため、論理回路の動作電力は、2009 年から 2010 年、2012 年から 2013 年、2015 年から 2016 年に各々上下に推移する。

#### SOC-PE における処理性能の傾向

基本的な仮定として、処理能力は、SOC 上の PE 数の増加という、デバイスの性能そのものに比例して改善されるであろう。

Figure 15 で示すように、処理能力に対する要求と予想のギャップは、線形傾向を超えて広がる。ここで述べられたギャップは、PE の数の増加によって解決される。

解決策の候補は、Design 章の中で詳細に議論され、示される。このドライバのための重要な解決策として、

高位設計段階での最適なハードウェアとソフトウェア分割が含まれており、高位合成のような、ハイレベルデザインのステージからインプリメンテーションのステージへの、自動化されたインタフェース技術も含まれている。

Figure 14 SOC-PE Power Consumption Trends

Figure 15 SOC-PE Processing Performance Trends

## マイクロプロセッサ(MPU)ドライバ

ハイボリューム向けのカスタム設計では、パフォーマンスと製造原価の問題が、設計や他の開発コスト (NRE)の問題より重要である。なぜなら、これらのチップは大きな利益を生む可能性を持っているからである。大きな利益は、非常に大きな売上個数に起因する。カスタム設計スタイル、特別なプロセスエンジニアリングや設備などを正当化するために、大量というだけでは、必要条件でもなく、十分条件でもない。NRE や製造装置への投資を合わせて、期待されるリターンがプラスになることが重要である。ハイボリューム向けのカスタム設計の分野における、3つの大きなクラスは、MPU、メモリ・、そしてリプログラマブル(例えば FPGA)である。このセクションでは、半導体製品のための重要なシステム・ドライバのうちの一つとして MPU に注目する。MPU は、目標を達成するために、最も積極的な設計スタイルおよび製造技術を使用する。これらの大量製品のおかげで、製造フローの変更、新しい設計スタイルおよび支援ツールの作成(大規模な収入は新しいツール生成の代価を払うことができる)、(設計者によって得られたすべてのリスクが出てくるとは限らないが)微妙な回路問題まで洗い出される。実際、MPU は、集積度および設計の複雑さ、電力・速度性能曲線、大規模チームの設計工程の効率、テストおよび検証、電力制御、パッケージシステム・コストに関して半導体産業をドライブしている。MPU(一般的にはハイボリューム・カスタム設計品)の生産は、非常に労働者に集約されているにもかかわらず、全産業によっててこ入れされる新技術およびオートメーション方法(設計および組立ての両方)を創造する。

ITRS の MPU ドライバは、汎用の命令セットアーキテクチャ(ISA)に基づいて設計され、デスクトップとサーバシステムにおけるスタンド・アローンでの使用、または、SOC アプリケーションでのコアとして組み込まれたりする。MPU システム・ドライバは、常に市場のけん引役で、歴史的に以下の特徴がある。1)標準アーキテクチャ・プラットフォームが出現したのち、それが複数世代にわたって供給され続ける、2)市場からの影響による激しい価格変動、3)非常に高い生産ボリュームおよび製造原価意識。MPU ドライバ・モデルの重要な要素は、以下のとおりである。(本章の調査内容は GTX ツールで検証できる。MPU に関する内容は、電子版でリンクされた研究で提供される。)

1. 3 つのタイプのMPU これまでの歴史をみると、3 つのタイプの MPU があった。1) 「デスクトップ」を反映したコストパフォーマンス(CP)タイプ、2) 「サーバ」向け高性能(HP)タイプ、3) power-connectivity-cost (PCC)タイプである。2001 年 ITRS の予測では、(ワイヤレス接続を備えた)電池駆動の携帯機器 の市場増加は、MPU の新しい PCC カテゴリを生成した。同時に、伝統的に「デスクトップ」向けであった CP の分野は、低額で廉価な従来型「サーバ」から、「モバイルのデスクトップ」(第 1 に AC モードで使用されるラップトップ)および「ブレード」サーバまで、価格性能トレードオフ・カーブの広範囲に拡大しつつある。結果として、CP と HP のカテゴリ間のパフォーマンスのギャップは小さくなっている。しかしながら、大規模なマージンのため生産量に不釣り合いな設計努力を施した本当に高額のサーバの市場は残るであろう。以前に予測されたように、新しいPCCカテゴリは、電池寿命の増加およびワイヤレス接続による便利性に後押しされ、高機能と低消費電力 SOC設計の特性を持ち始める。しかしながら、PCC設計のより大きなマージンおよび大きな生産量は、従来の SOCと比較して、はるかに大きな設計努力を必要とするであろう。

2. **ダイサイズ一定** ダイサイズ(CPでは 140mm²、HPでは 310mm²、PCCでは 70-100mm²)はロードマップ上一定であり、ロジック、メモリおよび集積のオーバヘッドにブレークダウンされる。集積のオーバヘッドとは、ブロック間チャネル、無駄な領域を持つフロアプラン、および設計所要時間に伸ばせるレイアウト密度とのトレードオフによる。以前のITRSモデルと異なり、電力とコスト・配線遅延がダイサイズの強い制約になる。追加ロジ

THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS: 2005

<sup>&</sup>lt;sup>5</sup> Memory is a special class of high-volume custom design because of the very high replication rate of the basic memory cells and supporting circuits. Since these cells are repeated millions of times on a chip, and millions of chips are sold, the amount of custom design for these parts is extraordinary. This aspect has led to separate fabrication lines for DRAM devices, with some of the most careful circuit engineering needed to ensure correct operation.

ックは、パッケージ・パワーの制限から効果的に利用できないかもしれないし、また、追加メモリ(たとえばより大きなキャッシュ、より高次なメモリ・ハイアラーキ・レベルのオンチップ・メモリ)も、ある点から先はコスト効率が良くないことが考えられる。さらに、(プロセス・スケーリングにより)配線のパイプライン段数が増加するとともに、正確なアーキテクチャの性能シミュレーションが困難になり、これもダイサイズの増加を制限するであろう。

- 3. マルチ・コア構成 MPU ロジックの内容は、HP およびハイエンド CP カテゴリで、130nm 世代でマルチプロセッシングユニットのオンチップ化がスタートするであろう。これは、以下のいくつかの事実を含んでいる。: 1)最近および今後計画されている商用 MPU 製品の構成(サーバおよびデスクトップの両方); 2)標準の ISA と同様に検証と論理設計を再使用する必要性の増加; 3) 暗号化、グラフィックスおよびマルチメディア等々と、世代ごとに(例えば、x86、multi-media instructions (MMX)および explicitly parallel instruction computing (EPIC))逐次「増大」していく ISA; 4)電力の観点ではそれほど効率的ではない汎用のプロセッサ・コアに、効率的な専用「補助エンジン」「を SOC のように集積することによって、アーキテクチャ、operating system (OS)およびアプリケーション・レベルでの電力の柔軟な管理を可能にする必要性; 5) プロセッサ・コアのサイズ制限 (近年のトレンドで控えめに見積もっても、コアあたり一定で 2000~2500 万トランジスタ®); 6) 設計生産性の必要から SOC と MPU の設計手法の収束。より複雑になる単一のコア設計がさらに数年間継続する一方、それらは、特に HP およびハイエンド CP カテゴリで等価なマルチ・コア設計と競争するようになる。この期間に、マルチ・コア設計のコア数はテクノロジ世代ごとで 2 倍になると予想されている。

- **4. 内蔵メモリ規模** MPU に搭載されるメモリは、180nm では、CP用では512K バイト(512 x 1024 x 9 ビット)、HP 用では2M バイトの SRAM である。メモリ規模は、ロジック規模と同じく、絶対時間間隔 (例えば18 か月ごと) で増加するわけではなく、テクノロジ世代ごとに2倍になると予想されている<sup>9 10</sup>。

- 5. **レイアウト密度** そのシステムの複雑さと生産ボリュームの高さから、MPUはレイアウト密度の改善ドライバである<sup>11</sup>。したがって、MPUドライバによってレイアウト密度が設定され、ORTCのトランジスタ数とチップ・サイズが規定されている。ロジックとSRAMレイアウト密度は、DRAMの「Aファクタ」と類似して、最近のMPU製品で数値合わせをしている。Fがテクノロジ世代の最小の特徴サイズである場合、ロジック・レイアウト密度は、ほぼ

<sup>7</sup> A "helper engine" is a form of "processing core" for graphics, encryption, signal processing, etc. The trend is toward architectures that contain more special-purpose, and less general-purpose, logic.

<sup>9</sup> The doubling of logic and memory content with each technology generation, rather than with each 18- or 24-month time interval, is due to essentially constant layout densities for logic and SRAM, as well as conformance with other parts of the ITRS. Specifically, the ITRS remains planar CMOS-centric, there is evidence that non-planar "emerging research devices" are moving into development, possibly as early as 45 nm (VLSI Symp'03). Adoption of such novel device architectures would allow improvements of layout densities beyond what is afforded by scaling alone.

Deviation from the given model will likely occur around 90 nm with adoption of denser embedded memories (eDRAM). Adoption of eDRAM, and integrated on-chip L3 cache, will respectively increase the on-chip memory density and memory transistor count by factors of approximately 3 from the given values. While this will significantly boost transistor counts, it is not projected to significantly affect the chip size or total chip power roadmap. Adoption of eDRAM will also depend strongly on compatibility with logic processes (notably the limited process window that arises from scaling of oxide thickness), the size and partitioning of memory within the individual product architecture, and density-performance-cost sensitivities..

<sup>11</sup> ASIC/SOC and MPU system driver products have access to similar processes, as forecast since the 1999 ITRS. This reflects emergence of pure-play foundry models, and means that fabric layout densities (SRAM, logic) are the same for SOC. and MPU. However, MPUs drive high density and high performance, while SOCs drive high integration, low cost, and low power.

<sup>&</sup>lt;sup>6</sup> Multi-core organization and associated power efficiencies may permit slight growth in die size, but the message is still that die areas are flattening out.

<sup>&</sup>lt;sup>8</sup> The CP core has 20 million transistors, and the HP core has 25 million transistors. The difference allows for more aggressive microarchitectural enhancements (trace caching, various prediction mechanisms, etc.) and other performance support.

320F<sup>2</sup>の平均スタンダード・セルゲート・レイアウトを反映している12。65nmおよびそれ未満では、光近接効果補 正(OPC)および位相シフトマスク(PSM)のようなサブ解像リソグラフィ技術によって課せられるスペーシング制約 の複雑さが増加するため、レイアウト密度のスケーリングがより遅くなる。このインパクトは 65nm世代で 20% にも なると予測している。その結果、0.7のスケーリング係数は、たった0.55~0.6の密度向上となる。上述のように、 ロジック・レイアウト密度は斬新なデバイスの到来で著しく改善するかもしれない。SRAMレイアウト密度は、 60%の周辺回路のエリア・オーバーヘッドと、MPUの中で6トランジスタ・ビットセル(F<sup>2</sup> = 223.19F(μ m)+97.74 を ビットセルあたりの面積単位)の使用を想定している。

6. 最大オンチップ(グローバリル)クロック周波数 MPU は、さらに OTRC の中で最大オンチップ・クロック周 波数をドライブしている。これらは、次には Interconnect、Process Integration, Devices, and Structures (PIDS)、 Front End Processes (FEP)、および Test のロードマップの様々な局面をドライブする。MPU 最大オンチップ・ク ロック周波数は、歴史的には1世代当たり2倍の増加を示している。これは、ほぼ1.4倍のデバイススケーリング 則(tox および他の制約要因)と、1.4 倍はパイプライン(例えば 180nm における 32 のファンアウト4のインバータ ー(FO4 INV)の遅延13と、130nm における 24~26 の FO4 INV 遅延に相当) のロジック段数の削減からきてい る。この歴史的なトレンドが継続しないいくつかの理由がある。1)良質のクロックパルスは 6~8 より少ない FO4 INV 遅延では生成することができない。2)パイプラインの中でオーバヘッド(効果の低減)が増加する(1フリッ プ・フロップあたり2~3 段の FO4 INV 遅延、 パルスモードラッチあたり1~1.5 段の FO4 INV 遅延)。3)手頃な パッケージングによって課された熱特性が非常に深いパイプラインを抑止する。4)アーキテクチャと回路の革 新は、周波数改善に直接寄与するものよりも、(デバイスに相関する)配線 RC の悪化への対策が増加する。 2005年の ITRS MPU のモデルは、最大オンチップ・グローバルクロック周波数の歴史的な増加割合を継続す るが、(歴史上の MPU クロック周期データのプロットが提供されている) 90nm で、クロック周期は 12 の FO4 INV 遅延でフラットになる。 これは 2001 年の ITRS で作られた 16 の FO4 INV 遅延の予測から変更された。 回 路とアーキテクチャの進歩に基づいた予測は、最小の達成可能なロジック深さが 10~12F04 に接近しているこ とを示している。90nm 世代の後は、斬新な回路およびアーキテクチャのアプローチがない状態で、デバイス性 能のみでクロック周波数が増加するであろう14。

#### MPU の進化

最近の「セントラライズド・プロセッシング」の状況は、1)従来の MPU 群(ここで想定しているドライバ)からなる ハイ・パフォーマンスな演算機能を持つ中央処理装置(サーバ)、および2) 例えばワイヤレス携帯端末マルチ メディア・プラットフォーム(Figure 12 の低電力の SOC PE モデル参照)を構成する、RF、アナログ/ミックスド・シグ ナルおよびディジタル回路を集積した SOC からなる、パワー効率を狙った演算処理を行う「インターフェイスリ メデリアル・プロセッサー」を統合したものである。従来型 MPU の将来に向けた進化に対するキーとなる課題 は、設計生産力、パワーマネージメント、マルチ・コア化、I/O 帯域幅、回路およびプロセス技術に関するもので ある。

設計生産力 MPU 製品のデザインおよび検証の複雑さやコストは、1 つのデザインあたりのエンジニアが

$<sup>^{12}</sup>$  A 2-input NAND gate is assumed to lay out in an 8  $\times$  4 standard cell, where the dimensions are in units of contacted local metal pitch (MP =  $3.16 \times F$ ). In other words, the average gate occupies  $32 \times (3.16)^2 = 320F^2$ . For both semi-custom (ASIC/SOC) and full-custom (MPU) design methodologies, an overhead of 100% is assumed.

$<sup>^{13}</sup>$  A FO4 INV delay is defined to be the delay of an inverter driving a load equal to 4× its own input capacitance (with no This is equivalent to roughly 14× the CV/I device delay metric that is used in the PIDS Chapter to track device performance. An explanation of the FO4 INV delay model used in the 2005 ITRS is provided as a link.

<sup>&</sup>lt;sup>14</sup> Unlike the ITRS clock frequency models used through 2000 (refer to Fisher/Nesbitt 1999), the 2005 model does not have any local or global interconnect component in its prototypical "critical path". This is because local interconnect delays are negligible, and scale with device performance. Furthermore, buffered global interconnect does not contribute to the minimum clock period since long global interconnects are pipelined—i.e., the clock frequency is determined primarily by the time needed to complete local computation loops, not by the time needed for global communication. Pipelining of global interconnects will become standard as the number of clock cycles required to signal cross-chip continues to increase beyond 1. "Marketing" emphases for MPUs necessarily shift from "frequency" to "throughput" or "utility."

年間数千人単位(設計チームで数何百チーム)で急速に増加しているのもかかわらず、いまだに数百のバグを抱えたプロセッサが市場に投入されている。この局面は、ロジック合成および自動的な回路チューニングのような設計オートメーションの使用を増加させ、激しいカスタム化および装飾的な回路ファミリーの使用を減少させた。その結果生じる生産力の増加は、プロセッサ開発スケジュールおよびチーム規模を一定にすることを可能にした。タイミング、雑音、電力および電気的ルールをチェックする設計ツールの改良は、安定した設計の高品質化にも寄与した。

パワーマネージメント パッケージの消費電力上限は(2005 ITRSタイムフレームの最後までに200W/cm²に達すると推測されるにもかかわらず)、高い供給電圧(世代あたりの理想値 0.7xに対して経験値換算 0.85x)および周波数(世代あたりの理想値 1.4xに対し経験値換算 2x)<sup>15</sup> を継続維持し続けることはできない。PIDS 章で述べられているように、MPUシステム・ドライバにおける過去のクロック周波数トレンドは、大きなオフ電流および非常に薄いゲート酸化物に導かれる将来のCMOSデバイス性能(スイッチング速度)を必要条件として説明されてきた。そのようなデバイスが与えられた場合、単に既存の回路やアーキテクチャ技術を継続するMPUは、2020 の最後までには、パッケージ電力上限を約 4 倍超過するであろう。もしくは、MPUロジック搭載量および(または)ロジック動作率は、パッケージ制約を守るために減少する必要がある。

携帯および組込み仕様のものは、厳密にパワー制限が行われており、このような障害(課題)に早い段階で遭遇するであろう。最近のパワー効率(たとえば、GOPS/mW)は、汎用 MPU に対して専用ハードウェア(組込み型ハードウェア)の方が 4 桁向上しており、この傾向がより大きくなっている。結果として、従来型の演算コアは、次世代の SOC ライクな MPU 領域において、特定用途向け、または、リコンフィギュアラブルなプロセッサ・エンジンとの競争に直面することになるであろう。

マルチ・コア構成 1 つダイの中にマルチ・コアを持つ MPU において、コアは 1)グローバル配線スケーリング則に逆らって、小さく速く、2)多数のアプリケーションおよび構成に横断的に再利用されるため最適化することができる。マルチ・コア・アーキテクチャは、工場の歩留りを達成するため冗長性を利用するのと同じように、消費電力削減を可能にする $^{16}$ 。また MPU モデルの構成は、チップ上にメモリ階層の規模を増やすことを可能とする。(メモリ混載プロセッサ、または、90nm ノードからの大規模オンチップ eDRAM L3)。 一般的な方法だけを考えるなら、より大きなメモリ容量がある方がリークやトータルの消費電力をうまく制御することが可能になる。

発展的なマイクロアーキテクチャの進化(スーパーパイプライン、スーパースカラー、および予測技術)は、推進する原動力が衰えてきているように見える。(「ポラックの法則」では、ある一定のプロセス技術において、新しいマイクロアーキテクチャは古い(前の世代の)マイクロアーキテクチャを使用した場合に比べ面積が2~3倍になり、その一方で性能は1.4倍~1.6倍しか改善されないとしている。) そのようなことから、最近は並列処理によるマルチスレッド化の傾向が大きくなっている。同様にネットワークやグラフィックス、セキュリティ等も、より複雑な専用ハード、および(または)専用エンジンが充てられる傾向にある。柔軟性のある効率のトレードオフ・ポイントは、汎用プロセッサから遠ざかる。

<sup>16</sup> Replication enables power savings through lowering of frequency and  $V_{od}$  while maintaining throughput (e.g., two cores running at half the frequency and half the supply voltage will save a factor of 4 in  $CV^{\rho}$  dynamic capacitive power, versus the "equivalent" single core). (Possibly, this replication could allow future increases in chip size.) More generally, overheads of time-multiplexing of resources can be avoided, and the architecture and design focus can shift to better use of area than memory. Redundancy-based yield improvement occurs if, for example, a die with k-1 instead of k functional cores is still useful.

<sup>&</sup>lt;sup>15</sup> To maintain reasonable packaging cost, package pin counts and bump pitches for flip-chip are required to advance at a slower rate than integration densities (refer to the Assembly and Packaging chapter). This increases pressure on design technology to manage larger wakeup and operational currents and larger supply voltage IR drops; power management problems are also passed to the architecture, OS, and application levels of the system design.

I/O 帯域幅 MPU システムにおける I/O ピンは、主として、高機能キャッシュメモリやメインシステムメモリに使われている。プロセッサのパフォーマンスが増加するに従い、I/O 帯域幅の要求は強くなってきている。最も高い帯域幅のポートは、伝統的に L2、L3 キャッシュに使われてきたが、最近の設計は、メモリの「レーテンシ」を減らすために、プロセッサにメモリコントローラを内蔵し始めている。これらのダイレクトメモリインターフェイスはキャッシュインターフェイス以上に I/O 帯域幅を要求する。メモリインターフェイスに加えて、多くの設計がシステムバスを高速なポイント・ツー・ポイント・インタフェースに置き換えている。これらのインタフェースは、Gbit/sのレートを実行するのに高速な I/O 設計を必要としている。シリアル・リンクは、このレートに到達しており、その一方で、単独チップ上の I/O の大規模集積化は、いまだ設計(各々の回路が超低消費電力を必要とする)、テスト(この速さを実行できるテスターを必要とする)、および、パッケージ(パッケージがチップとボードの接続を含め、バランスのとれた伝送ラインの配線を必要とする)に関してチャレンジ途上にある。

回路技術とプロセス技術 薄く信頼できないゲート酸化物・積極的なレチクル改良が必要なサブ波長の光学リソグラフィ・原子規模のプロセス変動(例えば注入プロセス)における増加する脆弱性を含む特徴サイズやデバイス構造のロードマップ、リソグラフィと PIDS、に必ず潜むプロセス変動によって、歩留りパラメータ(ウェハテスト後のウェハ価格/枚)は脅かされている。これにより、回路やアーキテクチャ設計のレベルで制約がかけられるであろう。ダイナミック回路の使用は、より低周波か、クロックゲート制御された分野での性能には魅力的であるが、雑音マージンおよび消費電力によって制限されているかもしれない。パス・ゲート・ロジックは基板効果により使用されなくなるであろう。歩留まりのロスを補うために冗長やリコンフィギュラブルの使用と同様に、ロジック中の single event upset(SEU)用エラー訂正が増加するであろう。設計と解析中のプロセス変動、および歩留まりパラメータ(ウェハテスト後)への影響が考慮できるように、設計技術はさらに発展するであろう。パワーマネージメントの必要性は、いくつかの要素技術の組合せを求めるであろう。

- 1. 並列処理および適応性のある電圧および周波数スケーリングを含むアプリケーション・OS・アーキテクチャレベルの最適化

- 2. Silicon-on-insulator(SOI)使用の増加を含むプロセス・イノベーション

- 3. マルチ Vth·マルチ Vdd·スループット制約のもとでの消費電力最小化·マルチドメインクロックのゲーティングとスケジューリングの同時使用を含む回路設計技術

- 4. リーク電流を減少させる斬新なデバイス

#### MPU のチャレンジ

MPU ドライバは、デバイス (オフ電流)・リソグラフィ/FEP/配線(変動性)・パッケージング(消費消費および電流分配)と同様に、設計とテスト技術(分散型/協調設計プロセス、検証、アットスピードテスト、ツール・キャパシティー、電力管理)に強く影響する。最も大きなチャレンジは、以下の項目である。

- •設計および検証の生産性 (例えば、総設計コスト、バグを大幅に減らすこと)(設計)

- •パワーマネージメントおよび電源供給 (例えば gigaoperations per second(GOPS)/mW) (設計、PIDS、アッセンプリおよびパッケージング)

- •量産時の歩留リパラメータ (リソグラフィ、PIDS、FEP、設計)

## ミックスド・シグナル・ドライバ

アナログ・ミックスド・シグナルチップは、少なくとも精度の高さが重要である入力信号を扱う部分を含むチップである。それはRF、アナログ、ADコンバータ、DAコンバータを含み多岐にわたる。また最近では、高精度で信号を計測する必要のある回路を有する多くのミックスド・シグナルチップが該当する。これらのチップはデジタル回路に必要な設計やプロセス技術とは異なる技術を必要とする。技術スケーリングはデジタ

ル回路に対しては、省電力、省面積、遅延減少の観点から常に好ましいものであるが、アナログ回路にとっ ては必ずしも好ましいものではない。何故なら、電源電圧スケーリングにともなって、精度要求を満たすこと や決められた電圧範囲の信号を取り扱うことが困難となるためである。このように新技術へのアナログ回路 のスケーリングは困難な技術課題である。一般に AMS 回路(例えば RF とアナログ設計)とプロセス技術 (例えばシリコン-ゲルマニウム、エンベディッド受動素子)は困難な技術課題として CMOS 統合によるコスト 効果を狙うものである。しかしながら、アナログとデジタルをうまく組み合わせると高機能化を提示できるだけ ではなく、デジタル回路と同じようにコストスケーリングも可能となる。

高精度性が必要であることはアナログ設計ツールへも影響を及ぼす。デジタル回路設計では、論理ゲー トが正しく作用する仕組みが作られている。これらの仕組みに従う限り、正確な信号値の計算は必要でなく なる。一方、アナログ設計者は要求精度を満たすために多くの「二次効果」を考慮しなければならない。関 連する技術課題としては、相互結合(信号や電源供給インテグリティに影響をあたえる静電容量、インダク タンス、抵抗および基板)や非対称性(局部的なインプラ、アライメント、エッチングなどすべての製造工程 の局所的な揺らぎは電気的特性に影響を与える)がある。これらの技術課題についての分析ツールがある が、専門家の手を必要とする。ただし、その精度は低消費電力アナログ回路、ミックストシグナル回路、さら には RF 設計においては未だ不十分である。統合ツールは未完成の状態であり、それらはアナログ回路レ イアウト合成に限定されている。AMS 回路に対する製造テストはまだまだ性能向上が必要であるが、SOC へ向けた取り組みとしてアナログ・ビルトイン・セルフ・テスト(BIST)の可能性がある。

今日の大規模なアプリケーションにおけるアナログ回路ならびにRF回路はSoCのほんの一部分である。 主流となる製品のビジネスは非常に競争的である - それらは大量生産品であるため、ミックスド・シグナル 技術を推進させる高額の研究開発費投資が必要である。移動体通信の基盤技術はミックスド・シグナルを 必要とする大規模回路である。アナログとミックスド・シグナル(AMS)のロードマップをまとめる時、多種多 様の回路とアーキテクチャが存在するので簡略化が必要となる。 本セクションでは 4 つの基本的なアナログ 回路について議論する。これらは最も重要な回路要素というだけではなく、それら回路の要求性能は代表 的であり、SoC のアナログ部ならびに RF 部で最も重要だからである。

- 1. 低雑音アンプ(ロー・ノイズ・アンプ)(LNA)

- 2. 電圧制御発振器(ボルテージ・コントロール・オシレータ)(VCO)

- 3. 電力増幅器(パワーアンプ)(PA)

- 4. アナログデジタル変換器(エー·ディー·コンバータ) (ADC)

これらの基礎回路を作り上げるために利用される設計およびプロセス技術は、さらに他の多くのミックスド・ シグナル回路の性能をも決定する。従って、これら4つの回路の性能は、性能指標(FoM)によって評価さ れ、ミックスド・シグナルのロードマップの優れた基盤となるものである。

以下、これらの性能指標について詳細に議論する。パラメータ(たとえば、利得 G)は、すべてデシベル・ スケールの代わりに絶対値として与えることにする。与えられた設計課題に対しての特定の解決策への偏 見を避けるものとする。予期しない解決策が障壁を克服することは度々あるので、むしろ異なるタイプの解 決策を推奨する(たとえば、代替解決策間の競争は、技術ロードマッピングと関係するすべてのタイプの進 歩のためによい推進力となる。)。 どの回路もその目的によってそれぞれ異なる要求性能がある。 つまり、 ある性能指数は異なる応用には矛盾している可能性がある<sup>17</sup>。そのような状況を回避するために、移動通 信プラットフォームに必要とされるアナログ回路および RF 回路の性能指数を議論する。最後に、本セクショ ンでは、デバイス・パラメータによる性能指標の依存性を評価する。その結果、回路設計上の要求からデバ

<sup>&</sup>lt;sup>17</sup> Certain cases of application are omitted for the sake of simplicity, and arguments are given for the cases selected. Considerations focus on CMOS since it is the prime technological driving force and in most cases the most important technology. Alternative solutions (especially other device families) and their relevance will be discussed for some cases, as well as at the end of this section.

イスおよびプロセス技術仕様を導くことができるようになる。アナログ回路性能の大きな進歩ならびに現実的で実現可能な技術進歩に結びつく外挿法が提案されている。これらのパラメータは、RF and Analog/Mixed-signal Technologies for Wireless Communications の章に与えられている。

## ロー・ノイズ・アンプ(LNA)

デジタル処理システムは、アナログ処理部分へのインタフェースを必要とする。これらのインタフェースの 典型的な例は有線あるいは無線通信での伝送媒体である。LNA は、次段の信号処理において雑音に不 感である程度にまで入力信号を増幅する。LNA の重要な性能指標は、次段の信号処理段に雑音を付加 することなく且つ歪なく増幅された信号を伝えることである。

LNA の応用(global standard for mobile (GSM, ), code division multiple access (CDMA), wireless local area network (WLAN), global positioning system (GPS), Bluetooth 等)は、種々の周波数帯に関連している。動作周波数、および時に LNA の周波数帯域幅が達成可能な性能に影響を与える。非線形性は多くのアプリケーションに適合するように考慮する必要がある。これらのパラメータは性能指標に含む必要がある。他方で、異なるシステムは多くの場合、直接に比較することが不可能であり、異なる必要条件を持つ。例えば、有線アプリケーションには非常に広い帯域幅が必要である。しかし、これは消費電力を増加させる。低消費電力性は、狭帯域の無線通信アプリケーションの重要な設計項目である。広帯域幅のシステムについては、LNAの性能を議論する際に帯域幅の方が線形性よりも重要となることがある。これら矛盾する設計要求を回避するために、無線通信に限定して議論を進める。

$$FoM_{LNA} = \frac{G \cdot IIP3 \cdot f}{(NF - 1) \cdot P}$$

[1]

さらに単純化させる仮定を作り、かつ「設計のノウハウ」を無視することで、技術スケーリングに沿った性能指標の外挿ができる $^{18}$ 。最大発振周波数  $f_{max}$ 、インダクタの性能、MOSFET $(g_m/g_{ds}|_{L_min})$ の利得および RF 供給電圧を考慮した LNA 設計用に関連したデバイス・パラメータの将来トレンドは RF and Analog/Mixed-signal Technologies for Wireless Communications の章に示されている。これらデータを将来へ外挿して、Table 10 の中で示されるような LNA 設計における将来の進歩予測を行うことができる。特に、線形性に関する問題は、デジタル校正手法を利用して長期的に解決してゆくべきものである。

#### ボルテージ・コントロール・オシレータ(VCO)

VCO は、フェーズ・ロック・ループ(位相同期ループ)(PLL)の重要構成要素であり、集積回路と外部の広帯域幅や高動作周波数アプリケーションの間の信号やりとりの同期をとる。VCO の重要な設計目標は、生

<sup>&</sup>lt;sup>18</sup> R. Brederlow, S. Donnay, J. Sauerer, M. Vertregt, P. Wambacq, and W. Weber, "A mixed-signal design roadmap for the International Technology Roadmap for Semiconductors (ITRS)," IEEE Design and Test, December 2001.

成された波形(あるいは位相雑音)のタイミング・ジッタと、消費電力を最小限にすることである。これらのパラメータにより、性能指標(*FoMyco*)は次のように定義される:

$$FoM_{VCO} = \left(\frac{f_0}{\Delta f}\right)^2 \frac{1}{L\{\Delta f\} \cdot P}$$

[2]

ここで、 $f_0$  は発振周波数、 $L\{\Delta f\}$  は  $f_0$  からの周波数オフセット  $\Delta f$  で測定した位相雑音スペクトル密度、P は全消費電力である。

この定義に動作周波数の絶対値が含まれていない。これは、動作周波数と性能指数の間に明確な関連がないためである。また、必要なチューニング幅がアプリケーションに強く依存するという理由で、ここでの定義には VCO のチューニング幅を無視している。チューニング幅という観点からは、FoMvco は位相雑音が最大になる周波数で評価すべきである。

位相雑音の主要因は、VCO を構成する能動素子および受動素子の熱雑音、LC タンク回路の性能指数、発信振幅、および能動部品の 1/f 雑音の影響を受けるオフセット周波数の値である。 $FoM_{VCO}$  は VCO の能動素子のオーバードライブ電圧におおよそ比例し、電源電圧に反比例し、LC タンク回路の性能指数の二乗に比例する。適当なオーバードライブ電圧を選ぶと、1/f 雑音の寄与の最小化と十分な発振振幅とのバランスをとることができる。 $FoM_{VCO}$  は、技術進歩とリンクする。将来の技術世代のデバイス・パラメータの予測に基づいて(RF and Analog/Mixed-signal Technologies for Wireless Communications の章 のデータを参照)、将来の技術世代における VCO の性能指標の外挿値が Table 10 に示されている。技術スケーリングに加えて、容量をスイッチで切り替えるデジタル制御発信器の技術トレンドについても掲載されている。

## パワーアンプ(PA)

パワーアンプ(PA)は有線あるいは無線のコミュニケーションシステムの伝送パス中の重要なコンポーネントである。パワーアンプは、隣接したチャネルへの漏洩を最小化するために高い線形性を備えつつ、情報をオフチップへ送信するのに必要な送信電力を供給する。特に電池動作の応用においては、所望の出力電力を最小の DC 電力で実現することが要求される。

CMOS パワーアンプは、その技術的理由から比較的小さな送信電力が必要とされる応用分野に限定される。個別部品で構成されるパワーアンプ(これらは SIP 技術のなかで集積化されます)については、バイポーラや化合物半導体テクノロジが強みを持っている(RF and Analog/Mixed-signal Technologies for Wireless Communication の章を参照)

性能の指標を議論するためには、いくつかの重要なパラメータを考慮する必要がある。これらのパラメータとは、出力電力 $P_{\text{out}}$ 、電力利得G、キャリア周波数f、線形性(IIP3 での)、および電力付加効率(PAE)である。不幸にも、線形性はアンプの動作級に強く依存する。このため、異なる動作級のアンプを比較することが困難となっている。さらには、将来における線形性に関する課題はデジタル校正手法により解決され得ると思われる。したがって、設計アプローチ手法やアプリケーション毎の固有の仕様といったものと無関係にするために、この線形性のパラメータを性能指数からは省略することにする。パワーアンプのRF利得の20dB/デケードのロールオフ $^{19}$ を補償するため $f^2$ のファクタを含めている。これらから性能指標(FoM)は次のように表すことができる。

THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS:

$<sup>^{19}</sup>$  Most CMOS PAs are currently operated in this regime. Using DC-gain for applications far below  $f_t$  would result in a slightly increased slope.

$$FOM_{PA} = P_{out} \cdot G \cdot PAE \cdot f^2$$

[3]

最後に、パワーアンプのアークテクチャとして最も単純な A 級動作 $^{20}$ に限定し、さらに単純化を行うことで、FOM とデバイス・パラメータ $^{21}$ との関係を与えることが可能となる。重要なデバイス・パラメータは、利用可能なインダクタの性能指数と $f_{max}$ である。クラス最高の CMOS パワーアンプの性能指標(FoM)は、能動デバイスと受動素子パラメータの改善に強く依存しており、最近では技術世代毎におおよそ 2 倍増加している。将来の技術世代に要求されるデバイス・パラメータ(RF and Analog/Mixed-signal Technologies for Wireless Communication の章のパワーアンプの表を参照)をもとに Table 10 に示される将来のパワーアンプに要求される性能指標(FoM)の要求値を類推することができる。

### アナログ-デジタル変換器(ADC)

デジタル処理システムはアナログの世界とのインタフェースを有している。それは、オーディオやビデオのインタフェース、磁気的あるいは光学的な記憶メディアへのインタフェース、さらに有線あるいは無線の伝送媒体へのインタフェースといったものである。アナログの世界は、ADCを介してデジタル信号処理の世界につながる。すなわち、ADCは、時間的にも信号振幅も連続的なアナログ信号を時間的に離散的(サンプリング)かつ信号振幅も離散的(量子化された)な量に変換する。したがって ADCは、システム・インテグレーションの観点から、将来のテクノロジの有効性や限界を明らかにする上で有効な性能指標になる。また、ADCは、今日の集積化ミックスド・シグナル回路設計において、最も重要かつ広く用いられているミックスド・シグナル回路である。

将来の技術世代の可能性を見込むために、ADC の性能指数(FoM)は、ダイナミックレンジ、サンプルレート  $f_{\text{sample}}$  それに消費電力 Pを考慮したものであるべきである。しかしながら、これらの名目的なパラメータは、変換器の実効的な性能への見識を与えるものではない。より正しい基準は、測定データから抽出される実効的な性能である。ダイナミックレンジは、低周波における信号対雑音および歪(SINAD<sub>0</sub>)の測定値から量子化誤差(これらの値は両方とも dB 単位)を引くことで得られる。SINAD<sub>0</sub> より"実効的な bit 数"が  $ENOB_0 = (SINAD_0 - 1.76)/6.02$  として与えられる。そして、ナイキスト基準とのリンクを保つために、次のことが行われる。つまり、実効的な帯域幅の倍の値(2×ERBW)が、もしより小さい値である場合には、サンプルレートの値が、この値で置き換えられる。

$$FoM_{ADC} = \frac{\left(2^{ENOB_0}\right) \times \min\left(\left\{f_{sample}\right\}, \left\{2 \times ERBW\right\}\right)}{P}$$

[4]

<sup>20</sup> R. Brederlow, S. Donnay, J. Sauerer, M. Vertregt, P. Wambacq, and W. Weber, "A mixed-signa design roadmap for the International Technology Roadmap for Semiconductors (ITRS)," IEEE Design and Test, December 2001.

2005

THE INTERNATIONAL TECHNOLOGY ROADMAP FOR SEMICONDUCTORS:

<sup>&</sup>lt;sup>21</sup> R. Brederlow, S. Donnay, J. Sauerer, M. Vertregt, P. Wambacq, and W. Weber, "A mixed-signal design roadmap for the International Technology Roadmap for Semiconductors (ITRS)," IEEE Design and Test, December 2001.

ADC に関して、性能指数 FoM とテクノロジパラメータの関係は、変換器のアーキテクチャや回路形式に強く依存する。ADC の複雑さと多様性は、性能指数とテクノロジパラメータの直接的な関連付けをほぼ不可能にする。RF 回路においては、この関連付けはある程度可能であった。にもかかわらず、性能指数に入れ込むパラメータに関する一般的な考察が行われている<sup>22</sup>。場合によっては、重要なサブ回路の性能要求から、デザインの性能要求を決めることができる。異なる ADC の設計に関連するデバイス・パラメータについては、RF and Analog/Mixed-signal Technologies for Wireless Communication の章にまとめられている。近年の傾向として、ADC の性能指数は3年ごとにおおよそ2倍改善している。設計上の知見が向上していることを考慮に入れると、過去の性能向上はアナログ素子のデバイス・パラメータの改善とよく一致している。自立型のCMOS/バイポーラCMOS(BiCMOS)の場合、現時点の最高クラスであるADCの性能は1600[ギガ変換/秒]であり、エンベディドCMOS の場合で800[ギガ変換/秒]である。ADC の性能指数の将来予想数値をTable10に示す。電源電圧や信号電圧振幅が減少する中で、ADC の性能向上をはかるために設計上の技術進歩が強く要求される。長期的には、基本的な物理的制約(例えば熱雑音)が、ADC の性能指数のさらなる改善の障害になるかもしれない。

|                                           | ,    | '    | 0       | G       | 5       |         | 71                                |

|-------------------------------------------|------|------|---------|---------|---------|---------|-----------------------------------|

| Year of Production                        | 2005 | 2008 | 2011    | 2014    | 2017    | 2020    | Driver                            |

| RF-CMOS ½ Pitch                           | 90   | 65   | 45      | 32      | 22      | 18      |                                   |

| FoM <sub>LNA</sub> [GHz]                  | 80   | 160  | 200–300 | 300–400 | 400–600 | 500-700 |                                   |

| FoM <sub>VCO</sub> [1/J] 10 <sup>22</sup> | 0.9  | 1.1  | 1.5     | 2       | 2.4     | 3       | Refer to the RF and AMS           |

| $FoM_{PA}$ [W× $GHz^2$ ] $10^4$           | 10   | 20   | 40      | 60-80   | 90–100  | 110–130 | Technologies for Wireless chapter |

| $FoM_{ADC}$ [GHz/W] $10^3$                | 1.2  | 2    | 3–4     | 4–10    | 6–20    | 8–40    |                                   |

*Table 10 Projected Mixed-Signal Figures of Merit for Four Circuit Types.*

#### ミックスド・シグナルの発展

ミックスド・シグナルのドライバの発展は、コストと性能の相互関係によって決定される。Table 10 に示される性能指標は、ミックスド・シグナル回路の性能をあらわします。しかしながら、現実のアナログ・ミックスド回路の開発においては、製品のコストも重大な問題である。コストと性能の両方が既存のアプリケーションに対して十分適応可能であるかを決定し、さらにコストと性能は既存の技術が新しいアプリケーションへの発展性を有しているかも決定する。

**コストの見積り** 大量生産されるデジタル製品においては、そのコストはほとんどチップ面積で決まっている。ところが、ミックスド・シグナルの設計においては、面積はいくつかのコスト要因の一つでしかない。 SoC におけるアナログ回路の占有面積は、通常、5~30%の範囲にある。したがって、ミックスド・シグナルの領域の面積を縮小しようとする経済的な圧力は、論理回路部分やメモリの部分に比べるとあまり強くない。 以下のような考察をすることができる。

- アナログ部分の面積は、システムにおけるアナログ部分とデジタル部分の切り分けを変えることで時として減らすことができる。(例えば ADC における自動校正機能やパワーアンプの線形性調整)

- 高性能のアナログ素子を導入するとプロセスが複雑化する。このような解決アプローチは、面積を削減 することには有効であるが、全体のコストを引き上げることになる。

- 使用する半導体技術の選択は、設計コストに影響を与える場合がある。というのは、ハードウェア設計

<sup>22</sup> R. Brederlow, S. Donnay, J. Sauerer, M. Vertregt, P. Wambacq, and W. Weber, "A Mixed-signal Design Roadmap for the International Technology Roadmap for Semiconductors (ITRS)," IEEE Design and Test, December 2001.

を何度もやり直すというリスクにつながるからである。(テープアウトに至る設計の繰り返し)

- 製造コストは、パラメータ歩留りがどの程度の感度を持っているかによっても影響を受ける。

- 複数のダイ(例えば、ダイサイズが大きく安価なデジタルチップと、ダイサイズの小さい高性能のアナログチップの組合せ)を使う SIP のような解決法の方が、SoC よりも安価になることもありえる。

このような考察は、ミックスド・シグナルの設計におけるコスト見積りを大変困難にする。まず最初に、高性能用途のみに議論を限定して、ミックスド・シグナルのコストを見積もることを試みる。というのは、このような用途というのは、テクノロジへの要求をドライブするものであるからである。次に、アナログ特性が高性能の受動素子やアナログトランジスタにより実現され、それらの面積がほぼコスト<sup>23</sup>に反映されることを注記しておく。トランジスタのスケーリングは、システムのデジタル部分の回路密度を向上させる目的でトランジスタの微細化が牽引されてきた。アナログトランジスタは、微細化の恩恵を受け、このことによりトランジスタのレイアウト密度も減少しているので特に言及する必要は無い。今日の多くのアナログ・ミックスド・シグナル回路の設計において、チップ面積はエンベディド受動素子の面積で決まっている。すなわち、これらの受動素子の面積がシステムのミックスド・シグナル部分のコストを決定している。したがって、Wireless 章における表は、高性能のミックスド・シグナル設計におけるコスト/性能比を向上させるのに必要なオンチップ搭載の受動素子のレイアウト密度のロードマップを示している。

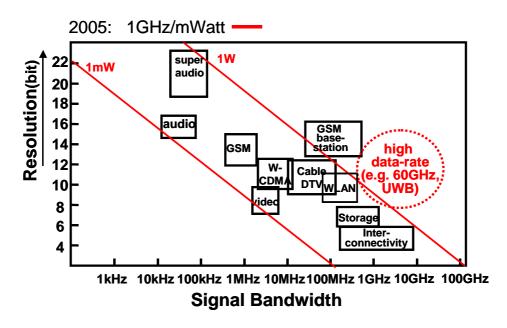

技術の充足度の見積り Figure 16 は、電力と性能の関係の観点で最近の応用分野ごとに ADC への要求を記載している。一定の性能(分解能×帯域幅)という条件のもとでの一定消費電力特性が傾き - 1 の直線で示されている。性能を向上するということは、よいテクノロジを使うか、回路設計を改善することで達成されるが、これは一定電力消費の線を右上に移動することと等価である。データによると、Table 10 に示される ADC の技術上の「バリア・ライン」は、1W の電力消費で表されているが、これは 10 年間で一桁程度しか移動していないことがわかる。今日の多くの ADC の技術(シリコン、SiGe、 - 族化合物半導体、それにこれらのハイブリッド)は、1W のバリア・ラインの下にある。そして、このバリア・ラインをより急速に引き上げるための解決策は見つかっていないが、2005 年の現状(GHz/mW)では、変換機能としては許容できる消費電力で高速データ通信分野に十分適応可能な位置にある。

Figure 16 Recent ADC Performance Needs for Important Product Classes

-

In analog designs, power consumption is often proportional to area—and since power is included in all four figures of merit, we have already implicitly considered area and cost criteria. Nonetheless, area requirements should be stated explicitly in a roadmap.

ADC の性能向上のペースはハンドセット(通信機)の用途に対しては十分であったが、GSM の基地局のデジタル線形化や、携帯応用における高データレートのデジタルビデオ用途に対しては、明らかに不足である。例えば、32 キャリアを扱うマルチキャリア GSM 基地局においては、80dB 以上のダイナミックレンジを必要とする。このような基地局において、25MHz の送信帯域幅でデジタル線形化を実現するためには、ADC に消費電力 1W 以下で 300MHz の標本化速度と 14bit の分解能が要求される。Table 10 と最近の進歩の具合を仮定すると、このような性能の ADC が量産されるのは恐らく 2010 年以降になるであろう。システム設計者は、現時点でもこのような性能の ADC を必要としている。シリコンと SiGe のテクノロジでは(多くのデバイスを一定の面積内に集積できることから)bit 分解能を達成することができるが、速度性能を達成することができない。反面、 - 族化合物半導体においては、速度目標を達成することはできるが、bit 分解能の方は達成できない。このことは、妥当なコストで、ADC の変換レートを上げる検討のための動機付けとなっている。例えば、CMOS と化合物半導体の混載を検討するといったことである。高性能パワーアンプを必要とするアプリケーションにおいては、Si-Ge ヘテロ接合バイポーラトランジスタ(HBTs)や III-V 化合物をパワーアンプに利用し、他のアナログフロントエンド部には CMOS を利用する SIP による解決が最適である。

新規製品分野の実現 通常の製品において、製品出荷を増やすために一般的に採られる戦略は、価格を下げて性能を上げることである。しかしながら、特にミックスド・シグナル部を含んでいる製品にとっては、この方策は半導体ビジネスにおいて唯一のものではない。技術と設計の改善により、新しい応用(近年の携帯電話のように)が生み出され、半導体産業は新しい市場に入ってゆくことができた。Figure16 に示されるミックスド・シグナルの設計に関する解析結果は、将来の製品や市場に向けた設計への要求や、設計の実現性を見積もることに使うことができる。性能を向上させることは、現時点の技術で実現されているものよりも高い性能や低い消費電力を必要とする新しい製品を開発できるということと等価であることがわかる。言い換えると、新しい製品の仕様がわかれば、これらの仕様を実現するために必要な半導体技術を見積もることができる。あるいは、半導体産業が妥当なコストと性能で製品を作ることができるようになるまでの時間を知ることができる。このように性能指数の概念は、新しいミックスド・シグナルの製品の市場の潜在性や実現可能性を評価することに使うことができる。高性能のミックスド・シグナルの回路を低コストで組み上げる能力は、半導体産業が新しい製品や市場を開拓する原動力となる。

#### ミックスド・シグナルにおけるチャレンジ

今日のミックスド・シグナルの設計のほとんど(特に古典的なアナログ設計において)は、処理対象の信号は、電圧の差として表されるので、電源電圧が最大の信号振幅を決定する。電源電圧の低下(定電界スケーリングの結果)は、最大の達成可能な信号レベルが下がることを意味する。このことは、SoC ソリューションのミックスド・シグナル製品の開発に対して大きな影響を与える。新しいミックスド・シグナル部分の開発は、一般的にデジタルやメモリ部分よりも多くの開発時間がかかる。設計リソースの不足は、別の重要なチャレンジとなる。理想的な設計プロセスは、既存のミックスド・シグナルの設計資産を再利用し、SoC と外部とのインタフェース仕様を整合するようにパラメータ調整をすることである。しかしながら、このような再利用をおこなうためには、最大動作電圧がスケーリングしないような別の MOSFET が必要となる。これは、PIDS 章でのミックスド・シグナルの CMOS トランジスタの特性として、高いアナログ供給電圧とこの電圧が複数のデジタルテクノロジ世代にわたって変更されず一定にとどまることにつながる。このようなデバイスをもってしても、アナログ回路プロックの電圧低下およびアナログ回路プロックの開発期間というものが、ミックスド・シグナル機能の低価格化と効率的なスケーリングに対して主要な障害となる。要約すると、最も困難なミックスド・シグナルにおけるチャレンジは以下のものであると言える。

供給電圧の低下:電流モード回路を使うこと、電圧を上げるためのチャージポンプ回路を使うこと そして、スタンダード・セル回路において、電圧の最適化が必要 (PIDS、設計)

- 相対的なパラメータのばらつきの増大: 能動的にパラメータのミスマッチを補償する機構の導入、製品の仕様決定の際に速度と分解能のトレードオフを行うことが必要 (PIDS、FET、リソグラフィ、設計)

- チップあたりのアナログトランジスタ数の増加: ミックスド・モードのシミュレーションツールの更なる高速処理、より正確なコンパクトモデル、および収束性の改善が必要 (モデリングとシミュレーション、設計)2

- *処理速度の向上(キャリア周波数およびクロック周波数)*: デバイスと配線を正確にモデリングすることに加えて、テスト能力、パッケージやシステムレベルのインテグレーションができることが必要 (テスト、実装およびパッケージング、モデリングとシミュレーション)

- SoC 集積に伴うクロストーク: 寄生効果のより正確なモデリング、RF 回路における完全差動回路の設計、これらに加えて PIDS 章に記載されている技術的な対処が必要 (PIDS、モデリングとシミュレーション、設計)

- *設計スキルおよび生産性の不足*: トレーニングが欠如していること、また、自動化が進んでいないことに起因する。教育と基本的な設計ツールに関する研究が必要(設計)

## 混載メモリ・ドライバ

SOC 設計は、混載される RAM や Read Only Memory(ROM)、そしてレジスタ・ファイルメモリの数や種類を益々増やしていくことを含んでいる。インターコネクトと IO 帯域幅、設計生産性、そしてシステム電力限界は、すべてマイクロエレクトロニクス・システムにおけるメモリ集積の高いレベルの継続的なトレンドを指し示している。混載メモリ技術をドライブするアプリケーションは、再構成可能な応用(たとえば、自動車用)のコード・ストレージであり、スマートまたはメモリ・カードのデータ・ストレージであり、そしてゲーム用あるいは大容量記憶システムに見られる高性能ロジックと混在する大容量メモリである。

ロジックとメモリのバランスは、総システム・コスト、電力や IO 制約、ハードウェア-ソフトウェア構成、そして全体的なシステムとメモリの階層に反映する。コストに関しては、デバイス性能とモノリシックなロジック-メモリ集積の追加マスク層は、チップ-積層-チップ、もしくは他のシステム・イン・パッケージ(SIP)集積の代案に対してバランスを保つ必要がある。ロジック-メモリ集積のレベルは、さらにコード-データ・バランス(たとえば、ソフトウェアはコードメモリに書かれ利用されるべきで、不揮発性やアプリケーションのデータはデータメモリに存在すべきである)だけでなく、ハードウェア-ソフトウェアの切り分けのトレードオフ(たとえば、ソフトウェアはより柔軟であるが、ブートしなければならず、より多くの面積を消費します)にも反映するであろう。IO ピン数と通信速度は、システム構成がどのように帯域幅対ストレージをトレードオフするかを決定する。つまり、1) メモリアクセスは、より高いもしくはより低いバンク・グループでメモリを構成する際の周辺オーバヘッドの代償によって速くすることができる。そして、2) アクセス速度は、ピンカウントと回路の複雑さを、高速少ピンカウント接続あるいは低速多ピンカウント接続の間でどのようにバランスさせるかにも依存する。

メモリ階層は、プロセッサの速度要求にメモリアクセスの能力が一致していることが重要である。この事実は伝統的なプロセッサ・アーキテクチャー領域ではよく知られており、プロセッサ・コアの"メイン"メモリとフォアグラウンド・メモリ(たとえば、レジスタ・ファイル)の間で、ハードウェア・コントロールのキャッシュのいくつかのレイヤーでの導入につながっている。各レイヤーでは、通常ひとつの物理キャッシュメモリが存在する。しかしながら、階層の選択は、さらに電力にとって強い意味合いを持つ。従来のアーキテクチャは、エネルギーの非効率的な制御オーバヘッドの代償に、たとえば、高次の連想キャッシュの周囲に含まれる予測/履歴メカニズムと余分なバッファにより、大きく性能を上げている。システムの観点から、ポータブル機器で主要な内蔵のマルチメディアや通信のアプリケーションは、ソフトウェア制御された分散のメモリ階層からより恩恵を受けることができる。メモリ階層の異なるレイヤーは、さらに高度な異なるアクセス・モードと内部分割を要求する。ページ/バースト/インターリーブといったモードの使用と、バンクの物理的な切り分け、サブアレイ、分割ワード/ビットラインは、一般にレイヤーごとに最適化されるに違いない。また、ますます支配的なリーク電力制約は、より異種混合のメモ

リ階層化に結びつく。

スケーリングは混載メモリ構造に多くの課題を提示する。回路レベルでは、SRAMのアンプ・センス・マージンおよび DRAMの減少した Ion ドライブ電流は、2 つの明確な課題である。より小さな形状は、ばらつき、たとえばデバイス当たりの少数のドーパントの、より大きな影響を暗示する。ひとつの製品の中に集積されるより多くのデバイスのために、ばらつきは、ノイズマージンとリーケパワー(リーケ電流の Vth への指数関数的な依存性があります)の両方に関して、より大きなパラメータの歩留まり損失につながる。将来の回路トポロジーと設計手法は、これらの問題に取り組む必要があるであるう。エラー耐性は、プロセス・スケーリングと積極的なレイアウト密度で深刻化するもう一つの課題である。混載メモリのソフト・エラー・レート(SER)は、形状の縮小につれ増加し、そして混載 SRAM および混載 DRAMともに影響する。これに関しては Design の章で議論される。不揮発性メモリでもビットの書き換えのときは、ソフト・エラーの影響を受けるかもしれない。特に、自動車部門でのような高度で信頼性のあるアプリケーションには、エラー訂正は、いずれくる要求であり、アクセス・タイム、パワー、およびプロセス・インテグレーションに対する歩留まりと信頼性のトレードオフを引き起こすであるう。最後に、大規模と異種混合メモリ・アレイのためのコスト効率のよい製造テストおよびビルトイン・セルフテストは、SOC における重要な要求である。

その高い繰り返しの割合から、メモリのセルサイズとパフォーマンスは、コストおよび性能に大きく直接の影響を持つので、ここで議論される他の基本回路すべてと比較して、最適化のために費やされる技術作業の量は大変高くなる。Table 11a と 11b は、3 つの現在主要なタイプの混載メモリ: CMOS 混載スタテック・ランダムアクセス・メモリ(SRAM)、混載不揮発性メモリ(NVM)、それに混載ダイナミック・ランダムアクセス・メモリ(DRAM)の技術要求を与える。それらのパラメータは、PIDS 章の中のロジック要求テーブルによって与えられた、回路設計考察と技術境界条件のバランスから発生する。CMOS SRAM の積極的なスケーリングは、高性能と低電力のドライバのため継続する。それらはノード当たり 0.7×のリード・サイクル・タイムのスケーリングを要求する。電圧スケーリングは、たとえば保持時間と読み出し動作電圧の間の関係、あるいは 45 nm ノードで始まる pMOS デバイス要求の電源やしきい値電圧スケーリングの影響と、多数の考察を伴う。発生期の強誘電体RAM、磁気抵抗 RAM、それに相変化メモリ技術は、PIDS 章の Emerging Research Devices 節で議論されている。

Table 11a Embedded Memory Requirements—Near-term

| Year of Production                                                                                              | 2005                              | 2006                              | 2007                              | 2008                              | 2009                              | 2010                              |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

| DRAM ½ Pitch (nm)                                                                                               | 80                                | 70                                | 65                                | 2008<br>55                        | 50                                | 45                                |

| DRAM ½ Pitch (nm)  CMOS SRAM High-performance, low standby power (HP/LSTP)  DRAM ½ pitch (nm), Feature Size – F | 90                                | 90                                | 65                                | 65                                | 65                                | 45                                |

| 6T bit cell size ( $\mathbb{F}^2$ ) [1]                                                                         | 140F <sup>2</sup>                 |

| Array efficiency [2]                                                                                            | 0.7                               | 0.7                               | 0.7                               | 0.7                               | 0.7                               | 0.7                               |

| Process overhead versus standard CMOS –<br>number of added mask layers [3]                                      | 1                                 | 2                                 | 2                                 | 2                                 | 2                                 | 2                                 |

| Operating voltage – V <sub>dd</sub> (V) [4]                                                                     | 1.1/1.2                           | 1.1/1.2                           | 1.1                               | 1/1.1                             | 1/1.1                             | 1                                 |

| Static power dissipation (mW/Cell) [5]                                                                          | 1.5E-4/6E-7                       | 1.5E-4/6E-7                       | 3E-4/1E-6                         | 3E-4/1E-6                         | 3E-4/1E-6                         | 5E-4/1.2E-6                       |

| Dynamic power consumption per cell – (mW/MHz) [6]                                                               | 7E-7/8.5E-7                       | 6E-7/8E-7                         | 4.5E-7/7E-7                       | 4E-7/6.5E-7                       | 4E-7/6E-7                         | 3E-7/5E-7                         |

| Read cycle time (ns) [7]                                                                                        | 0.4/2                             | 0.4/2                             | 0.3/1.5                           | 0.3/1.5                           | 0.3/1.5                           | 0.2/1.2                           |

| Write cycle time (ns) [7]                                                                                       | 0.4/2                             | 0.4/2                             | 0.3/1.5                           | 0.3/1.5                           | 0.3/1.5                           | 0.2/1.2                           |

| Percentage of MBU on total SER                                                                                  | 8%                                | 8%                                | 16%                               | 16%                               | 16%                               | 32%                               |

| Soft error rate (FIT/Mb) [8]                                                                                    | 1100                              | 1100                              | 1150                              | 1150                              | 1150                              | 1200                              |

| Embedded Non-Volatile Memory (code/data), DRAM ½ pitch (nm)                                                     | 130                               | 130                               | 90                                | 90                                | 90                                | 65                                |

| Cell size (F <sup>2</sup> ) –<br>NOR FLOTOX /NAND FLOTOX [9]                                                    | 10F <sup>2</sup> /5F <sup>2</sup> |

| Array efficiency –<br>NOR FLOTOX/NAND FLOTOX [10]                                                               | 0.6/0.8                           | 0.6/0.8                           | 0.6/0.8                           | 0.6/0.8                           | 0.6/0.8                           | 0.6/0.8                           |

| Process overhead versus standard CMOS – number of added mask layers [11]                                        | 6–8                               | 6–8                               | 6–8                               | 6–8                               | 6–8                               | 6–8                               |

| Read operating voltage (V)                                                                                      | 2.5V                              | 2.5V                              | 2V                                | <b>2V</b>                         | 2V                                | 1.8V                              |

| Write (program/erase) on chip maximum voltage (V) – NOR/NAND [12]                                               | 12V/15V                           | 12V/15V                           | 12V/15V                           | 12V/15V                           | 12V/15V                           | 12V/15V                           |

| Static power dissipation (mW/Cell) [5]                                                                          | 1.E-06                            | 1.E-06                            | 1.E-06                            | 1.E-06                            | 1.E-06                            | 1.E-06                            |

| Dynamic power consumption per cell – (mW/MHz) [6]                                                               | 0.8E-08                           | 0.8E-08                           | 0.6E-08                           | 0.6E-08                           | 0.6E-08                           | 0.6E-08                           |

| Read cycle time (ns) NOR FLOTOX /NAND FLOTOX [7]                                                                | 14/70                             | 14/70                             | 10/50                             | 10/50                             | 10/50                             | 7/35                              |

| Program time per cell (µs)<br>NOR FLOTOX /NAND FLOTOX [13]                                                      | 1.0/1000.0                        | 1.0/1000.0                        | 1.0/1000.0                        | 1.0/1000.0                        | 1.0/1000.0                        | 1.0/1000.0                        |

| Erase time per cell (ms) NOR FLOTOX /NAND FLOTOX [13]                                                           | 10.0/0.1                          | 10.0/0.1                          | 10.0/0.1                          | 10.0/0.1                          | 10.0/0.1                          | 10.0/0.1                          |

| Data retention requirement (years) [13]                                                                         | 10                                | 10                                | 10                                | 10                                | 10                                | 10                                |

| Endurance requirement [13]                                                                                      | 100000                            | 100000                            | 100000                            | 100000                            | 100000                            | 100000                            |

| Embedded DRAM, ½ pitch (nm)                                                                                     | 130                               | 90                                | 90                                | 90                                | 65                                | 65                                |

| 1T1C bit cell size (F <sup>2</sup> ) [14]                                                                       | 12–30                             | 12–30                             | 12-30                             | 12–30                             | 12–30                             | 12–30                             |

| Array efficiency [2]                                                                                            | 0.6                               | 0.6                               | 0.6                               | 0.6                               | 0.6                               | 0.6                               |

| Process overhead versus standard CMOS – number of added mask layers [3]                                         | 3–5                               | 3–5                               | 3–5                               | 3–5                               | 3–5                               | 3–5                               |

| Read operating voltage (V)                                                                                      | 2.5                               | 2                                 | 2                                 | 2                                 | 1.8                               | 1.7                               |

| Static power dissipation (mW/Cell) [5]                                                                          | 1E-11                             | 1E-11                             | 1E-11                             | 1E-11                             | 1E-11                             | 1E-11                             |

| Dynamic power consumption per cell – (mW/MHz) [6]                                                               | 1.E-07                            | 1.E-07                            | 1.E-07                            | 1.E-07                            | 1.E-07                            | 1.5E-07                           |

| DRAM retention time (ms) [13]                                                                                   | 64                                | 64                                | 64                                | 64                                | 64                                | 64                                |

| Read/Write cycle time (ns) [7]                                                                                  | 1                                 | 0.7                               | 0.7                               | 0.7                               | 0.5                               | 0.4                               |

| Soft error rate (FIT/Mb) [8]                                                                                    | 60                                | 60                                | 60                                | 60                                | 60                                | 60                                |

FIT—failures in time FLOTOX—floating gate tunnel oxide MBU—multiple bit upsets NAND—not an "AND" logic operation NOR—not an "OR" logic operation

Table 11b Embedded Memory Requirements—Long-term\*

| Table 110 Embedaed Memory I                                                                      | tequirements      | Long term        | ı                 |

|--------------------------------------------------------------------------------------------------|-------------------|------------------|-------------------|

| Year of Production                                                                               | 2012              | 2015             | 2018              |

| DRAM ½ Pitch (nm)                                                                                | 36                | 25               | 18                |

| CMOS SRAM High-performance, low standby power (HP/LSTP)<br>DRAM 1/2 pitch (nm), Feature Size – F | 35                | 25               | 18                |

| 6T bit cell size (F <sup>2</sup> ) [1]                                                           | 140F <sup>2</sup> | $140F^2$         | 140F <sup>2</sup> |

| Array efficiency [2]                                                                             | 0.7               | 0.7              | 0.7               |

| Process overhead versus standard CMOS – number of mask adders [3]                                | 2                 | 2                | 2                 |

| Operating voltage – V <sub>dd</sub> (V)                                                          | 0.9/1             | 0.8/0.9          | 0.7/0.8           |

| Static power dissipation (mW/Cell) [5]                                                           | 1E-3/1.5E-6       | 2E-3/2E-6        | 3E-3/2.5E-6       |

| Dynamic power consumption per cell – (mW/MHz) [6]                                                | 2.5E-7/4.5E-7     | 2E-7/4E-7        | 1.5E-7/3E-7       |

| Read cycle time (ns) [7]                                                                         | 0.15/0.8          | 0.1/0.5          | 0.07/0.3          |

| Write cycle time (ns) [7]                                                                        | 0.15/0.8          | 0.1/0.5          | 0.07/0.3          |

| Percentage of MBU on total SERs                                                                  | 64%               | 100%             | 100%              |

| Soft error rate (FIT/Mb) [8]                                                                     | 1250              | 1300             | 1350              |

| Embedded Non-Volatile Memory (code/data), DRAM ½ pitch (nm)                                      | 45                | 35               | 25                |

| Cell size (F <sup>2</sup> ) – NOR FLOTOX/NAND FLOTOX [9]                                         | $10F^{2}/5F^{2}$  | $10F^{2}/5F^{2}$ | $10F^{2}/5F^{2}$  |

| Array efficiency – NOR FLOTOX/NAND FLOTOX [10]                                                   | 0.6/0.8           | 0.6/0.8          | 0.6/0.8           |

| Process overhead versus standard CMOS – number of mask adders [3]                                | 6–8               | 6–8              | 6–8               |

| Read operating voltage (V) [4]                                                                   | 1.5V              | 1.3V             | 1.2V              |

| WRITE (program/erase) on chip maximum voltage (V) – NOR/NAND [4]                                 | 12V/15V           | 12V/15V          | 12V/15V           |

| Static power dissipation (mW/Cell) [5]                                                           | 1.E-06            | 1.E-06           | 1.E-06            |

| Dynamic power consumption per cell – (mW/MHz) [6]                                                | 0.4E-8            | 0.35E-8          | 0.3E-8            |

| Read cycle time (ns)                                                                             | 5/25              | 3.5/18           | 2.5/12            |

| Program time per cell (μs) [13]                                                                  | 1.0/1000.0        | 1.0/1000.0       | 1.0/1000.0        |

| Erase time per cell (ms) [13]                                                                    | 10.0/0.1          | 10.0/0.1         | 10.0/0.1          |

| Data retention requirement (years) [13]                                                          | 10                | 10               | 10                |

| Endurance requirement [13]                                                                       | 100000            | 100000           | 100000            |

| Embedded DRAM, ½ pitch (nm)                                                                      | 45                | 35               | 25                |

| 1T1C bit cell size (F <sup>2</sup> ) [14]                                                        | 12–30             | 12-30            | 12–30             |

| Array efficiency [2]                                                                             | 0.6               | 0.6              | 0.6               |

| Process overhead versus standard CMOS – number of mask adders [3]                                | 3-6               | 3-6              | 3-6               |

| Read operating voltage (V)                                                                       | 1.6               | 1.5              | 1.5               |

| Static power dissipation (mW/Cell) [5]                                                           | 1E-11             | 1E-11            | 1E-11             |

| Dynamic power consumption per cell – (mW/MHz) [6]                                                | 1.6E-07           | 1.7E-07          | 1.7E-07           |

| DRAM retention time (ms) [13]                                                                    | 64                | 64               | 64                |

| Read/Write cycle time (ns) [7]                                                                   | 0.3               | 0.25             | 0.2               |

| Soft error rate (FIT/Mb) [8]                                                                     | 60                | 60               | 60                |

<sup>\*</sup>Figure 11b data will be annualized in 2006. For the 2005 ITRS, long-term years are 2014–2020.

#### Figure11aと11bの注記:

- [1] 最小加工寸法の関数としての標準 6T CMOS SRAM のサイズ。

- [2] (コア面積/メモリインスタンス面積)として定義される標準的なアレイ効率。

- [3] 同等テクノロジの標準的な CMOS ロジックプロセスに対して追加される標準的なマスク枚数。通常は0であるが、いく つかの高性能もしくは高信頼性(ノイズ耐性)SRAM において、より良いノイズマージンの為の高 Vth pMOS セルトランジスタの追加や高 Vdd の使用、もしくは高速読み出しの為のゼロ Vth アクセストランジスタなどのようないくつかの特別なプロセスオプションを適用する場合がある。

- [4] PIDS 章の logic device requirements table で示される HP と LSTP デバイスの標準動作電圧。

- [5] スタンバイモードでのセル毎の静的電力消費。これは、I\_Standby x Vdd で測定される(PIDS 章の logic device requirements table 中の HP と LSTP デバイスから得られたオフ電流と Vdd)。

- [6] このパラメータはアレイアーキテクチャーに強く依存する。しかし、テクノロジのパラメータとしてセルレベル毎に決めることができる。 ワードライン (WL) は Vdd フルスイング、ビットライン (BL) は  $0.8\,$  Vdd のスイングと仮定する。 セル毎の WL 容量(CWL)と BL 容量(CBL)を決める。 そのとき、セル毎・1MHz 毎のダイナミック電力消費は  $V_{dd}\times CWL$  (per cell)  $\times$  ( $V_{dd}$ )  $\times$   $V_{dd}\times CBL$  (per cell)  $\times$  ( $V_{dd}$ )  $\times$   $V_{dd}\times CBL$  (per cell)  $\times$  ( $V_{dd}$ )  $\times$   $V_{dd}\times CBL$  (per cell)  $\times$  ( $V_{dd}$ )  $\times$   $V_{dd}\times CBL$  (per cell)  $\times$  ( $V_{dd}$ )  $\times$   $V_{dd}\times CBL$  (per cell)  $\times$  ( $V_{dd}$ )  $\times$   $V_{dd}\times CBL$  (per cell)  $\times$   $V_{dd}\times CBL$   $V_{dd}\times CBL$  (per cell)  $V_{dd}\times CBL$   $V_{dd}\times CBL$   $V_{dd}\times CBL$  (per cell)  $V_{dd}\times CBL$

- [7] read cycle time は、アドレスからリード動作を完了するまでの標準的な時間である。これは、メモリサイズやアーキテク チャに依存する。 write cycle time はアドレスからライト動作を完了するまでの標準的な時間である。 これは、メモリサイズや アーキテクチャに依存する。

- [8] 1 FIT は、10 億時間に 1 度の誤動作を表す。このデータは Mbit 当たりの FIT 数である。

- [9] 標準的な 1T FLOTOX セルサイズ / 標準的な 2T Select Gate(SG) セルサイズ / 標準的な NAND セルサイズ。セルサ イズは、集積化の課題の為に単体の不揮発性メモリと比較し、多少増加される。

- [10] 標準的なスタックゲート NOR アーキテクチャ / 標準的なスプリットゲート NOR アーキテクチャ / 標準的な NAND ア ーキテクチャのアレイ効率。データは、PIDS 章の NVM device requirements table を参照する。

- [11] 標準的な CMOS プロセスに比較すると、技術を実現するには特別なプロセスステップが必要である。

- [12] 動作に要求される最大電圧で、通常はライト動作で利用される。データは、PIDS 章の NVM device requirements table を参照する。

- [13] program time per cell は、ひとつのセルにデータをプログラムするのに必要な標準的な時間である。erace time per cell は、ひとつのセルを消去するのに必要な標準的な時間である。data retention requirement は、最悪な条件下でさえもデ ータが不揮発でありつづけなければならない持続時間である。Endurance requirement は、セルがプログラムそして消去さ れることのできる回数である。

- [14] トレンチ構造の混載 DRAM の標準的なセルサイズ。データは PIDS 章の DRAM requirements table を参照する。