# トータルテストソリューション - DFTとATEの競合と協調 -

WG2(テスト)主査 畠山 一実(ルネサステクノロジ)

STRJ WS: March 4, 2004, WG2

## トータルテストソリューション

・デバイスのトレンド 論理規模増大,メモリ規模増大,プロセス微細化, 設計マージンの低下テストコスト増大,テスト品質低下

- ・対応策は?

- ・ATEの改善従来どおりの設計でも対応可能

- ・DFTの採用 古いテスタでも対応可能

このような対応策はすぐに限界

## トータルテストソリューション(DFTとATEの協調)が必須

DFT: Design for Test ATE: Automatic Test Equipment

## 微細化のテストへのインパクト

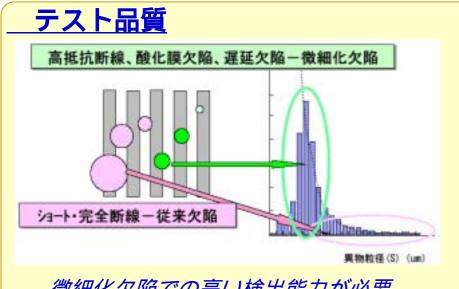

微細化欠陥での高い検出能力が必要

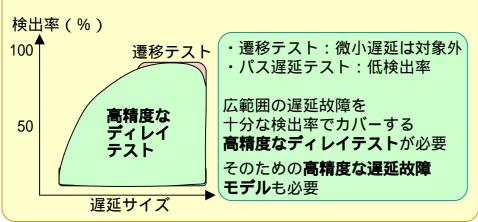

#### 高精度ディレイテスト

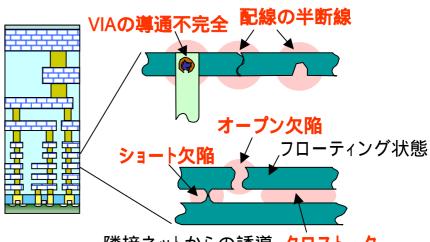

#### ナノメータプロセスの複雑な故障欠陥

隣接ネットからの誘導 クロストーク

#### SI故障モデル

|         | stuck-at | short | open | delay | X-talk |

|---------|----------|-------|------|-------|--------|

| EM      |          |       |      |       |        |

| X-talk  |          |       |      |       |        |

| IR-drop |          |       |      |       |        |

| EMI     |          |       |      |       |        |

X-talk故障モデルによるテスト・診断が必要

## 2003年度の活動体制

STRJ-WG2(テスト)(23名)

DFT-SWG(9名)

委員 : 富士通 ルネサス 松下 NECEL 沖 東芝 ローム

特別委員:都立大 STARC

-ATE-SWG(14名)

委員 : 富士通 ルネサス 松下 NECEL シャープ 東芝

特別委員:<u>SEAJ(7名)</u>

アドバンテスト 横河電機 シバソク 日本マイクロニクス 東京エレクトロン イノテック

SEAJ:日本半導体製造装置協会

## <u>2003年度の活動のポイント</u>

- ・ITRS2003への貢献

- ・DFT-SWG:SoCテスト技術

- ・ ATE-SWG: テスタ周辺技術

- ・STRJとしての活動

- トータルテストソリューションの検討

- DFT-SWG: SoCモデルに基づく具体的指標

- ATE-SWG: SoC/SiPテストの課題と対策

- ・合同会議および合宿での議論により融合を図る DFTとATEの協調は可能か

## ITRS2003の概要 - Key Challenges

- ・高速シリアルI/Fのテスト

- ・SoCとSiPのテスト

SoCテスト

- ・信頼性スクリーニング

- ・テストコスト削減

ハンドラ&プローバ, デバイスI/F

- New! ← 故障診断・テストプログラム生成

- ・モデリングとシミュレーション

## ITRS2003の概要 - SoCテスト

## ・技術分野ごとに課題を抽出

(ITRS2001:Supplementary Material)

#### ・関連性を考慮して分類

SoCテスト技術課題/関連技術課題

- ・SoC**のイメージに沿った分類に見直し**(ITRS2003)

- Embedded Cores: Logic, Memory, Analog

- Core Access

- SoC Level Testing

- Manufacturing

| Year of Production                       | 2003                                       | 2004      | 2005       | 2006                      | 2007                      | 2008                      |  |  |  |  |  |

|------------------------------------------|--------------------------------------------|-----------|------------|---------------------------|---------------------------|---------------------------|--|--|--|--|--|

| Embedded Cores                           |                                            |           |            |                           |                           |                           |  |  |  |  |  |

| Standardization of core test data        |                                            |           | on EDA/ATE | Extension to analog cores | Extension to analog cores | Extension to analog cores |  |  |  |  |  |

| Embedded Cores: Logic                    |                                            |           |            |                           |                           |                           |  |  |  |  |  |

| Test logic insertion at RTL design       | Partially                                  | Partially | Fully      | Fully                     | Fully                     | Fully                     |  |  |  |  |  |

| BISR for logic cores                     | Minimal                                    | Minimal   | Minimal    | Some                      | Some                      | Some                      |  |  |  |  |  |

| Embedded Cores: Memory                   | ,                                          |           |            | -                         | -                         | -                         |  |  |  |  |  |

| Embedded non-volatile memory BIST        |                                            |           | Yes        | Yes                       | Yes                       | Yes                       |  |  |  |  |  |

| SoC Level Testing                        |                                            |           |            |                           |                           |                           |  |  |  |  |  |

| Fault model for SoC level fault coverage | ault model for SoC level   Single stuck-at |           | Yes        | Yes                       | Yes                       | Yes                       |  |  |  |  |  |

-

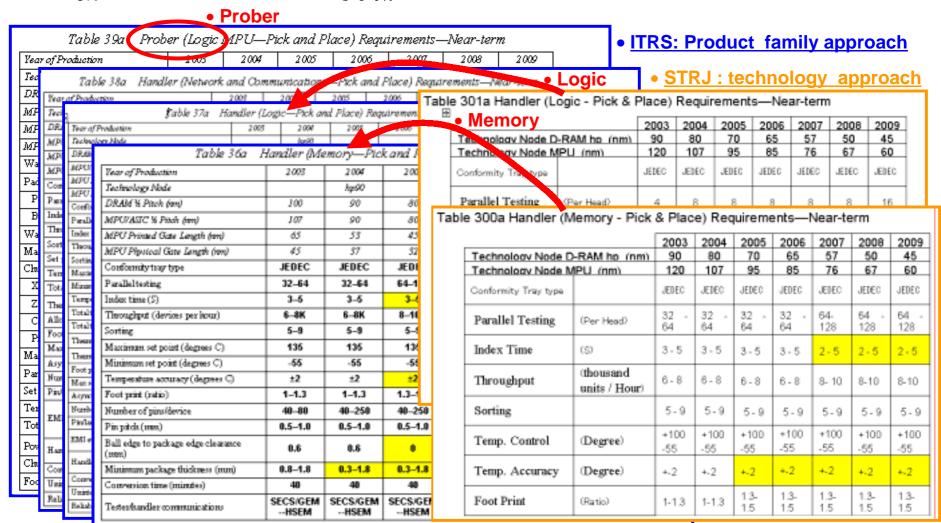

## ITRS2003の概要 - ハンドラ&プローバ

- ハンドラのRM表が初めて日米合意の上で正式掲載

- 新たにプローバのRMも掲載

## ITRS2003の概要 - デバイスI/F

- プローブカードのRM表が初めて日米合意の上で正式掲載

- 表の形態は米国側提案で決着 ただし,日本提案の数値でRM化,日本の提案も巻外に参考添付

- ITRS: Product family approach

#### • STRJ : Probe technology approach

| Year of Production                  | 20              | 003           | 2004           |                |  |

|-------------------------------------|-----------------|---------------|----------------|----------------|--|

| Technology Node                     |                 |               | hp90           |                |  |

| I/O Pad Size (µm)                   | х               | X Y           |                |                |  |

| Wirebond                            | 40              | 70            | 35             |                |  |

| Bump                                | 75              | 75            | 75             |                |  |

| Scrub (% of I/O)                    | AREA            | DEPTH         | AREA           |                |  |

| Wirebond                            | 25              | 75            | 25             |                |  |

| Bump                                | 30              |               | 30             | 30             |  |

| Multi-DUT Volume (% of To           | otal P _act Typ | oe Wafers     | s Probed       | )              |  |

| Memory (DRAM)                       | · ·             | JU.3          |                | .9             |  |

| ASIC                                | 3               | 33            |                | 5              |  |

| Microprocessor                      | (               | 60            |                | 5              |  |

| RF                                  | 3               | 30            | 4              | 0              |  |

| Mixed-signal                        | 4               | 10            | 45             |                |  |

| Number of Probe Points<br>Touchdown | Signal          | Total         | Signal         | Total          |  |

| Memory (DRAM)                       | 1730-<br>5180   | 2240-<br>6720 | 1730-<br>10260 | 2240-<br>13300 |  |

| ASIC                                | 775             | 1550          | 950            | 1900           |  |

| Microprocessor                      | 310             | 925           | 400            | 1200           |  |

| RF                                  | 180             | 325           | 235            | 425            |  |

| KF                                  |                 |               |                |                |  |

Product family vs function and performance of Probe card

|   |                         |                                                                                                                                                                                                                     | 2003       | 2004   | 2005   |        |

|---|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|--------|--------|

|   | Technology No           | de D-RAM hp                                                                                                                                                                                                         | 90         | 80     | 70     |        |

| ſ | Technology No           | de MPU (nm)                                                                                                                                                                                                         | )          | 120    | 107    | 95     |

|   |                         |                                                                                                                                                                                                                     | 50         | 50     | 50     |        |

| H | ш                       |                                                                                                                                                                                                                     | 30         | 30     | 30     |        |

| ř | <b>^</b>                | ριτοιτ (μ΄ ιτι)                                                                                                                                                                                                     | Area array | 150    | 150    | 150    |

| 4 | (1) 1                   | Maximal                                                                                                                                                                                                             | L.O.C.     | 3200   | 3200   | 2200   |

|   | Cantilever /            | Pin count                                                                                                                                                                                                           | Peripheral | 2000   | 2000   | 2000   |

| ١ | Conventional            |                                                                                                                                                                                                                     | Area array | 1300   | 1300   | 1300   |

| ١ |                         |                                                                                                                                                                                                                     | L.O.C.     | 64     | 64     | 64     |

| 4 |                         |                                                                                                                                                                                                                     | Peripheral | 4~8    | 4~8    | 4~8    |

| ı |                         | Area array                                                                                                                                                                                                          |            | 2      | 2      | 2      |

| ١ |                         |                                                                                                                                                                                                                     | Q.C.       | 80     | 60     | 60     |

| ١ |                         |                                                                                                                                                                                                                     | Peripheral | 80     | 80     | 80     |

|   |                         | Maximal milever / nventional  Multi-die test A  Minimal pitch (μ m) A  Minimal pitch (μ m) A  Maximal Pin count P  A  Multi-die test A  Minimal pitch (μ m) A  Multi-die test P  Multi-die test P  Multi-die test P | Area array | N/A    | N/A    | N/A    |

|   | Probe card              | Maximal                                                                                                                                                                                                             | L.O.C.     | 30~100 | 30~100 | 30~100 |

|   | (1) – 2<br>Cantilever / | Pin count                                                                                                                                                                                                           | Peripheral | 60~400 | 60~400 | 60~400 |

|   | HF type                 |                                                                                                                                                                                                                     | Area array | N/A    | N/A    | N/A    |

|   |                         |                                                                                                                                                                                                                     | L.O.C.     | 1      | 1      | 1      |

| ı |                         |                                                                                                                                                                                                                     | Peripheral | 1      | 1      | 1      |

| ١ |                         | เยรเ                                                                                                                                                                                                                | Area array | N/A    | N/A    | N/A    |

| ľ |                         |                                                                                                                                                                                                                     |            |        |        |        |

Probe card technology vs Suitable Probe card for the arrangement bond pad of the DUT (=Function)

|                                                | 2003     | 2004  |

|------------------------------------------------|----------|-------|

| Technology Node D-RAM hp (nm)                  | 90       | 80    |

| Technology Node MPU (nm)                       | 120      | 107   |

| 1. Positional accuracy ( ± u m): Maximal       |          |       |

| (1) - 1 Cantilever / Conventional              | ± 5      | ± 5   |

| (1) - 2 Cantilever / HF type                   | ± 5      | ± 5   |

| (2) - 1 Cantilever / New generation            | ± 3      | ± 3   |

| (1) - 4 Aembrane type                          |          |       |

| (1) - 3 Vertical / Conventional                | ± 5      | ± 5   |

| (2) - 2 Vertical / New generation              | ± 3      | ± 3   |

| 2. Co-planarity (u m): Maximal                 |          |       |

| (1) - 1 Cantilever / Conventional              | 15       | 15    |

| (1) - 2 Cantilever / HF type                   | 15       | 15    |

| (2) - 1 Cantilever / New generation            | 15       | 15    |

| (1) - 4 Membrane type                          |          |       |

| (1) - 3 Vertical / Conventional                | 25       | 25    |

| (2) 2 Ventical / New constant                  | 15       | 15    |

| 3. Contact Force: mN / over drive (u m ) / pin | (1mN=0.1 |       |

| (1) - 1 Cantilever / Conventional              | 50/60    | 50/60 |

| (1) - 2 Cantilever / HF type                   | 50/60    | 50/60 |

| (2) - 1 Cantilever / New generation            | 50/60    | 50/60 |

| (1) - 4 Membrane type                          |          |       |

| (1) - 3 Vertical / Conventional                | 70/60    | 70/60 |

| (2) - 2 Vertical / New generation              | 20/50    | 15/50 |

Probe card technology vs

Performance of Probe card

# ITRS2003の概要 - デバイスI/F

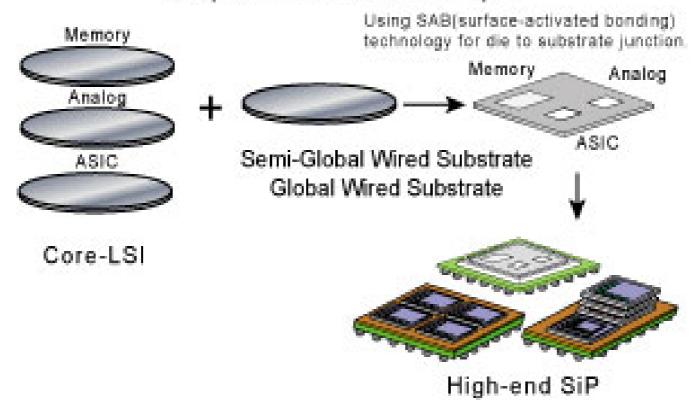

• SiPテストの課題について提案 RM化には至らなかったが,本文の随所で今後の課題として言及

## Super-connect technique

STRJ WS: March 4, 2004, WG2

# SWGごとの活動状況

・ DFT-SWG: SoCモデルに基づく具体的指標

・ATE-SWG: SoC/SiPテストの課題と対策

## <u>2003年度 DFT-SWGの活動状況</u>

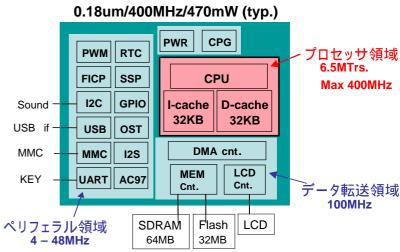

## 90nm 65nm世代のテスト指標の策定

- ・テスト課題を解決するにあたっての DFTとATEに望まれるテスト技術指標 を検討

- ・SoCモデルを策定し指標化を実施

参考:「設計TF/PIDS/FEPクロスカット

活動報告(2002)」

モバイルマルチメディア向け

SoCモデル

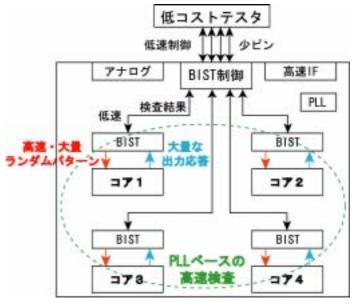

・BISTを用いた低コストテスタによる 実速度検査を想定

BIST: Built-in Self Test

設計TF/PIDS/FEPクロスカット活動報告(2002)より

STRJ WS: March 4, 2004, WG2

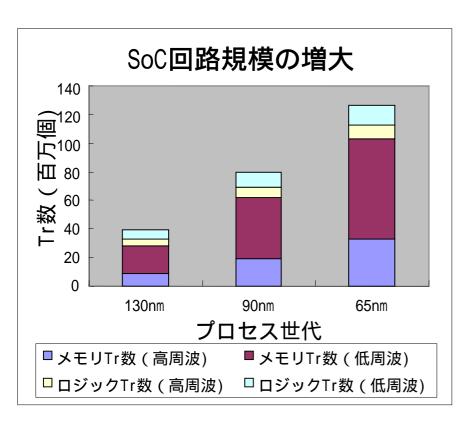

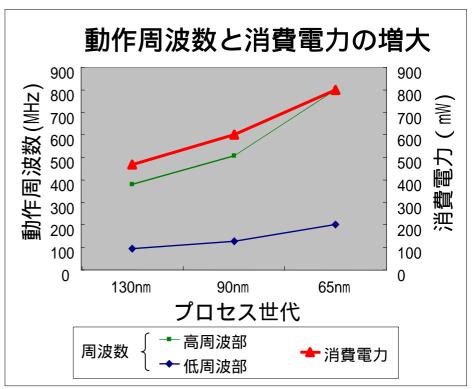

## SoCモデル:動作周波数と消費電力

・低電力を目的としたSoCにおいても、微細化とともにトランジスタ数の増大と高速化により消費電力が増大

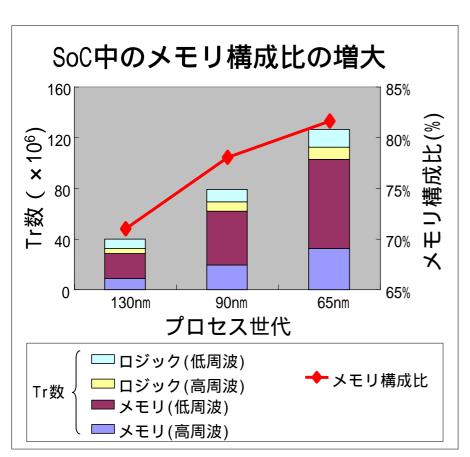

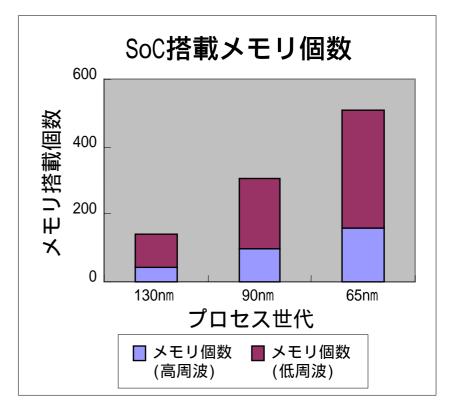

# SoCモデル:搭載メモリの構成比が増大

- ・SoC中の構成比においては,65nmではメモリが80%以上

- ・メモリ搭載数が増加を続け,65nmでは500個超

## ランダムパターンロジックBIST技術の課題

|                 | 90nm       | 65nm        |

|-----------------|------------|-------------|

| 面積オーバヘッド(Scan比) | 3 ~ 5%     |             |

| 設計TATオーバヘッド     | 1 ~ 2Week  | 1.5 ~ 3Week |

| テストパターン長        | 64K ~ 100K |             |

| テスト時間(WT/FT:各々) | 1秒         |             |

| シフト動作速度         | 30 ~ 40MHz | 50 ~ 65MHz  |

#### ・その他の課題

- 1. テスト時間と消費電力のトレードオフ

- 2. シフト動作とキャプチャ動作の切替え時の電圧安定策も必要

- 3. 故障モデル:高精度ディレイ故障,クロストーク故障への対応

## パターン圧縮ロジックBIST技術の課題

|                     | 90nm       | 65nm       |

|---------------------|------------|------------|

| 面積オーバヘッド(Scan比)     | 0.5 ~ 3%   | 0.3~2.5%   |

| 設計TAT <b>オーバヘッド</b> | 0 ~ 1Week  |            |

| テストパターン長            | 5K ~ 25K   | 10K ~ 50K  |

| テスト時間(WT/FT:各々)     | 0.2~0.5秒   | 0.3~0.7秒   |

| シフト動作速度             | 30 ~ 40MHz | 50 ~ 65MHz |

#### ・課題

- 1. パターン長を削減する方策(例えば検査点挿入)

- 2. シフト動作とキャプチャ動作の切替え時の電圧安定策

- 3. 故障モデル:高精度ディレイ故障,クロストーク故障への対応

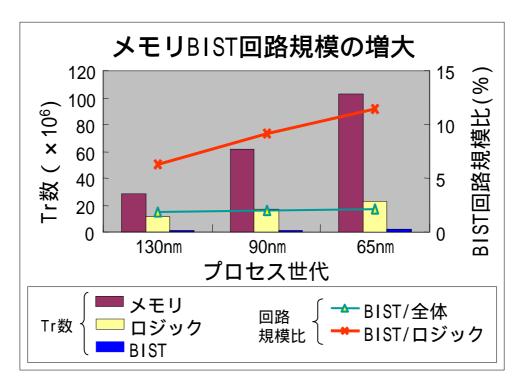

## メモリBIST技術の課題

- ・搭載メモリ個数の増加に伴い,メモリBIST回路規模が増大90nm(300個):200~600kゲート65nm(500個):330k~1Mゲート

- ・課題 設計初期段階におけるメモリBIST回路規模の見積りと最適化

# SWGごとの活動状況

・ DFT-SWG: SoCモデルに基づく具体的指標

・ATE-SWG: SoC/SiPテストの課題と対策

## <u>ATE-SWG:SoC/SiPテストの課題と対策</u>

- '03年度活動概要 -

< 今年度の活動方針 >

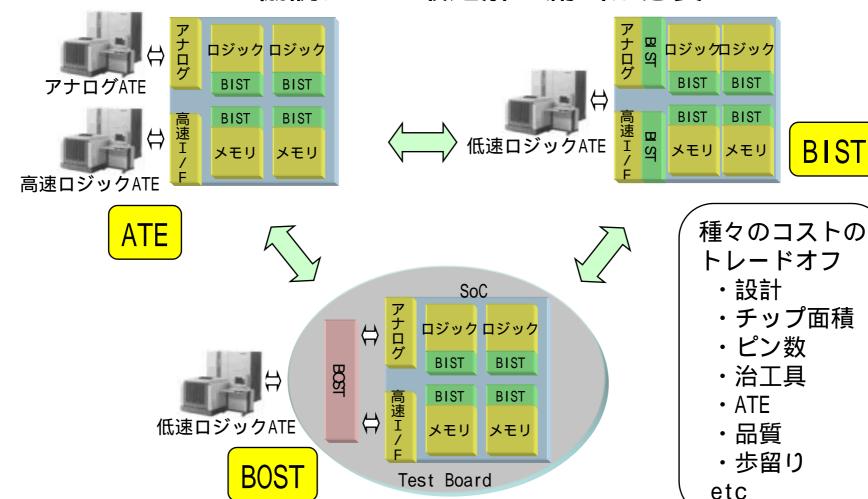

SoCは,SoC内の各機能プロック(ロジック,メモリ,アナログ)にコアアクセス機能を付加して個別にテストできるようにすることでSiPと同等とした

- 1. SiPテストの取り組み

- 2. WLBIの位置付けと取り組み (SEAJの検査WGと協働)

WLBI: Wafer Level Burn-in

- 3. ATE**コスト低減への取り組み**

- \*SoC対応DFTテスタへの提言('04年度継続審議)

- \*テスタ構造表現言語 ('04年度継続審議)

- \* M&S(テストボード) (SEAJの検査WGと協働)

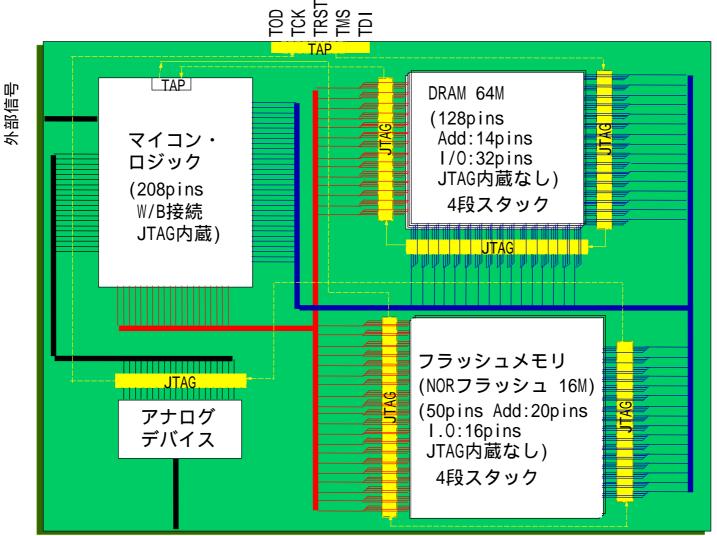

# SiP(ロジック+メモリ)テストの取り組み

<基本的考え> メモリが中心に

要求されるテスト品質によりテスト戦略を変える

\*高信頼性品:メモリをメモリテスタで直接的にテスト

\*汎用品: メモリをBIST等で間接的にテスト

\*廉価品: メモリの接続チェックのみ

<課題>

\*搭載チップ単体での品質保証の切分け チップ単体の品質保証として WLBIの高機能化/低コスト化必要

\*SiPトータルのテスト 一つのソリューション提案

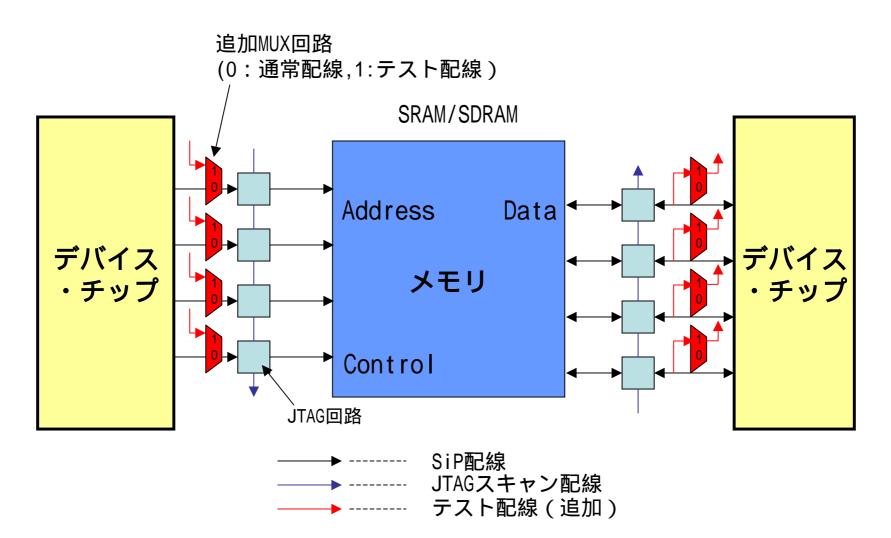

## SiPテストでの提案

#### 構造可変テスタを応用

- (1)基板内装JTAGの整備により,テスト容易性と不良解析性を向上JTAG: バウンダリスキャン

- (2) JTAGチップの機能追加により, DRAMで フラッシュメモリの書込み消去特性テストを実現

- (3) DRAMにテスト回路を構成し,SiPでの マイコン・ロジックのテスト容易化を実現

SiPのKTD(Known Tested Die)化が可能

注)構造可変テスタとは?(02年度に提案) DUT対応に必要な測定装置をユニークに実現する機能を有するテスター例はメモリで実現可能

STRJ WS: March 4, 2004, WG2

## SiPテスト方法の提案例

SiP構造 + JTAG(機能向上)構成

WE,CSなどの コントロール信号 は省略

アナログ信号

# JTAG(機能向上)

## テストMUX対応JTAG回路

## WLBIの位置付けと取り組み

<WLBIの位置付け> チップ単体の品質保証のソリューションの一つ

#### 目的

KGD(Known Good Die)ニーズへの対応

・SiP,MCM製品の最終歩留り向上

バーンイン,テストコスト,実装コストの低減

- ・多ピンデバイス(高額なバーインソケット不要)

- ・汎用メモリ(バーンイン後に冗長救済が可能)

- <WLBIへの取り組み> デバイスメーカ,装置メーカ,双方の協力が不可欠 STRJとSEAJ,各々の技術ロードマップWG協働

## <u>トータルテストソリューションに向けて</u>

## DFT-SWGからの協調のための技術的要求

- ・短TAT故障診断

- ・テスト時の電源問題への対応

- ・アナログ / 高速インタフェースのテスト

- ・テスト品質の保証

## ATE-SWGからの協調のための技術的要求

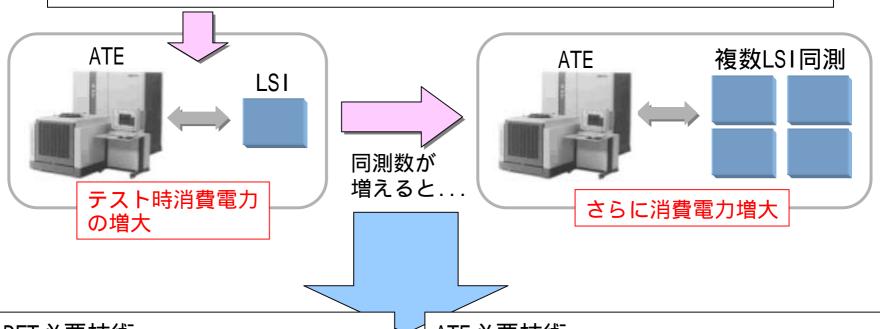

- ・同測によるテストコスト削減

- ・テストピン数削減

- ・テスト周波数低減

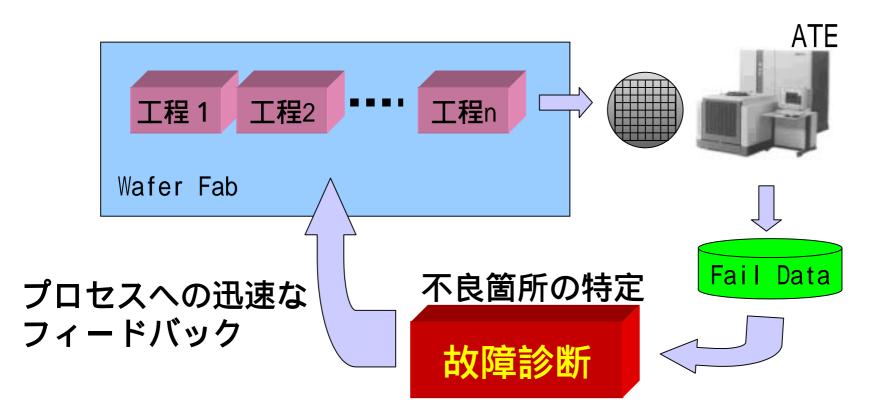

## 短TAT故障診断

・故障診断の短TAT化がTime-to-VolumeへのKey 各種DFTへの対応,充分なフェイルメモリ,インタフェースの標準化

## テスト時の電源問題への対応

- ・テスト時の電源問題の背景

- 回路規模増大による、スキャンシフトの同時スイッチ数の増加

- •BIST化による多数ブロックの同時テスト etc.

#### DFT必要技術

- 低消費電力DFT技術の開発

- IPコアテストのスケジューリング技術

#### ATE必要技術

- ・電源系の強化(供給力・追従性・プロービング)

- 複数LSI 同測への対応

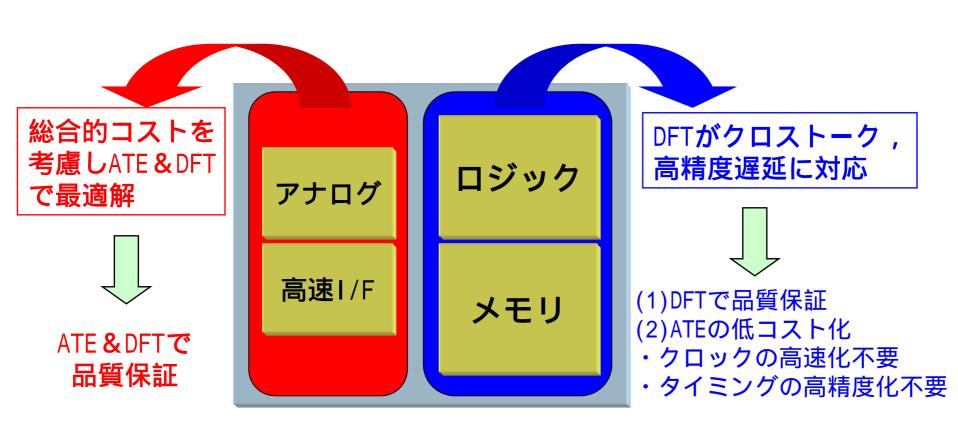

## <u>アナログ / 高速インタフェースのテスト</u>

#### DFTとATEの協調による最適解の創出が必要

STRJ WS: March 4, 2004, WG2

## テスト品質の保証

DFTとATEの役割分担による品質とコストの最適化

## トータルテストソリューションに向けて

#### DFT-SWGからの協調のための技術的要求

- ·短TAT故障診断

- ・テスト時の電源問題への対応

- ・アナログ / 高速インタフェースのテスト

- ・テスト品質の保証

## ATE-SWGからの協調のための技術的要求

- ・同測によるテストコスト削減

- ・テストピン数削減

- ・テスト周波数低減

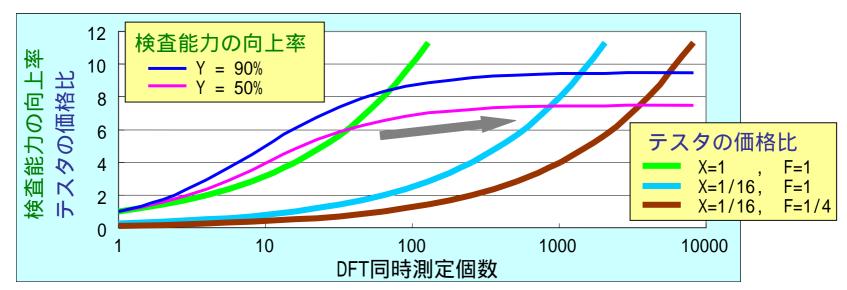

## DFTとテストコスト

■ ITRS2003にて,DFTベースの

## <u>超多数個同測ロードマップが示された</u>

ITRS2003 : Table22 Multi-site Test for Product Segments

| Year of Production              | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 | 2010 | 2012 | 2013 | 2015 | 2016 | 2018 |

|---------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Low Performance Microcontroller |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Number of sites (Wafer test)    | 16   | 32   | 32   | 64   | 64   | 128  | 128  | 128  | 128  | 128  | 256  | 256  | 512  |

| Number of sites (Package test)  | 96   | 128  | 128  | 256  | 256  | 512  | 512  | 512  | 512  | 512  | 768  | 768  | 1024 |

| Commodity Memory                |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Number of sites (Wafer test)    | 128  | 128  | 128  | 128  | 256  | 256  | 256  | 512  | 512  | 512  | 512  | 512  | 512  |

| Number of sites (Package test)  | 64   | 128  | 128  | 128  | 256  | 256  | 256  | 512  | 512  | 512  | 512  | 512  | 512  |

● 同測によるテストコスト削減に限界はないの?

DFT 同測個数 歩留り テスタ価格

の 相関関係を検証してみよう!!

STRJ WS: March 4, 2004, WG2

## 同測によるテストコスト削減

● 同測によるテストコスト削減には限界 DFTにより拡大可能

DFTとの協調でテストコスト削減を推進しよう

#### Multiテスト 対 Singleテスト

検査能力の向上率 =  $\frac{(1+Y) \cdot N}{\{1+(N-1) \cdot d\} \cdot \{2-(1-Y)^N\}}$

Y:歩留り

N:同時測定個数

d: 同測オーバヘッド(10%)

#### DFTテスト 対 Functionテスト

テスタの価格比 = X <sup>1/2</sup> • F <sup>1/2</sup>

X:テストピン数比 (DFT / Function)

F:テスト周波数比 (DFT / Function)

## <u>テストコスト削減のための要求</u>

- DFTに対するテストからの技術的要求

- o DFTのテストピン数はなるべく少なく

- DFTのテスト周波数はなるべく低速に

# テストコスト ATEコスト DFTコスト テスタ価格 設計コスト 同時測定個数 チップ面積オーバヘッド ハンドラ / プローバ価格 テスト時間 テスト治具価格 テストカバレッジ

## 2003年度活動のまとめ

- ・ITRS2003への貢献

- ・DFT-SWG:SoCテスト技術

- ・ATE-SWG:テスタ周辺技術

- ・STRJとしての活動

- ・トータルテストソリューションの検討

- DFT-SWG: SoCモデルに基づく具体的指標

- ・ATE-SWG: SoC/SiPテストの課題と対策

- ・合同会議および合宿での議論により融合を図った 品質・信頼性・コスト面での協調が必要