# ITRS 2004 Updateの概要

STRJ 副委員長 (株)東芝 石内秀美

#### 内容

- ●概要

- ●設計

- ●リソグラフィ

- プロセスインテグレーション(PIDS)

- 新探究(エマージング)デバイス(ERD)

- フロントエンドプロセス (FEP)

- ●配線

- ●実装

- ●まとめ

#### ITRSの歴史

- ・ 米国でロードマップの編集(1991-1997)

- 1991 Micro Tech 2000 Workshop Report (米)

- 1992 NTRS (National Technology Roadmap of Semiconductors, 米)

- 1994 NTRS (米)

- 1997 NTRS (米)

- ・ ロードマップ国際化の議論(1998)

- 1998 ITRS Update

- ・ 米・日・欧・韓・台の5極でロードマップを編集(1999-)

- 1999 ITRS

- 2000 ITRS Update (改訂版)

- 2001 ITRS

- 2002 ITRS Update (改訂版)

- 2003 ITRS

- 2004 ITRS Update (改訂版)

#### 2004 ITRS Updateの概要

- ・ すべての章を改訂

- ・ 改訂の規模

- 2003年版に含まれる219の表のうち128を改訂

- 新たに4つの表を追加

- 12の図を改訂

- 2003年版の表に2011年、2014年、2017年を追記

- ERM(新探究材料)の節を追加しました。

- 2004年ITRSの会議

- イタリアのストレーザ(4月19日、20日)

- 米国のサンフランシスコ(7月12日、13日)

- 東京(11月30日、12月1日)

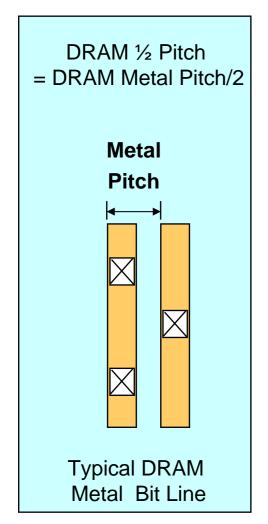

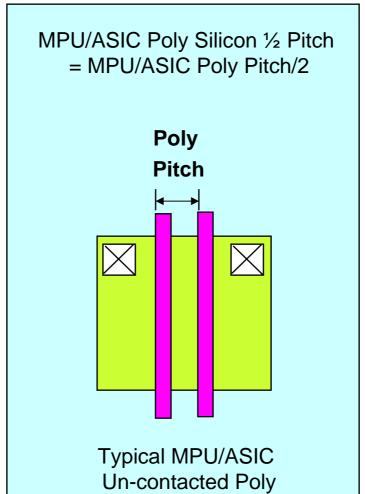

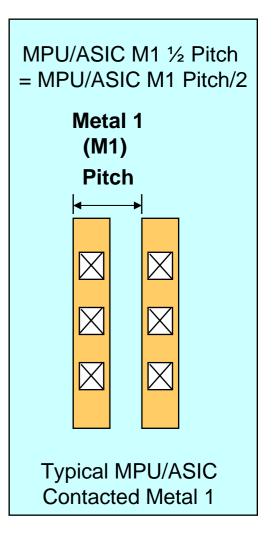

#### ハーフピッチの定義 [DRAM ハーフピッチが 2003 ITRS "node"を決定する]

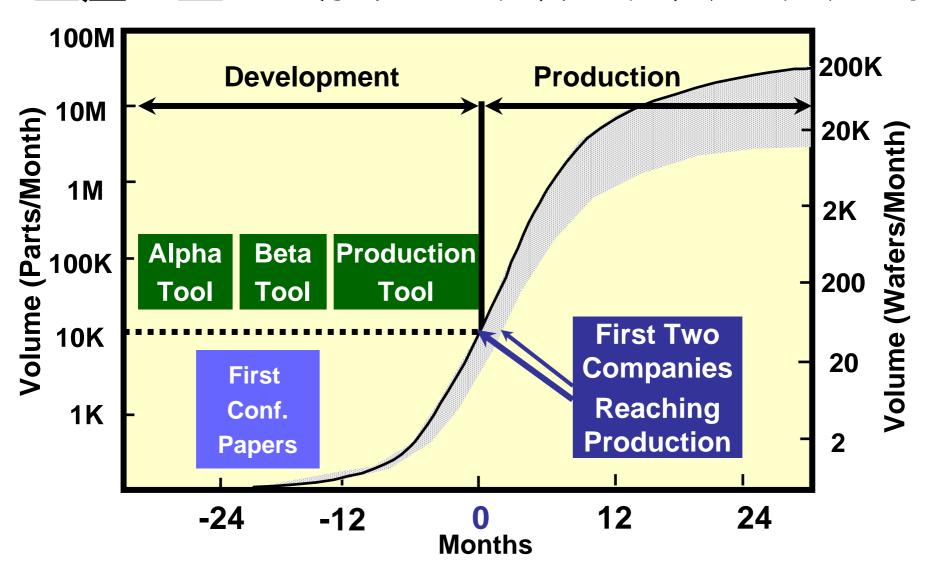

## 生産の立ち上がりのモデルとテクノロジノード

STRJ WS: March 3, 2005, ITRS 2004 Update の概要

#### テクノロジノードは3年サイクル

Source: 2003 ITRS - Exec. Summary Table C

| 生産年           | 2002<br>[Actual] | <u>2003</u> | 2004 | <u>2006</u> | 2007 | <u>2009</u> | 2010 | <u>2012</u> | 2013 | <u>2015</u> | <u>2016</u> | <u>2018</u> |

|---------------|------------------|-------------|------|-------------|------|-------------|------|-------------|------|-------------|-------------|-------------|

| テクノロジノード (nm) | hp130            |             | hp90 |             | hp65 |             | hp45 |             | hp32 | 2           | hp22        |             |

#### 3年サイクル

## 技術ノードと主要な寸法

#### (ITRS 2004 Updateでは<u>下線部の数字</u>を追加)

| 生産開始年                                 | 2003 | 2004 | 2005 | 2006 | 2007 | 2008 | 2009 |

|---------------------------------------|------|------|------|------|------|------|------|

| テクノロジーノード                             |      | hp90 |      |      | hp65 |      |      |

| DRAM ハーフピッチ (nm)                      | 100  | 90   | 80   | 70   | 65   | 57   | 50   |

| MPU/ASIC Metal 1 (M1) ハーフ<br>ピッチ (nm) | 120  | 107  | 95   | 85   | 76   | 67   | 60   |

| MPU/ASIC Poly Si ハーフピッチ (nm)          | 107  | 90   | 80   | 70   | 65   | 57   | 50   |

| M P U リソグラフィー後のゲー<br>ト長 (n m)         | 65   | 53   | 45   | 40   | 35   | 32   | 28   |

| M P U 物理的ゲート長 (nm)                    | 45   | 37   | 32   | 28   | 25   | 22   | 20   |

| 生産開始年                          | 2010 | 2011      | 2012 | 2013 | 2014      | 2015 | 2016 | 2017      | 2018 |

|--------------------------------|------|-----------|------|------|-----------|------|------|-----------|------|

| テクノロジーノード                      | hp45 |           |      | hp32 |           |      | hp22 |           |      |

| DRAM ハーフピッチ (nm)               | 45   | <u>40</u> | 35   | 32   | <u>28</u> | 25   | 22   | <u>20</u> | 18   |

| MPU/ASIC (M1ハーフピッチ<br>(nm)     | 54   | 48        | 42   | 38   | <u>34</u> | 30   | 27   | <u>24</u> | 21   |

| MPU/ASICPoly Si ハーフピッチ<br>(nm) | 45   | 40        | 35   | 32   | 28        | 25   | 22   | <u>20</u> | 18   |

| MPU リソグラフィー後のゲー<br>ト長 (nm)     | 25   | 22        | 20   | 18   | <u>16</u> | 14   | 13   | <u>11</u> | 10   |

| M P U 物理的ゲート長 (n m)            | 18   | <u>16</u> | 14   | 13   | <u>11</u> | 10   | 9    | <u>8</u>  | 7    |

### 設計 - DFM(Design for Manufacturing)

#### <del>----→</del> ばらつき考慮設計 DFM challenges

<u>回路/chip</u> (スピード、電力)

<u>^</u> 2. <u>デバイス</u> (∨<sub>t</sub>, l<sub>off</sub>)

3. <u>物理レベル (La, NA、)</u>

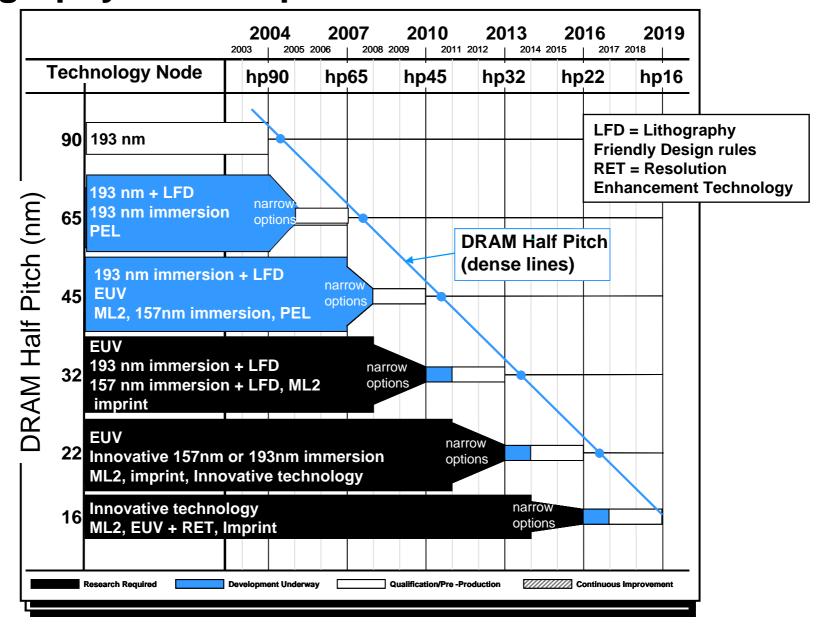

#### リソグラフィ

- リソグラフィーツール

- 193nm波長のドライまたは液浸リソグラフィー技術が65nm,45nmで使われ、32nm、22nmでも使用される可能性

- EUVリソフラフィーは45nm、32nm, 22nmの有力候補技術

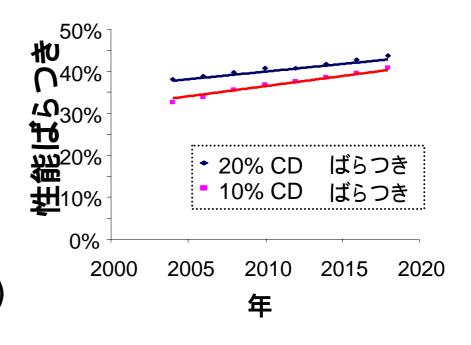

- CD制御 (total CD control)

- 3σ <4nm にCD を制御する解決策がないことが判明。

- レジストゲート長は2005年に見直し。

- 液浸リソの実用化には多くの課題

- 色づけとフットノート他を改訂

- リソの全般的要求の表77a and 77bの定義

- マスクの表

- レジストの表

- 更なる議論が必要(2005改訂に反映)

- LWR/LER の定義と値をPIDS, FEP and Metrologyからもらう

- Advanced Process Control への要求事項

# Lithography Roadmap with Potential Solutions

#### フロントエンドプロセス

- ゲートのCD(寸法)制御について

- ITRSと現実との乖離を注記

- ITRSのばらつき限界を達成できていない。

- 2005年版の表の改訂を提案

- SOIウェーハの認定/少量量産時期を2006年から2004年へ

- 450mmウェーハの導入時期を強調

- 2011年、ないし2015年。450mmウェーハ導入時期についての合意は未。

- ウェーハメーカーの開発は2011年の導入には間に合わないと注記

- 450mmウェーハ導入時期についての合意はまだとれていない。

- 2005年にも、標準化の議論を始める必要あり

- チャンネル部のキャリア移動度増加技術は実用化

- 先端製品では、Siに歪を加える技術の利用が始まる。

- ゲートスタックのリーク電流の仕様を改訂

- 100°Cでの電流値を記入

# PIDS (Process Integration Devices, and Structures)

- 2004年の改訂: 2003年版の小改訂と誤り修正

- 2003年版の表には記載されていなかった2011年、2014年、 2017年の数値を追加

- 上記の各数値は前後の年の中間に近い値になっている。

- DRAMの微細化トレンドには変化なし。

- 2004年にハーフピッチ90nmが実現

- 2005年版にむけての準備を開始

- 多くの課題が想定される。

## Emerging Research Devices (新探究デバイス) 章の構成の変更 (2004/2005)

Emerging Research Devices (新探究デバイス)

Emerging Materials (新探究材料) Emerging

Logic and Memory

Devices

新探究ロジックとメモリ)

Emerging Architectures (新探究アーキ テクチャー)

2004年改訂 でERD に 追加 Non-classical CMOS (ノンクラシカル CMOS)

2005年版では PIDS/FEPへ

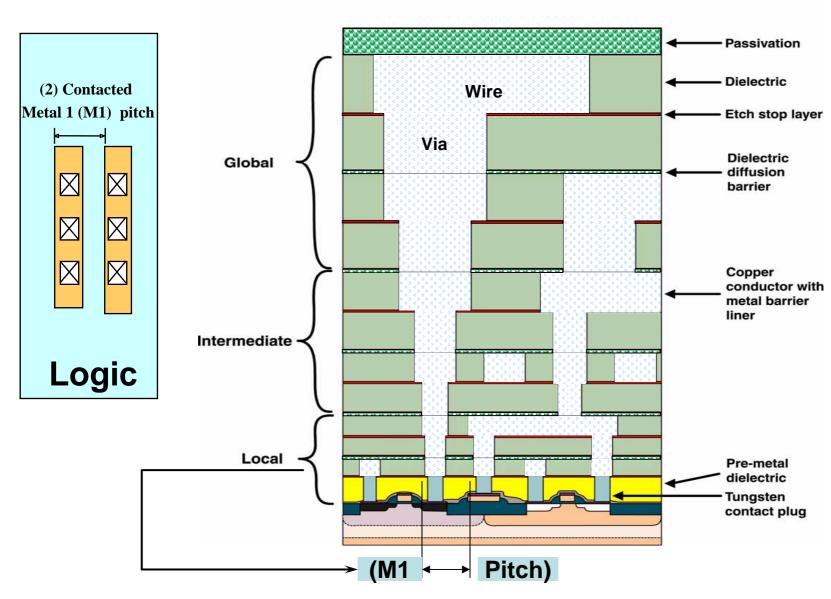

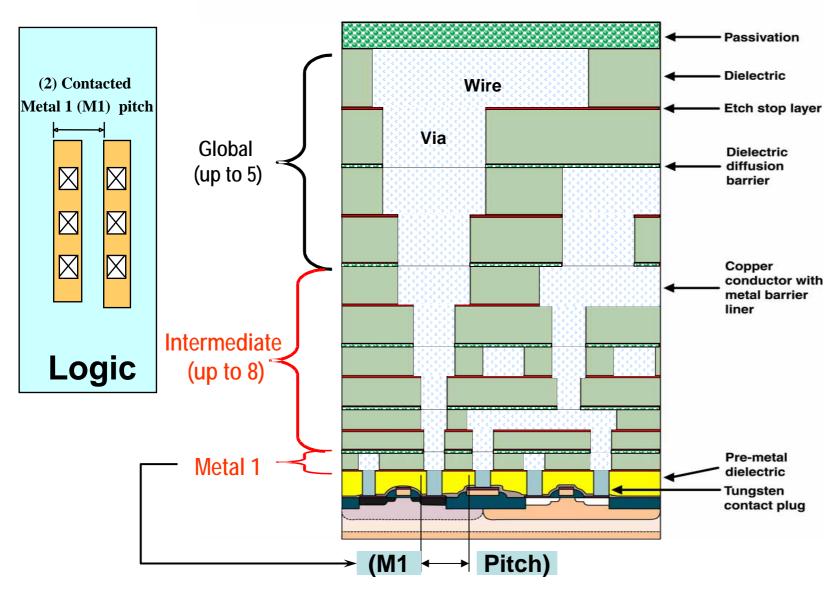

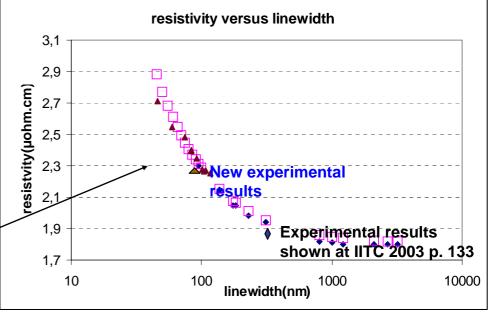

#### 配線技術

#### ロジックデバイス

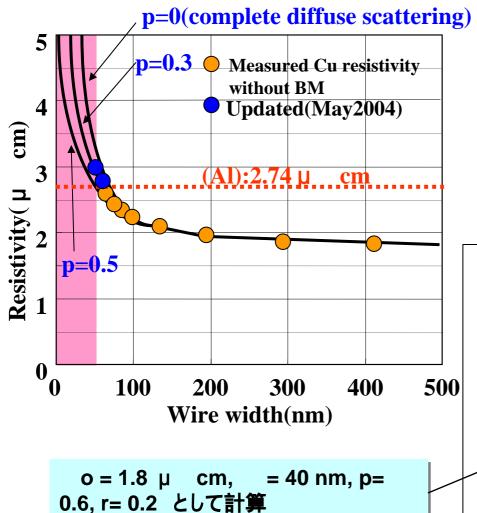

- 銅の配線抵抗は散乱効果のため増大

- 第一メタル、インターミディエット、グローバル配線の抵抗を計算 する方法を追加した。

- RC遅延の数値を改訂した。

- 第一メタルのデザインルールについて

- コンタクトなしのハーフピッチ、コンタクト付きのハーフピッチについての混乱、MPUにおけるテクノロジーノードの誤用を解消

- 最近の文献によると、第一メタルの微細化が加速(2005年版の 検討項目)

- 高性能(high performance)チップのための別の表が必要 (2005年版の検討項目)

- Low k 技術への要求と kの値(材料の値、実効値とも)は

2003年版と同じ。

- 比誘電率(k値)の前倒しをしなかったのは、10年来初めて

- 技術的な困難度を示す色を小修正

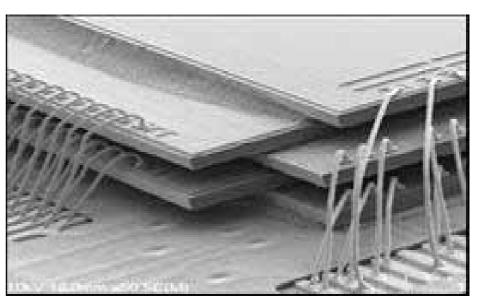

#### **Typical Chip Cross Section**

Work in Progress - Do not publish

#### **Typical Chip Cross Section**

#### 電子散乱効果による銅(Cu)配線の抵抗増大

| wire width(cm)   | ire width(cm) o(u cm) |       | (om)     |      | Measured |       |       |          |

|------------------|-----------------------|-------|----------|------|----------|-------|-------|----------|

| wire width(Cili) | o( µ                  | cm)   | (cm)     | P=0  | P=0.2    | P=0.3 | P=0.5 | data     |

| 5.00E-05         | 1.9                   | 0E+00 | 3.40E-06 | 2.05 | 2.03     | 2.02  | 2.00  | 2.00E+00 |

| 2.00E-05         | 1.9                   | 0E+00 | 3.40E-06 | 2.26 | 2.21     | 2.19  | 2.14  | 2.10E+00 |

| 1.40E-05         | 1.9                   | 0E+00 | 3.40E-06 | 2.42 | 2.35     | 2.32  | 2.25  | 2.20E+00 |

| 1.17E-05         | 1.9                   | 0E+00 | 3.40E-06 | 2.52 | 2.44     | 2.40  | 2.31  | 2.30E+00 |

| 1.00E-05         | 1.9                   | 0E+00 | 3.40E-06 | 2.63 | 2.53     | 2.48  | 2.38  | 2.40E+00 |

| 8.50E-06         | 1.9                   | 0E+00 | 3.40E-06 | 2.76 | 2.64     | 2.58  | 2.47  | 2.50E+00 |

| 7.50E-06         | 1.9                   | 0E+00 | 3.40E-06 | 2.87 | 2.74     | 2.68  | 2.55  | 2.70E+00 |

| 6.50E-06         | 1.9                   | 0E+00 | 3.40E-06 | 3.02 | 2.87     | 2.79  | 2.65  | 2.80E+00 |

| 5.50E-06         | 1.9                   | 0E+00 | 3.40E-06 | 3.22 | 3.05     | 2.96  | 2.78  | 3.00E+00 |

| 5.00E-06         | 1.9                   | 0E+00 | 3.40E-06 | 3.35 | 3.16     | 3.06  | 2.87  | Non      |

| 3.90E-06         | 1.9                   | 0E+00 | 3.40E-06 | 3.76 | 3.52     | 3.39  | 3.14  | Non      |

| 3.60E-06         | 1.9                   | 0E+00 | 3.40E-06 | 3.92 | 3.65     | 3.52  | 3.25  | Non      |

| 2.80E-06         | 1.9                   | 0E+00 | 3.40E-06 | 4.50 | 4.15     | 3.98  | 3.63  | Non      |

| 2.40E-06         | 1.9                   | 0E+00 | 3.40E-06 | 4.93 | 4.52     | 4.32  | 3.92  | Non      |

| 2.00E-06         | 1.9                   | 0E+00 | 3.40E-06 | 5.53 | 5.05     | 4.81  | 4.32  | Non      |

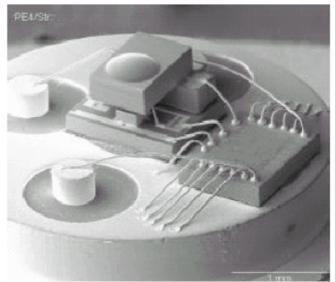

#### アセンブリとパッケージ

#### コンシューマ / Mixed Signal市場への対応

- ・システム・イン・パッケージ (SiP)

- ・3次元パッケージ

- •ウェハレベルパッケージ

- •薄チップ化

#### 新規デバイスへの対応

- •MEMS

- •光エレクトロニクス

- •バイオチップ

# まとめ --- 2004 ITRS Updateのポイント

- 193nm波長のドライまたは液浸リソグラフィー技術が 65nm,45nmで使われ、32nm、22nmでも使用される可能性

- EUVリソフラフィーは45nm、32nm, 22nmの有力候補技術

- CD(重要寸法: Critical Dimension)制御とLER(Line Edge Roughness)の問題がクローズ・アップ

- 450mmウェーハの導入は2011-2015年だが、コンセンサスは未。2005年にも、標準化の議論を始める必要あり。

- ・ 先端製品にはSiに歪を加える技術の利用が始まる。

- 配線技術についてはLow k 技術への要求と k の値(材料の値、実効値とも)は2003年版と同じ。kの値の変更をしなかったのは、10年来初めて。

- ICの機能を十分に引き出すため、パッケージ技術に注目。

# 参考文献: 関連webサイトのURL

- ITRSの公式ホームページ

- <a href="http://public.itrs.net/">http://public.itrs.net/</a>

- ITRS 2004 Updateはじめ、ITRSの最新情報

- JEITAのロードマップのホームページ

- http://strj-jeita.elisasp.net/strj/index.htm

- ITRS 2003の日本語訳

- その他 STRJ(半導体技術ロードマップ専門委員会) の活動情報など