# WG12 ERD

## 新探求デバイス・材料

### —2020年に向けて情報処理デバイスを考える—

平本俊郎

東京大学生産技術研究所

- 1 . ERDの目的とスコープ

- 2 . 新探求メモリとロジック

- 3 . メモリとロジックの評価

- 4 . ERDの指導原理

# 2005年版の新しい動き

- 1 . ERDが単独の章として独立

- 2 . ノンクラシカルCMOSの節がPIDSへ

Beyond CMOSの考え方方がより鮮明に

- 3 . Emerging Research Materials

新材料がデバイス機能に与える影響が大

- 4 . Variable States の議論

電荷以外を用いるデバイスを積極的に議論

## ERDの目的

- 1 . 極限CMOSを超える情報処理へのアプローチ

- 2 . 2020年までに実用化される新情報処理デバイスの同定

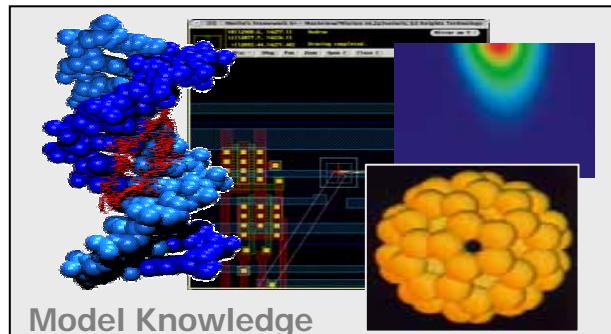

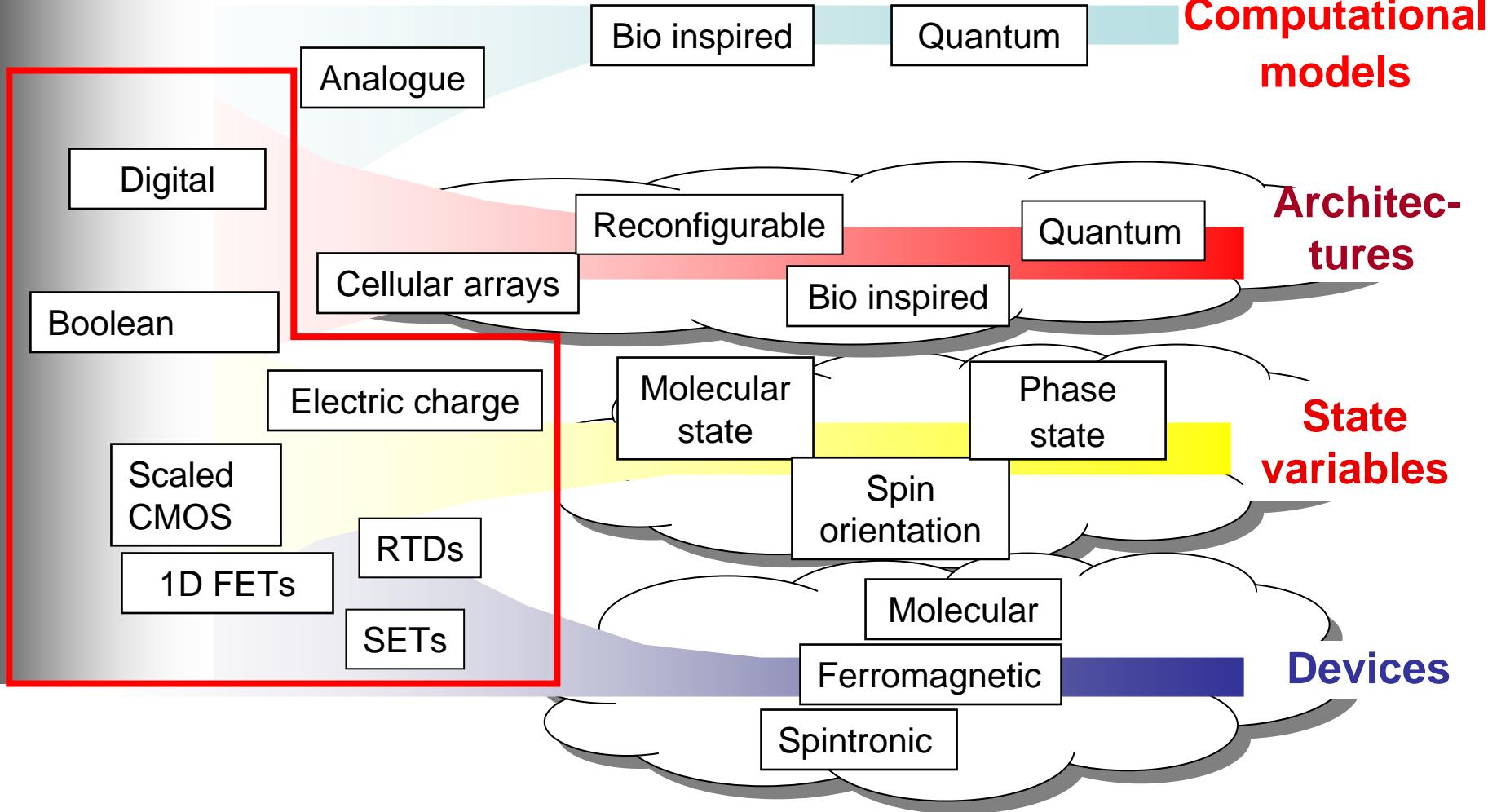

# 2005年版ERDのスコープ

新材料

新情報処理のコンセプト

# 求められる機能

- **要求される特性:**

- スケーラビリティ

- 性能

- エネルギー効率

- 利得

- 信頼性

- 室温動作

- **望まれる特性:**

- CMOSプロセスとの互換性

- CMOSアーキテクチャとの互換性

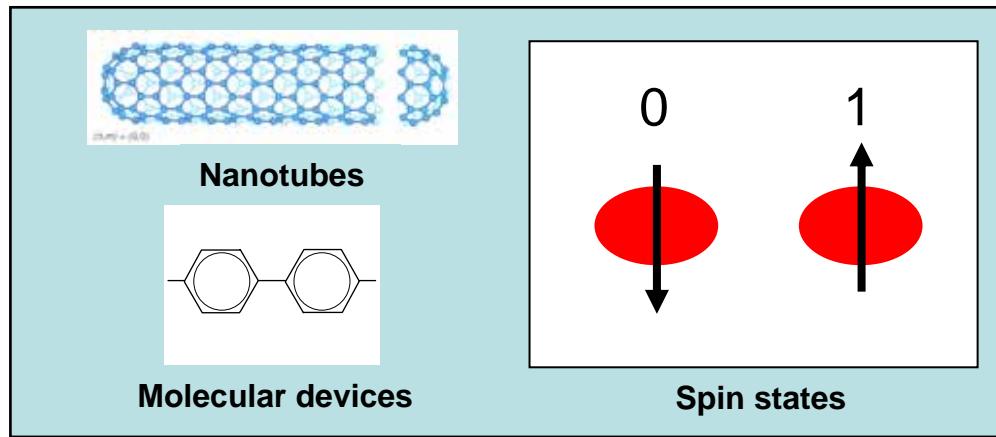

## 他の状態変数

(電荷だけでなく)

- スピン状態

- 分子状態

- 強相関電子状態

- 位相状態

- 量子状態

- 磁気单一量子磁束

- 機械的変形

- ダイポール

# ナノ情報処理の分類

Hierarchy

# 新探究メモリ

|         | ナノフローティングゲートメモリ | トンネル障壁メモリ | 強誘電体FETメモリ      | 抵抗変化メモリ    | ポリマーメモリ    | 分子メモリ      |

|---------|-----------------|-----------|-----------------|------------|------------|------------|

| 記憶メカニズム | 浮遊ゲートの電荷        | 浮遊ゲートの電荷  | 強誘電体ゲート絶縁膜の残留分極 | 複合機構       | 不明         | 不明         |

| セル構成    | 1T              | 1T        | 1T              | 1T1R or 1R | 1T1R or 1R | 1T1R or 1R |

新たに加わったもの： 強誘電体FETメモリ，ポリマーメモリ

候補から外れたもの： 単電子メモリ，浮遊ボディDRAM，PRAM

# 新探究ロジックデバイス

| デバイス |         |                                            |            |                |     |                                |                               |          |

|------|---------|--------------------------------------------|------------|----------------|-----|--------------------------------|-------------------------------|----------|

| 種類   | Si CMOS | CNT FET<br>NW FET<br>NW ヘテロ構造<br>クロスバーナノ構造 | 共鳴トンネルデバイス | RTD-FET<br>RTT | SET | クロスバーラッチ<br>分子トランジスタ<br>分子 QCA | 強磁性ロジック<br>ドメインウォール<br>M: QCA | スピントラジスタ |

新たに加わったもの： 強磁性ロジック

候補から外れたもの： RSFQ , E-QCA

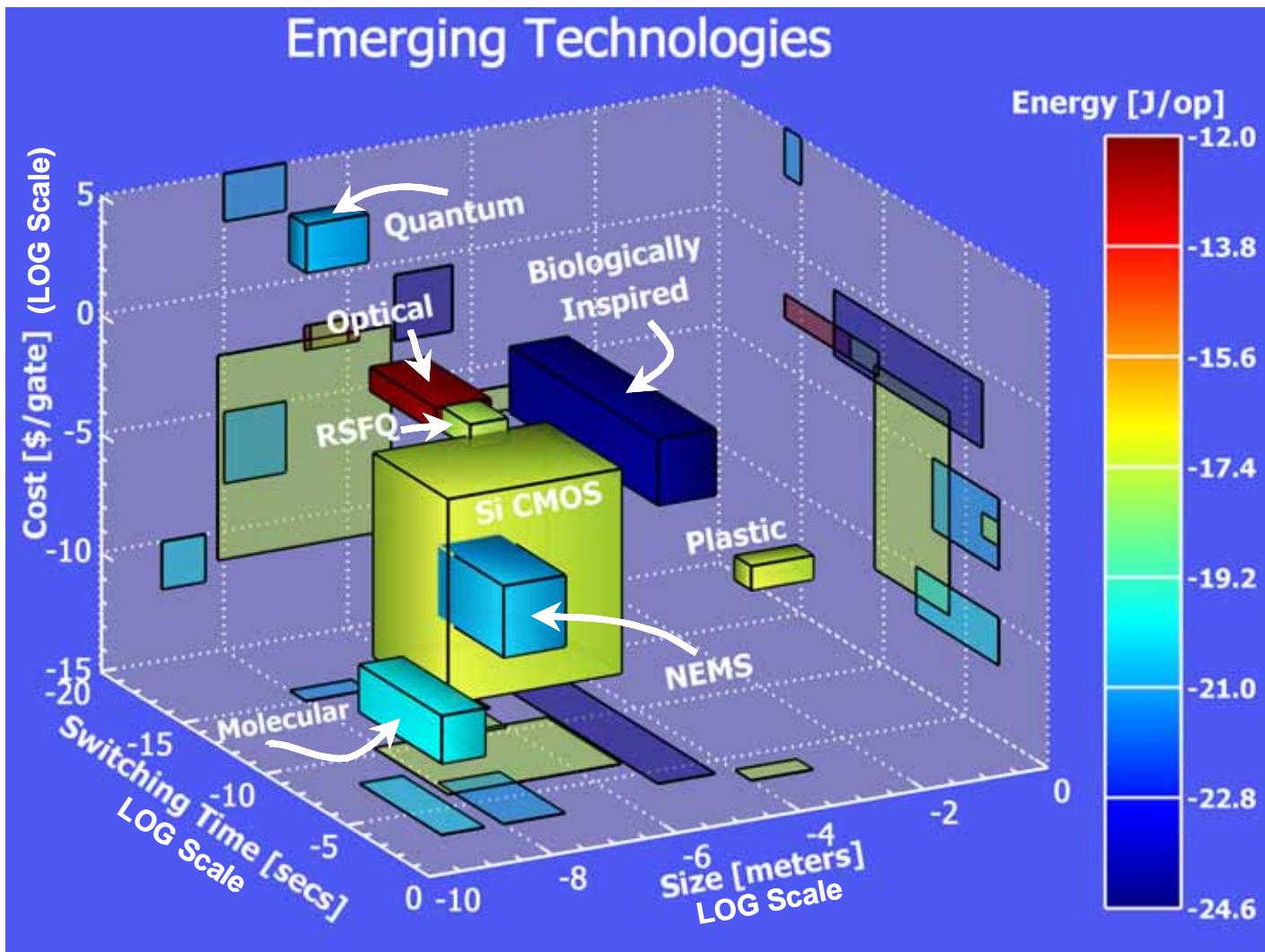

# 技術比較

# 評価 - メモリ

| メモリデバイスの候補 | スケーラビリティ | 性能  | エネルギー効率 | OFF/ON比 | 信頼性 | 動作温度 | CMOS技術との互換性 | CMOSアーキテクチャとの互換性 |

|------------|----------|-----|---------|---------|-----|------|-------------|------------------|

| ナノ浮遊ゲートメモリ | 2.5      | 2.5 | 2.5     | 2.5     | 2.2 | 2.7  | 2.7         | 3.0              |

| トンネル障壁メモリ  | 2.2      | 2.3 | 2.3     | 2.3     | 2.4 | 2.8  | 2.8         | 3.0              |

| 強誘電体FETメモリ | 1.9      | 2.3 | 2.5     | 2.2     | 2.0 | 3.0  | 2.6         | 3.0              |

| 抵抗変化メモリ    | 2.5      | 2.5 | 2.0     | 2.2     | 1.9 | 2.8  | 2.6         | 2.8              |

| ポリマーメモリ    | 2.1      | 1.5 | 2.3     | 2.2     | 1.6 | 2.9  | 2.3         | 2.5              |

| 分子メモリ      | 2.3      | 1.5 | 2.4     | 1.6     | 1.4 | 2.6  | 1.9         | 2.3              |

# 評価 - ロジック

| ロジックバイスの候補       | スケーラビリティ | 性能  | エネルギー効率 | 利得  | 信頼性 | 室温動作 | CMOS 技術との互換性 | CMOS アーキテクチャとの互換性 |

|------------------|----------|-----|---------|-----|-----|------|--------------|-------------------|

| 1D 構造 (CNT & NW) | 2.4      | 2.5 | 2.3     | 2.3 | 2.1 | 2.8  | 2.3          | 2.8               |

| 共鳴トンネルデバイス       | 1.5      | 2.2 | 2.1     | 1.7 | 1.7 | 2.5  | 2.0          | 2.0               |

| SET              | 1.9      | 1.5 | 2.6     | 1.4 | 1.2 | 1.9  | 2.1          | 2.1               |

| 分子デバイス           | 1.6      | 1.8 | 2.2     | 1.5 | 1.6 | 2.3  | 1.7          | 1.8               |

| 強磁性デバイス          | 1.4      | 1.3 | 1.9     | 1.5 | 2.0 | 2.5  | 1.7          | 1.7               |

| スピントランジスタ        | 2.2      | 1.3 | 2.4     | 1.2 | 1.2 | 2.4  | 1.5          | 1.7               |

# ERDの指導原理

1. 電荷だけではなく電荷以外の状態の利用

スピン, 位相, 量子状態, メカニカルな位置, 分子状態など

2. 非熱平衡状態システム

3. 新しい情報・エネルギー転送機構

4. サブリソグラフィック作製プロセス

「CMOSが最も効率の良いスイッチである」

- (1) Extend CMOS?

- (2) Added to CMOS?

- (3) Replacing CMOS?

# まとめ

-

- 1. いよいよ Beyond CMOSを考えるべきときか？

- 2. 従来の電荷だけでなく他の状態を積極的に利用

- 3. いわゆる Universal Memory の候補はない

- 4. CMOSに代わるロジックはまだ考えにくい

- 5. 2020年むけて新情報処理デバイスに関する真剣な議論を開始すべき