# MOSFETの特性ばらつき予測と コンパクトモデルの役割

STRJ-Workshop

2007年3月8日

広島大学先端物質科学研究所:三浦道子

# 目次

## I. ばらつき予測

- I-1. ばらつき分類

- I-2. ばらつき見積もり

- I-3. ばらつき予測

## II. コンパクトモデルの役割

- II-1. コンパクトモデル

- II-2. コンパクトモデルの精度

- II-3. コンパクトモデルの可能性

# I-1. ばらつきの分類

- **Inter-Chip (Die)ばらつき: Systematic**

- **Intra-Chip (Die)ばらつき: Random** → **Mismatch**

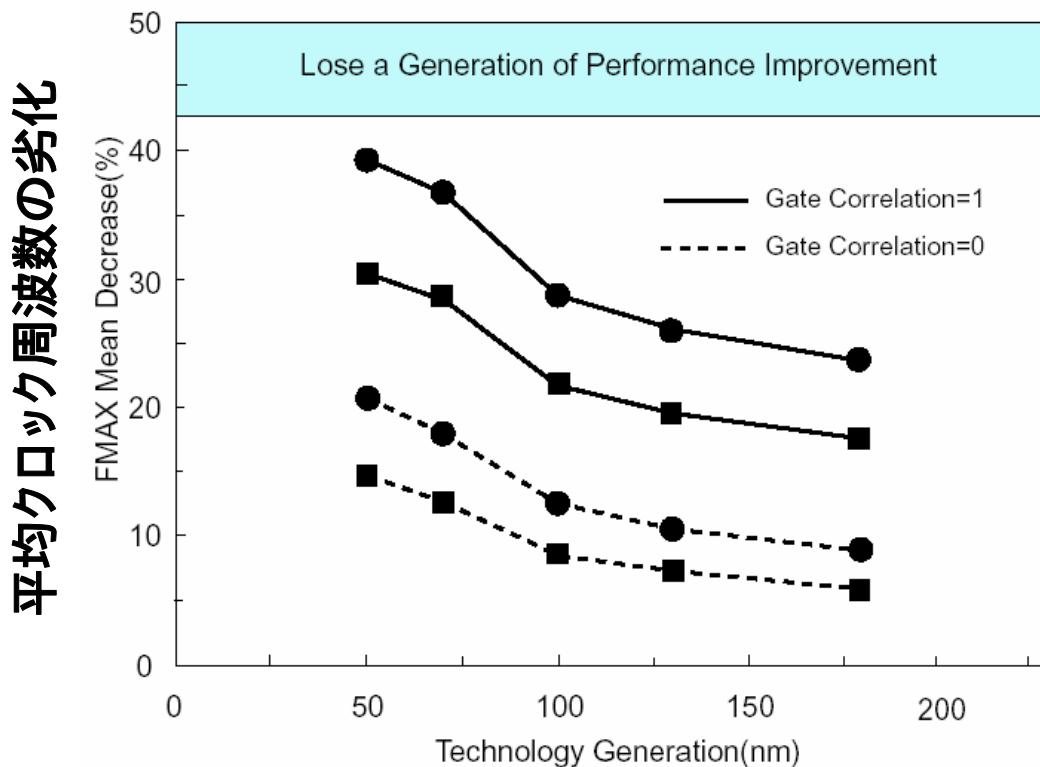

K. A. Bowman et al., IEEE J. SSC, 37, 183, 2002.

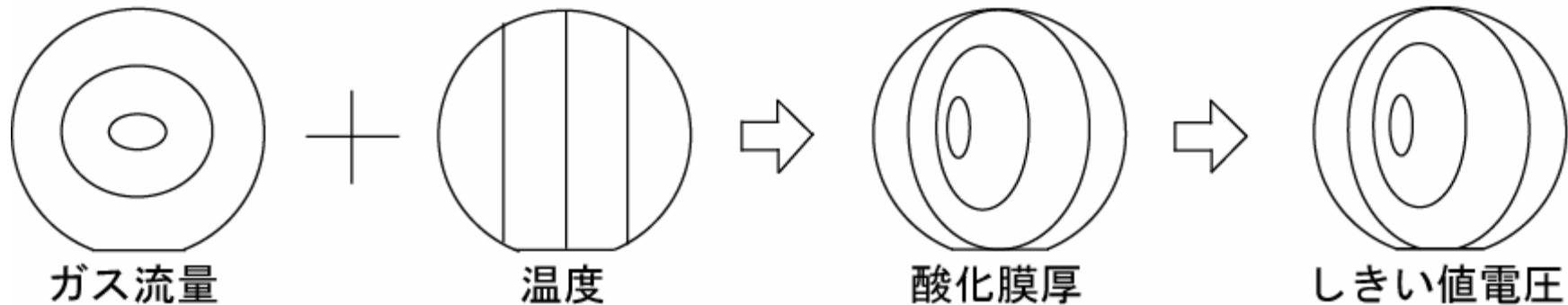

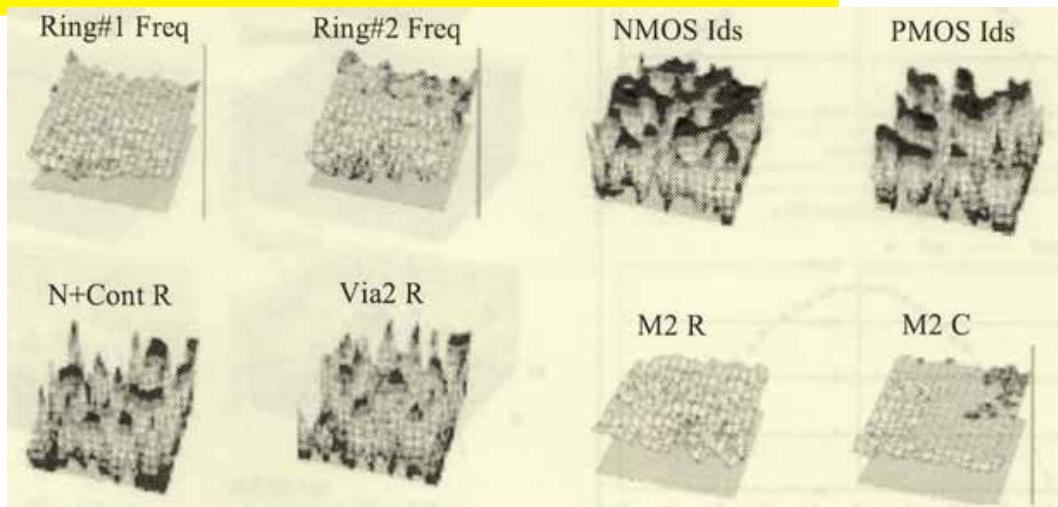

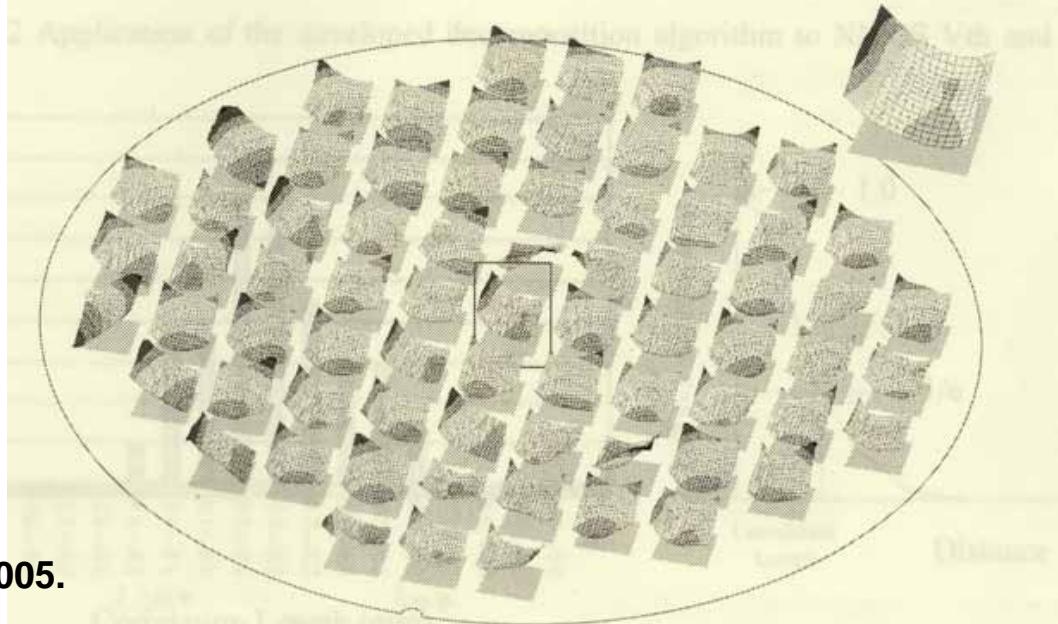

# Inter-Chipばらつき

装置

Wafer上のはらつき: In-Line測定からの抽出

# デバイスレベルのばらつき

# 回路レベルのばらつき

|   | $\Delta L$ | $\Delta N_{sub,n}$ | $\Delta N_{sub,p}$ | $\Delta T_{ox}$ |

|---|------------|--------------------|--------------------|-----------------|

| 1 | $2\sigma$  | $2\sigma$          | $-2\sigma$         | $2\sigma$       |

| 2 | $2\sigma$  | $2\sigma$          | $-2\sigma$         | $-2\sigma$      |

| 3 | $2\sigma$  | $-2\sigma$         | $2\sigma$          | $2\sigma$       |

| 4 | $2\sigma$  | $-2\sigma$         | $2\sigma$          | $-2\sigma$      |

| 5 | $-2\sigma$ | $2\sigma$          | $-2\sigma$         | $2\sigma$       |

| 6 | $-2\sigma$ | $2\sigma$          | $-2\sigma$         | $-2\sigma$      |

| 7 | $-2\sigma$ | $-2\sigma$         | $2\sigma$          | $2\sigma$       |

| 8 | $-2\sigma$ | $-2\sigma$         | $2\sigma$          | $-2\sigma$      |

O. Prigge et al., IEICE, E82-C, p. 9107, 1999.

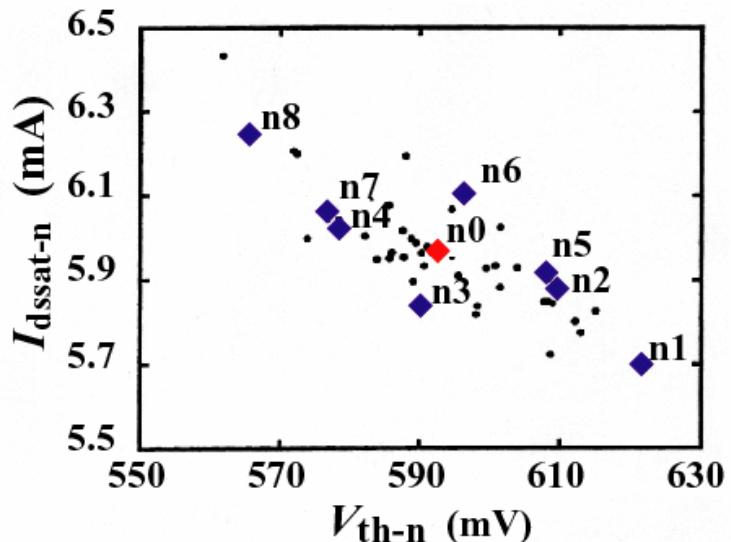

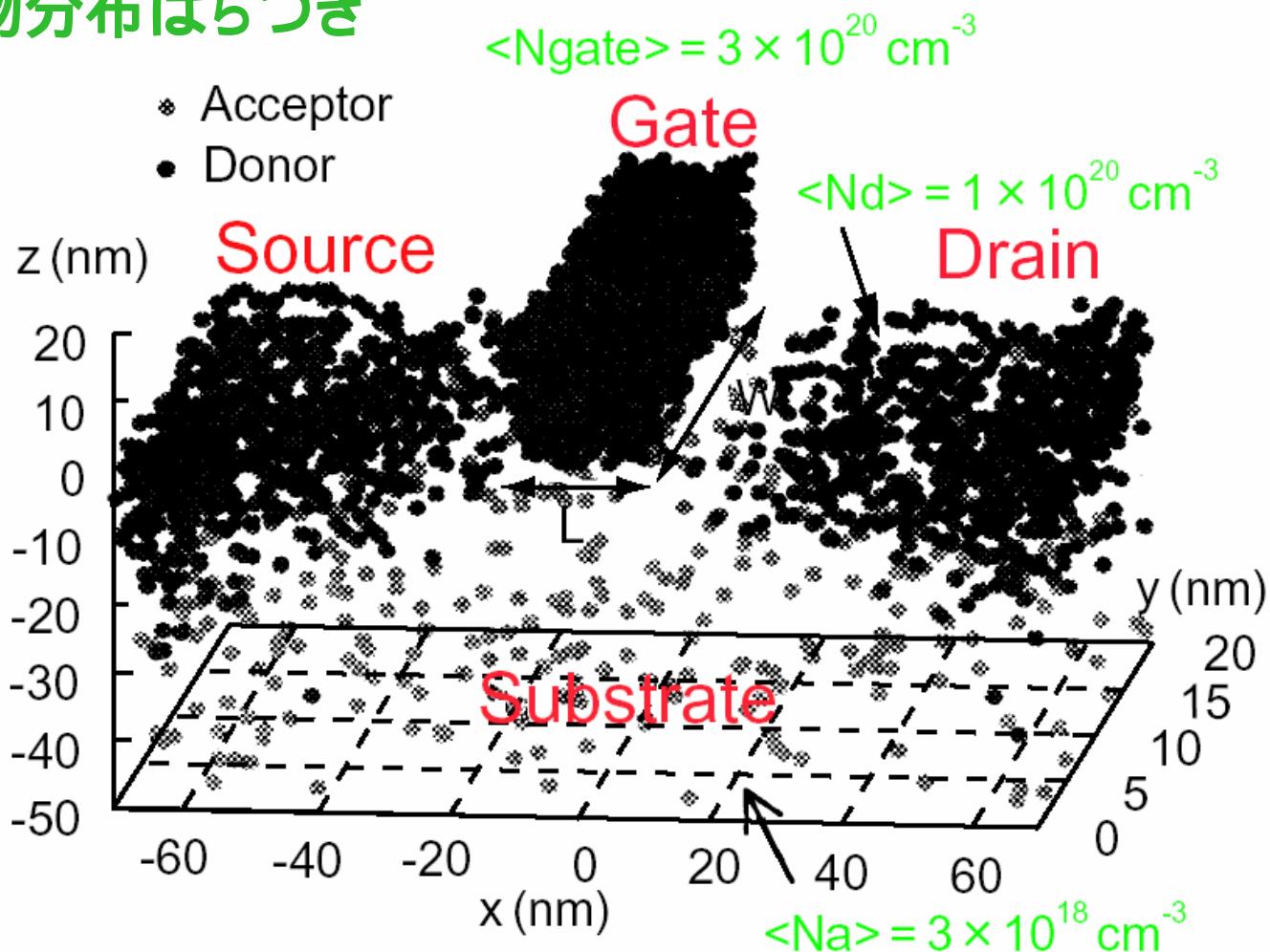

# Intra-Chipばらつき

## 不純物分布ばらつき

S. Toriyama et al., Proc. SISPAD, 23, 2005.

## 不純物ばらつきによって生じた電流ばらつき

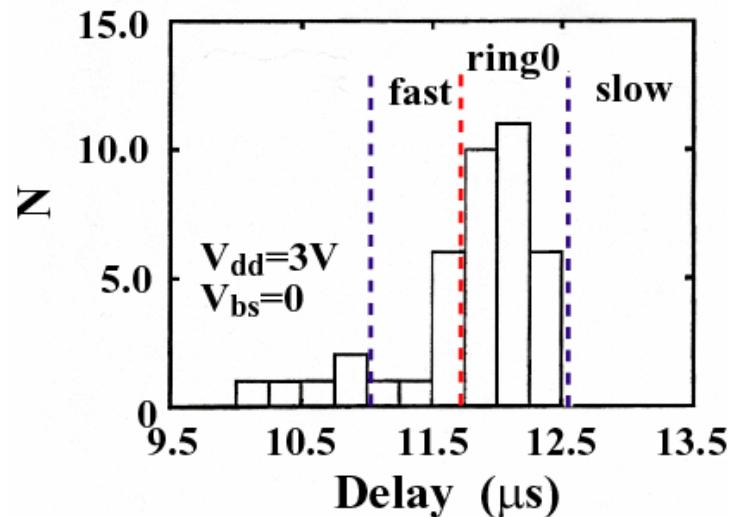

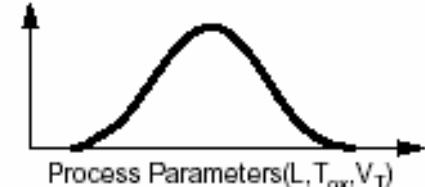

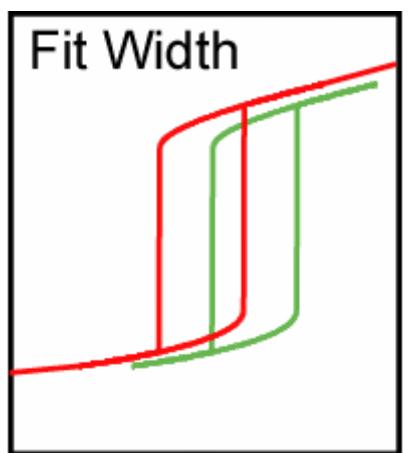

## Inter-Dielばらつき

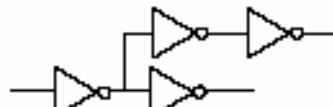

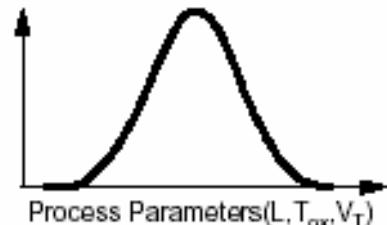

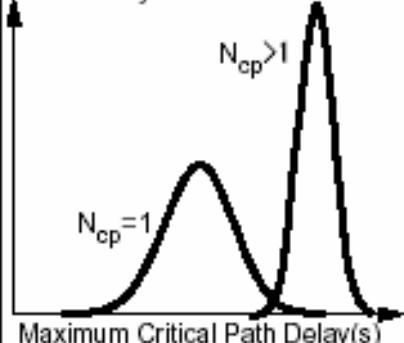

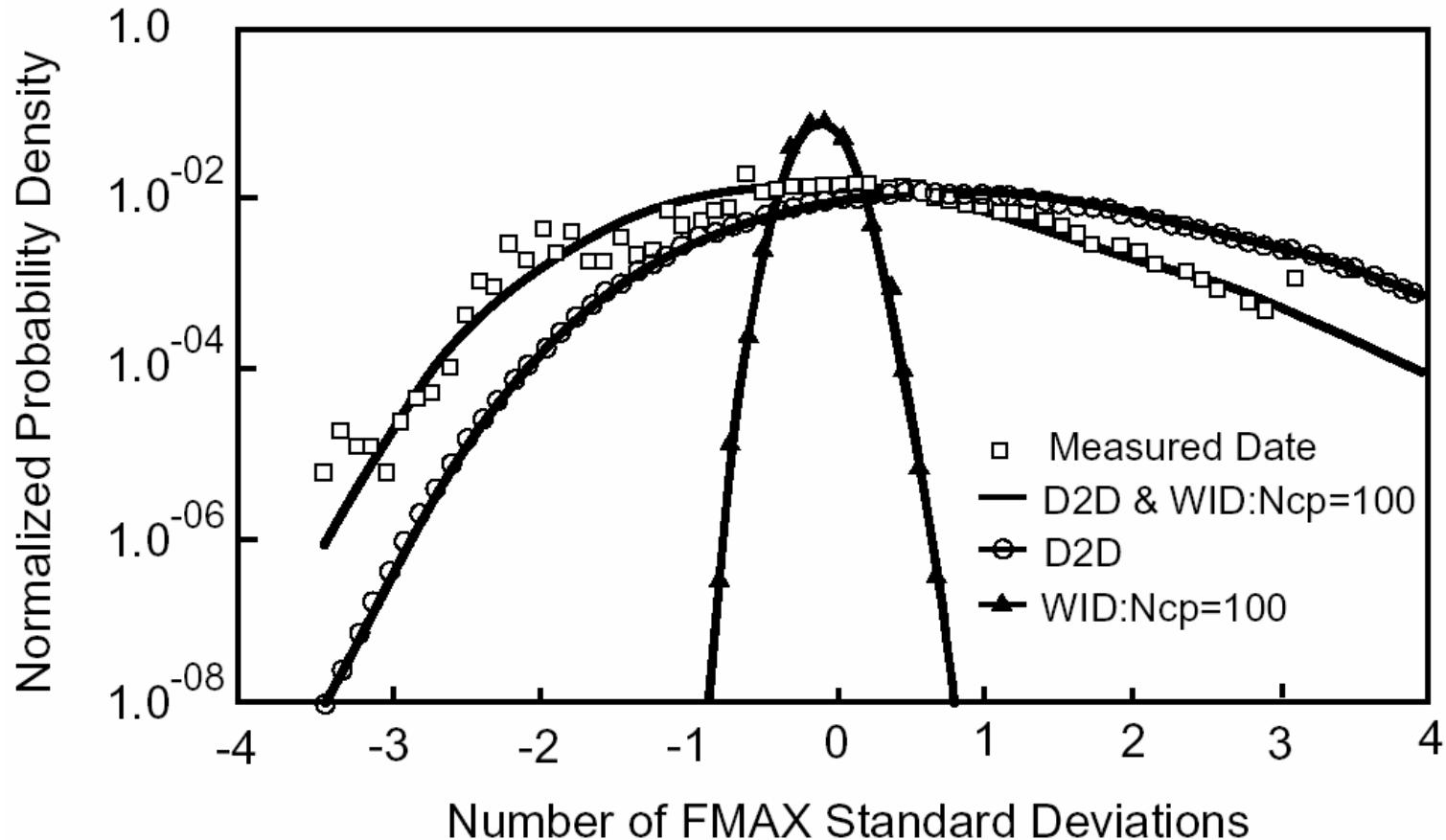

Die-to-Die(D2D)Statistical Process Models

## Process Models

Netlist of Critical Paths

## Intra-Dielばらつき

Within-Die(WID)Statistical Process Models

## Statistical Circuit Simulator

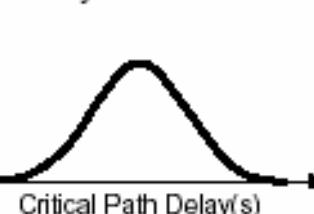

D2D Critical Path Delay Distribution

WID Maximum Critical Path Delay Distribution

## Statistical Circuit Simulator

WID Critical Path Delay Distribution for N\_cp = 1

D2D&amp;WID Maximum Critical Path Delay Distribution

FMAX Distribution

FMAX(Hz)

K. A. Bowman et al., IEEE J. SSC, 37, 183, 2002.

# 不十分な特性(critical path)が回路全体の性能を損なう

(Ncp: Number of Critical Path)

性能ばらつきはInter-DieばらつきとIntra-Dieばらつきから決まる

Stochasticな考察

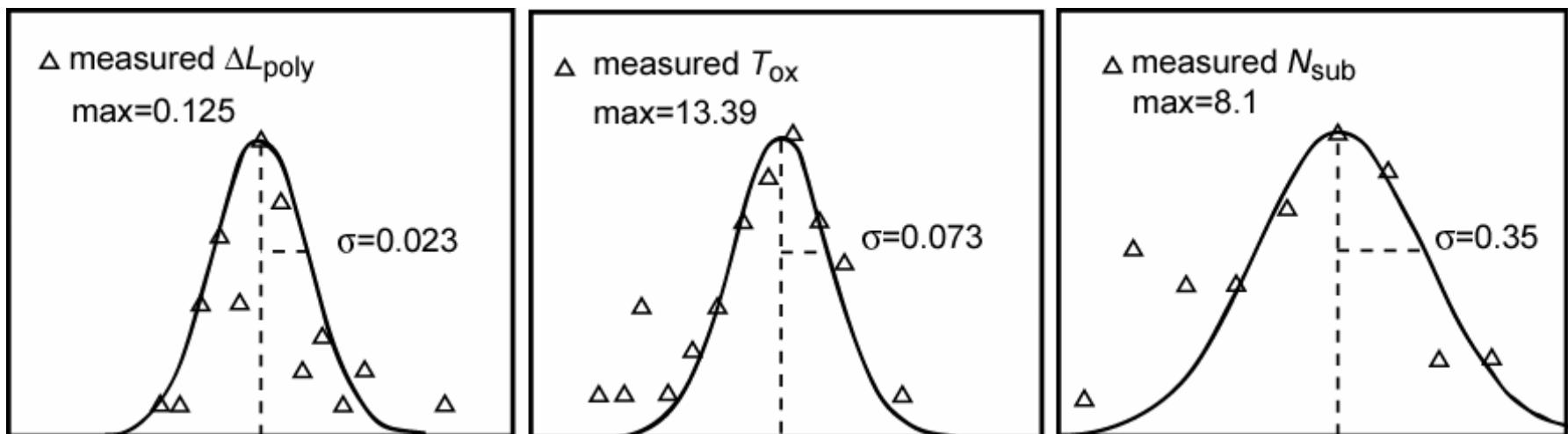

## I-2. ばらつきの見積もり

MOSFETばらつきが支配的

H. Masuda et al., CICC, p. 593, 2005.

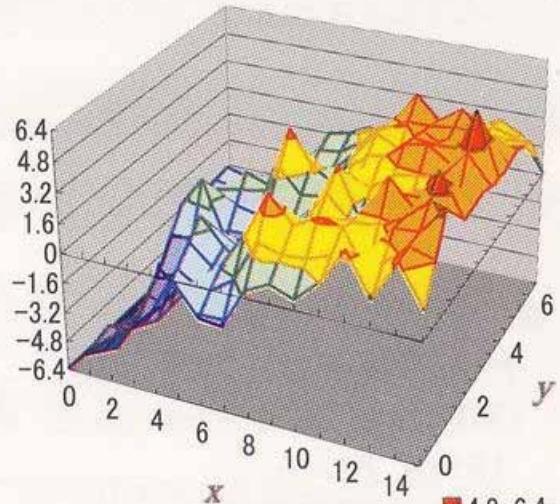

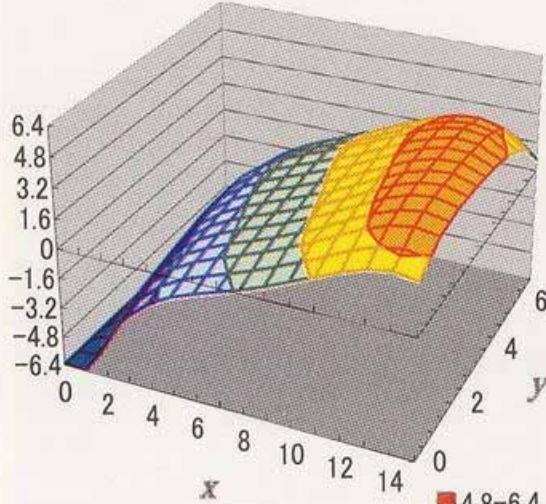

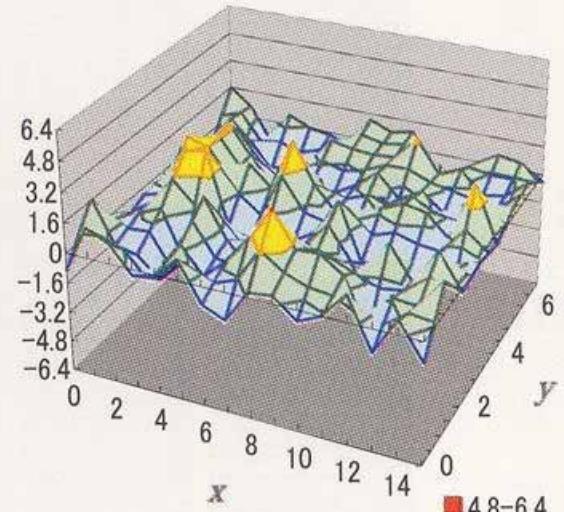

# SystematicばらつきとRandomばらつきの分離

CMA 16×8 での周期ばらつき[%]

$\sigma(\%) = 3.60$

$\min(\%) = -10.89$

$\max(\%) = 6.58$

■ 4.8-6.4

■ 3.2-4.8

■ 1.6-3.2

■ 0-1.6

■ -1.6-0

■ -3.2--1.6

■ -4.8--3.2

■ -6.4--4.8

システム成分(4次多項式近似)[%]

$\sigma(\%) = 3.42$

$\min(\%) = -9.95$

$\max(\%) = 4.09$

■ 4.8-6.4

■ 3.2-4.8

■ 1.6-3.2

■ 0-1.6

■ -1.6-0

■ -3.2--1.6

■ -4.8--3.2

■ -6.4--4.8

ランダム成分(近似残差)[%]

$\sigma(\%) = 1.12$

$\min(\%) = -2.23$

$\max(\%) = 3.26$

■ 4.8-6.4

■ 3.2-4.8

■ 1.6-3.2

■ 0-1.6

■ -1.6-0

■ -3.2--1.6

■ -4.8--3.2

■ -6.4--4.8

増田弘生、STARC設計技術開発の5年間

4次のpolynomial function近似

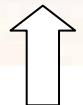

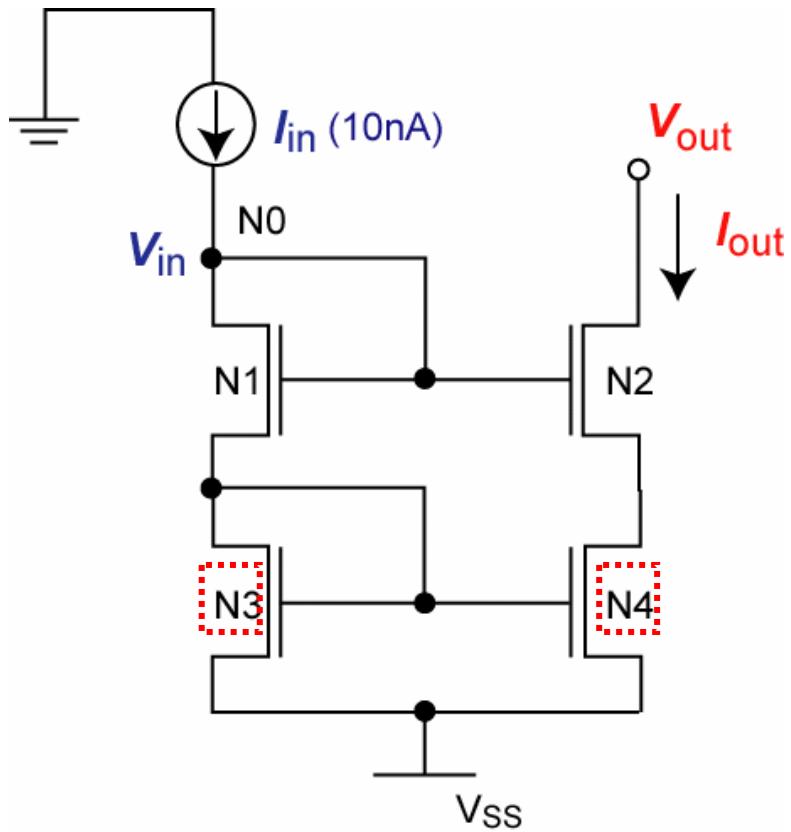

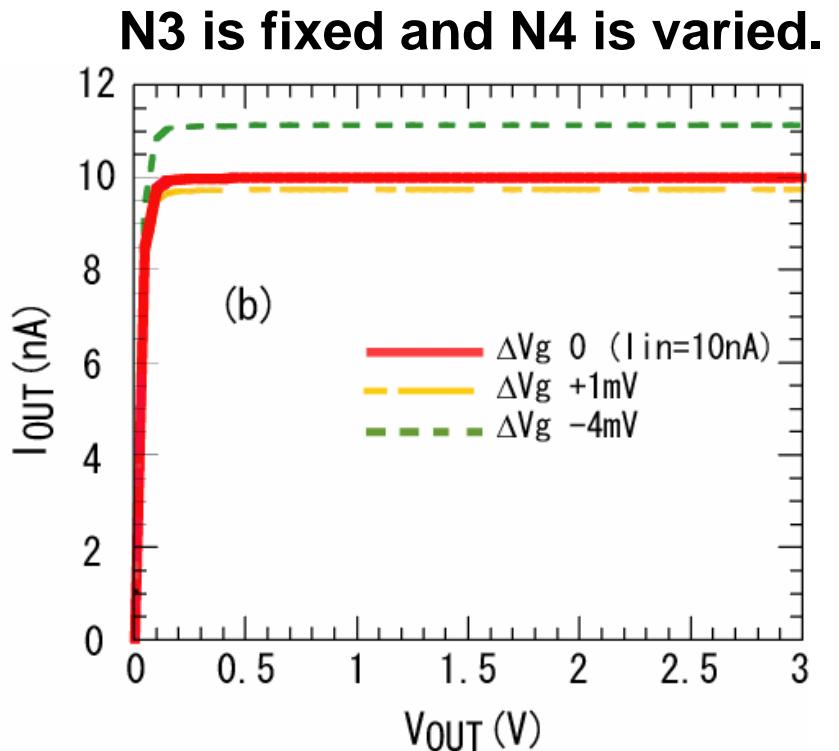

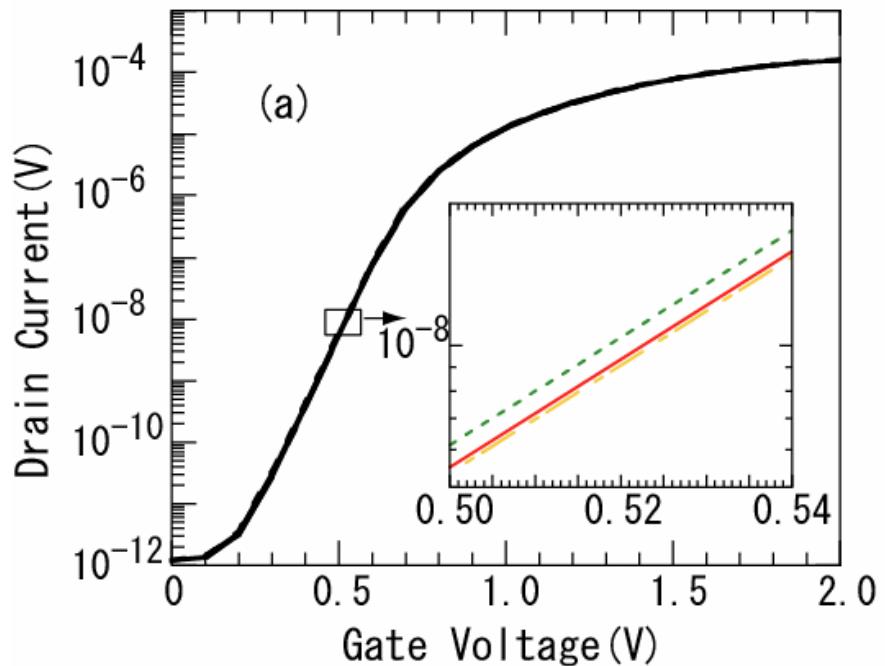

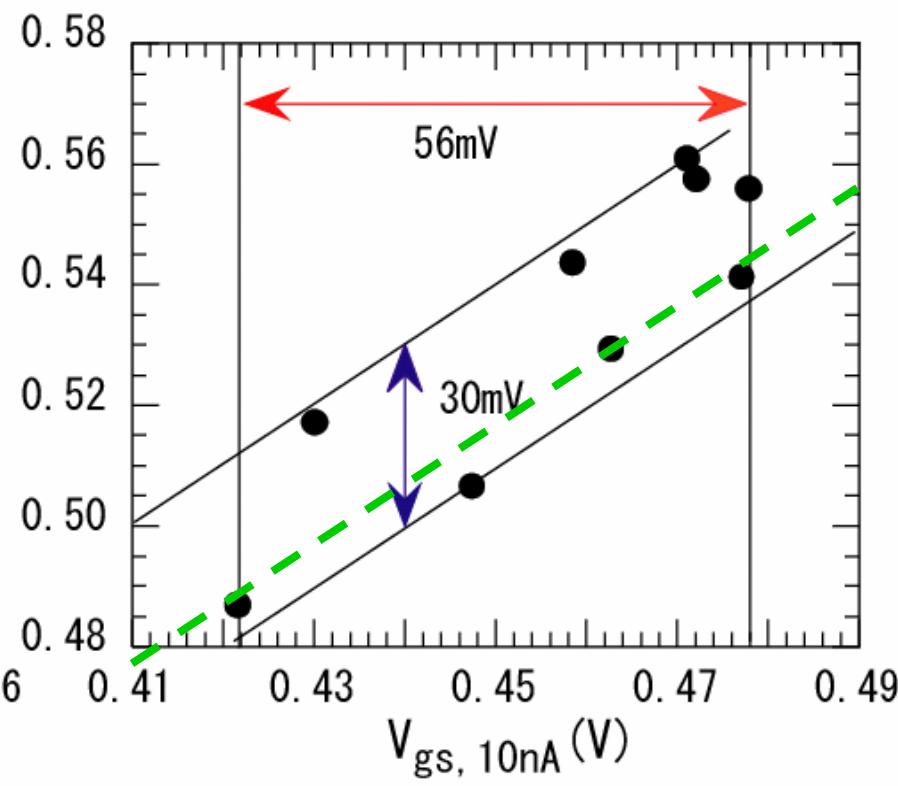

# 回路を用いた抽出: Cascode-Current Source

$L_{gate} = 0.6 \mu\text{m}$

Function: to provide a constant current  $I_{out}$ , which is proportional to the given current  $I_{in}$  and independent of  $V_{out}$ .

$I_{in} = 10 \text{nA}$ : technology variation が顕著

resistanceなどの効果が抑圧

D. Miyawaki et al., APS-DAC, p. 39, 2001.

# $I_{\text{out}}$ のばらつきはN3とN4のmismatchが原因

$I_{\text{out}}$ のばらつきを用いて $\Delta V_g$ のMismatchを見積もることができる

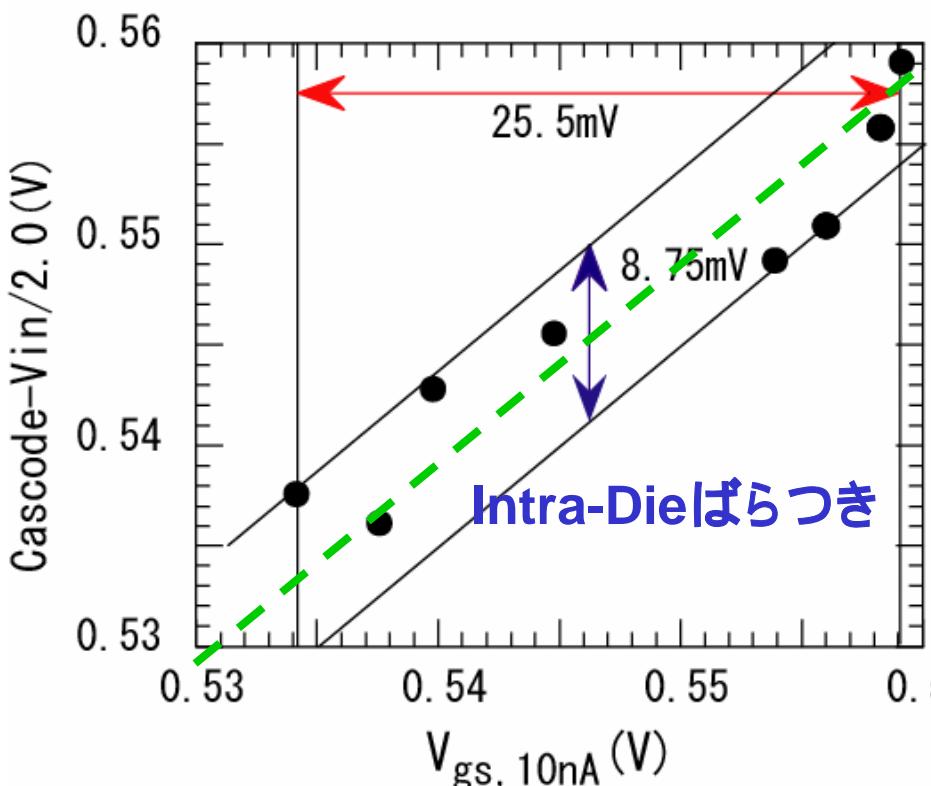

# 簡単な見積もり方法

$V_{in}$ のばらつきはN1とN3のばらつきの和が原因

$V_{in}/2$ : Inter-Dieばらつきと仮定

$V_{gs, 10nA}$ : 単体MOSFETのInter-Dieばらつき

$L_{gate}=2.1\mu m$

$L_{gate}=0.6\mu m$

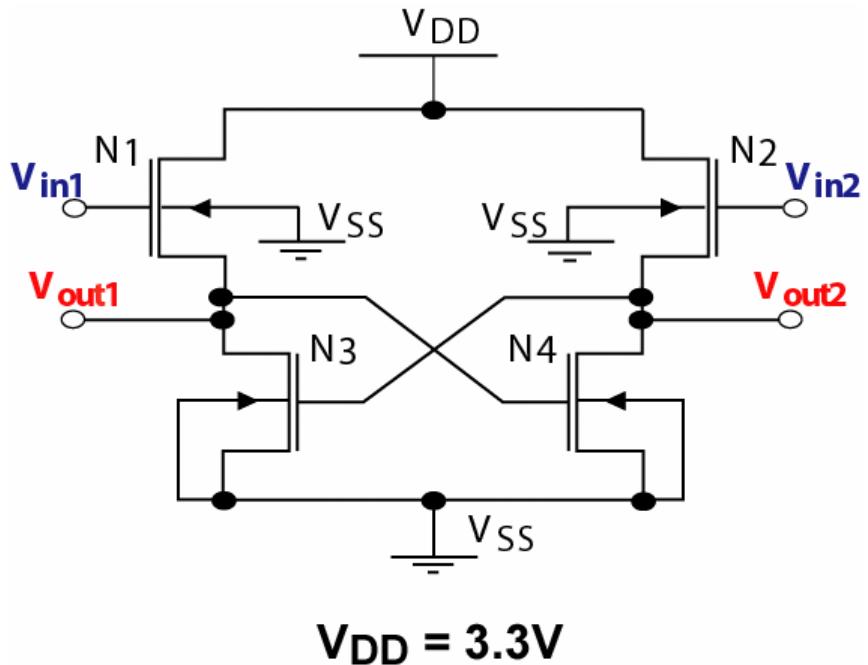

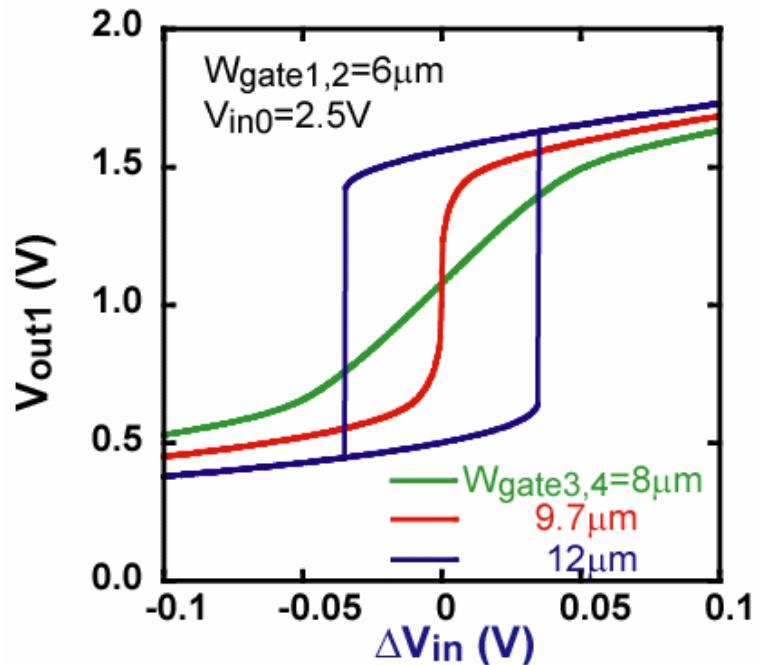

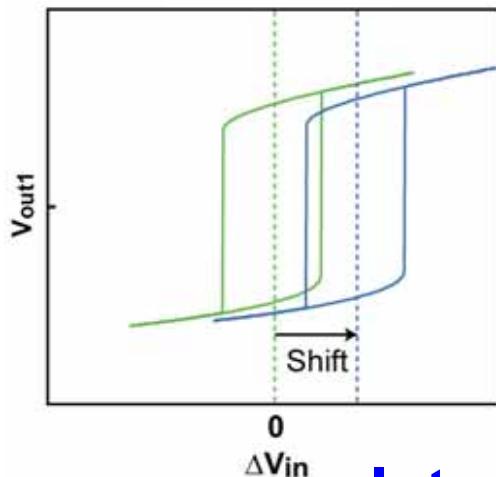

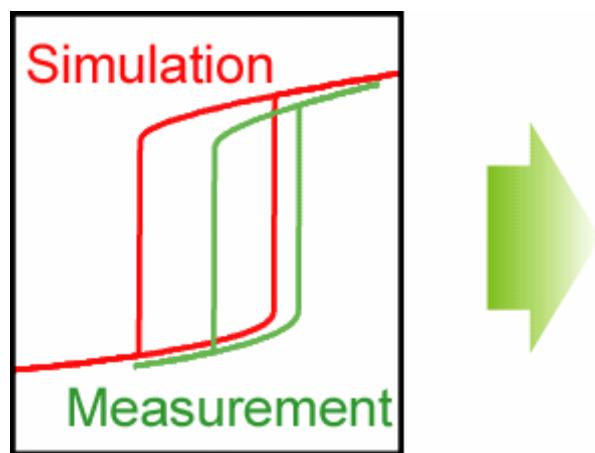

# Differential-Amplifier-Stage with Feed-back Coupling

Function: to amplify  $V_{in}$  to  $V_{out}$ .

$\Delta V_{in} = V_{in1} - V_{in2}$

チャネル幅によってHysteresisが現れる

S. Matsumoto et al., CICC, p. 357, 2001.

4個のトランジスタ全部が同じように変化する場合

Inter-Dieばらつき

4個のトランジスタが別々に変化する場合

Intra-Dieばらつき

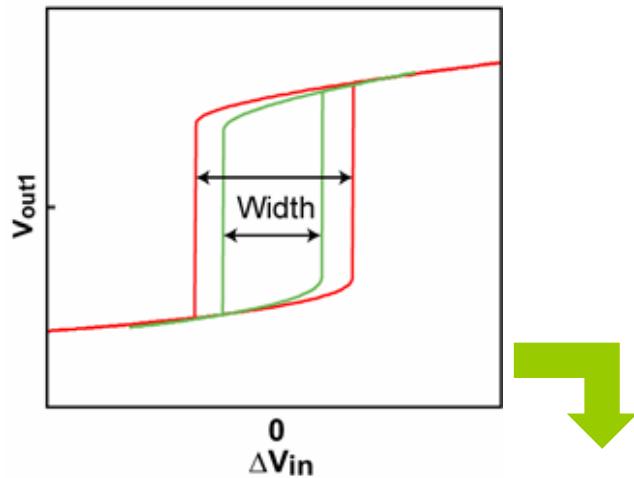

Inter-Dieばらつき抽出

Intra-Dieばらつき抽出

# ばらつき見積もり結果

## Cascode-Current Source

|       | $\Delta N_{\text{sub}}$ | $\Delta L_{\text{gate}}/0.6\mu\text{m}$ |

|-------|-------------------------|-----------------------------------------|

| Inter | 7%                      | 6.7%                                    |

| Intra | 1%                      | 3.8%                                    |

## Differential-Amplifier-Stage with Feed-Back-Coupling

|       | $\Delta N_{\text{sub}}$ | $\Delta L_{\text{gate}}/0.6\mu\text{m}$ |

|-------|-------------------------|-----------------------------------------|

| Inter | 5.9%                    | 6.2%                                    |

| Intra | 2.3%                    | 3.2%                                    |

# I-3. ばらつき予測

## 1. Process Model

### ➤ Inter-Chip ばらつき

温度分布

濃度分布

プラズマ分布

### ➤ Intra-Chip ばらつき

濃度ばらつき

欠陥分布( $1/f$ ノイズ)

Layout依存性

## 2. Stochastic Model

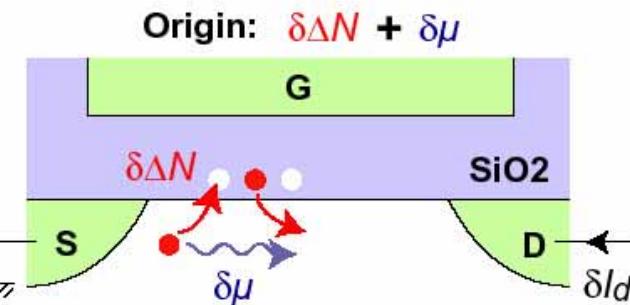

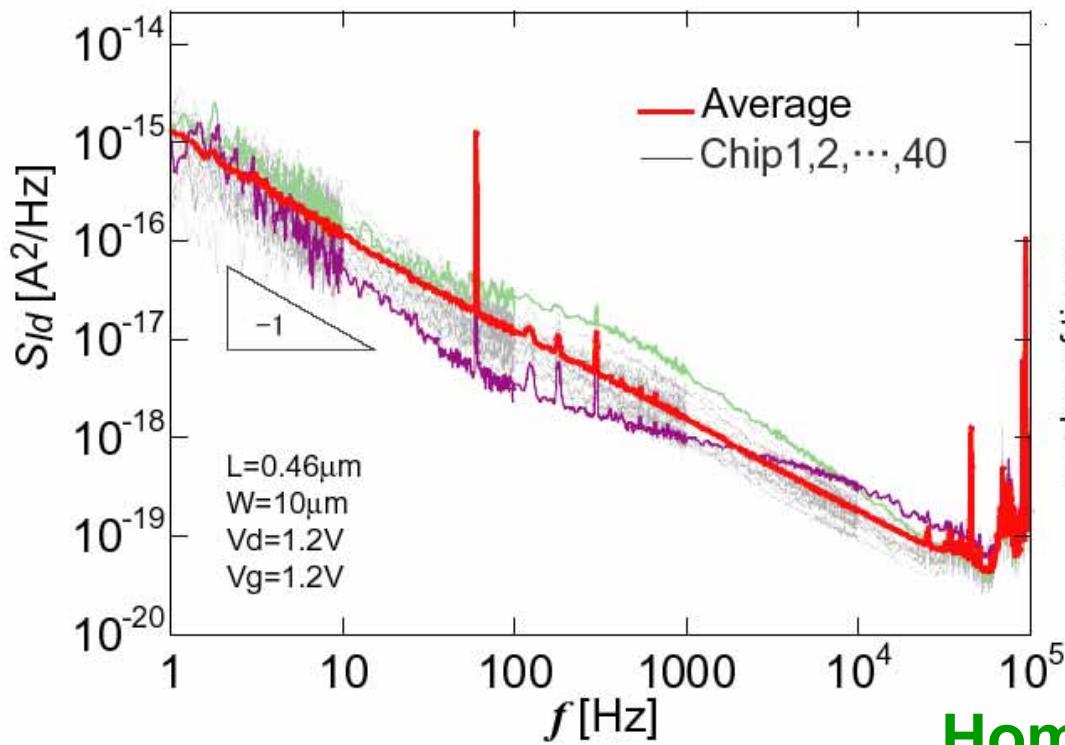

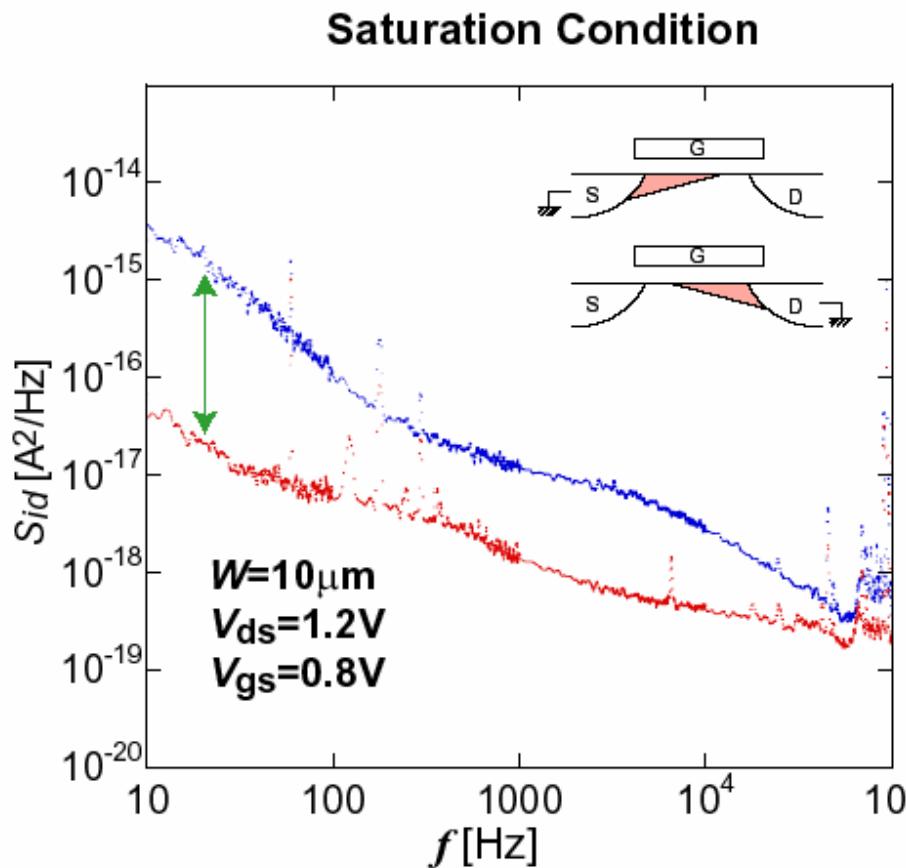

# 1/fノイズ特性

## 1/fノイズの起源

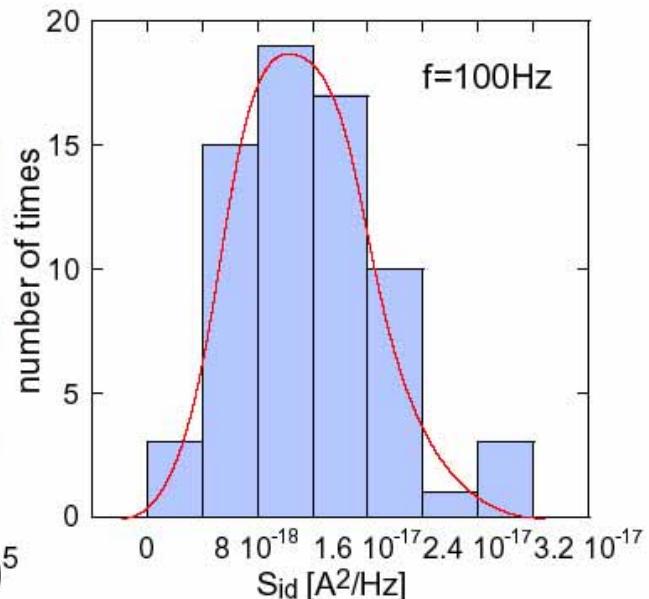

## Statistics on a Wafer

**Homogeneous Distribution**

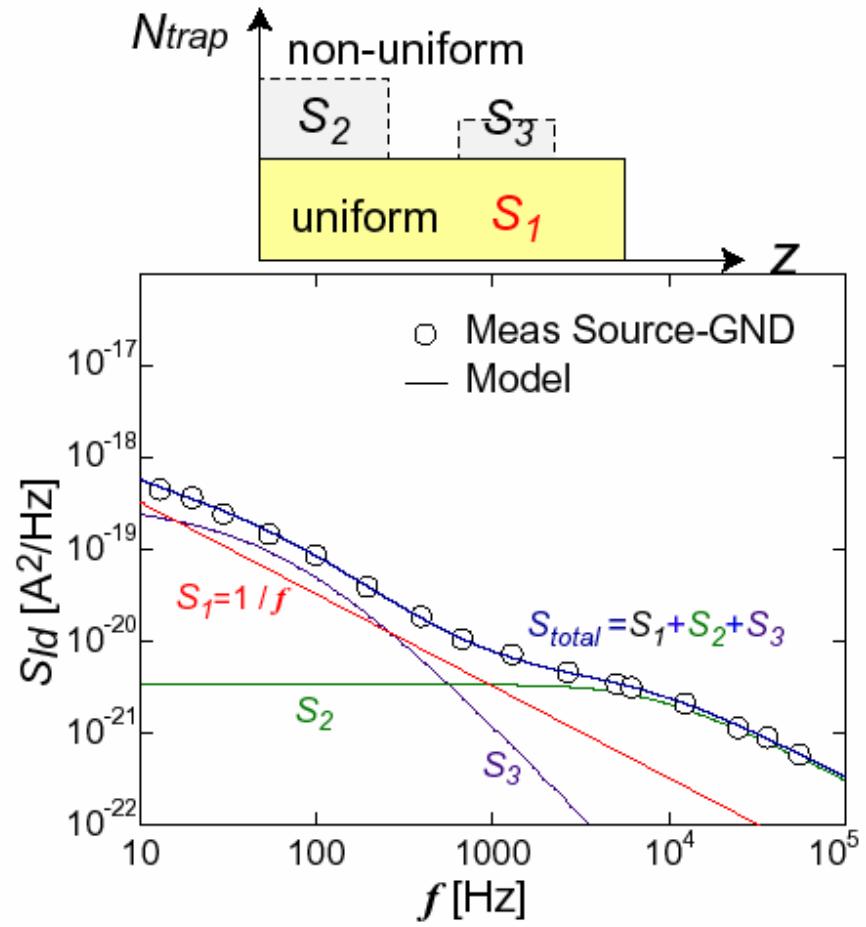

# 1/fノイズ特性からのずれ

$L_g=0.13\mu\text{m}$  (nMOSFET)

# 目次

## I. ばらつき予測

- I-1. ばらつき分類

- I-2. ばらつき見積もり

- I-3. ばらつき予測

## II. コンパクトモデルの役割

- II-1. コンパクトモデル

- II-2. コンパクトモデルの精度

- II-3. コンパクトモデルの可能性

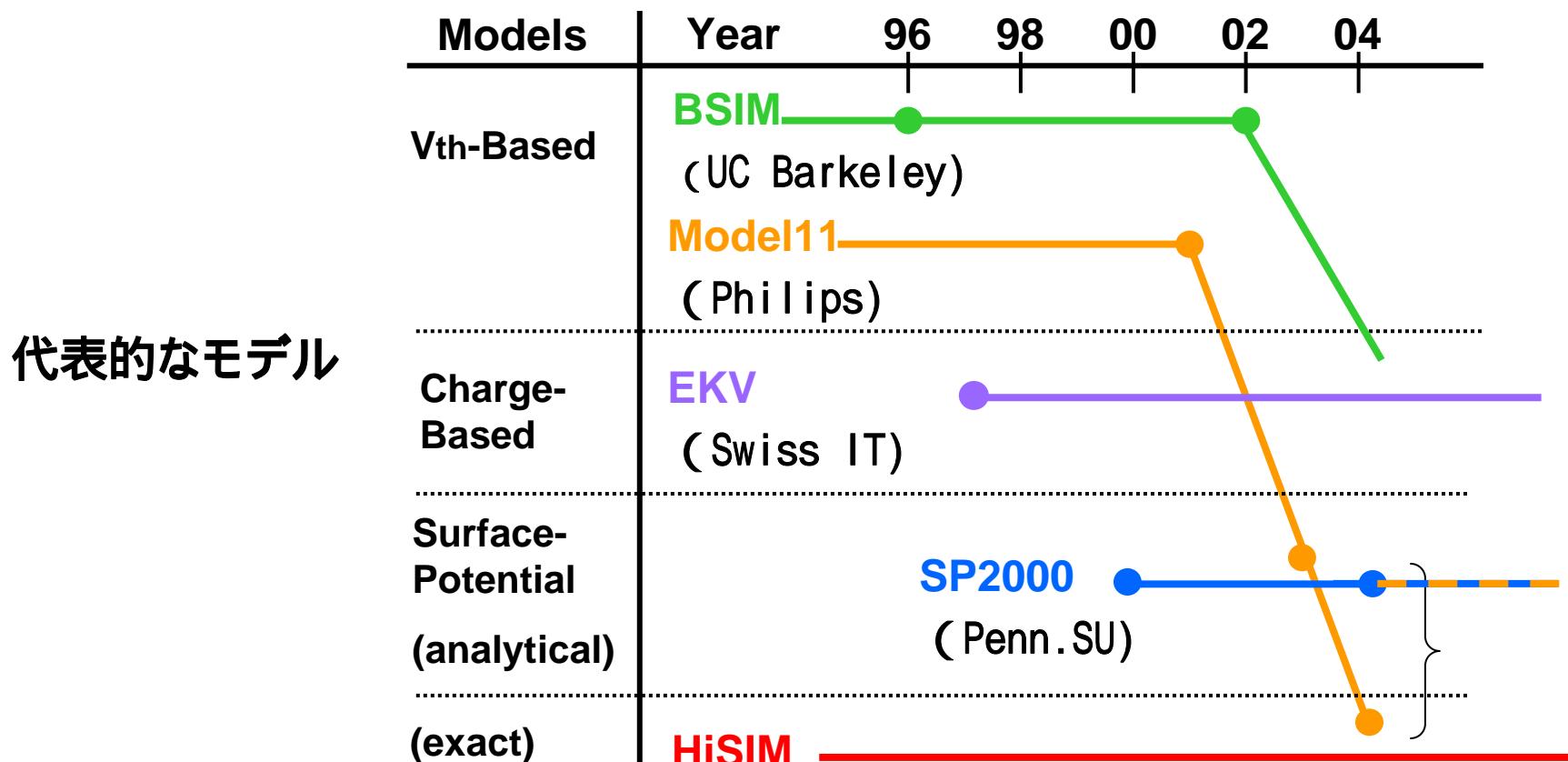

## II-1. コンパクトモデル

- 回路モデルはデバイスと集積回路をつなぐ要

- 回路モデルの精度が回路予測精度を決定

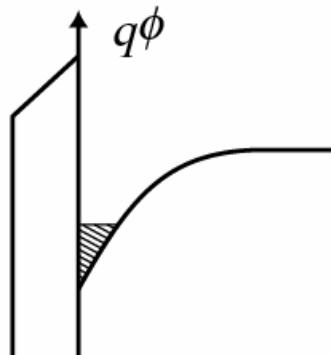

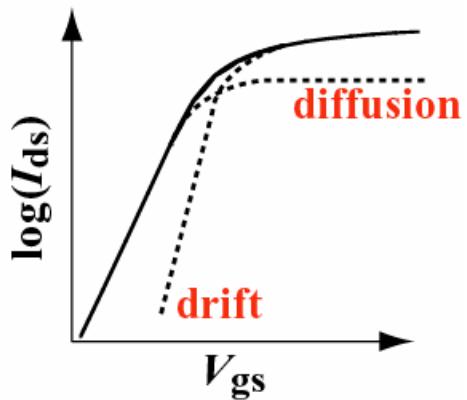

# デバイスの基本方程式

-Poisson:

$$\nabla^2\phi = -\frac{q}{\epsilon_{\text{Si}}}(N_D - N_A + p - n)$$

$$n = n_i \exp \frac{q(\phi - \phi_n)}{kT}$$

$$p = n_i \exp \frac{q(\phi_p - \phi)}{kT}$$

-Current Density:

$$j_n = q\mu_n n \frac{\phi}{y} + qD_n \nabla n$$

$$j_p = q\mu_p p \frac{\phi}{y} - qD_p \nabla p$$

-Continuity:  $I(t) = I_0(t) + \frac{dQ}{dt}$

( solved by circuit simulator )

-Quantum Mechanical Effect

-Ballistic Effect

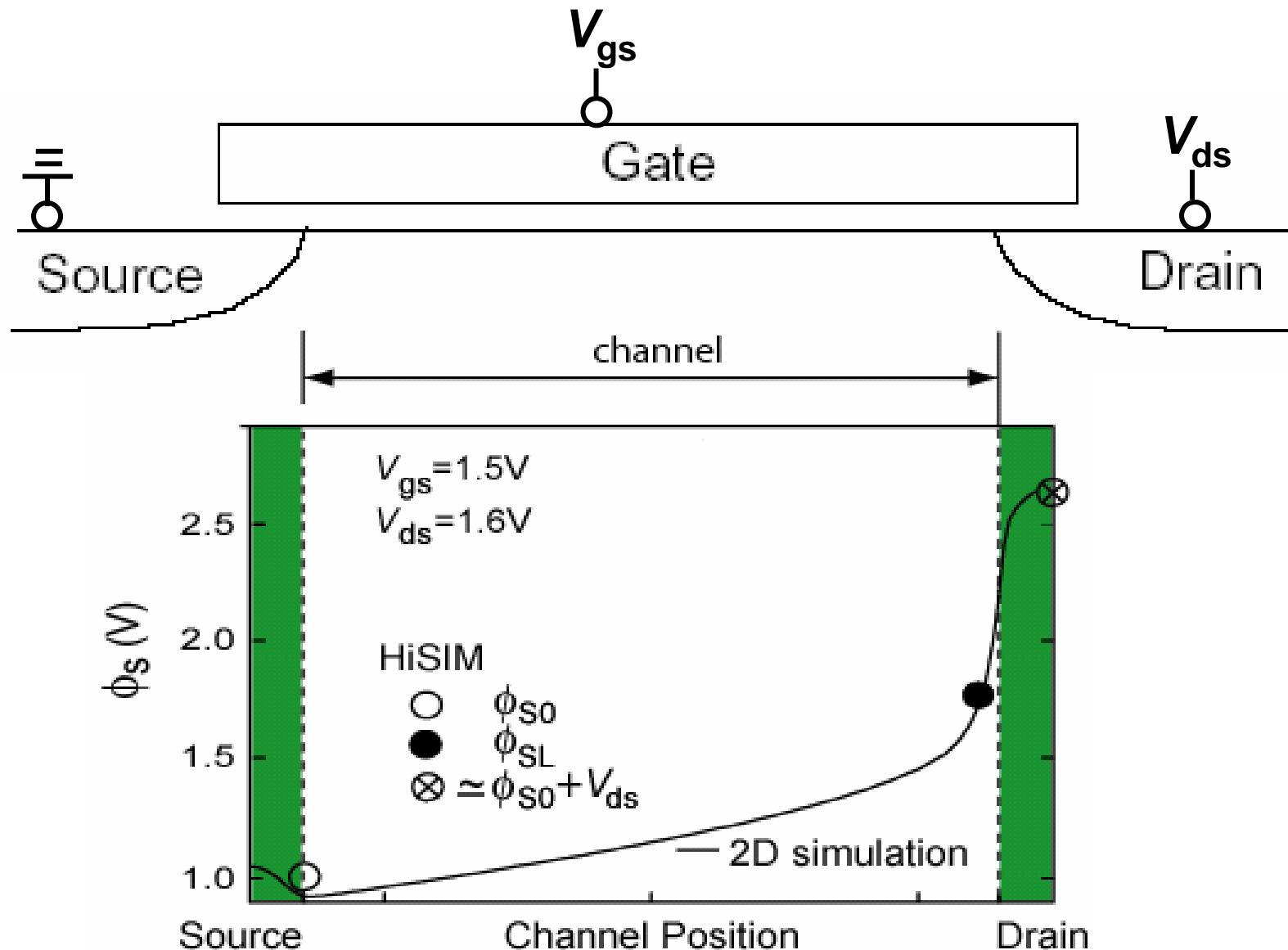

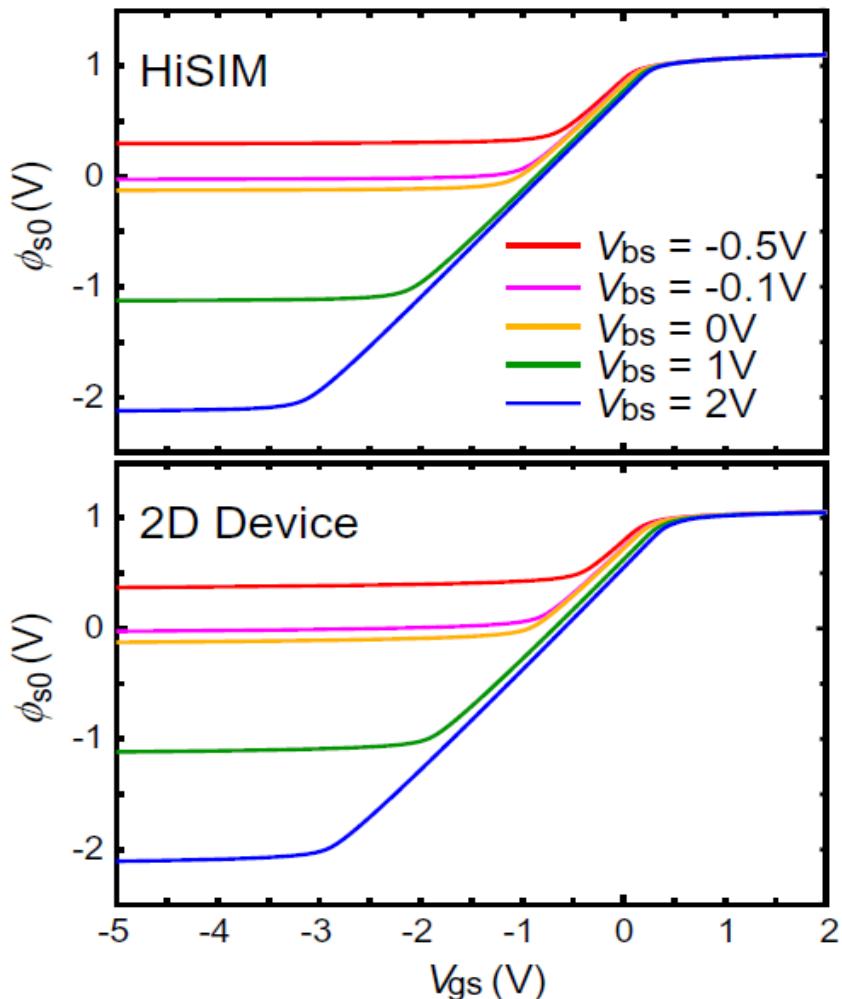

# 表面ポテンシャル

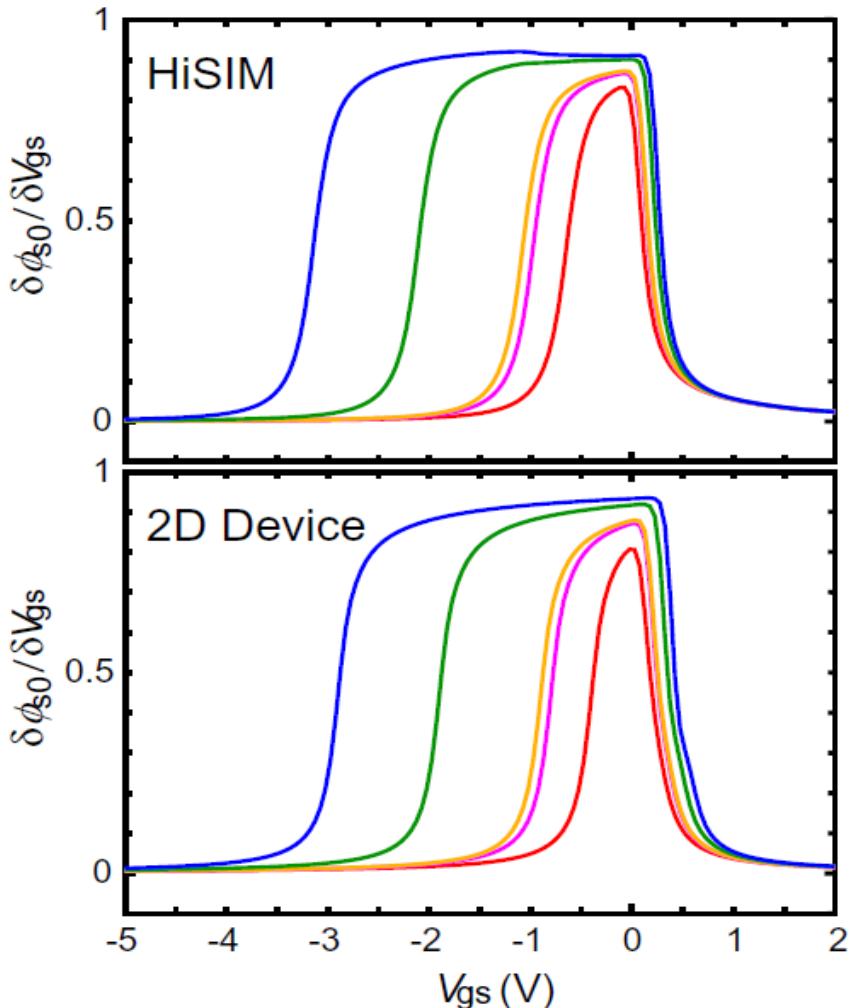

## II-2. コンパクトモデルの精度

### 表面ポテンシャルの比較

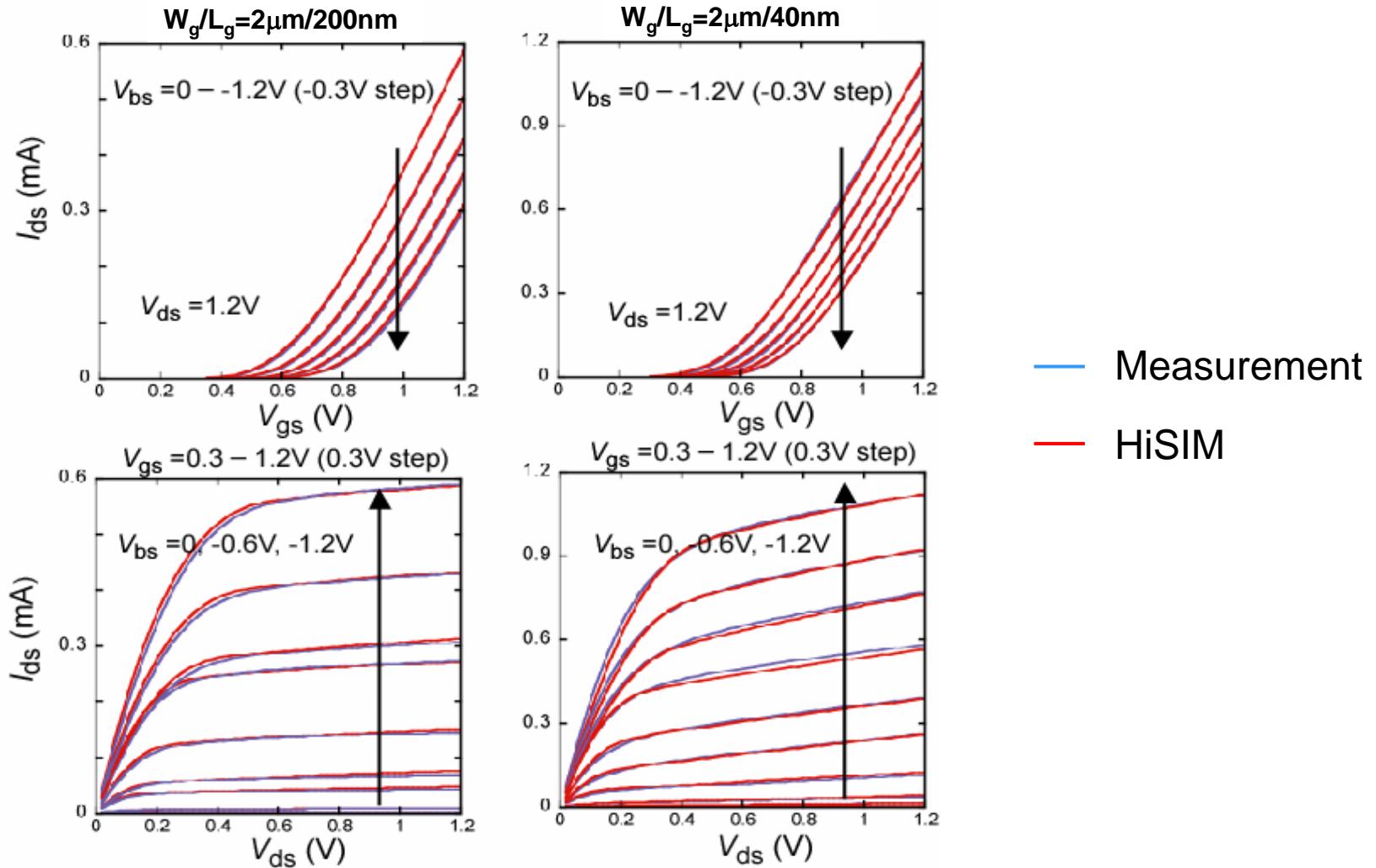

# 45nmノードにおける電流の再現性

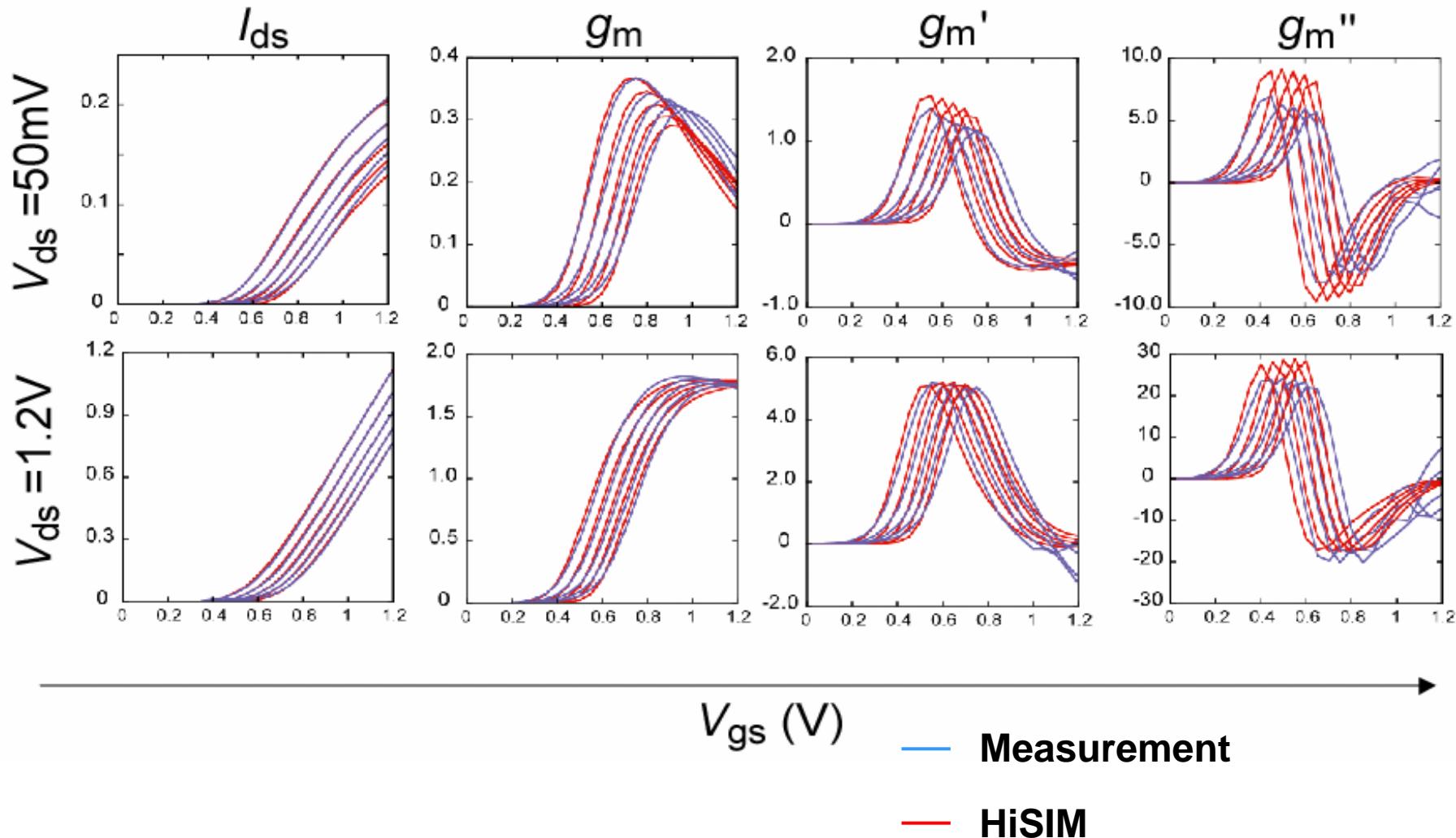

# 微分值の再現性

$$W_g/L_g = 2\mu\text{m}/40\text{nm}$$

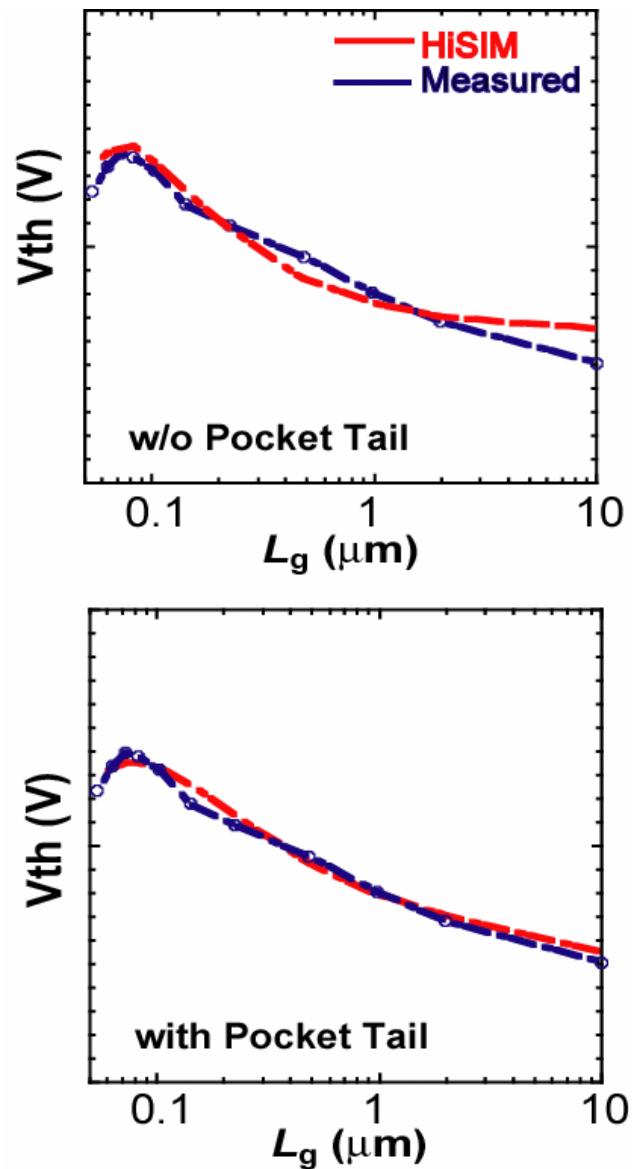

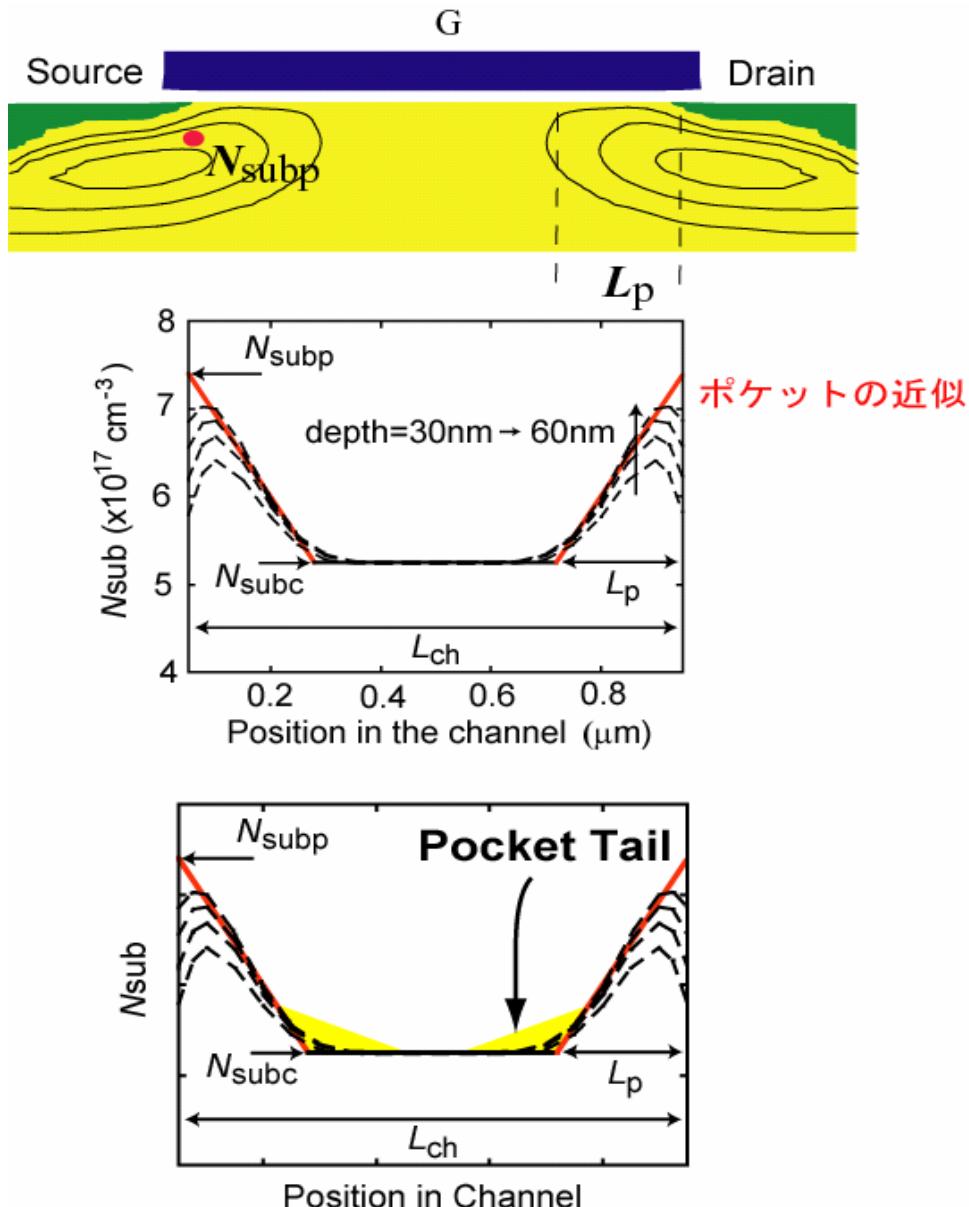

# ポケット注入の場合

## II-3. コンパクトモデルの可能性

### モデルパラメタの予測性

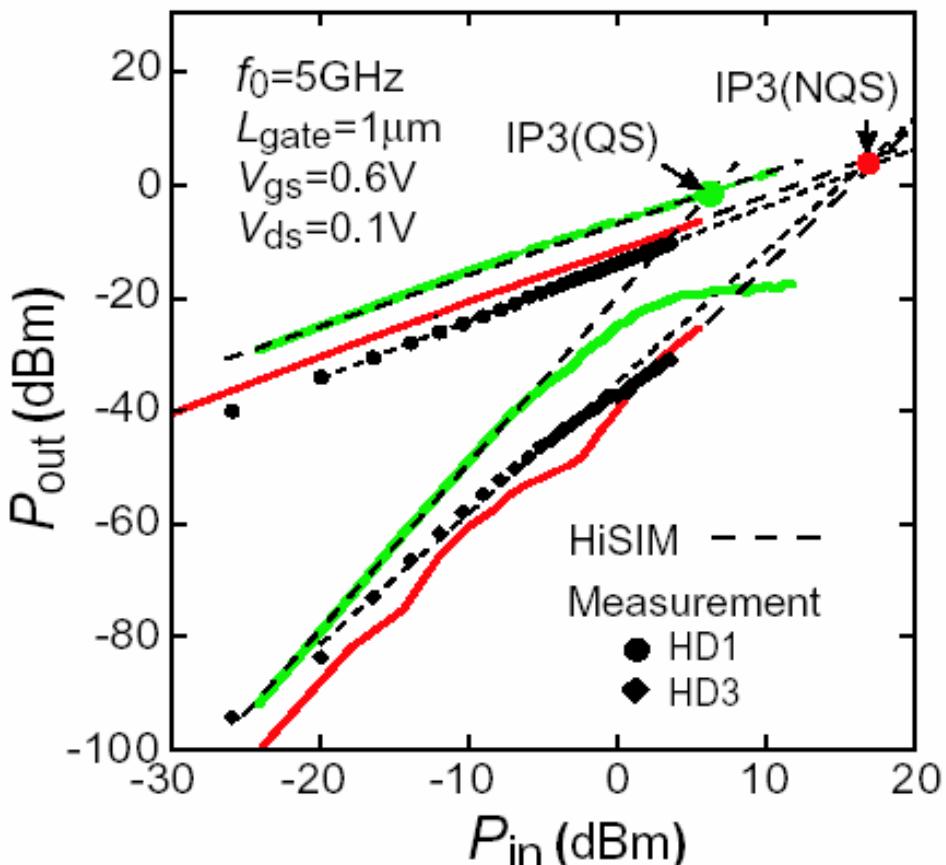

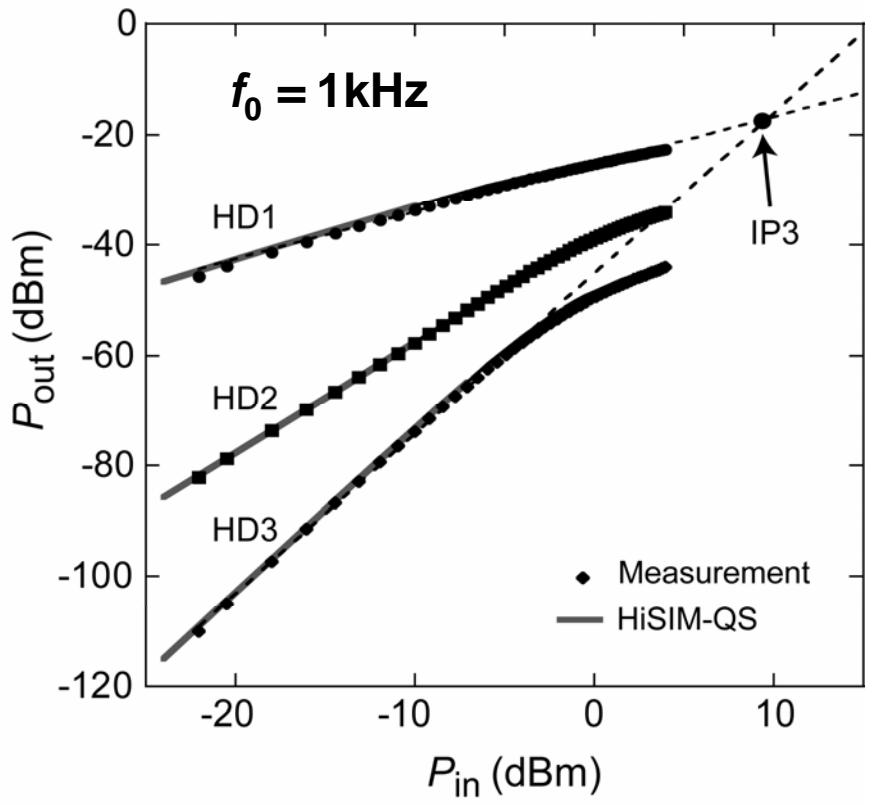

# RF特性の予測性

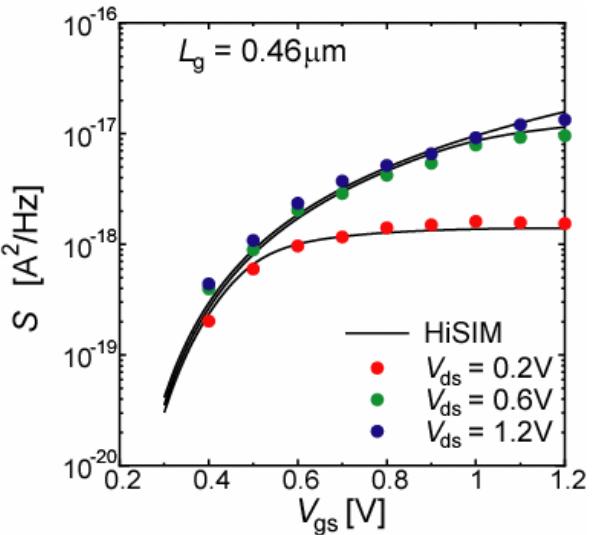

## 1/f Noise

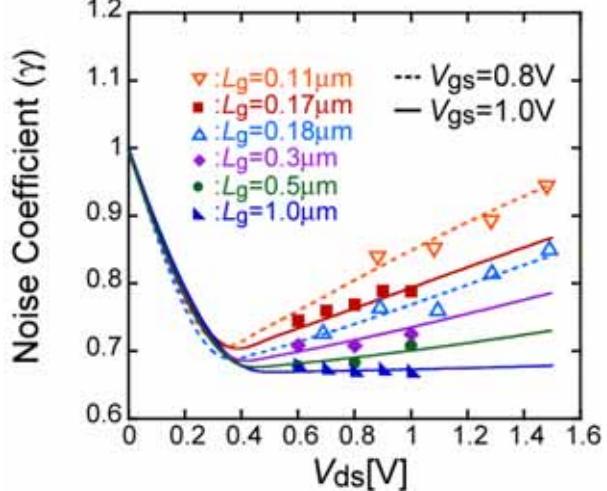

## Thermal Noise

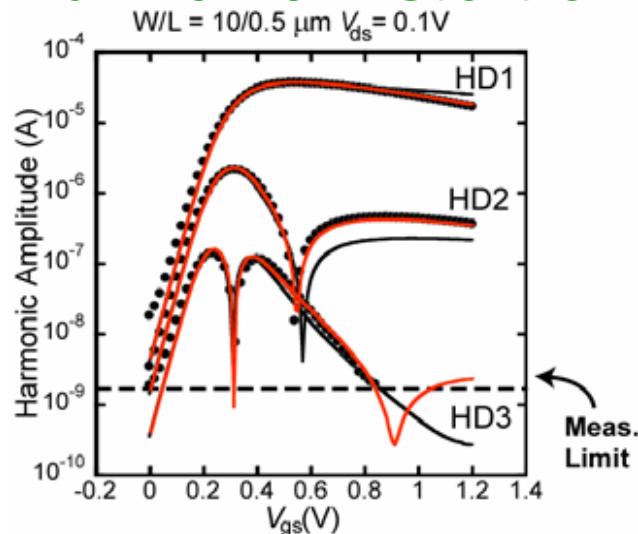

## Harmonic Distortion

- No model parameters are required.

- Features are determined only by *I-V* characteristics.

Electrostatic effect is still dominating.

Surface potential is important.

# IP3 Prediction

## キャリアの遅延効果

Y. Takeda et al., CICC, p. 827, 2005.

D. Navarro et al., IEEE MWC Lett., p. 125, 2006.

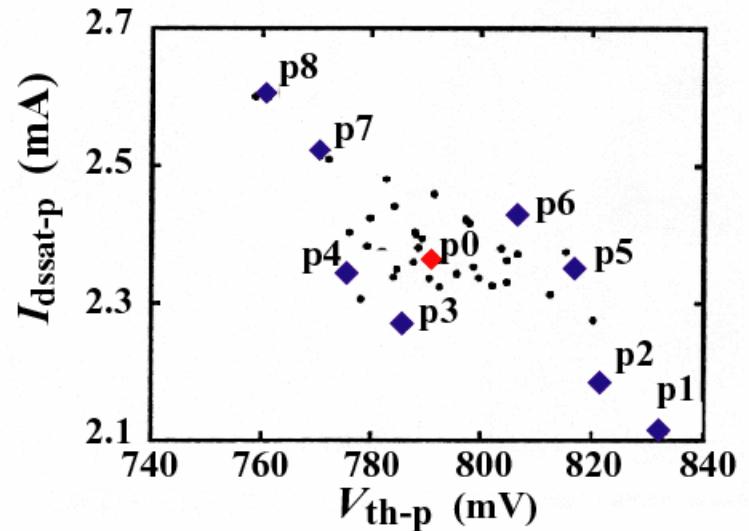

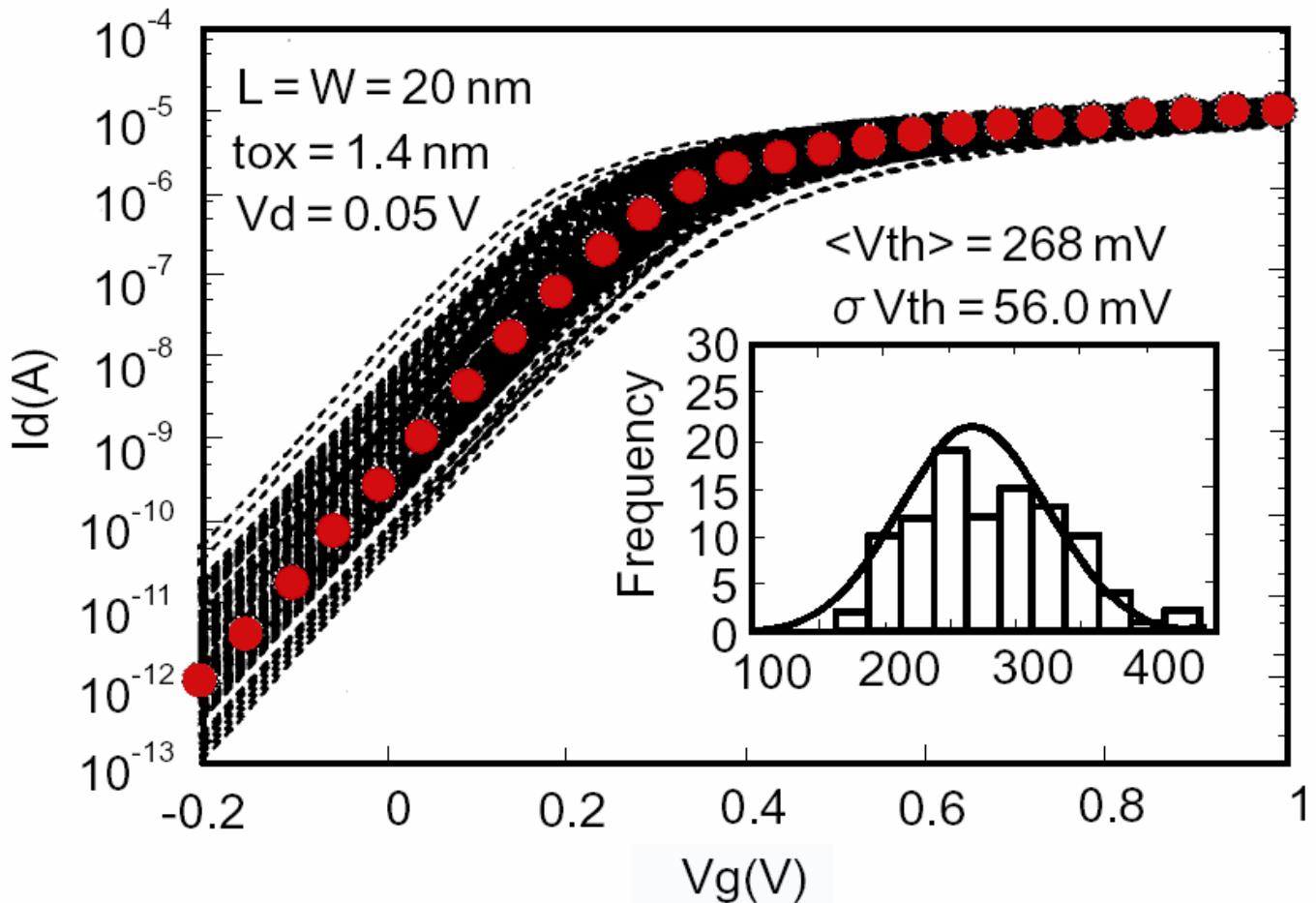

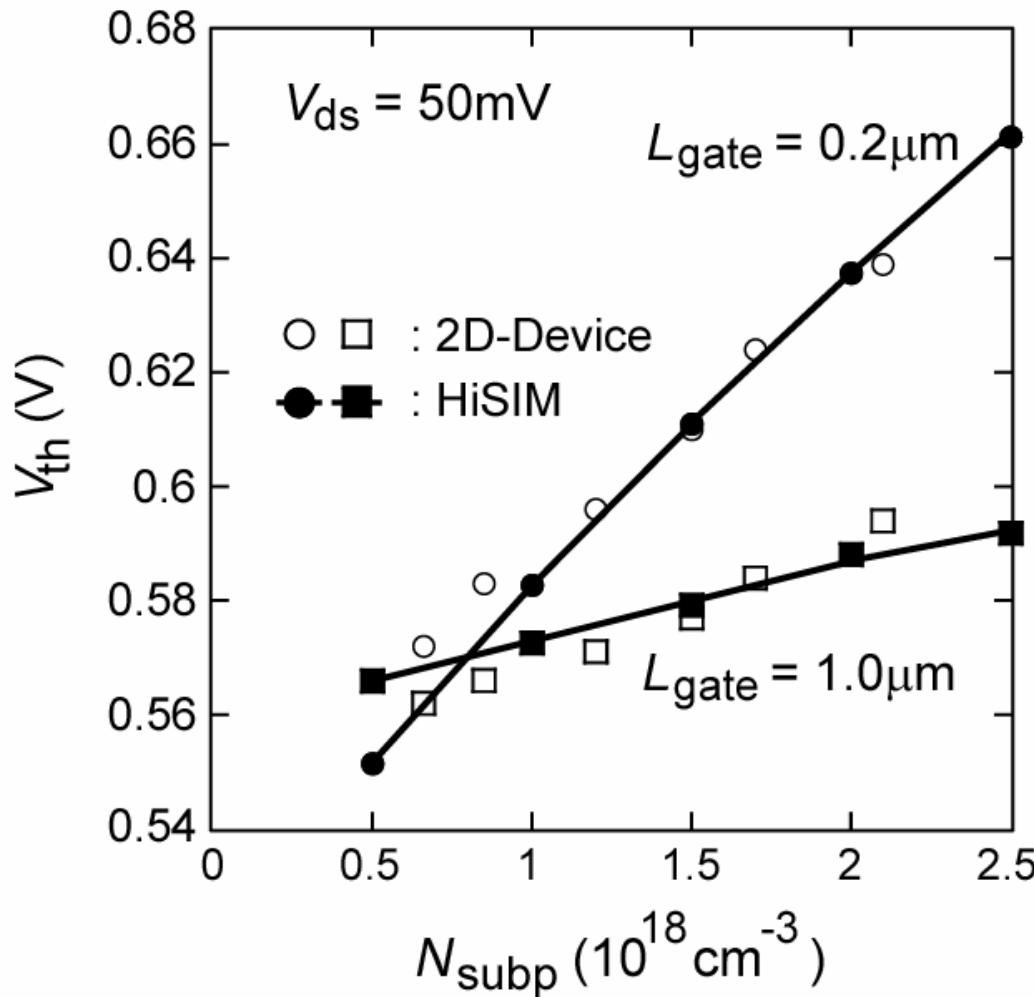

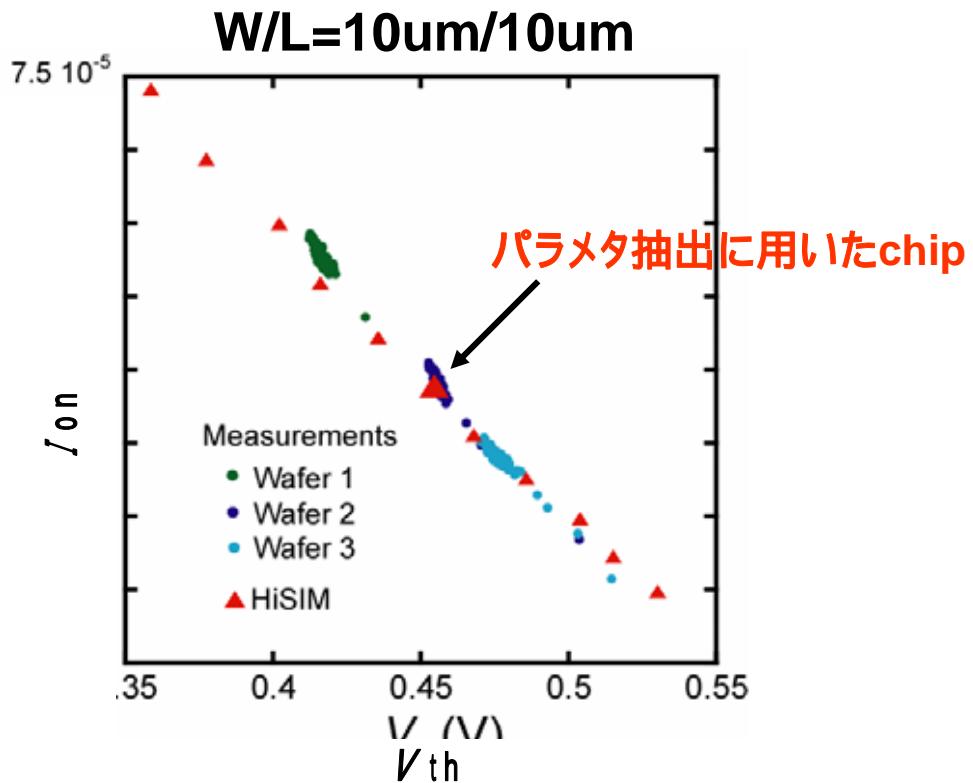

# 基板濃度Nsubを振ったwaferの特性予測

$I_{on}$ は基本的には  $V_{th}$  に支配されている

プロセスばらつきモデルがあればデバイス特性のばらつき予測可能

# まとめ

- Intra-Chipばらつきの増大

- Intra-Chipばらつきの原因

- 不純物分布

- 欠陥分布

- Layout依存性

- 各種ばらつきモデルの構築が必須

- Stochasticモデルの構築も大事

- Inter- & Intra-Chipばらつきの考慮

- 回路ではばらつきが抑制

- クリティカルパスの影響