# 半導体パッケージ技術の動向

## — デジタル家電の小型化・ 高性能化を担うSiP技術 —

実装WG(WG7)

(株)ルネサステクノロジ / 春田 亮

### 略語集

**BG** : Back Grinding

**FCB** : Flip Chip Bonding

**KGD** : Known Good Die

**MCP** : Multi Chip Package

**SiP** : System in Package

**WB** : Wire Bonding

# 2006年度 WG7 メンバ

リーダ : 春田 亮(ルネサス)

サブリーダ : 中島 宏文(NECエレ)

国際対応委員 : 宇都宮 久修(ICT)、中島 兼務

委員 : 春口 秀哉(シャープ)、上田 茂幸(ローム)、

木村 通孝(ルネサス)、高田 隆(松下)、

西山 和夫(ソニー)、吉田 英治(富士通)、

二渡 信夫(沖)、春日 壽夫(NECエレ)、

大塚 雅司(東芝)、高橋 邦明(東芝)、

臼井 良輔(三洋)、大槻 哲也(エプソン)、

特別委員 : 林 智雄(SEAJ; 東京精密)、

前原 信治(日本特殊陶業)

# STRJ-WG7とJJTRC

電子システム実装技術委員会 … 標準技術部

実装技術ロードマップ専門委員会 (JJTRC)

WG1: 電子機器

WG3: パッケージ

WG4: 電子部品

WG5: 実装基板

WG6: 実装設備

隔年、「日本実装技術ロードマップ(JJTR)」を発行。

今回、「07年5月に 2007年度版(JJTR2007) を発行予定。

# 2006年度活動

## 1) JJTR2007年度版(JJTR2007)の作成

- ・2005年度版の内容の見直し

## 2) ITRS2006 Updateへの協力

- ・JJTR2007での検討内容をITRS2006 Updateへ反映

## 3) ITRS SiP White Paper作成への協力

- ・新規にSiP White Paperを作成 ('07/3発行予定)

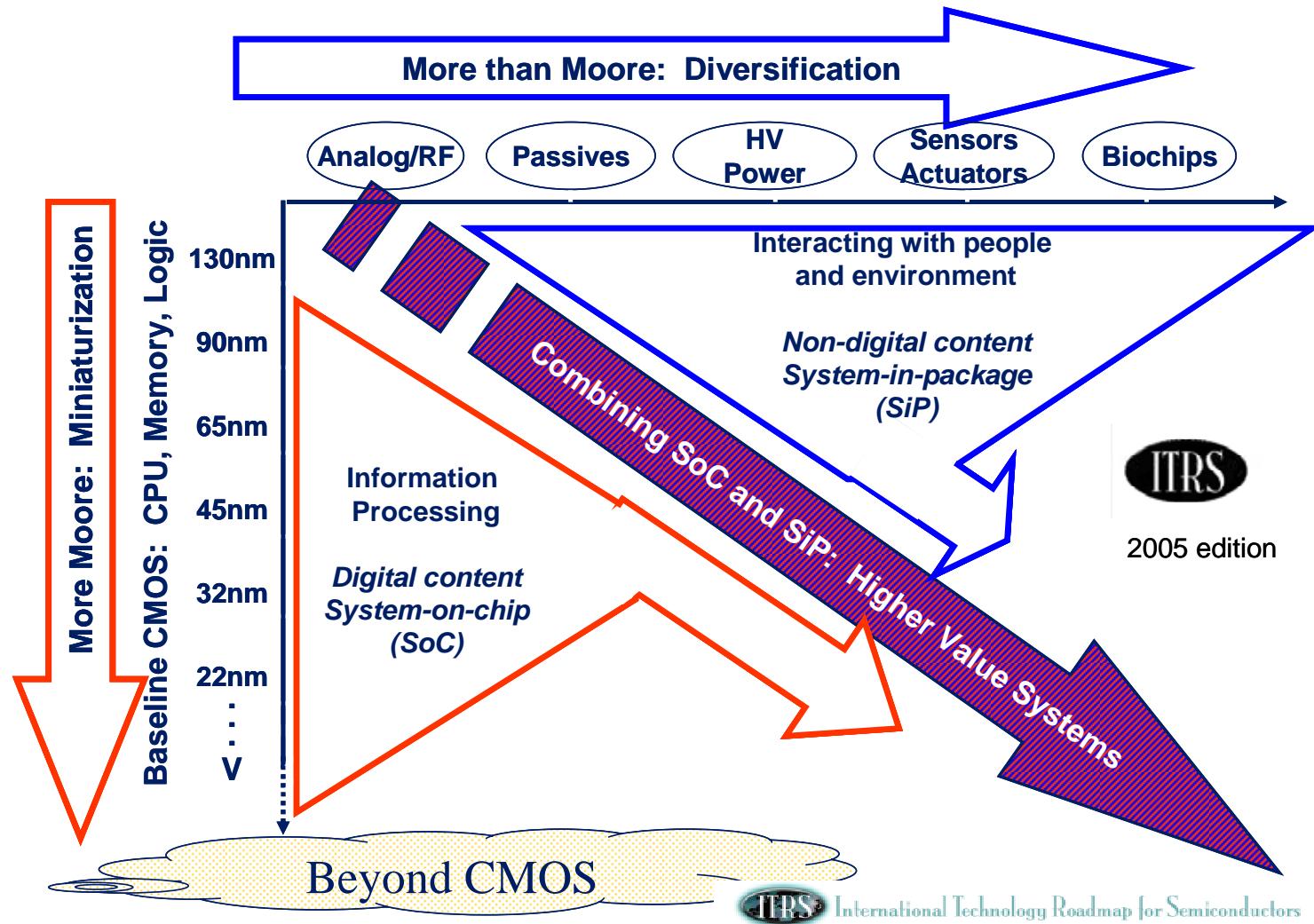

# Moore's Law and More

出典: ITRS 2005

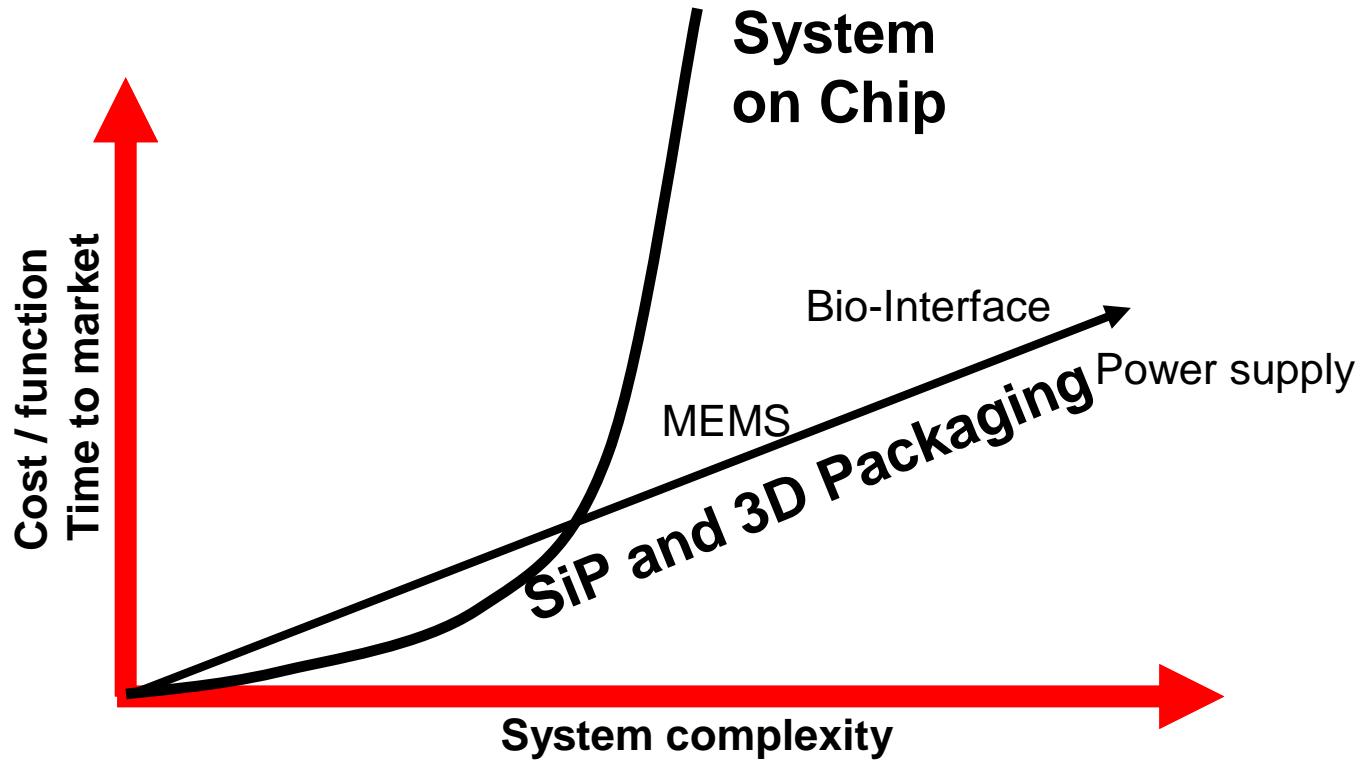

# Comparison between SoC & SiP

*SoC and SiP Comparison for Cost per Function and Time to Market vs. Complexity*

出典:ITRS 2005

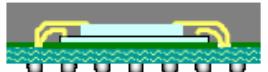

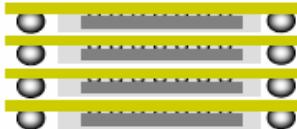

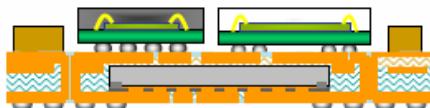

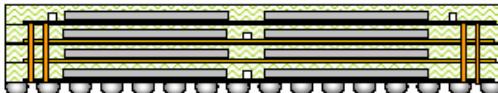

# 各種SiP/MCPの構造

|       |            |                                                                                      |                                                                                      |

|-------|------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 平面構造  |            |    |   |

| 3次元構造 | チップ間ビア経由接続 |     |    |

|       | チップ間直接接続   |   |   |

| 内蔵構造  |            |   |  |

|       |            |  | Package in Package                                                                   |

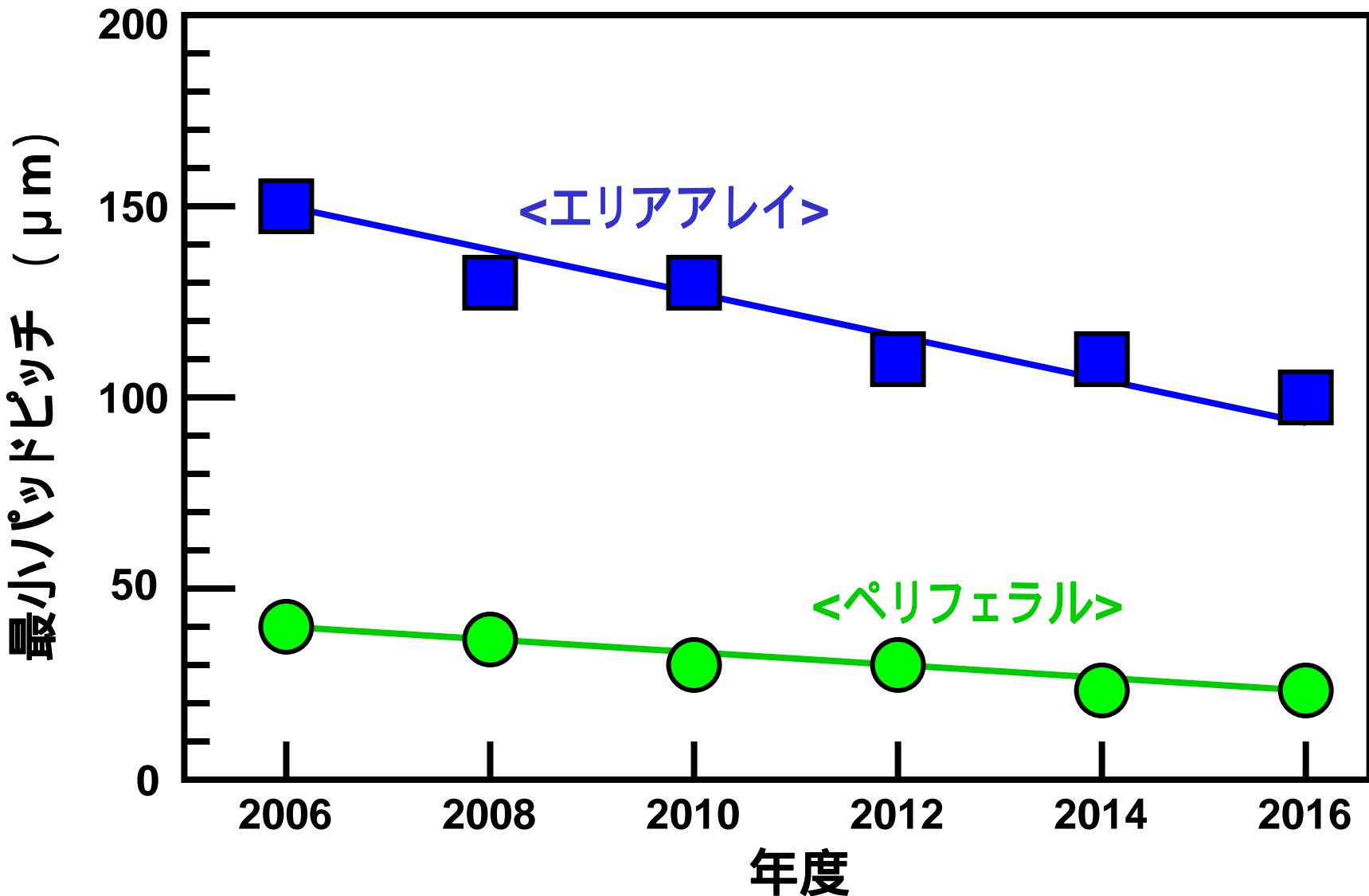

# SiP/MCPの動向

## — Low cost/Hand-held用途のSiP/MCP —

|                 | 2006 | 2008 | 2010 | 2012 | 2014 | 2016 |

|-----------------|------|------|------|------|------|------|

| 搭載IC マイコン       |      |      |      |      |      |      |

| ロジック            |      |      |      |      |      |      |

| メモリ             |      |      |      |      |      |      |

| RF/Mixed Signal |      |      |      |      |      |      |

| 最大搭載IC個数        | 8    | 10   | 10   | 12   | 12   | 14   |

| 最大チップ積層数        | 8    | 8    | 8    | 10   | 10   | 12   |

| 最薄チップ厚さ (μm)    | 40   | 35   | 25   | 20   | 17   | 15   |

| PKG最大端子数        | 600  | 800  | 800  | 800  | 1000 | 1000 |

| PKG取付高さ (mm)    | 1.4  | 1.2  | 1.0  | 1.0  | 0.8  | 0.8  |

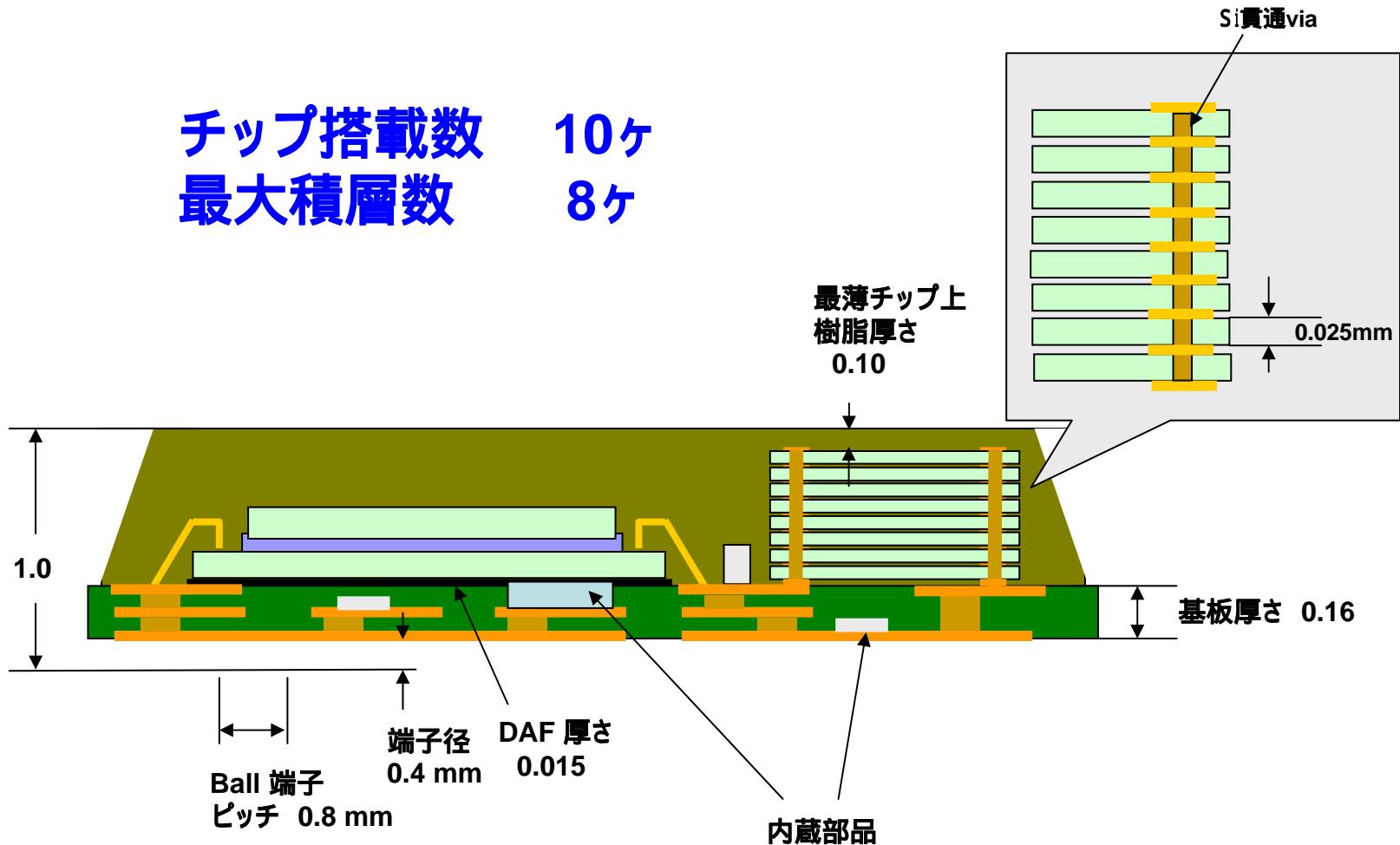

# 2010年のSiPの事例

チップ搭載数 10ヶ

最大積層数 8ヶ

# 3次元構造SiPの課題

樹脂封止技術

薄厚封止技術

低反り封止技術

薄チップ化技術

低ストレス裏面研磨技術

ダイシング技術

ピックアップ技術

WB技術

狭ピッチ接続技術

ロングワイヤ形成

低ループワイヤ形成

基板技術

薄厚基板技術

低反り基板技術

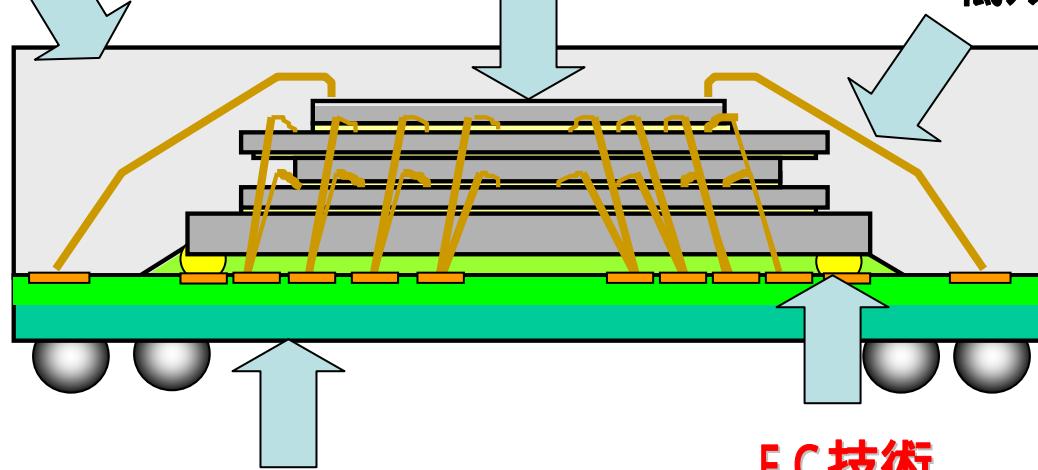

FC技術

狭ピッチ接続技術

多ピン接続技術

アンダーフィル技術

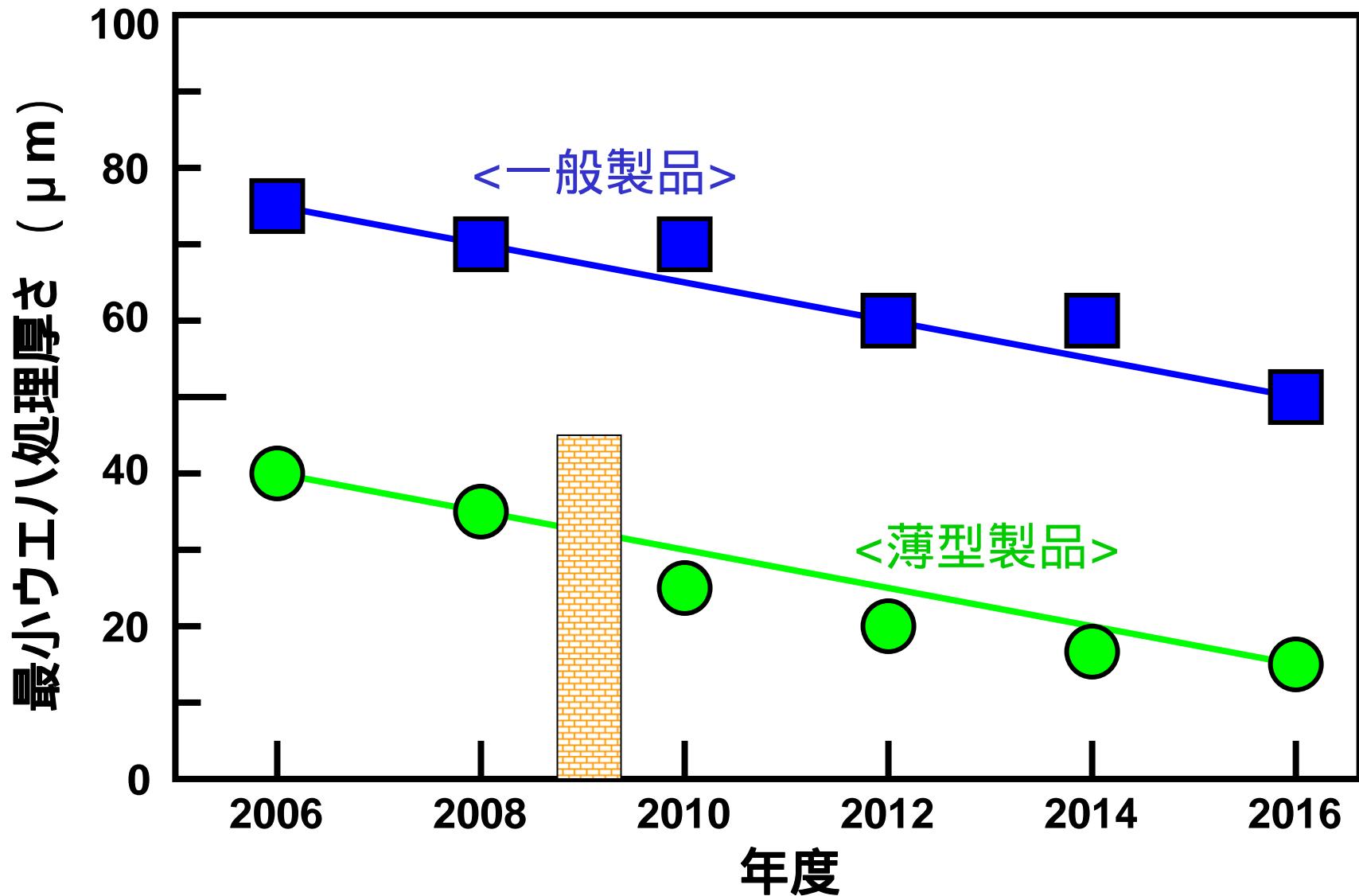

# 薄チップ化技術

# BG技術の課題

- ダメージレス

- ・裏面研磨破碎層の除去による強度確保

- 研磨後のウエハ反り防止

- ・極薄チップは反り易く、ハンドリングが困難

- 大ウエハ対応

- ・450 での均一性、無欠陥化

- 極薄チップのハンドリング

- ・次工程以降での極薄チップの扱いが困難

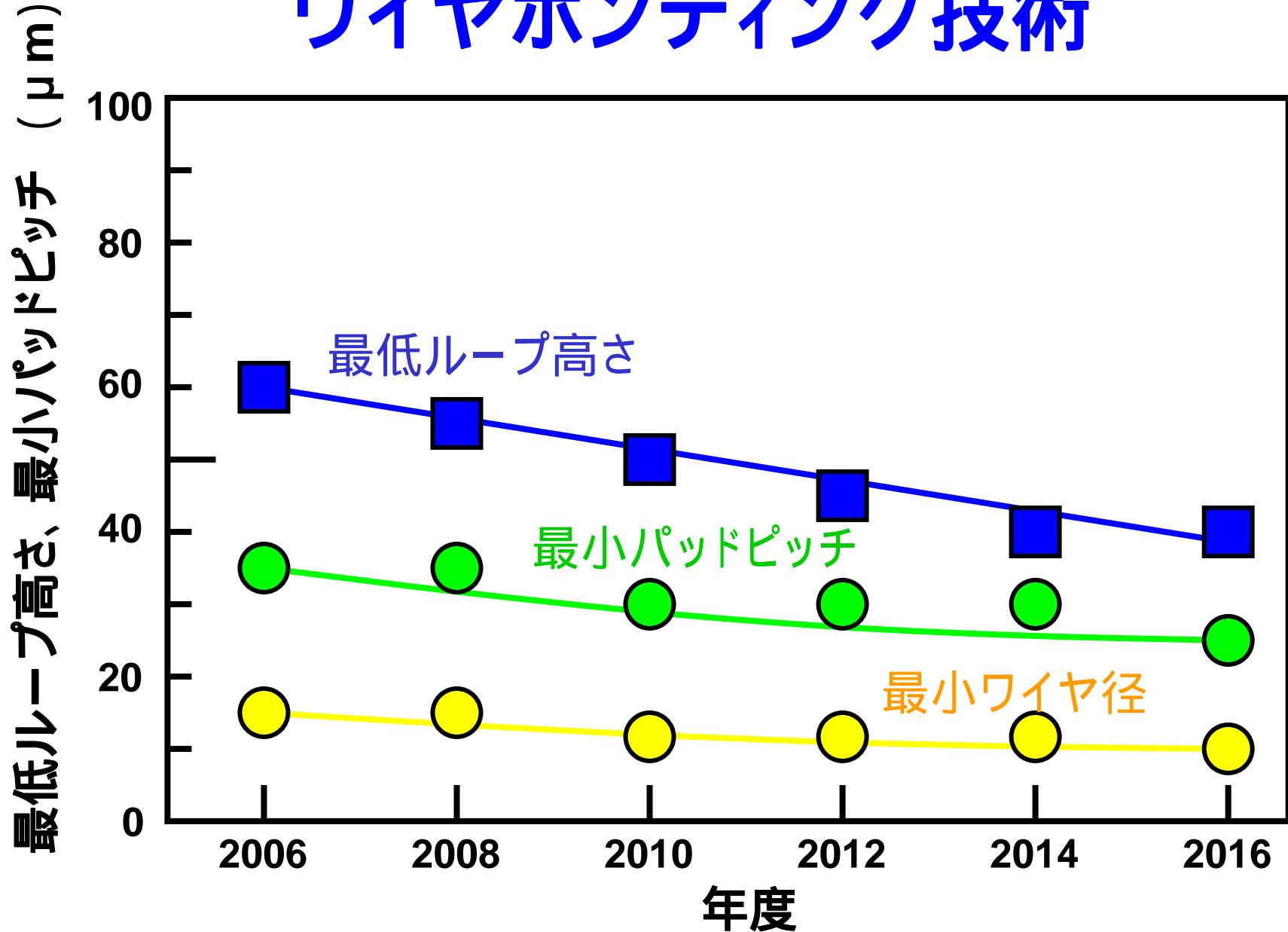

# ワイヤボンディング技術

# WB技術の課題

## WB装置(ハードとソフト)

- ・**高精度WB装置(位置精度)**

- ・**高精度ワイヤ制御技術**

- ・**高信頼接合技術(低ダメージ)**

- ・**高速・低コスト装置・技術**

## WB技術実現のためのインフラ技術

- ・**極微細金線および極微細金線対応キャピラリ**

- ・**ワイヤ流れの少ない封止技術**

- ・**狭ピッチパッド対応プロープ技術**

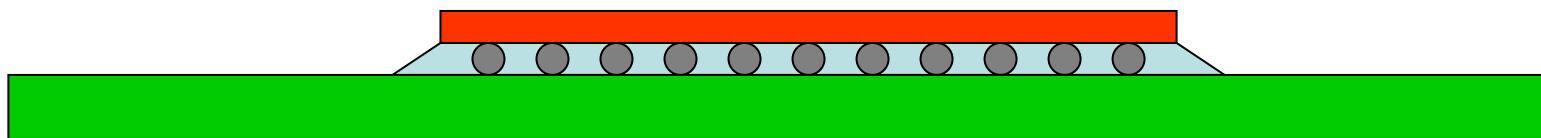

# フリップチップ技術

# FCB技術の課題

## はんだボール形成技術

- ・高精度微小はんだボール形成

## はんだボール搭載

- ・極狭間隙樹脂充填技術

- ・狭ピッチ対応低成本実装基板

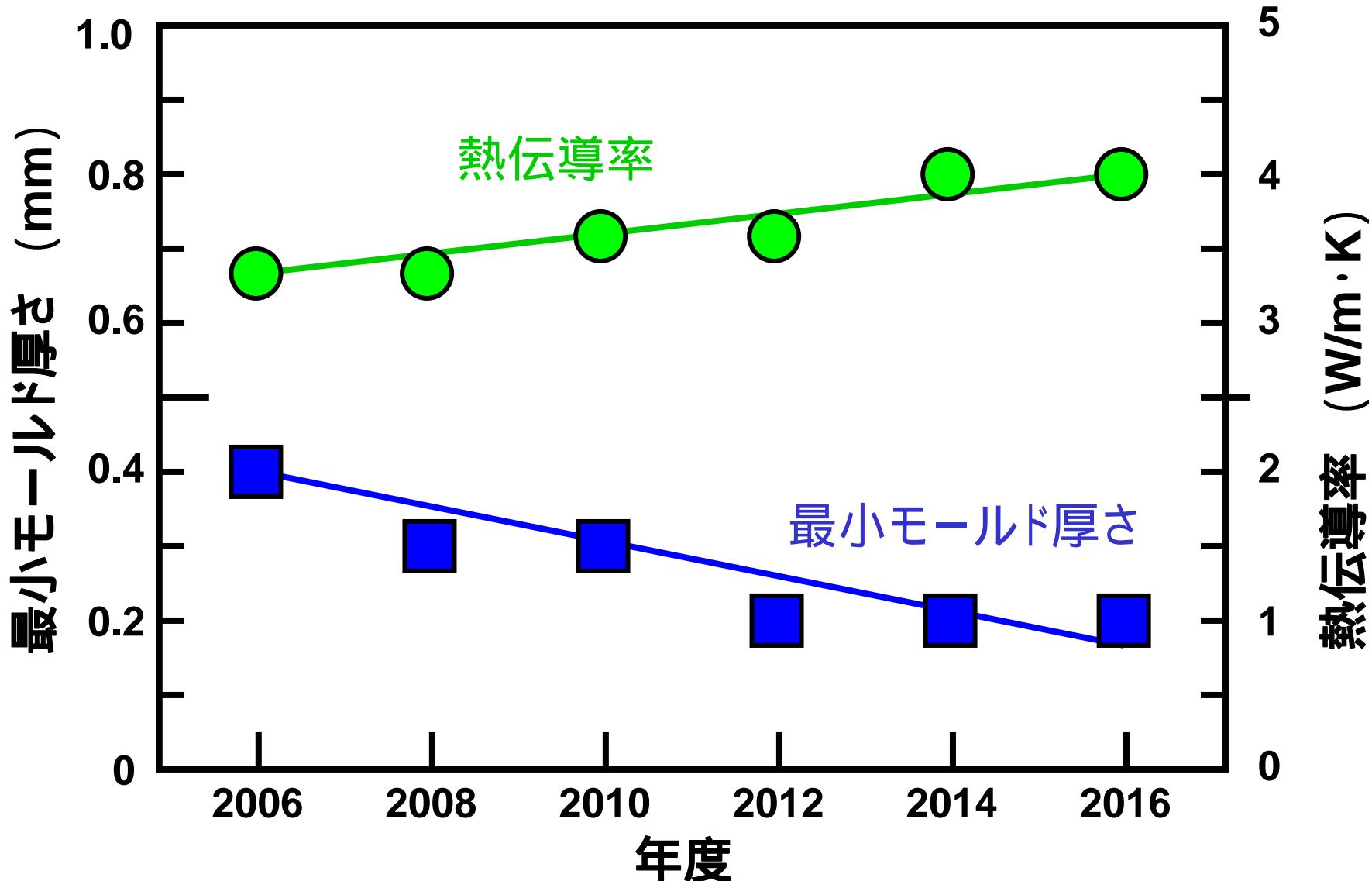

# 樹脂封止技術

# 樹脂封止技術の課題

- 高充填化・ボイドレス化

- ・高流動性、低粘度化、真空モールド etc.

- 低ワイヤ流れ

- ・低粘度化、コンプレッションモールド etc.

- 大面積化

- 低反りレジン

- ・低収縮率、低熱膨張係数 etc.

- 低応力レジン

- ・Low-k材対応、低弾性率 etc.

- 高熱伝導化

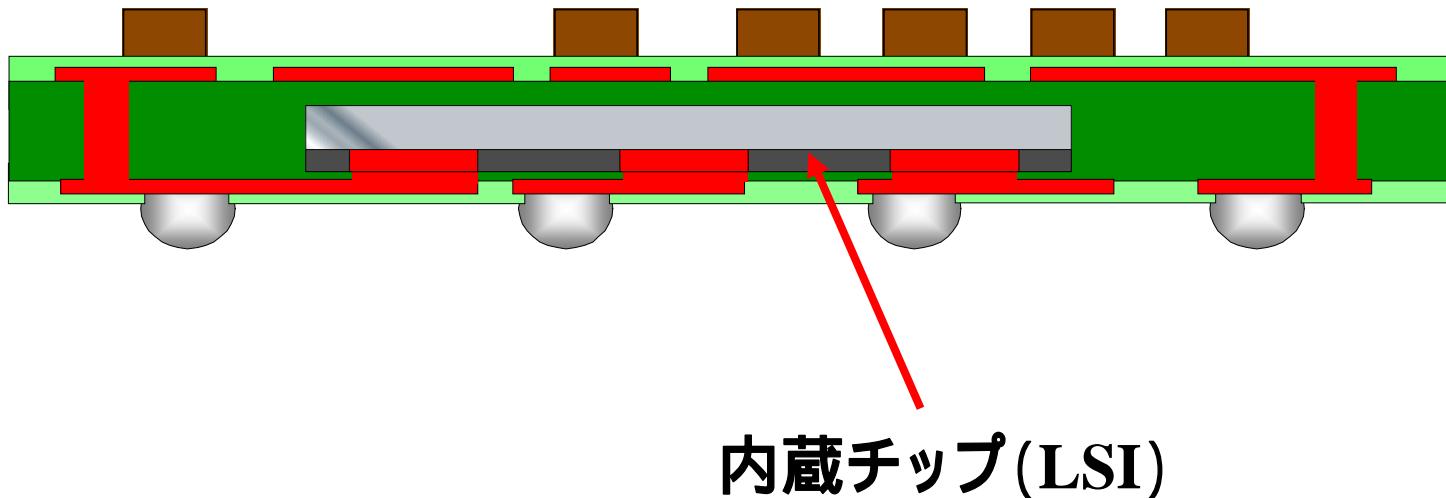

# 能動部品内蔵基板技術

- ・LSI内蔵基板の量産化開始(一部)

- ・LSI内蔵基板のSiPへの展開が今後進む

# SiP/MCPの今後の課題

## ■ KGD

- ・特性と信頼性が保証されたチップの供給

## ■ 極薄チップのハンドリングと多層積層化技術

## ■ 高放熱技術

- ・多数チップによる発熱を如何に放熱するか？

## ■ テスト・解析技術

- ・システムとしてのテストと不良チップの解析

## ■ インターポーヴ(サブストレート)

- ・部品内蔵サブストレート

- ・微細接続に対応した安価なシリコン基板