# DFT(テスト設計)とATE(テスト装置)との融合 品質とコストの両立する テスト技術ロードマップに向けて

WG2(テスト)リーダ·西村安正 (株)ルネサステク/ロジ

DFT: Design for Testability ATE: Automatic Test Equipment

## 報告のアウトライン

- 1,2006年度活動メンバ

- 2.ITRSのテストWG

- 3.DFTサブWG活動

- 4.ATEサブWG活動

- 5,2006年度活動まとめ

## 1.2006年度活動メンバ

\*: 2006年 交替、新任

<DFTサプ>

委員: 江守道明(富士通)、内田亘(ルネサス)\*、小林拓也(松下)

中村芳行(NECエレ)\*、牛久保政憲(沖・サブリーダ)

正田剛史(ソニーLSI) \*、安藏顕一(東芝)

平野正樹(ローム・幹事)

特別委員: 佐藤康夫(日立·国際担当)、畠山一実(STARC)

<ATEサプ>

**委員: 島林和彦(富士通)\*、西村安正(ルネサス・リーダ)**

前川道生(松下・サブリーダ)、田村智昭(NECエレ)\*、

五十殿宏二(シャープ)\*、渡邉均(セイコーエプソン・幹事)

伊藤修一(東芝)\*

特別委員: 多田哲生(徳島文理大)、木村伸一(アドバン) \*

山崎光夫(シバソク・国際担当)、江口光一(日本マイクロニクス)

相吉克彦(東京エレクトロン)、佐藤正幸(GTI)、鈴木宏叔(浜松ホト)

堀部久夫(日本エンジニアリング)、高溝久明(横河電機)\*

高橋弘行(アドバン) \*、大里衛知(日本マイクロニクス) \*

DFT: Design for Testability、テストのことを考えた設計

ATE: Automatic Test Equipment、大型テスタ他テスト装置全般の呼称

DFM: Design for Manufacturing、製造のことを考えた設計

WLBI: Wafer Level Burn-In、ウエー八を一括して加速度テスト(バーンイン) すること

オーバーキル: 実動作と無関係なテストの為のテスト等による歩留り悪化

スキャンBIST: スキャンBuilt in Self Test、チップ内蔵のスキャン手法のセルフテスト

BOST: Built Out Self Test、テスタの計測機能を補完する為にテスト・ボード上に搭載したもの

KTD: Known Tested Die、電気的テストしたことを保証するダイ

KGD: Known Good Die、信頼性を含めて保証されたダイ

TAT: Turn Around Time、ある仕事が完了するまでに要する工期

シリアルATA: Serial Advanced Technology Attachment、ATAはANSI(アメリカ標準化機構)で

規格化が進んでいるIDE(ハードディスクインターフェースのひとつ)の正式な規格

HDMI: High Definition Multimedia Interface、高品位テレビ(HDTV)とマルチチャネルオーディオを

一つのコネクタとケーブルに統合するコンシューマ製品向けインターフェイス

DDR2: Double Data Rate 2、クロック周波数の2倍のデータレートで動作するメモリ

システマティック不良: 製造装置の不具合や性能限界が原因で発生する不良

パラメトリック不良: テスト条件(電圧、温度など)により発生する不良

Loop Back: タイミングテストの手法の一つで信号をループバックすることに因んだ呼称

PKG: Package、パッケージ 以下、パッケージの呼称(フルネームのみ記載)

TSOP: Thin Small outline Package

QFP: Quad Flat Package

**BGA:** Ball Grid Array

FBGA: Fine pitch Ball Grid Array

CSP: Chip Scale Package

## 2. ITRSのテストWG

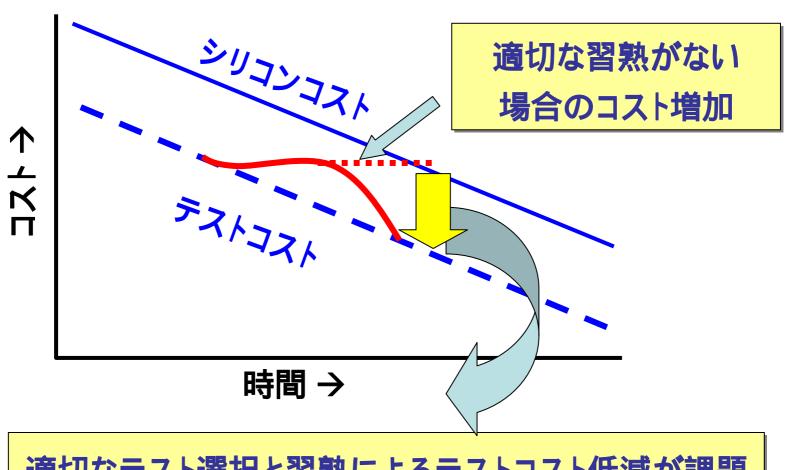

ITRS2006でのテスト課題

新デバイスにおける開発初期でのテストコスト増加

適切なテスト選択と習熟によるテストコスト低減が課題

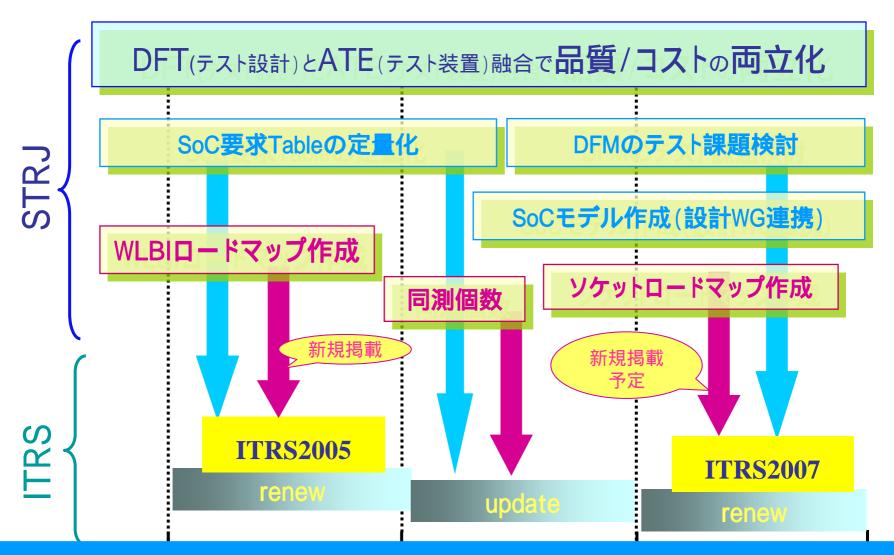

## STRJからの貢献 ~ DFT & ATE ~

STRJからのメッセージ(テストへの意識改革)

回路オーバーヘッド(必要悪) から DFTエリア・インヴェスメント(価値源泉) へ

# 3. DFTサブWG活動

SoCテストの技術課題を見直し、読者(EDAベンダなど)が 容易に理解できる実践的なロードマップ作成、同時に ITRS2006/2007へ貢献

## 検討項目

SoCテストの課題

\*テスト品質・歩留・信頼性

\*テスト設計生産性

DFT技術課題抽出用SoCモデル

SoCテストの課題 SoCモデル

勉強会/合宿 設計WG(WG1)と連携

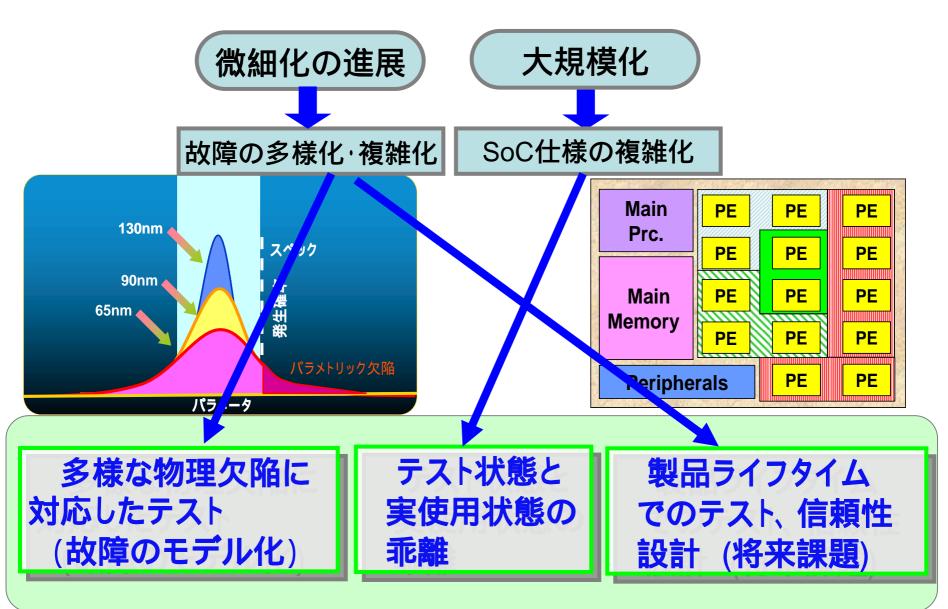

## SoCテスト

### < 背景 >

## プロセスの微細化

- ・欠陥の多様化

- ・故障発生率の増加

- メテスト設計生産性低下

- × テストコスト増加

- ×テスト品質と歩留低下

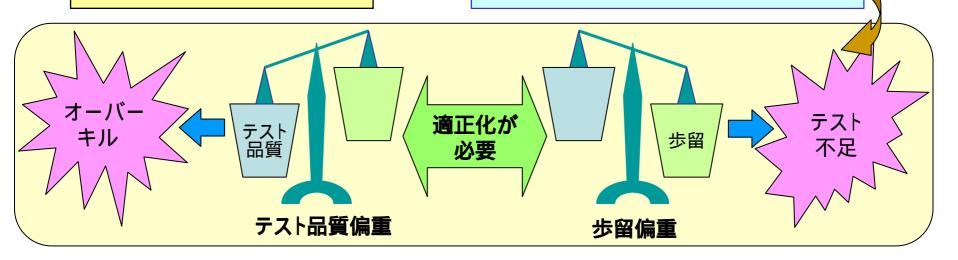

## テスト品質・歩留・信頼性

製品ごとの要求に合わせた適正化が課題

大規模・微細化に対応した技術の掘下げが必要

## テスト品質・歩留・信頼性の課題

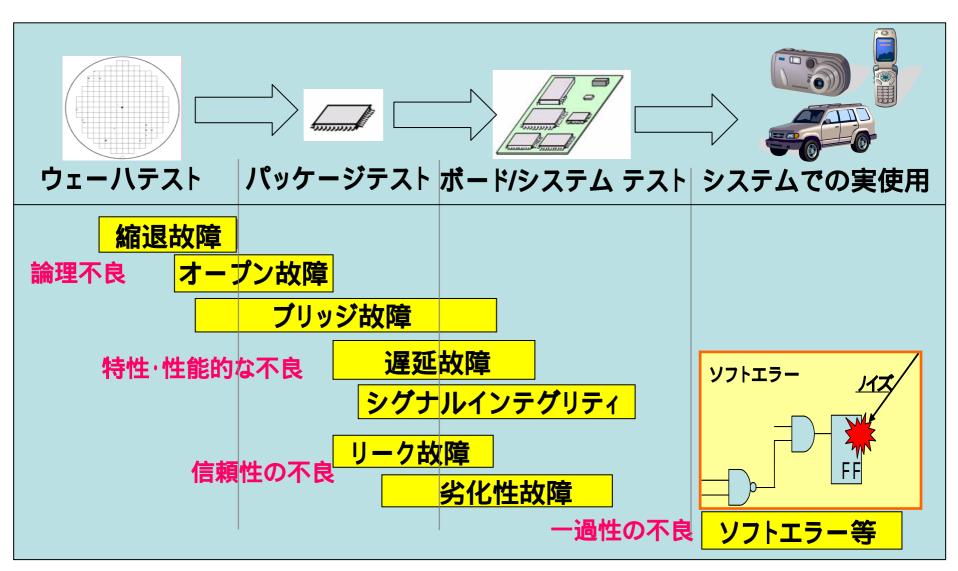

## 多様な物理欠陥に対応したテスト(故障のモデル化)

### 複数の拡張故障モデルによる総合的なテスト品質指標の確立

実際の物理的欠陥による不良動作

クロストーク / ノイズ オープン / ショート

乖離が増大

- \* 故障モデルで想定していない不良の見逃し

- \* 故障検出率とテスト品質が必ずしも一致しない

システマティック不良 パラメトリック不良

論理的な故障モデル

- ・縮退故障モデル

- ·遷移遅延故障モデル etc.

故障モデルの拡張

拡張された故障モデルの要件

- ・レイアウトの考慮

- ・回路情報の考慮

- ・統計的手法への対応

不良除去効果と故障検出率の乖離 = 新たなテスト品質指標

新たな品質指標の要件

- ・故障密度の考慮

- ・計算機負荷の抑制

Work in Progress - Do not publish

STRJ WS: March 9, 2007, WG2 Test

## テスト状態と実使用状態の乖離

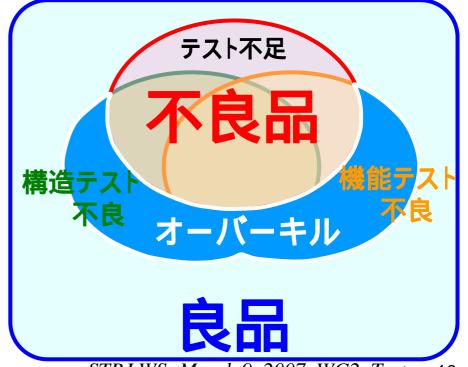

## 構造テスト/機能テストと良品/不良品の関係

| テスト種別                    | テスト対象                                    | 問題·懸念点                                     |

|--------------------------|------------------------------------------|--------------------------------------------|

| 構造テスト<br>(スキャン、<br>BIST) | テスト動作<br>(主として、<br>製造不良)                 | テスト起因の<br>オーバーキル<br>一例:<br>テスト時の<br>動作電流増大 |

| 機能テスト                    | 機能動作<br>(実使用状態<br>に近い:<br>製造不良、<br>設計不良) | テスト人手作成<br>による工数増大<br>カバレッジ定義無<br>(品質予測低下) |

## 製品ライフタイムでのテスト、信頼性設計

## SoCの信頼性向上:製品のライフタイム全体を考慮

# 4.ATEサブWG活動

将来課題の共有とポテンシャルソリューション検討で、 コストと品質を踏えたテスト技術ロードマップ作成、 同時に ITRS2006/2007 へ貢献

検討項目

同測個数精查

SiPテスト 高速IOテスト ソケットロードマップ ディスプレイドライバ テスト開発の経済性

課題の共有 ソリューション検討 勉強会/合宿 WG内/WG外アンケート

#### Work in Progress - Do not publish

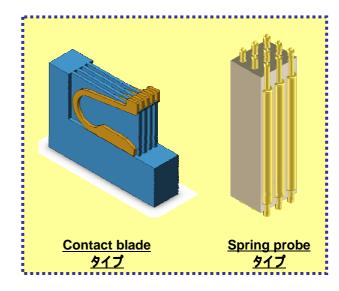

## ソケットロードマップ

## STRI

#### <背景>

\*コンタクト技術(ソケット)はテストの基本であり、且つ、ITRSから要望のあった テストソケットロードマップをSEAJ検査WGと連携で検討

\*ITRS台湾(昨年12月)で提案を行いITRS2007に新規掲載で合意

PKGタイプ·アプリケーションに使用される主コンタクタータイプ

| PKGタイプ   | アプリケーション        | コンタクタータイプ            |

|----------|-----------------|----------------------|

| TSOP     | Flash (NAND)    | Contact blade        |

| QFP      | SoC (ASSP/ASIC) | 検討中                  |

| BGA      | DRAM            | Spring probe         |

|          | Flash (NOR)     | 検討中                  |

|          | SoC             | Spring probe (50ohm) |

| FBGA/CSP | DRAM            | 検討中                  |

|          | SoC             | 検討中                  |

#### 一例)BGA – SoC – Spring probe (50 ohm) のロードマップ

| 1/0/                       | opinio (o          |       |       |       |        |        |        |        |        |

|----------------------------|--------------------|-------|-------|-------|--------|--------|--------|--------|--------|

| Table26: Logic (High volum | ne microprocessor) | 2006  | 2007  | 2008  | 2009   | 2010   | 2013   | 2016   | 2019   |

| PKG Pitch                  | (mm)               | 0.8   | 0.8   | 0.8   | 0.8    | 0.65   | 0.65   | 0.5    | 0.5    |

| PKG Pin count              |                    | 2,600 | 2,600 | 2,800 | 2,800  | 3,000  | 3,600  | 4.200  | 4,200  |

| PKG I/O data rate          | (GT/s)             | 0.1-6 | 0.1-6 | 0.1-6 | 0.2-12 | 0.2-12 | 0.2-15 | 0.2-20 | 0.2-40 |

| Spring probe (50 ohm)      |                    |       |       |       |        |        |        |        |        |

| Impedance                  | (ohm)              | 50    | 50    | 50    | 50     | 50     | 50     | 50     | 50     |

| Contact stroke             | (mm)               | 0.3   | 0.3   | 0.3   | 0.3    | 0.3    | 0.3    | 0.3    | 0.3    |

| Contact force              | (N)                | < 0.4 | < 0.4 | < 0.4 | < 0.4  | < 0.3  | < 0.3  | < 0.2  | < 0.2  |

| Contact resistance         | (mohm)             | 100   | 100   | 70    | 70     | 50     | 50     | 50     | 50     |

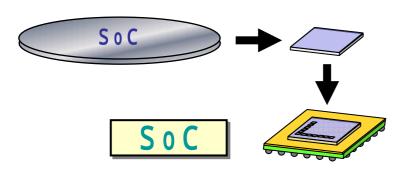

## SiPテスト

2005年度活動

DFT/ATE間でSiPテスト 課題を共有

#### 2006年度活動

具体的なSiPモデルを設定しテストコストと品質を考慮した課題マップ作成とソリューション検討を実施

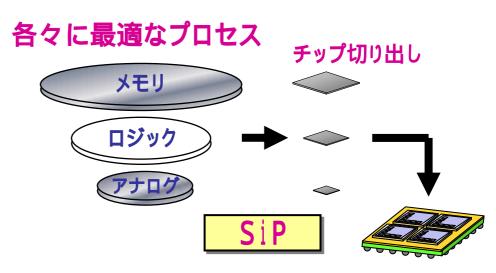

### 高集積 / 高性能 L S I を 実現する 2 つのアプローチ 混載プロセス

## 【テストからみたSoCとSiP】

- \*1つのチップに全ての機能を集積

- \*チップコスト大

- \*統一思想でのテスト設計が容易

- \* 各構成要素に最適なプロセスでチップ化後、 1つのパッケージに集積

- \*実装コスト大 KGD,KTD(チップレベルでの品質保証)必要 コスト低減のテスト戦略がより重要

どんなテスタで測定したらいいの? 高速IOはどう測ったらいいの? 他社チップ相互間のDFT?

コスト

同測は可能? 低コストで実現可能? KGDでもテスト必要? 品質とコストの トレード・オフ 必要!

品質

チップメーカはKGD/KTDで どこまで保証して〈れるの? KGDなら大丈夫? どうやって解析するの?

SiPテスト坊や

### 【具体的SiPモデル(DSC)】

DSC: Digital Still Camera

|           | 構成要素                         | 特徴                                           | l l l l l l l l l l l l l l l l l l l |

|-----------|------------------------------|----------------------------------------------|---------------------------------------|

|           | CPU                          | 高速                                           | 32bit RISC                            |

|           | Graphic Engine<br>User Logic | 10Mピクセル                                      | Logic                                 |

| <u>Si</u> | Memory                       | CCDデータ取り込み<br>CCDデータ補正、圧縮                    | 100Mbit 強                             |

| _         | AD Converter                 | Sensor Analog Digital 変換                     | 16bit ADC                             |

| <u> </u>  | Motor Driver                 | 高速モーター駆動                                     | Driver                                |

| SiP モデル   | Data Bus                     | CCDデータ転送 SoC Core<br>画像データ転送 内部DRAM<br>ストレージ | Serial / parallel Interface           |

|           | Serial Data Bus              | USBデータ転送 PC、Printer                          | Serial / parallel Interface           |

|           | Monitor Driver               | Monitor Data転送<br>Cameraモニタ                  | Serial Interface<br>LCD Driver        |

|           | Analog Data Output           | Video出力(NTSC、PAL)                            | Analog AMP                            |

|           | Power Management             | 待機状態/動作状態<br>ストロボ充電                          | Detector / Regulator<br>Analog SW     |

### 具体的モデルを想定し 課題を深堀

# 品質/コストへの影響をマップ化

| DSC対応            |                       | ATE      |                       |           |     |         |     |  |

|------------------|-----------------------|----------|-----------------------|-----------|-----|---------|-----|--|

|                  |                       | High End |                       | Mid Range |     | Low End |     |  |

|                  | SiP IP                |          | コスト                   | 品質        | コスト | 品質      | コスト |  |

|                  | CPU 32bit RISC        | 0        | X                     | 0         | 0   | ×       | _   |  |

| Lagio            |                       |          | ×                     | 0         | Δ   | Δ       | 0   |  |

| Logic            | □ 品質的には               | 「りだれ     | ) <b>Y</b>   <u>×</u> | 0         | Δ   | 0       | 0   |  |

|                  |                       |          |                       | 0         | Δ   | 0       | 0   |  |

|                  | いま コスト的に 7            |          | <b>X</b> ×            | 0         | 0   | Δ       | 0   |  |

| Memory           | DRA                   |          | ×                     | 0         | Δ   | Δ       | 0   |  |

|                  | Flash                 |          | ×                     | Δ         | Δ   | Δ       | 0   |  |

|                  | ADC                   | 0        | ×                     | 0         | Δ   | ×       | _   |  |

|                  | DAC                   | 0        | ×                     | 0         | Δ   | ×       | _   |  |

|                  | AMP                   | 0        | ×                     | 0         | Δ   | ×       | _   |  |

| Analog           | Sencer AMP(~uV Range) | Δ        | ×                     |           |     |         | _   |  |

|                  | Digital AMP           | 0        | ×                     | 0         | 品質的 | に不可     | 0   |  |

|                  | Video/Audio AMP       | 0        | ×                     |           | 7   |         |     |  |

|                  | PLL                   | 0        | ×                     |           |     | ×       | _   |  |

|                  | Parallel I/F =<500MHz | 0        | ×                     | 0/        | U   | Δ       | 0   |  |

|                  | 500MHz - 1.5GHz       | 0        | ×                     | Х         | _   | ×       | _   |  |

| High Speed I/F   | Over 1.5GHz           | Δ        | ×                     | X         | -   | ×       | _   |  |

| riigii opeed i/i | Serial I/F =<500MHz   | 0        | X                     | 0         | 0   | Δ       | 0   |  |

|                  | 500MHz – 3GHz         | 0        | X                     | ×         | _   | ×       | _   |  |

|                  | Over OGHz             | 0        | X                     | Х         | -   | ×       | _   |  |

| Power Control    | Regulator             | Δ        | X                     | Δ         | Δ   | Δ       | 0   |  |

| 1 OWEL COLLINI   | Analog Switch         | Δ        | X                     | Δ         | Δ   | Δ       | 0   |  |

|     | 充分な精度でテストができる | 0 |

|-----|---------------|---|

| 品質  | 精度は劣るがテストができる | Δ |

|     | 技術的にテストは行えない  | × |

|     | コスト的に充分である    | 0 |

| コスト | 満足はしないが許容できる  | Δ |

|     | 量産には使えない      | × |

高速I/FのテストをMid Range ATEで 如何に実現するかが最大の課題

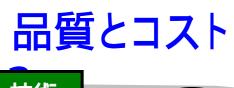

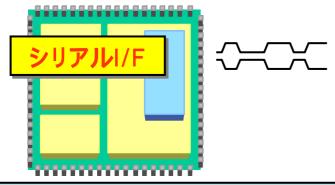

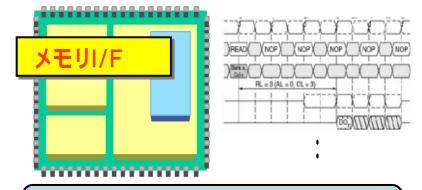

## 高速 I/Fテスト

### 【高速!/Fの種類(大別)】

- ・シリアルATA, HDMI, USB2.0,etc

- · 少ピン/小振幅/超高速~6.4Gbps

- ·DDR2, DDR3,etc

- ·比較的多ピン/高速~1.0Gbps

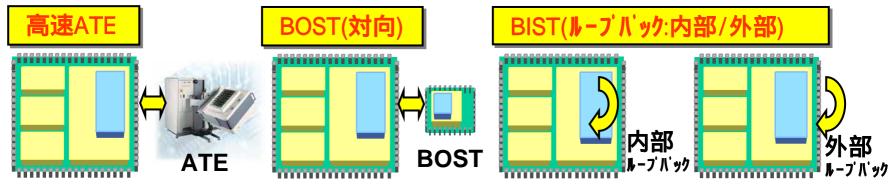

### 【高速I/Fの代表的なテスト手法と特徴】

- ·高品質

- ·解析容易

- ·高価(設備/治具)

- ·限定品質

- ·解析困難

- ·安価(設備)

- ·限定品質

- ·解析困難

- ·安価(設備/治具)

- ・ウェール検査容易

- ·限定品質

- ·解析困難

- ·安価(設備)

## 品質とコスト

## STRI

#### 触強会(レベル合わせ) シリアルATA, DDR2

#### ソリューション毎に量産テストにおける 技術/コスト/品質/TAT/解析性を検討

|                          |                   |                  |              |          |                    |          |             | $\overline{}$ |  |

|--------------------------|-------------------|------------------|--------------|----------|--------------------|----------|-------------|---------------|--|

|                          |                   | ATE<br>Mid Range |              |          |                    |          |             | ATE不使用        |  |

|                          |                   |                  |              |          |                    |          |             |               |  |

|                          |                   | High End         | BOST<br>(対向) | 外部計測器    | BIST<br>(ルーフ゜ハ゛ック) | 実機と2パス   | 計測器<br>PC制御 | 実機元計          |  |

| ウェーハで出来るか?(超高速,小振幅,ジッタ等) |                   | ×(治具起因)          | ×(治具起因)      | ×(治具起因)  | 〇(制約あり)            | ×        | ×           | ×             |  |

|                          | 量産コスト(時間)         | ×                | 0            | Δ        | 0                  | ×        | ∆or×        | 0             |  |

|                          | 投資コスト(装置)         | ×                | 0            | 0        | 0                  | 0        | 0           | 0             |  |

|                          | テストブログラム/バターン開発   | 0                | 0            | 0        | 0                  | 0        | 0           | 0             |  |

| コスト面                     | テストボード開発          | ×                | ×            | ×        | 0                  | ×        | ×           | Δ             |  |

|                          | ブローブカード,ソケット開発    | ×                | ×            | ×        | 0                  | ×        | ×           | ×             |  |

|                          | 設計負担/オーバーヘッド      | 0                | 0            | 0        | ×                  | 0        | 0           | 0             |  |

| TAT面                     | (テスト開発のTAT)       | 0                | ×            | 0        | 0                  | 0        | 0           | 0             |  |

| 品質面                      |                   | 0                |              | 0        |                    | 0        | ×           | ×             |  |

| 解析(不良時                   | の故障個所絞込み、歩留向上のため) | 0                | Δ            | 0        | ×                  | ×        | Δ           | ×             |  |

| 測定システムの汎用性               |                   | 0                | Δ            | 0        | 0                  | X        | 0           | ×             |  |

| ブローブカードへの要求              |                   | €speed動作         | espeed動作     | €speed動作 | _                  | espeed動作 | espeed動作    | espeed動作      |  |

| ソケットへの                   | ノケットへの要求          |                  | espeed動作     | espeed動作 | espeed動作           | espeed動作 | espeed動作    | espeed動作      |  |

| 備考                       |                   |                  |              |          | 送受信前提              |          |             |               |  |

**★ジッタ付加、レベルシフト等によるスクリーニングマージン確保手法の確立が必要**

品質・コスト・工程上の制約などにより 適切な量産テスト手法を選択

例 \*KGD保証を行う場合 BIST(内部ループバック)が有効

\*投資額/量産コストを最小化

BOST(特に送信/受信が片方向のみ対応の場合)

BIST(設計負担が許容できる場合)

## サブWG活動まとめ

#### DFT

#### SoCテストについて技術課題の抽出整理

- ~ テスト品質・歩留・信頼性を重点的に検討 ~

- 多様な物理欠陥に対応したテスト

- テスト状態と実使用状態の乖離

- 製品ライフタイムでのテスト、信頼性設計

#### 他WGとの連携開始

WG1と連携しSoCモデルを基にDFT技術課題議論

#### ATE

ITRS2007へ新規掲載するソケットロードマップのドラフト案作成 SiPテストについて技術課題と品質/コストへの影響をマップ化

- テスト対象モデルをDSCに技術課題抽出整理

- 各種(High End、Mid Range、Low End) ATEでのテスト実現可否議論

高速 I/Fテストについて量産における課題とソリューション案整理

- 量産テスト適用ATE対応で技術/品質/コスト/TAT/解析性議論

- 高速I/FのテストをMid Range ATEで如何に実現するかが最大の課題

# 5.2006年度活動まとめ

DFT(テスト設計)とATE(テスト装置)との融合

~ 品質とコストの両立する

テスト技術ロードマップ ~ に向け

月一度の会合と秋合宿、及び、勉強会を通し、メンバ間で

SoCテスト、SiP/高速IOテスト、テスト経済性の課題に

対する深堀と共有化を達成

ITRS2006への貢献

- DFTより、SoC要求Tableの定量値プラッシュアップ

- ATEより、同測個数プラッシュアップ

2007年度WG2活動へ

## テストの役割

テスト分析 デバッグ

システム欠陥

步留習熟

テスト(WG2)

テスト考慮設計

実動作条件

(電力、タイミング etc)

欠陥情報

(構造、頻度)

テスト分析 故障解析

プロセス欠陥

步留習熟

設計(WG1) 設計TF

> 低電力SoCモデルで 議論開始中

歩留向上(WG11) モデリング(WG10)

> 故障診断の活用で 今後相談予定

## LCDドライバICロードマップ(大型TV用)調査アンケート

| NO. 項目                    | 2006           | 2007         | 2008             | 2009        | 2012    | 2015       | 2020          |

|---------------------------|----------------|--------------|------------------|-------------|---------|------------|---------------|

| 1 プロセス ルール 2 ウェーハサイズ      |                |              |                  |             |         |            |               |

| 3 出力ピン数(生)                |                |              |                  |             | 7       |            |               |

| 5 総ピ JEIT                 | A(ST           | RJ-WG        | 2)/SE            | AJ(特別       | 委員)     |            |               |

| 6 7                       |                |              |                  |             |         |            |               |

| j                         | 里携の・           | 一環で          | デバイス             | ス動向部        | 問查      |            |               |

| (第二楼                      | 終 <b>見</b> 月1月 | スアン          | ケート              | を行な         | いましか    | <u> </u>   |               |

| (オューリ                     | 変 夫  Cd        | トロナン         |                  | 7 1 J / A   | V 12 01 | <b>C</b> 0 |               |

| ご協力」                      | 買いた方           | つにご          | なめて後             | 『礼申し        | 上げま     | す。         |               |

|                           | <b>+</b> 11    | <b>大学レニ・</b> | ا رتب            | E1 #        |         |            | $\mathcal{A}$ |

| 16                        | のリ             | がとう          | _ <b>C</b> l l a | <b>にした。</b> |         |            |               |

| 18 デ 引続                   | きのご            | 支援を          | お願い              | 申し上げ        | ずます。    |            |               |

| 19 パッケー><br>20 テープ厚(TCP:> |                |              |                  |             |         |            |               |

| 21 ファンクション試験方法            |                |              |                  |             |         |            |               |

| 22   出力電性試験力法             |                |              |                  |             |         |            |               |

アンケート集計結果は活動報告書に記載