# EUVは間に合うか、

それともトリプルパターンニングか? ー リソグラフィ技術の最新動向 ー

WG5 (リソグラフィ Working Group) 富士通セミコンダクター(株) 千々松 達夫

#### 一内容一

- ◆WG5の活動体制

- ◆EUVか、トリプルパターニングか

- ◆その他のトピックス

- ◆まとめ

# WG5(リソグラフィWG)の活動体制

#### 一JEITA半導体部会/関連会社-

- ■千々松達夫/リーダー(富士通セミコンダウター)

- ■上澤史且/サブリーダー(ソニー)

- ■田村貴央(ルネサスエレクトロニクス)

- ■東川巌(東芝)

- ■和田恵治(ローム)

- ■山本次朗(日立製作所)

- ■笹子勝 (パナソニック)

#### ーコンソーシアムー

■須賀治(EIDEC)

#### -SEAJ 他-

- ■奥村正彦/国際委員(SEAJ:ニコン)

- ■高橋和弘(SEAJ:キヤノン)

- ■中島英男(SEAJ:TEL)

- ■山口哲男(SEAJ:ニューフレアテクノロジー)

- ■笠間邦彦(SEAJ:ウシオ電機)

- ■大久保靖(HOYA)

- ■林直也(大日本印刷)

- ■森本博明(凸版印刷)

- ■大森克実(東京応化工業)

- ■栗原啓志郎(アライアンスコア)

#### 計18名

### STRJ-WG5活動状況

- ◆ITRS 2012 update/ITRS 2013改訂に向けた取り組み

- ●各テーブルの見直し

- ●Potential Solutionsテーブルの見直し

- ●新規DSA Tableへの対応を議論

- ◆NGL進捗確認 (学会発表等の最新状況を参加委員から報告)

- ●EUVL開発状況

- ・ 光源パワー、マスクインフラ、レジスト開発

- → 光リソからEUVLへの移行時期の見極め

- ●その他の露光技術(ML2, Imprint, DSA)の動向確認

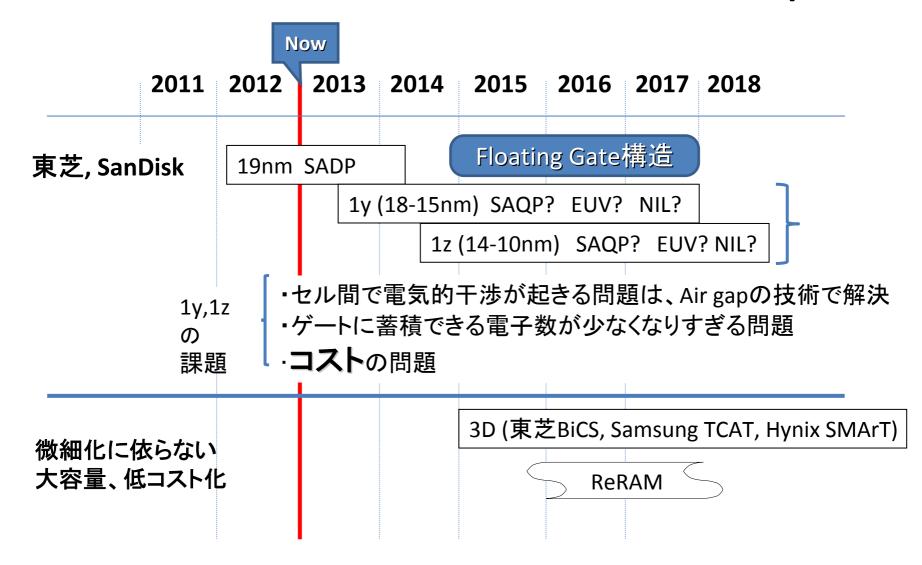

### NANDフラッシュ

#### Micro SDカード

現在、SDカードで128GB, μSDカードで64GBのものが販売されている。

### 2年弱で、半値に!

#### SD-MF032G [32GB] の 価格推移グラフ

いかに安く作るか?が重要

# NANDで量産適用されている技術

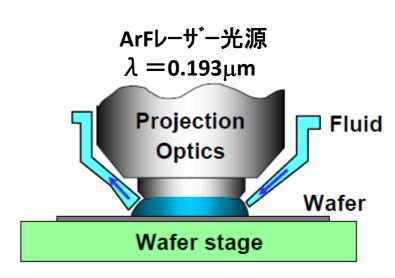

解像限界 =

$$0.25 \times \frac{\lambda}{NA}$$

$$= 0.25 \times \frac{0.193}{1.35}$$

$= 0.036 (\mu m)$

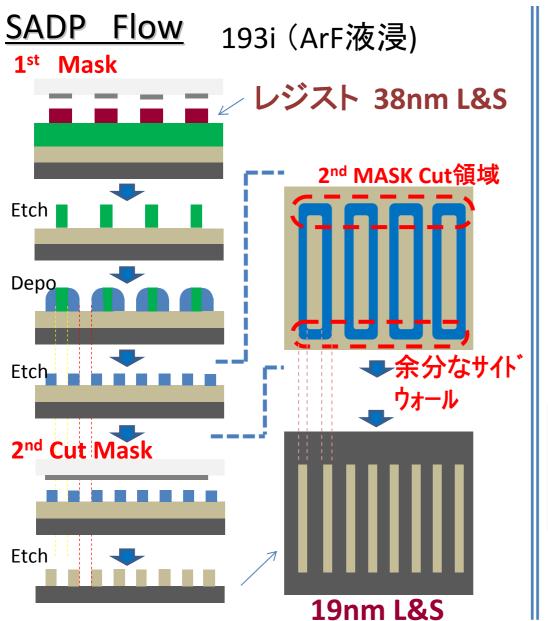

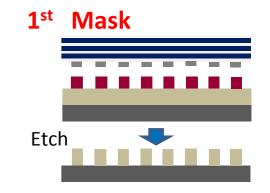

リソのマージンを考慮すると、ArF液浸での解像限界は 38nm×ラインアンドスペース。

次のSlideのSelf Aligned Double Patterning(SADP)で、19nmラインアンドスペースまで、形成可能。

**※ LOGIC デバイス(2Dランダム形状)では、**45nmライン&スへ<sup>®</sup>ース前後か。 SMOやネガティブ現像技術で、もう少し頑張れるか? 先端突き合わせ部が困難。

# SADPは19nmハーフピッチが限界

EUVL Flow  $\lambda = 13.5$ nm NA = 0.32

EUVLが使えれば、 単純なリソ/エッチングエ 程で、製造できる。

# 19nm以下のパターンを液浸で形成するために STRD は、トリプルパターニングが必要

**Flow** EUVL Flow  $\lambda = 13.5$ nm (Self Aligned Quadruple Patterning) NA = 0.5Mask レジスト 38nm L&S 1<sup>st</sup> Mask Depo Etch Etch Depo **Ftch** SADPを繰り返す事によって Etch 10nm hpまで可能だが工程 **3rd Cut Mask** 数が多い。 チップサイズ縮小による単 2<sup>nd</sup> Cut Mask 価削減に見合うかどうかが Etch Etch Key

STRJ WS: March 8, 2013, WG5 Litho

Work in Progress - Do not publish

8

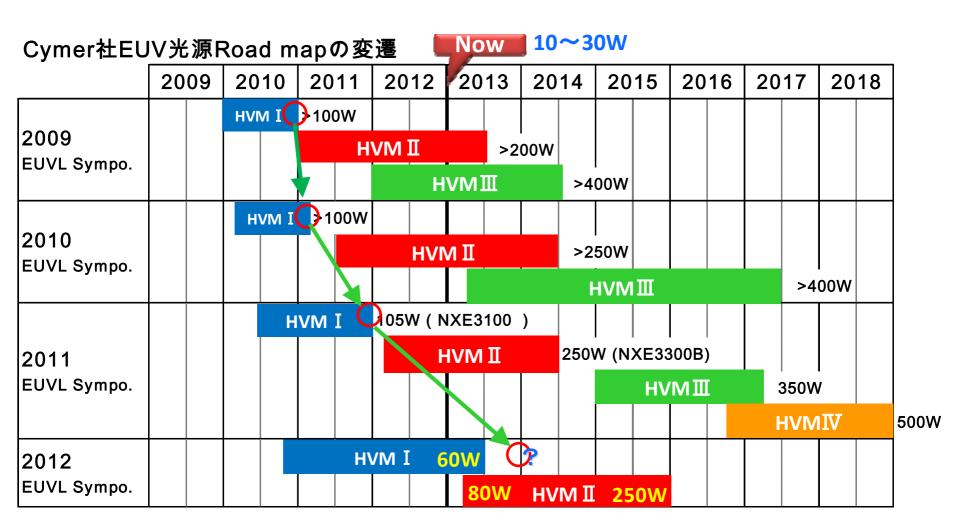

# EUVLの大きな課題

1. 光源の出力 計画通りに進んでいない

- 2. 無欠陥マスク

- ■EUV波長の検査機の登場はこれから

- 多層膜の欠陥が0にならない

- 3. レジストの解像力、感度、LER まだ、両立せず

### EUV光源の状況

#### <u>露光機のスペック</u>

| 年                      | 2011     | 2012      | 2013      |

|------------------------|----------|-----------|-----------|

|                        | NXE:3100 | NXE:3300B | NXE:3300C |

| スループット(wph)            | 60       | 125       | 150       |

| 光源ハ <sup>°</sup> ワー(W) | 105      | 250       | 350       |

|                        | プレ量産機    | 量産機       |           |

#### 光源パワーの現状

1時間に5~6枚

125wphを実現するには、 25台の露光装置が必要

● LPP, LDP光源とも、現状のパワーは10W程度(NXE:3100)

● LPP光源:Cymer = 40W、Gigaphoton=20W。

実験機レベル

● LDP光源: Xtreme= 45W

LPP: Laser Produced Plasma

LDP: Laser assisted Discharge Plasma

一番の問題は、予定通りに向上しないこと。

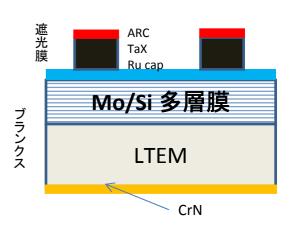

### EUVマスク開発状況

■ ブランクスにおいて、LTEM(ガラス基板)のPit欠陥は抑えられる。

しかし、<u>多層膜の欠陥を減らす事</u>ができていない。

現状では、欠陥の真上に遮光膜が来るようにして回避するしかない。

■ EUV波長の検査装置が登場するのは、今年(2013年)。

新たな欠陥(種)が見えてくる可能性も有り。

EUVマスクの断面構造

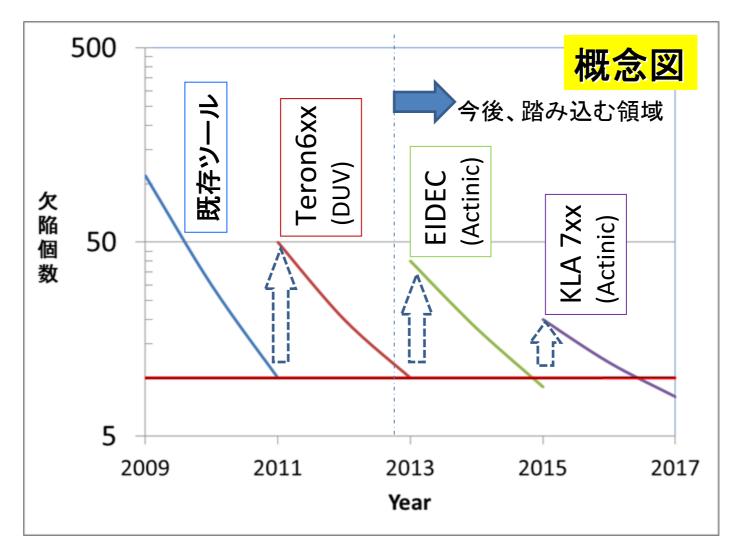

# EUV Mask欠陥検査装置開発状況

#### 量産対応装置のリリース時期

■ ブランクス欠陥検査(EUV)

Lasertec / EIDEC: 2013 (16nmhp)

KLA : 2015 (11nmhp)

■ 転写性レビュー検査(EUV AIMS) (Aerial Image Measurement System)

Zeiss/Sematech: 3Q.2014(NA0.3)

■ マスクパターン欠陥検査

(EB) Ebara/EIDEC : 2014(16nmhp)

HMI, AMAT

(EUV) KLA : 4Q.2015

▶ 現状は既存の欠陥装置(DUV光源)とウエーハ転写/検査で開発が進められている。

# 欠陥検査ツールが進化すると、見えていたいなかったものが見えてくる。

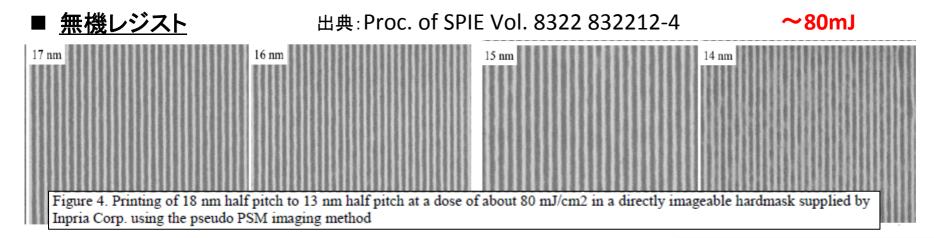

### EUVレジスト開発状況

Figure 4. Ultimate resolution data of recent progress (NA0.3, Pseudo PSM)

感度の悪い点が問題

# Logicデバイス各社の微細化road map

|        |                                                   | N        | low                                          |                   |                    |                 |                |                     |        |

|--------|---------------------------------------------------|----------|----------------------------------------------|-------------------|--------------------|-----------------|----------------|---------------------|--------|

|        | 2011                                              | 2012     | 2013 201                                     | 4 2015            | 2016               | 2017            | 2018           |                     |        |

|        | 22n                                               | m: FINFE | T, M1=p <b>90</b> ni                         | <b>n</b> , M2,3=p | 80nm 193           | i <b>single</b> | pat.           |                     |        |

| Intel  |                                                   |          | 14nm: Fl                                     | NFET(Bulk         | ), M1= <b>p6</b> 4 | <b>lnm</b> ?,   | 193i <b>d</b>  | <b>louble</b> pat.  |        |

|        |                                                   |          |                                              | 10                | Dnm: <i>詳細</i>     | ???             |                |                     |        |

| TCNAC  |                                                   |          | 20nm: Plane                                  | r, M1= <b>p6</b>  | <b>4nm</b> ,193i   | double          | pat.           |                     |        |

| TSMC   |                                                   |          | 16nm: FINFET, BEOLは、20nmと同じ。M1= <b>p64nm</b> |                   |                    |                 |                |                     |        |

|        |                                                   |          |                                              |                   | 10nm : 🖺           | <b>詳細???</b> ?  | ° М1= <b>р</b> | <b>44nm</b> ?? do   | ouble? |

| Global |                                                   |          | 20nm: Plane                                  | r, M1= <b>p6</b>  | <b>4nm</b> ,193i ( | double          | e pat.         |                     |        |

| Found  | Foundry 14nm: FINFET, BEOLは、20nmと同じ。M1= <b>p6</b> |          |                                              |                   |                    |                 |                |                     |        |

|        |                                                   |          |                                              | 1                 | 0nm: <i>詳細</i> :   | ???M1           | =p <b>44</b> r | <b>nm</b> ?? double | e?     |

### 最近の情報

# 2013/2/5 Common Platform Technology Forum (IBM, Global Foundry, Samsung)

While everyone agrees <u>EUV</u> will be necessary sometime in the future, it is taking longer to develop and facing more issues than expected. Now it isn't likely to be used <u>until 7nm production</u> or even later.

M1 16nm hp???

2017? 2018?

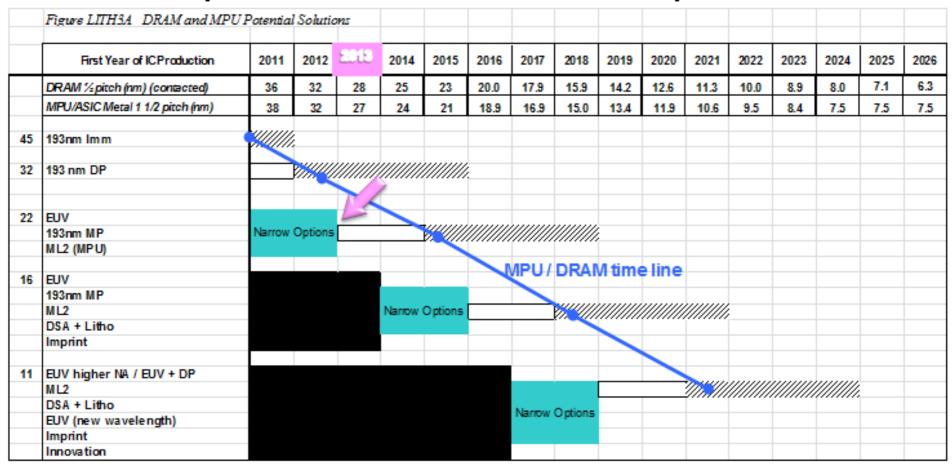

#### Updated MPU/DRAM Options

We will narrow options for 22nm hp in 2013.

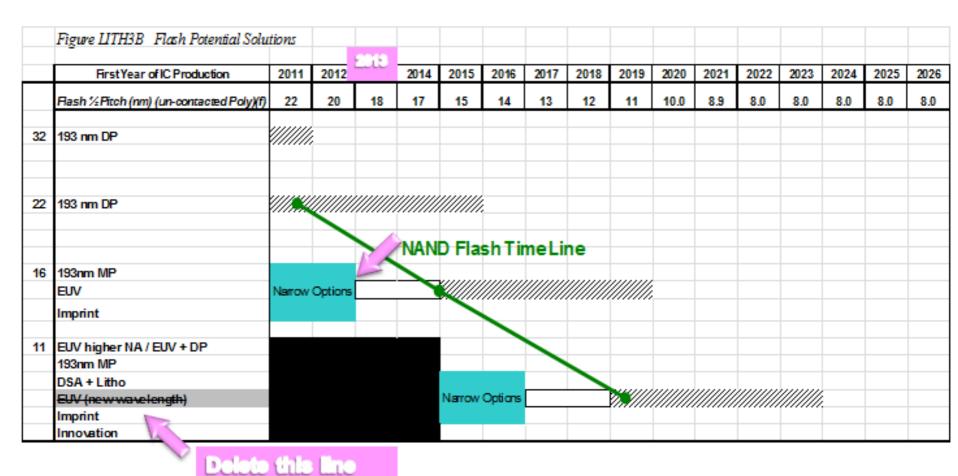

# NAND Flashの微細化road map

### 昨年の情報

#### 2012/7/27 Korean IT news

"If ASML develops the equipment without delays and Samsung Electronics and SK Hynix adopt EUV equipment according to their schedule, the era of 10-nano memory semiconductors will begin next year. EUV equipment will be applied to NAND flash and is anticipated to be adopted for **DRAM** in the future," said a source of the industry. In order to use EUV lithography in actual production, it should be able to treat more than 60 wafers an hour. This is a challenge that ASML has to overcome in developing EUV lithography. NXE3100で105W出れば、使うぞというメッセージか。

### Updated Flash Options

This table shows the requirements for 2-D flash development. The potential introduction of 3-D flash does not drive lithography.

Notes: from 2016 3dimensional solutions with lower resolution will have to be considered, which implies solutions from earlier nodes.

※100Wが出てくるはずのタイミングを○で示した。

### EUVは間に合うか、

### それともトリプルパターンニングか?

現時点のEUV光源出力、これまでの進捗から判断すると、

NANDフラッシュ **16nm**-hp, <u>DRAM Logic</u> **22nm**-hpに用いる

リソグラフィー技術は、ArF液浸。

NAND: SAQP トリプルパターニング

LOGIC: LELEダブルか、(Cutマスクを含む)トリプルか。

<u>懸念点</u>: 工程(マスク)数の増大に対して、コストへの影響。 レイアウト設計が複雑になること。これもコスト増の要因に なる。

EUVは、光源出力が上がれば、11nm-hp NAND, 16nm-hp DRAM, Logicへ適用か。

Work in Progress - Do not publish STRJ WS: March 8, 2013, WG5 Litho

**1**22

# その他のトピックス

# さらなる微細化に向けて(1) EUV

必要

入射角度を大きくできない。MASK倍率と

| Shotサイ | くズの             | 見直し | が  |

|--------|-----------------|-----|----|

| 311017 | / <b>/</b> \//. | 兀巴! | ノル |

| 波長 | 13.5  | nm /      | NXE3 | 100 | NXE  | 3300 | Sho    | tサイズ |

|----|-------|-----------|------|-----|------|------|--------|------|

|    | hp/NA | $\bigvee$ | 0.25 | \   | 0.32 | 0.5  | 0.7    | 0.85 |

|    | 32    |           | 0.59 |     | 0.76 | 1.19 | 1.66   | 2.01 |

|    | 22    |           | 0.41 |     | 0.52 | 0.81 | 1.14   | 1.39 |

|    | [16   |           | 0.30 |     | 0.38 | 0.59 | 0.83   | 1.01 |

|    | 11    |           | 0.20 |     | 0.26 | 0.41 | 0.57   | 0.69 |

|    | 8     |           | 0.15 |     | 0.19 | 0.30 | / 0.41 | 0.50 |

|    | 6     |           | 0.11 |     | 0.14 | 0.22 | , 0.31 | 0.38 |

波長

短波長化

**6.7** nm

| hp/NA |    | 0.25 | 0.35 | 0.45          | 0.65 | 0.85 |

|-------|----|------|------|---------------|------|------|

|       | 22 | 0.82 | 1.15 | <u>/</u> 1.48 | 2.13 | 2.79 |

|       | 16 | 0.60 | 0.84 | / 1.07        | 1.55 | 2.03 |

|       | 11 | 0.41 | 0.57 | 0.74          | 1.07 | 1.40 |

|       | 8  | 0.30 | 0.42 | 0.54          | 0.78 | 1.01 |

|       | 6  | 0.22 | 0.31 | 0.40          | 0.58 | 0.76 |

|       | 4  | 0.15 | 0.21 | 0.27          | 0.39 | 0.51 |

|       | 3  | 0.11 | 0.16 | 0.20          | 0.29 | 0.38 |

'19 NAND 11nmには、 間に合わ ないだろう。

**Opportunity**

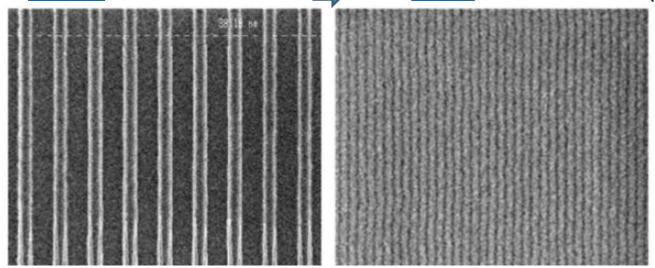

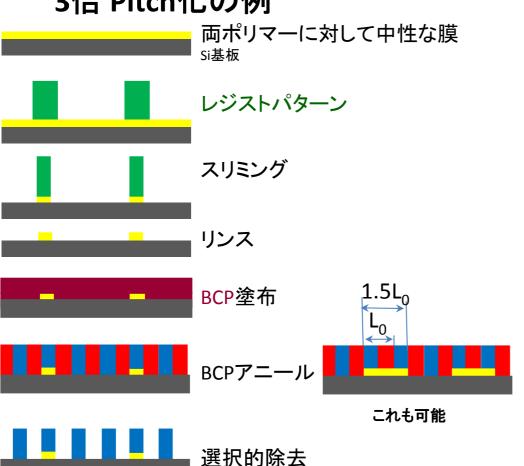

# さらなる微細化に向けて(2) DSA

#### <u>Directed-Self-Assembly Lithography</u>

PS-PMMA( $\chi$ =0.04)では、pitch 12nm-hpが可能。 PS-PDMS ( $\chi$ =0.26)では、pitch 9nm-hpが可能。

χ:相互作用のパラメータ

Pitch 100nmのレジストパターン Pitch 25nm のDSAパターン(PS-PMMA)

出典: J. Micro/Nanolith. MEMS MOEMS 11(3), 031302 (July-Sept 2012)

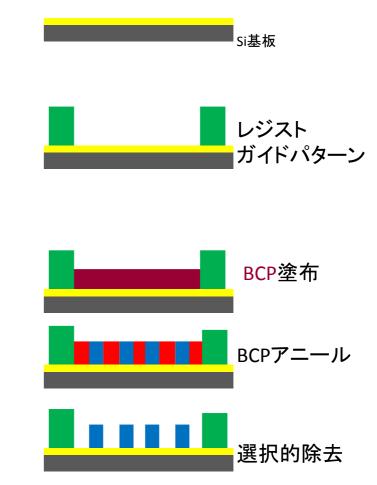

### DSA(Directed-Self-Assembly)リソ プロセスフロー

#### ■ <u>ケモエピタキシー法</u> 3倍 Pitch化の例

#### ■ <u>グラフォエピタキシー法</u>

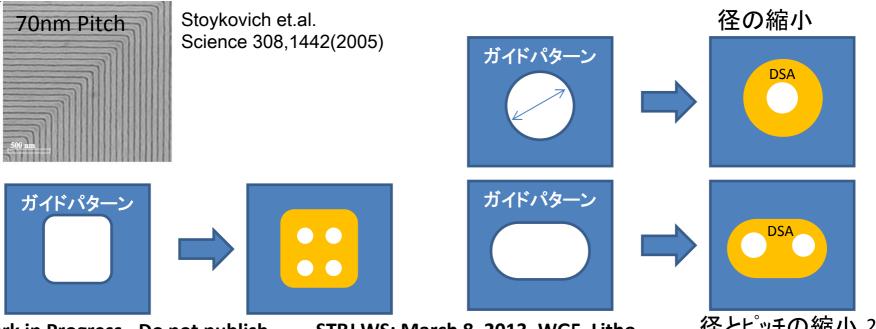

## DSA(Directed-Self-Assembly)リソ 応用例

- ケモエピタキシー法は、ラインパターンの3~6倍ピッチ化への応用が期待できる。

- 密なL字パターンは、di-block copolymerに、各ホモPolymerをブレンドすれば形成できる。(下の写真)

- その他の形状も、いろいろと検討されている。

- グラフォエピタキシー法は、ホール調整(rectification:縮小等)への応用が期待できる。

- 多少、ガイドパターンの径がばらついていても、ばらつきの小さいDSA径が出来る可能性あり。

#### L字パターンの例

Work in Progress - Do not publish

STRJ WS: March 8, 2013, WG5 Litho

径とピッチの縮小 27

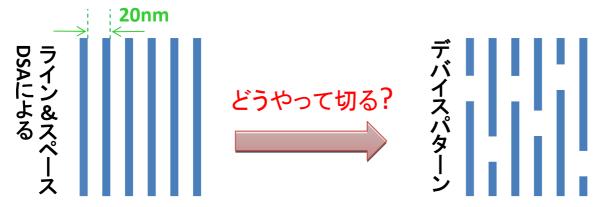

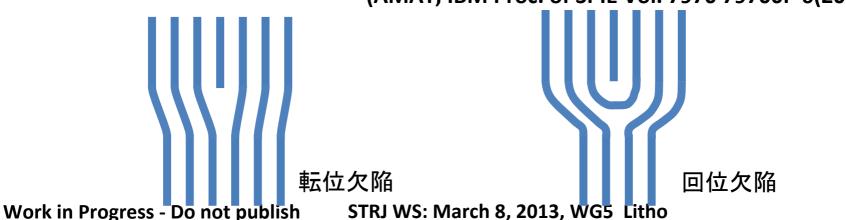

### DSAリソの課題

- ■大きな課題は、

- DSA固有欠陥のないこと (転位、回位欠陥)

- 設計ルール (特に、ライン系の倍Pitch化への適用時)

■ 12nm hp L&S での欠陥評価として、(多めに見積もって) < 26個/cm² という報告があり。

(AMAT, IBM Proc. of SPIE Vol. 7970 79700F-6(2011)

### DSA Table for 2013 ITRS (案)

| Table LITH3C DSA Capability                                                                           |      |      |      |      |      |      |      |      |      |      |

|-------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|

| Year of Production                                                                                    | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 |

| DRAM ½ pitch (nm) (contacted) values from row 4, LITH2                                                |      |      |      |      | 22.5 | 20.0 | 17.9 | 16   | 14   | 13   |

| Flash ½ pitch (nm) (un-contacted poly), values from row 13, LITH2                                     |      |      |      |      | 15.5 | 14.2 | 13.0 | 12   | 11   | 10   |

| LITH2                                                                                                 |      |      |      |      | 21.2 | 18.9 | 16.9 | 15   | 13   | 12   |

| MPU gate in resist length (nm) values from row 21, LITH2                                              |      |      |      |      | 22.2 | 19.8 | 17.7 | 16   | 14   | 12   |

| Defects in patterned resist films, gates, contacts, etc. (#/cm2), values from line 17, Table Lith3A   |      |      |      |      | 0.01 | 0.01 | 0.01 | 0.01 | 0.01 | 0.01 |

| Patterning layer thickness (nm)                                                                       |      |      |      |      |      |      |      | 4    |      |      |

| Resist meets requirements minimum feature CD control (nm. 3 sigma)<br>values from Lith3A, line 10     |      |      |      |      | 1.7  | 1.6  | 1.5  | 1.3  | 1.2  | 1.1  |

| CD uniformity (nm, 3 sigma), contact/vias [G]<br>values from table Lith4, line25                      |      |      |      |      | 1.5  | 1.5  | 1.5  | 1.5  | 1.5  | 1.5  |

| Registration (nm,3 sigma)**                                                                           |      |      |      |      |      |      |      |      |      |      |

| Minimum defect size in patterned DSA (nm)                                                             |      |      |      |      |      |      |      |      |      |      |

| Low frequency line width roughness*: (nm, 3 sigma) values from<br>LITH3A, line 19                     |      |      |      |      | 1.8  | 1.6  | 1.4  | 1.3  | 1.1  | 1.0  |

| Backside particle density (particles/cm²) values from LITH3A, line 13                                 |      |      |      |      | 0.28 | 0.28 | 0.28 | 0.28 | 0.28 | 0.28 |

| Back surface particle diameter: lithography and measurement tools (nm)<br>Values from LITH3A, line 14 |      |      |      |      | 75   | 50   | 50   | 50   | 50   | 50   |

| Defects in spin-coated resist films (#cm²) † values from LITH3A, line<br>IS                           |      |      |      |      | 0.01 | 0.01 | 0.01 | 0.01 | 0.01 | 0.01 |

| Minimum defect size in spin-coated resist films (nm) values from<br>LITH3A. line 16                   |      |      |      |      | 10   | 10   | 10   | 10   | 10   | 10   |

|                                         |      |      |           | 2274      |           |           |           |           |           |           |

|-----------------------------------------|------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Year of Production                      | 2011 | 2012 | 2013      | 2014      | 2015      | 2016      | 2017      | 2018      | 2019      | 2020      |

| DRAM/ MPU/ ASIC (M1) ½ pitch (nm)       | 36   | 20   | 28        | 0.5       | 23        | -00       | 40        | 40        | 44        | 42        |

| (contacted)                             | 30   | 32   | 20        | <u>25</u> | 23        | <u>20</u> | <u>18</u> | <u>16</u> | 14        | <u>13</u> |

| DRAM CD control (3 sigma) (nm)          | 3.7  | 3.3  | 2.9       | 2.6       | 2.3       | 2.1       | 1.9       | 1.7       | 1.5       | 1.3       |

| Flash ½ pitch (nm) (un-contacted poly)  | 22   | 20   | <u>18</u> | <u>17</u> | <u>15</u> | 14        | <u>13</u> | <u>12</u> | <u>11</u> | <u>10</u> |

| MPU/ASIC Metal 1 (M1) ½ Pitch           | 38   | 32   | 27        | 24        | 2.7       | 19        | 17        | 15        | 13        | 12        |

| (nm)(contacted)                         | 30   | 32   | 27        | 24        | 21        | 19        | 1/        | 13        | 13        | 12        |

| Gate CD control (etched) (3 sigma) (nm) | 2.5  | 2.3  | 2.1       | 1.9       | 1.7       | 1.6       | 1.5       | 1.3       | 1.2       | 1.1       |

| Overlay (3 sigma) (nm)                  | 7.6  | 6.4  | 5.4       | 4.8       | 4.2       | 3.8       | 3.4       | 3.0       | 2.7       | 2.4       |

LSIへの適用検 討が始まった ばかり。 2018年頃か?

| This section shows guide feature size based on | target CD  | and pitch | <u>multiplica</u> | tion factor |           |       |           |      |           |           |   |

|------------------------------------------------|------------|-----------|-------------------|-------------|-----------|-------|-----------|------|-----------|-----------|---|

|                                                |            |           |                   |             |           |       |           |      |           |           |   |

| DSA Based Density Multiplication for Dense Art | rays (Driv | en by NAN | D)                |             |           |       |           |      |           |           |   |

| Target CD (flash)                              | 22         | 20        | <u>18</u>         | <u>17</u>   | <u>15</u> | 14    | <u>13</u> | 12   | <u>11</u> | <u>10</u> | I |

| Target Pitch (ArF Immersion)                   |            |           |                   | 134.8       | 123.7     | 113.4 | 104.0     | 95.4 | 87.4      | 80.2      |   |

| Guide feature CD (chemoepitaxy) 1.5L 0         |            |           |                   | 50.6        | 46.4      | 42.5  | 39.0      | 35.8 | 32.8      | 30.1      | I |

| Guide feature CD (chemoepitaxy) 0.5L 0         |            |           |                   | 16.9        | 15.5      | 14.2  | 13.0      | 11.9 | 10.9      | 10.0      | Ī |

| Pitch Multiplication Factor [E]                |            |           |                   | 4X          | 4X        | 4X    | 4X        | 4X   | 4X        | 4X        | I |

|                                                |            |           |                   |             |           |       |           |      |           |           |   |

|                                                |            |           |                   |             |           |       |           |      |           |           |   |

ホール形成へ の適用が最初 か。

|     | This section shows guide feature requirements |  |  |  |  |  |

|-----|-----------------------------------------------|--|--|--|--|--|

|     | Guide Pattern CD Control (nm, 3 sigma)        |  |  |  |  |  |

|     | LWR of Guide Pattern (nm, 3 sigma)            |  |  |  |  |  |

|     | Defects in guide pattern (#/cm²)              |  |  |  |  |  |

| 14/ | Minimum defect size in guide-pattern (nm)     |  |  |  |  |  |

| VV  |                                               |  |  |  |  |  |

### 450mm化の対応

| Table LITH2 Lithography Technology Requi | rements   |           |           |           |      |             |             |        |      |

|------------------------------------------|-----------|-----------|-----------|-----------|------|-------------|-------------|--------|------|

| Year of Production                       | 2012      | 2013      | 2014      | 2015      | 2016 | 2017        | 2018        | 2019   | 2020 |

| DRAM ½ pitch (nm) (contacted)            | <u>32</u> | <u>28</u> | <u>25</u> | <u>23</u> | 20.0 | <u>17.9</u> | <u>15.9</u> | 14.2   | 12.6 |

| Flash ½ pitch (nm) (un-contacted poly)   | 20        | 18        | 17        | 15        | 14.2 | 13.0        | 11.9        | 10.9   | 10.0 |

| MDU(ASICMetal I (MI) 1/ pitch (mn)       | 22        | 27        | 24        | 24        | 12.0 | 16.0        | 15.0        | -124 - | 1449 |

| Wafer size (diameter, mm)                | 300       | 300       | 450       | 450       | 450  | 450         | 450         | 450    | 450  |

|                                          |           |           |           |           |      |             |             |        |      |

#### オランダ会議で、赤に修正した。

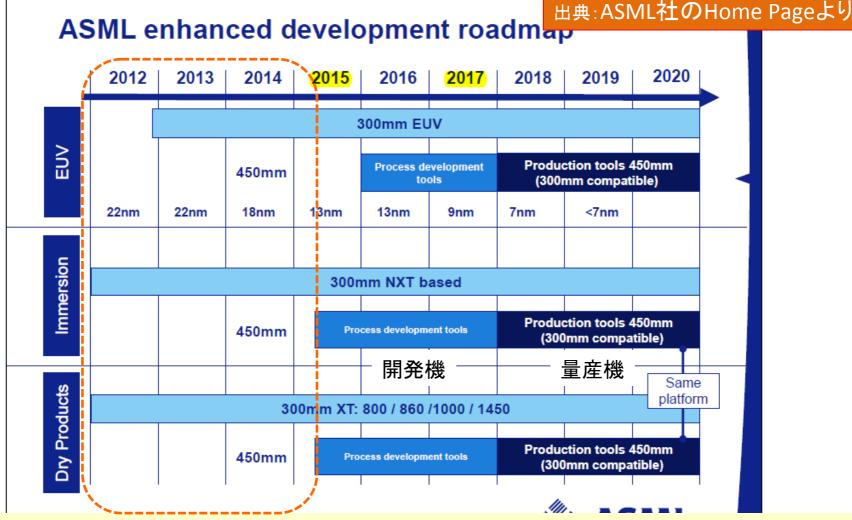

July.9 ASML 共同投資プログラムを発表(450mm対応装置、EUVL)

July.9 Intel 社、ASML社に総額\$4.1Bの投資(研究開発費、株式投資)

(7割が450mm化向け)

- Aug.6 TSMC社、ASML社に総額\$1.36Bの投資

- Aug.8 Intel社、ニコンに¥数百億の開発費提供

Aug.27 Samsung社、ASML社に総額\$0.95月24投資+\$6.4B(5,100億円)の資金

Work in Progress - Do not publish

STRJ WS: March 8, 2013, WG5 Litho

### 加速資金を得た結果のスケジュール

2012-14年は、空白状態。

Global 450 Consortium(G450C)は、昨年にNano Imprintの装置を導入して開発を進めている。NikonはArF露光機を17年に出荷予定。

### まとめ

- EUVL量産使用開始は、2015年。ただし、光源パワーが 目標値に近づかないとCost-effectiveにならない。

- DPTが量産適用されている。EUVL導入までに、MPTまで 延命適用される可能性が高い。 Cost-effectiveに出来るかどうかが鍵。

- 450mm化対応に向けて、露光機メーカにデバイスメーカーから開発資金が投入された。量産機のリリースは2017年から。

- STRJ-WG5として、今後もITRSロードマップ策定に貢献していく。

| AIMS  | Aerial Image Measurement System         |

|-------|-----------------------------------------|

| AMC   | Airborne Molecular Contamination        |

| ARC   | Anti-Reflection Coating                 |

| BARC  | Bottom ARC                              |

| TARC  | Top ARC                                 |

| CAR   | Chemical Amplified Resist               |

| CD    | Critical Dimension                      |

| CDU   | CD Uniformity                           |

| DE    | Double Exposure                         |

| DFM   | Design for Manufacturing/               |

|       | Design for Manufacturability            |

| DP/MP | Double Patterning / Multiple Patterning |

| DPP   | Discharged Produces Plasma              |

| DSA   | Directed-Self-Assembly                  |

| DOF   | Depth of Focus                          |

| EBDW  | Electron Beam Direct Writer             |

| EDA   | Electronic Design Automation            |

| EPL   | Electron Projection Lithography         |

| ESD   | Electro Static Discharge                |

| EUVL  | Extreme Ultraviolet Lithography         |

| IPL   | Ion Projection Lithography              |

| LDP   | Laser assisted Discharge Plasma         |

| LER   | Line Edge Roughness                     |

| LPP   | Laser Produced Plasma                   |

| LTEM  | Low Thermal Expansion Material          |

| LWR     | Line Width Roughness                  |

|---------|---------------------------------------|

| MEEF    | Mask Error Enhancement Factor (=MEF)  |

| ML2     | Maskless Lithography                  |

| NA      | Numerical Aperture                    |

| NGL     | Next Generation Lithography           |

| NIL     | NanoImprint Lithography               |

| NTD     | Negative Tone Development             |

| OAI     | Off-Axis Illumination                 |

| OPC     | Optical Proximity Corrections         |

| RBOPO   | C Rule Base OPC                       |

| MBOP    | C Model Base OPC                      |

| PSM     | Phase Shifting Mask                   |

| cPSM    | complementary PSM                     |

| APSM    | Alternating PSM                       |

| EPSM    | Embedded PSM                          |

| Att. PS | SM Attenuated PSM                     |

| PXL     | Proximity X-ray Lithography           |

| RET     | Resolution Enhancement Techniques     |

| SADP    | Self Aligned DP                       |

| SAQP    | Self Aligned Quadruple Patterning     |

| SB      | Scattering Bar (same meaning as SRAF) |

| SRAF    | Sub Resolution Assist Feature™        |

| SFIL    | Step & Flash Imprint Lithography      |

| UV-NIL  | Ultraviolet NIL                       |