### 小型・低コストパッケージとして実用化が始まるFO-WLP

2016年3月4日

WG7リーダ:杉崎吉昭(東芝)

- ■WG7の活動概要

- ■ファンアウト型パッケージ(FO-WLP)の動向

- ■FO-WLPの概要と課題

- ■各社製造プロセスの動向

- ■まとめと今後の活動方針

# 半導体パッケージのロードマップ活動

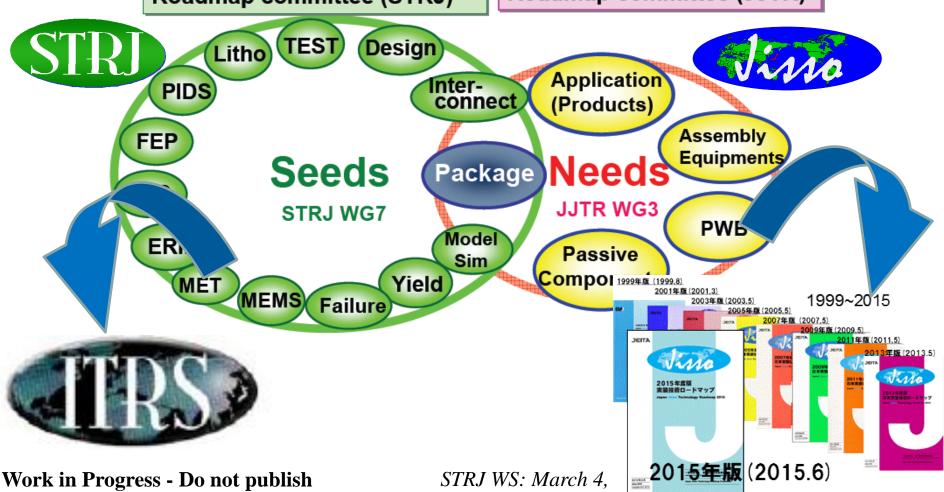

STRJ WG7(実装)は、電子機器セットのニーズと半導体技術のシーズの両面からロードマップを検討している

### 半導体技術ロードマップ

Semiconductor Technology Roadmap committee (STRJ)

### 日本実装技術ロードマップ

Japan Jisso Technology Roadmap committee (JJTR)

## 半導体パッケージのロードマップ活動

杉崎吉昭(東芝)

尾崎裕司(ソニー)

萩原靖久(ルネサスエレクトロニクス)

奥村弘守(ローム)

濱崎浩史(東芝)

藤木達広(ナミックス)

村松茂次(新光電気工業)

若林猛(HTL)

高橋守(旭硝子)

川内拓男(東京エレクトロン)

STRJ-WG7

リーダー

サブリーダー

委員

委員

委員

特別委員

特別委員

特別委員

特別委員

特別委員

JJTR-WG3

主査

副主査

委員

委員

委員

委員

特別委員

特別委員

オブザーバー

オブザーバー

### 9社10名

### 2015年度WG7活動実績

- **■** WG会議

- 12回(月例)

- ITRS2.0,JJTR2015対応の反省と次回以降に向けての情報収集

- ITRSとの国際会議

- 2回(5月、8月)

- ITRS2.0の議論

- 主要学会からの情報収集

- ECTC(5月)、IEDM(12月)

- JJTR各WGとのクロスカット

- プリント基板WG、メディカルヘルスケアアプリ検討TF(12月)

- 外部からの招待講演

- 8月:Yole Development(FO-WLP関連)

- 1月:新川、ヤマハ発動機(チップ搭載技術)

- 2月:富士機械(チップ搭載技術)、TDK(IC内蔵基板)

- 3月:AT&S(IC内蔵基板)

- 2016年度以降: TOWA、アピックヤマダ(樹脂封止技術)、芝浦メカトロニクス、東レエンジニアリング(チップ搭載技術)、オルボテック、オーク製作所(レーザダイレクト露光技術)

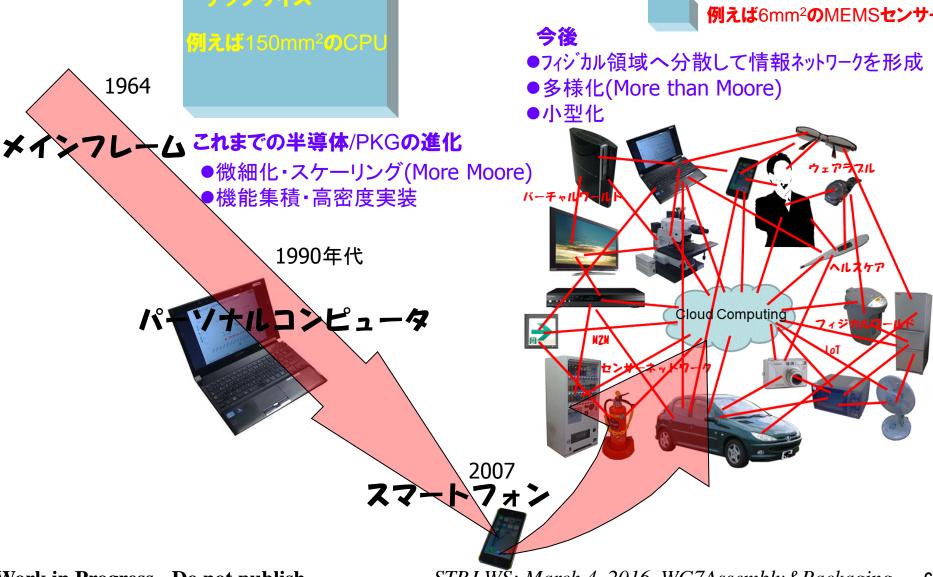

### WG7のフォーカス領域

フィジカル領域に分散される 小さくて安いPKG チップサイズ

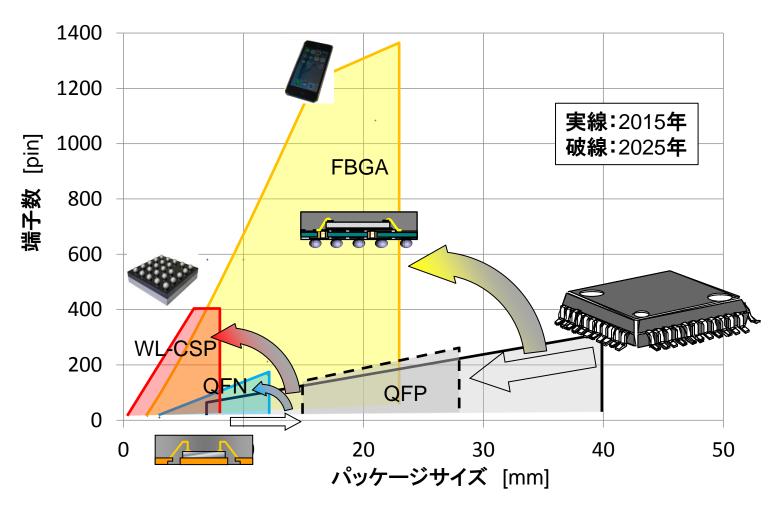

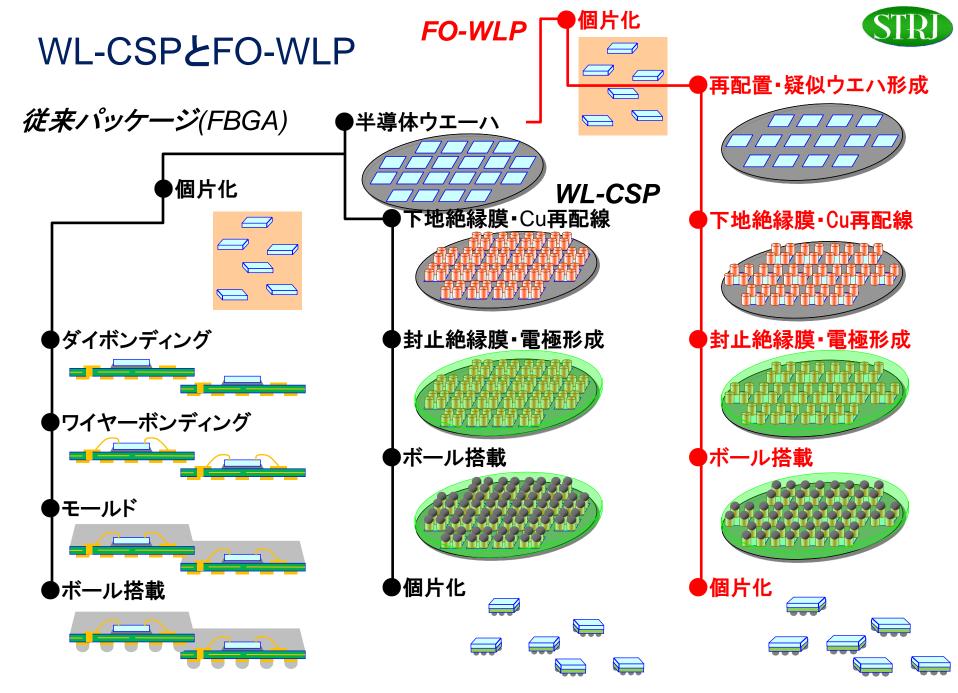

## 各種パッケージの位置付けと動向

- ■小型化・高速対応が困難なQFPは適用領域が狭まりつつある

- ■大チップ、多ピンは、FBGAへ移行

- ■小チップは、QFNやWL-CSPへ移行

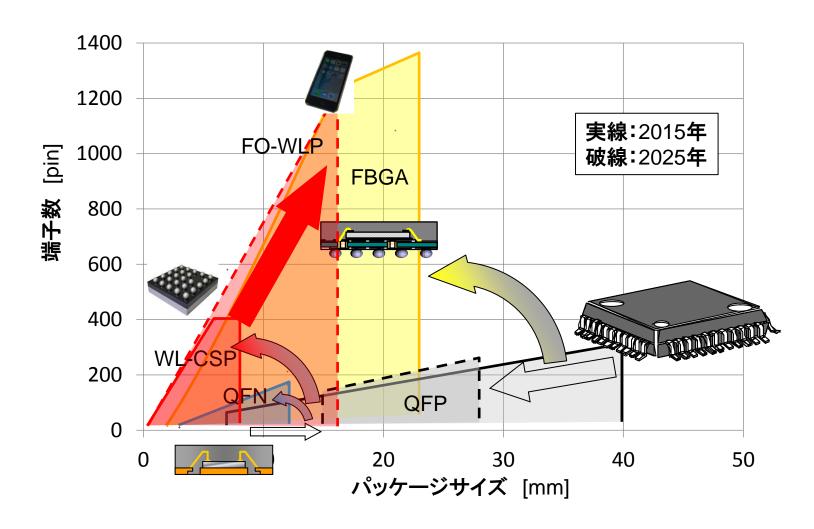

# 各種パッケージの位置付けと動向

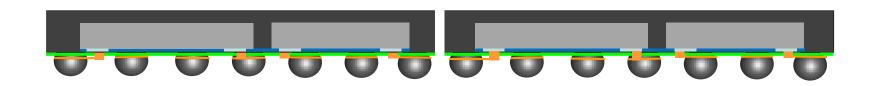

■小型用途のWL-CSPは、ファンアウト構造(F0-WLP)により、より他端子、大型へ適用範囲を拡大

### FO-WLPの特徴と課題

### ■ 特徴

- パッケージサイズがチップサイズより大きい

- 端子数の多いチップを狭ピッチにしなくても搭載できる

- チップシュリンクしてもパッケージサイズが変わらない

- パッケージサイズを標準化できる

- 複数のチップを混載可能

- ヘテロ集積(プロセス違い、ウエーハ径違い、Passive)

### ■ 課題

- 製造方法が百花繚乱

- Face-down/Face-up、Chip-1st/RDL-1st、流品外形(ウェハ、PWB)、基材

- チップ再配列

- スループット、位置精度

- 歩留り(平坦性、パーティクル)、信頼性(チップ端部の特異点)、

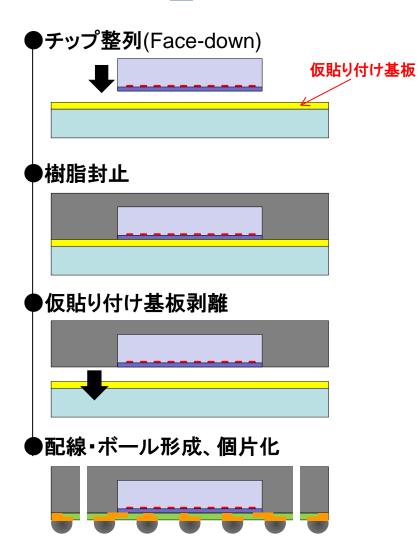

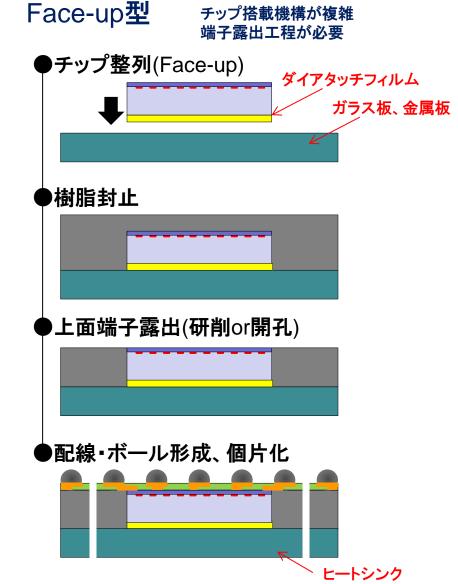

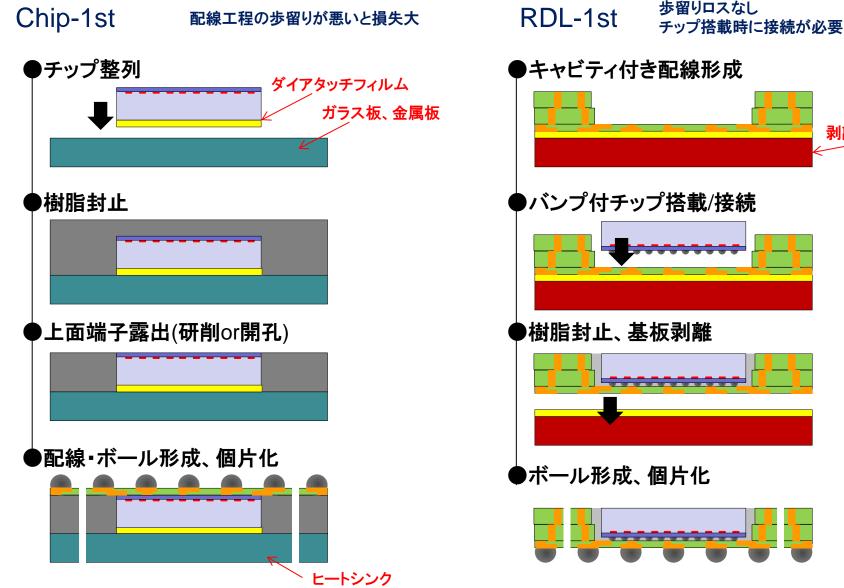

# チップ搭載方向の違い

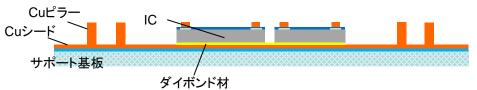

### Face-down型

剥離層付基板

## チップ搭載・配線形成の順番の違い

# 各社プロセスの比較(1)

Face down

Face up

Chip-1st RDL-1st Wafer外形 パネル外形

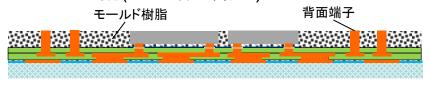

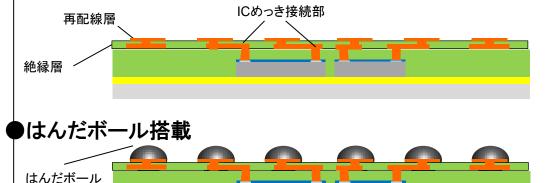

#### 始めに実用化が進んだ工法

IC仮固定材 サポート基板

設備

✓ ICマウンター

#### ▶樹脂モ―ルド(擬似ウェハ形成)

✓ モールド装置

#### **▶支持基板剥離**

▶絶縁膜形成、シード成膜、配線形成、シード剥離 x積層数

**海配線層**

#### ✓ 剥離装置

- ✓ コータ or ラミネータ

- ✓ 露光現像装置

- ✓ スパッタ

- ✓ 電解Cuめっき

- ✓ Wet

- ✓ ボール搭載機

- ✓ リフロ一炉

- ✓ ダイサー

#### ●はんだボール搭載

はんだボール

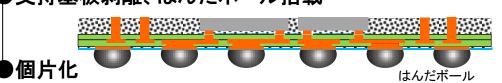

### ●個片化

# 各社プロセスの比較(2)

Face down Face up Chip-1st RDL-1st Wafer外形 パネル外形

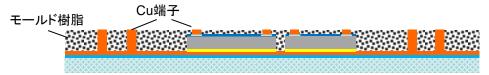

#### 多端子、ファインピッチ用途で台頭

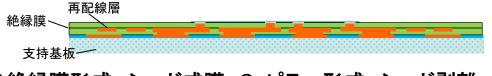

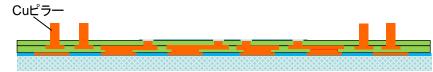

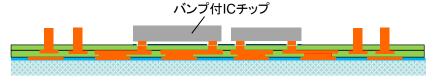

●Cuピラー形成、チップ再配列(Cuバンプ付、Face up)

●樹脂モ―ルド(擬似ウェハ形成)、研削Cu端子露出

▶絶縁膜形成、シード成膜、配線形成、シード剥離 x積層数

●支持基板剥離、はんだボール搭載

●研削(背面Cu端子露出)

●個片化

#### 設備

L/S=2/2um

- ✓ コータ or ラミネータ

- ✓ 露光現像装置

- ✓ 電解Cuめっき

- ✓ ICマウンター

- ✓ モールド装置

- ✓ バックサイドグラインダー

- ✓ コータ or ラミネータ

- ✓ 露光現像装置

- ✓ スパッタ

- ✓ 電解Cuめっき

- ✓ Wet

- ✓ ボール搭載機

- ✓ リフロ一炉

- ✓ 剥離装置

- ✓ バックサイドグラインダー

- ✓ ダイサー

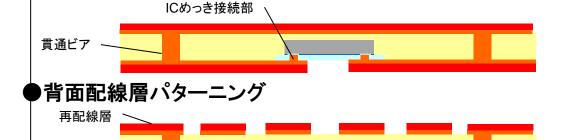

## 各社プロセスの比較(3)

Face down Face up

Chip-1st RDL-1st Wafer**外形** パネル外形

設備

**●絶縁膜形成、シード成膜、配線形成、シード剥離 x積層数**

前ページの対抗技術(多端子、ファインピッチ用途)

●絶縁膜形成、シード成膜、Cuピラー形成、シード剥離

▶FCボンディング(バンプ付、Face down、ローカルリフロー)

▶樹脂モールド、研削(背面端子露出)

●支持基板剥離、はんだボール搭載

- ✓ コータ or ラミネータ

- ✓ 露光現像装置

- ✓ スパッタ

- ✓ 電解Cuめっき

- ✓ Wet

- ✓ FCボンダー(加熱機構付)

- ✓ モールド装置

- ✓ バックサイドグラインダー

- ✓ 剥離装置

- ✓ ボール搭載機

- ✓ リフロ一炉

- ✓ ダイサー

### 各社プロセスの比較(4)

Face down

Face up

Chip-1st RDL-1st Wafer外形 パネル外形

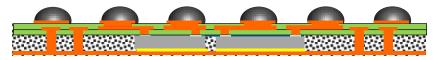

#### プリント基板技術の流用

●Cu**箔上チップ再配列**(Cu**バン**プ付、Face down)

樹脂層積層、平坦化、Cu箔積層

設備

L/S=25/25um

✓ ICマウンター

- ✓ ラミネータ

- ✓ 研削装置

- ●キャリアCu箔剥離、貫通ビア/IC端子開孔、レジスト形成、Cuめっき

- ✓ レーザードリル

- ✓ ラミネータ

- ✓ 露光現像装置

- ✓ 電解Cuめっき

- ✓ Wet

- ソルダーレジスト形成、はんだボール搭載

- はんだボール

- ✓ コータ

- ✓ 露光現像装置

- ✓ ボール搭載機

- ✓ リフロ一炉

●個片化

樹脂層

キャビティ付樹脂層 一

✓ ダイサー

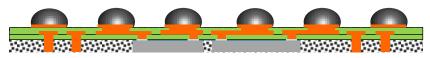

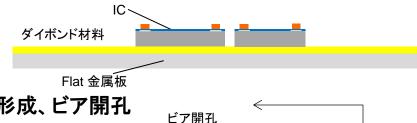

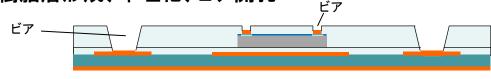

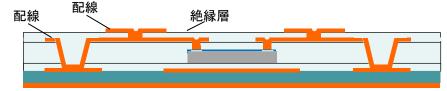

### 各社プロセスの比較(5)

Face down Face up

x積層数

Chip-1st RDL-1st

Wafer外形 パネル外形

#### プリント基板技術の流用

▶金属板上チップ再配列(Cuバンプ付、Face up)

樹脂層形成、ビア開孔

絶縁層

シード成膜、配線形成、シード剥離

設備

✓ ICマウンター

- ✓ ラミネータ

- ✓ レーザードリル

- ✓ ラミネータ

- ✓ コータ

- ✓ 露光現像装置

- ✓ 電解Cuめっき

- ✓ Wet

- ✓ ボール搭載機

- ✓ リフロ一炉

✓ ダイサー

●個片化

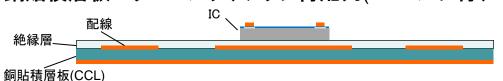

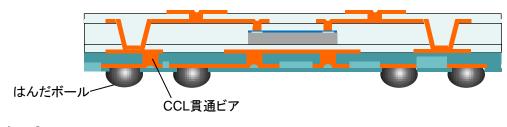

## 各社プロセスの比較(6)

Face down Face up Chip-1st RDL-1st Wafer外形 パネル外形

#### プリント基板技術の流用

●銅貼積層板パターニング、チップ再配列(Cuバンプ付、Face up)

●樹脂層形成、平坦化、ビア開孔

●配線形成 → 絶縁膜形成、ビア開孔 — x積層数

CCL貫通ビア開孔、配線形成、はんだボール搭載

●個片化

### 設備

- ✓ ラミネータ

- ✓ 露光現像装置

- ✓ Wet

- ✓ ICマウンター

- ✓ ラミネータ

- ✓ レーザードリル

- ✓ ラミネータ

- ✓ 露光現像装置

- ✓ 電解Cuめっき

- ✓ Wet

- ✓ レーザドリル

- ✓ 同上(ラミネータ~Wet)

- ✓ コータ

- ✓ ボール搭載機

- ✓ リフロ一炉

- ✓ ダイサー

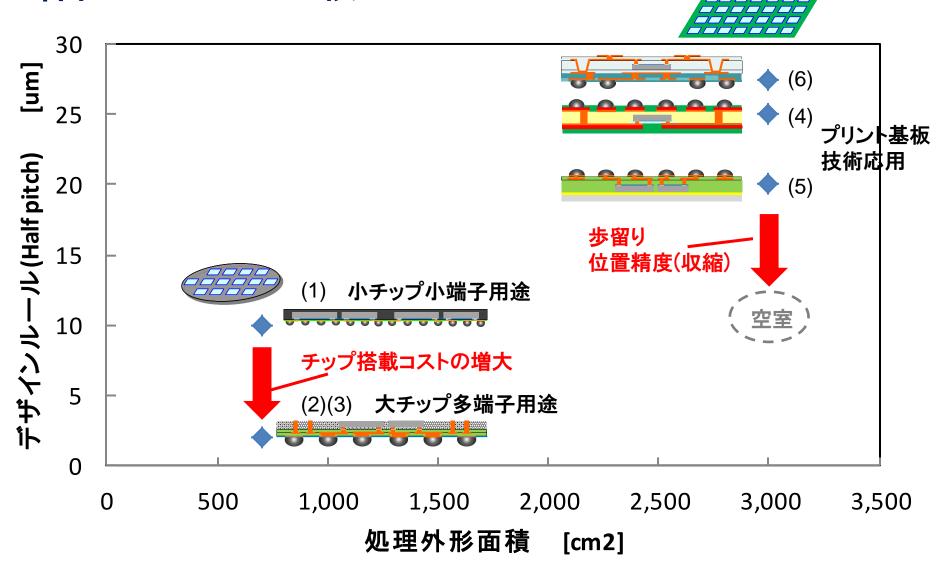

### 各社プロセスの比較

# まとめと今後の活動方針

- IoT・センサーネットワークの台頭とともに、小型で低コストなパッケージが伸長

- もっとも小型なパッケージであるWL-CSPは、これまで端子数の少ないデバイスに適用が限られてきていたが、ファンアウト型構造(FO-WLP)の提案により、1000ピン級のデバイスへの適用が始まりつつある

- ■ファンアウト型WL-CSPの伸長に向けての課題

- 構造・プロセスが各社より提案されており、百花繚乱

- ■大口径化、デザインルール、歩留り、チップ搭載コスト

- ■2016年度の活動予定

- FO-WLPの普及に向けて、共通基盤となる部分を整理して、 ロードマップとして提示していく

- 電子デバイスおよび実装としての新たな取り組み領域として、バイオ系デバイスの調査を開始する

CCL : Copper Clad Laminate

DFR : Dry Film Resist

FBGA : Fine-pitch Ball Grid Array

FC : Flip Chip

FO-WLP : Fan-Out Wafer Level Package

L/S :Line / Space

NCF : Non-Conductive Film

PLP : Panel Level Package

PWB : Printed Wiring Board

QFN : Quad Flat No-lead package

QFP : Quad Flat Package

RDL : Re-Distribution Layer

WL-CSP : Wafer Level Chip Scale Package