# 第 12 章 WG10 モデリング&シミュレーション

## 12-1 はじめに

## 12-1-1 モデリング&シミュレーションのスコープ

半導体ロードマップにおいて、モデリング&シミュレーション(M&S)[1]は、いわゆる Technology Computer Aided Design (TCAD)とほぼ同じ内容を意味する手法・技術である[2]。M&S は、実シリコンの試作において、設計要求とプロセス、材料、動作条件の情報を元に、求めるデバイスのノミナル特性、ばらつき初期特性をタイミングよく予測することである。 従来の 2 次元計算以外に、3 次元化が必須な(例:歪)計算が増え、計算対象(構造作成例:図表 12-)も拡大している。

図表 12-1 M&S における 2 次元、3 次元デバイス・シミュレーション例 (Selete ENEXSS[3]による例) 以下、M&S による寄与をより多く認知されるよう取組んで来た活動の成果を報告し、今後への提起を行う。

### 12-1-2 ITRS M&S 構成 および STRJ WG10 M&S 構成

ITRS M&S 構成を図表 12-2 に示す。また、STRJ WG10 M&S メンバー構成を、図表 12-に示す。

# 欧州 米国

STM-F, Infineon Fraunhofer, NXP + 9 members

INTEL, TI, Synopsys, + 8 members

Japanese TWG 18members

アジア

TSMC, Faraday, Macronix, UMC Hynix, Samsung

| 氏名    | 組織      | 役割      | 主担当領域                       |

|-------|---------|---------|-----------------------------|

| 麻多 進  | NEC EL  | リーダ     | Interconnects               |

| 佐藤 成生 | 富士通     | 国際対応    | Device Modeling             |

| 國清 辰也 | ルネサス    | 国際対応    | Device Modeling             |

| 林 洋一  | 沖       | 幹事      | Design, Manufacturing Yield |

| 木村 光紀 | ソニー     | 委員      | Front End Process Modeling  |

| 青木 伸俊 | 東芝      | 委員      | Front End Process Modeling  |

| 泉 直希  | ローム     | 委員      | Device Modeling             |

| 海本 博之 | 松下      | 委員      |                             |

| 藤原 秀二 | 三洋      | 委員      |                             |

| 西尾 修  | シャープ    | 委員      |                             |

| 中村 光利 | Selete  | コンソーシアム | Numerical Methods           |

| 谷口 研二 | 阪大      | 特別委員    |                             |

| 小谷 教彦 | 広島国際大   | 特別委員    |                             |

| 大野 隆央 | 物質•材料機構 | 特別委員    | Materials Modeling          |

| 佐野 伸行 | 筑波大     | 特別委員    | Device Modeling             |

| 三浦 道子 | 広島大     | 特別委員    | Circuit Element Modeling    |

| 小方 誠司 | アルバック   | SEAJ    | Equipment Modeling          |

| 和田 哲典 | TCAD-I  | 特別委員    | Design, Manufacturing Yield |

図表 12-2 ITRS M&S 構成

下線:2007年度新規

図表 12-3 STRJ M&S の構成

ITRS M&S は、図表 12-2 のように、欧州、米国、アジアの 3 極で構成されている。リーダは Fraunhofer IISBの J. Lorenz である。欧州は SUGERT(Strategic User Group for European Research on TCAD)[4] 等の組織をベースに活動している。日本は、STRJ ベースで、主担当領域を分担しながら、活動している。日本以外のアジア、及び、米国は、特に組織ベースで活動していない。

STRJ M&S メンバー構成は、図表 12-のように、半導体企業、コンソーシアム、大学、SEAJ (Semiconductor Equipment Association of Japan) 装置メーカ、ソフトウエア・ベンダーからなる。 M&S において、ソフトウエア・ベンダーの役割は非常に重要である。 そのため、今年度は、新しく、ソフトウエア・ベンダー所属の特別委員の申請を行い、2007 年 11 月より、専門委員会の承認のもとで、メンバーが 1 名、追加された。

### 12-2 何が技術課題か?

#### 12-2-1 M&S の国際学会の動向

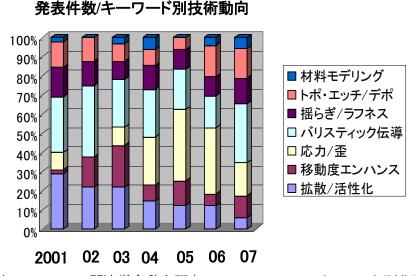

M&S の国際学会としては、International Conference on Simulation of Semiconductor Processes and Devices (SISPAD)が主なものであり、昨年[5]に引き続き技術動向を調べた。2001 年から 2007 年まで 7 年間の発表を調査対象として、分野のキーワードを選び、キーワード別の発表件数を調べた。今年度は、新しく Emerging Research Materials (ERM) が、STRJ に新分科会として誕生しており、M&S としても、ERM のテーマに関連する「材料モデリング」へどのような寄与が出来るかが今年度の懸案であった。そこで、昨年度調査したキーワードの他に、新たに「材料モデリング」をキーワードとして付け加えた調査を行った。結果を図表 12-に示す。

図表 12-4 M&S 関連学会動向調査 SISPAD2001-2007 キーワード別分類

図表 12-のように純粋に「材料モデリング」に関する発表の件数自体はそれ程多くはなかったが、現在の課題と考えられる Metal/High-K 境界の仕事関数の第一原理計算の発表[6]が出始めている。なお、図表 12-は調査したキーワードについての内訳である。カーボンナノチューブ関連は今回、その他に分類し、今回の図表 12-には示していない。

注目の揺らぎ/ばらつきの発表は、トポグラフィやリソグラフィと同程度に発表があり、問題が継続している。 バリスティック伝導の発表も多いが、内容を分析できていない。

応力/歪による移動度エンハンスは、発表件数は一段落したが、インパクトのある課題が残っていると言える。 拡散も発表件数は少ないが、課題が減った訳ではない。 この他、国際学会でのM&S 発表は、IEDM 他、幾つかある。M&S 活用の事例の項で一部を簡単に紹介する。

## 12-2-2 M&S の今年度の課題

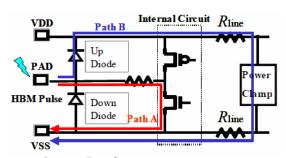

M&S の具体的な課題は、実シリコンの試作において、設計技術者やインテグレーション技術者による様々な要求課題に対し、タイミングよく予測できるかである。予測以外にも故障解析や Tr のロバスト化への支援が求められる。ロバスト化は、例えば、Electro Static Discharge (ESD)など IO 関連の対策へ寄与が重要である。図表 12-に耐 ESD 設計の 1 例[7] を示す。

耐ESD設計 SISPAD2005, 6-1

図表 12-5 耐 ESD 設計の一例

M&S への要求課題として、何が最も問題かは、やはり、デバイス開発において、スケーリングによる性能向上と、MOSFET ロバスト特性の両立は困難になって来ていることである。これは、ゲート酸化膜薄膜化、速度飽和の存在など材料的課題、リソグラフィ等微細加工の困難さがあり、プロセスの寸法の加工揺らぎ、さらに、チャネルが短くなるにつれ、関与する不純物原子数減少に起因する本質的な、ばらつき問題が浮上しているからである。加工揺らぎば、Optical Proximity Correction (OPC)やフェーズシフトマスク、Chemical Mechanical Polishing (CMP)等、ぎりぎりのパターン加工を駆使することや、さまざまなプロセス条件に依存するため、要因が分かりにくいことがネックとなっている。また、不純物の離散性やキャリヤの準弾道性、量子性をも考慮すべきデバイスサイズに到達しつつあるため、ばらつきの起源は非常に複雑である。

このため、M&S では、MOSFET へのばらつき影響の TCAD による調査をしてきたが、未だ、十分でなく、「ばらつきモデリング」は今年度も調査を継続すべき課題である。更に、学会動向に関連して述べたように、M&S として、ERM に関連する「材料モデリング」へどのような寄与が出来るかが懸案であった。

そこで、今年度の STRJ 活動は、2007 ITRS M&S 改訂を確実に実行するとともに、「ばらつきモデリング」を理解し、更に、「材料モデリング」の調査で寄与を行うことを目標とした。

## 12-3 ITRS M&S 課題への取組み

#### 12-3-1 ITRS 2007 M&S 改訂

ITRS 2007 M&S[1]は、2006 年の Table 見直し[8] をもとに、本文の改訂がなされた。主な内容は、次のとおりである。

M&S の困難な技術課題として、項目数は変わらないが、22nm 世代までの 6 分野の Challenge 項目と、22nm 世代以降の 4 分野の Challenge 項目が示された。

2007 年度の M&S の困難な技術課題としては、主に次の 2 点が変更された。第 1 のメッセージとして、「5-100GHz で使用する高周波デバイスと回路モデリング」は、「160GHz に至る領域で使用する高周波用の回路とシステムのモデリング」に変更された。その理由は、2005/2006 年度のままでは記載が古くなったこと、また

SoC や SiP などのシステムレベルのシミュレーションが必須でこれを追記したためである。更に、プロセスばらっきの影響は回路レベルに含めることになった。

第 2 のメッセージとして、「回路パラメータ分散の予測」は、長期的に困難な技術課題(旧版)では最早なく、既に実現されつつある短期の課題に位置付けるように変更したことである。

これに伴い、短期的困難な技術的課題は、特に優先度は付けずに、シミュレーション順の並べた 6 項目の課題とする修正がなされた。

この変更は、WG10 の中で、主にランダムばらつきとシステマティックばらつきの意味と内容を、三浦委員へ問いかけ、議論を行ったことが背景になっている。特に第2点の最初の変更は、三浦委員からITRS M&S のコンパクト・モデルの捉え方が不自然との指摘があり、日本からの修正案として変更されたものである。

ITRS M&S のその他、細かな変更点のまとめは次のとおりである。

短期的困難な技術的課題は、「装置、材料、形状やプロセス、ばらつきを含めたデバイス特性への影響などの、要素および統合モデリング」、「極小ナノスケールデバイスシミュレーション実行機能」、および、「160GHz に至る領域で使用する高周波用の回路とシステムのモデリング」であると修正変更した。その理由は、ばらつきや揺らぎの影響は、すぐにでも解を提供できるように、開発すべきものであるからである。これに関連して、短期的困難な技術課題の「NGL を含むリソグラフィシミュレーション」は、「EUV を含むリソグラフィシミュレーション」と長期的困難な技術課題の「NGL リソグラフィシミュレーション」とに分離した。前者には、multiple exposure/patterning、シミュレーションが追加されている。

FEP から要求されている主な研究分野に関しては、通常の連続体近似の拡散と活性化のモデリングの他に、活性化と拡散の原子的モデリングの項目を加えた。その一方で、エッチングとデポジションに関しては一項にまとめた。デバイスモデリングに対しては、メモリ以外の新規デバイス(non charge-state devices 等)への要求が追加された。

また、M&S リソースが危機的で、協力や配慮が必要なことが、再度、強調して書き込まれている。

モデリングは、本来、基礎的な大学等の研究機関での長期的研究が事前に必要な内容が多く、企業と大学等の研究機関との協力は必須である。また、地道なデータの積み重ねと最新の測定技術があって、初めて検証される技術である。

これに対し、現状、M&Sの人材やリソースが極めて少ない点は危機的な状況であり、大きな課題である。

#### 12-4 STRJ M&S 課題への取組み

# 12-4-1 材料モデリング

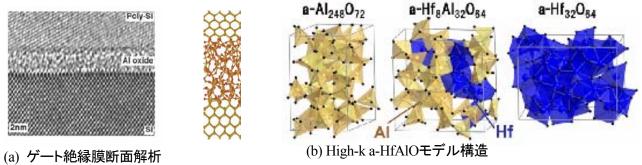

半導体デバイスは、性能向上は、ゲート寸法やゲート酸化膜厚のスケーリングが困難になるにつれ、等価スケーリング(Equivalent scaling)の時代に入っている。すなわち、単に形状的なスケーリングに頼らず、材料上の工夫などがなされ、半導体デバイスに関与する材料の種類は飛躍的に増加している。更に、最も根本のゲートスタック構造が、High-k/メタル構造に変わり始めるまでになっている。このように、新材料への寄与が今まで以上に重要な鍵となってきた。そこで、STRJのWG10では、今年度の新たなテーマとして「材料モデリング」を取り上げ、現状調査から開始することにした。

具体的には、2007年11月30日に、2名の講師による「材料関連モデリング講演会」をJEITA会議室で開催した。最初は、「ナノ・シミュレーション・システムの概要」と題して、物質材料研究機構の大野隆央委員に、全容を講演頂いた。「ナノ・シミュレーション・システムの開発」[9]は2002年から2006年にかけての文科省ITプログラムプロジェクトであり、ナノ・物質・材料(High-k, Low-k)などをテーマとして、プログラムの開発と実用性の証明を行ったもので、その成果プログラムはウェブ[10]で公開され、制限なく、アクセス、ダウンロード可である。その

後の研究は「革新的シミュレーションソフトウエアの研究開発」プロジェクトとして更に続けられている。半導体と の接点は、ゲート絶縁膜の High-k アモルファス構造の解析(図表 12-)などである。手法は、殆どが第一原理の 量子計算であるが、ナノ構造のリーク電流や薄膜の量子伝導などを扱っている。また半導体の界面は、量子計 算と古典連続体計算とのハイブリッド手法で扱う試みが成されている。

図表 12-6 材料モデリング「ナノ・シミュレーション・システム」によるゲート絶縁膜材料の構造計算例

産業界と関連の強いテーマについての計算例については、「誘電体材料設計」と題して、日立基礎研の濱田 智之氏に講演頂いた。

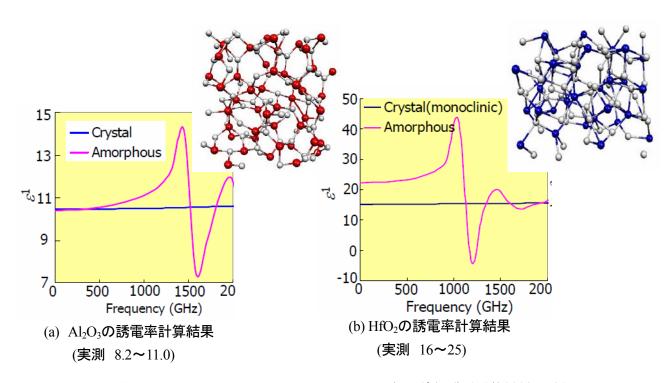

ポイントは、次のような点である。High-k アモルファス HfAlO の構造を先ず計算する。両端組成の Al<sub>2</sub>O<sub>3</sub> や HfO2の誘電率の周波数依存特性の予測結果は、アモルファスHigh-kの低周波側誘電率が、結晶構造の誘電 率に比べ大きい点、その計算値も、実測値とよく対応するという点である(図表 12-)。

この誘電率計算プログラムはHigh-kゲート材料設計用に、十分、実用性のあるプログラム[10]であることが分か った。

図表 12-7 ナノ・シミュレーション・システムによるゲート絶縁膜誘電体材料設計例

## 12-4-2 揺らぎ/ばらつきモデリング

今年度は、ばらつきに対する予測、ばらつき起源の理解を深めるため、WG3 の企画に協力し、WG3 とWG10の合同ピアリングを2007年8月9日に開催し、DFMツールや、特性の抽出方法の状況を調べた。1件は、「デバイスプロセスからのIDFMへのアプローチ」と題して、日本シノプシスの高田秀希氏に講演頂いた。

もう 1 件は、「65nm 世代トランジスタの特性ばらつきと抽出方法」[11]と題してソニーの菅野道博氏に講演頂いた。ばらつき起源を明らかにするには、ばらつきの抽出、定量化手法が重要であることが分かった。

以下は、国際学会 EDM2007 で発表された、揺らぎ/ばらつきモデリングの重要な知見を、要約したものである。

ばらつきのモデルとして、しきい電圧  $V_{TH}$ の標準偏差  $\sigma(V_{TH})$ がチャネル長 Lとチャネル幅 W に関し、通常、Pelgrom plot と呼ばれる次のような関係式が知られている。

$$\sigma(V_{TH}) \equiv A_{VT} \sqrt{\frac{1}{LW}} \tag{1}$$

ここで、 $A_{VT}$  は勾配係数である。これに対し、異なる条件のデバイスに対しても適用可能にするため、電気的ゲート酸化膜厚  $T_{NVV}$ を考慮した次のような関係式が提案された[12]。

$$\sigma(V_{TH}) \equiv B_{VT} \sqrt{\frac{T_{INV}(V_{TH} + 0.1V)}{LW}}$$

(2)

このとき、勾配係数  $B_{VT}$ について、異なる工場や、 $0.35\mu m$  から 65nm までの技術世代の N-FETs や P-FETs の実測データを調べたところ、勾配係数  $A_{VT}$  に比べ条件依存性が極めて小さく、かつ、P-FETs については、 殆ど共通な値が得られることが示された。また、N-FETs についても、ほぼ共通であるが、P-FETs の値よりは若 干大きく、ややズレが見える結果であった。式(2)は、典型的な、基板濃度  $N_{SUB}$ と、空乏層幅  $W_{DEP}$ としきい電圧  $V_{TH}$  および  $\sigma(V_{TH})$  との間になりたつ解析的で、実験的にもよく対応する式から経験的に導いた表式である。このような簡単な機構が実効的に成り立っていることが示された点は、ばらつき解析の進展に明るい材料である。 N-FETs の勾配の振舞いが P-FETs と微妙な違いがある点が、現時点説明されていないが、不純物の性質に 起因するかなど、より詳細なばらつき起源の鍵があるものと考えられる。

#### 12-4-3 M&S 活用の事例

以下も、文献調査結果であるが、M&S活用事例の幾つか紹介する。

最初は、SRAM の揺らぎ/ばらつきに関するものである。文献[13]は、Line Width Roughness (LWR)を考慮し原子レベルのプロセスシミュレーションを行い、LWR 起因で局所ブリッジが見られ、Drain Induced Barrier Lowering (DIBL) が生じることを示した。すなわち、局所ブリッジと関係付けて、SRAM の  $V_{TH}$  分布の非ガウシャン裾の起源をシミュレーションで解明したものである。

次に、文献[14]は、90nm 実デバイスの  $V_{TH}$  分布データをもとに、回路モデルレベルで、リソグラフィや、チップ内電気特性ばらつき、チップとチップ間の Lpoly ばらつき、セルフヒーティングによる温度ばらつき、電源電圧ばらつき、配線間結合など種々のパラメータの回路遅延へのインパクトを見積り報告している。電源変動や、熱のインパクトが大きいなど、ばらつきへの起源が数多くあり、無視できないことが示されている。

また、浅接合デバイス開発へのM&Sの活用が、文献[15]で発表されている。通常のBF₂注入とスパイクアニ

ールで作成した浅接合と、クラスタボロンのミリ秒アニールで作成した浅接合がそれぞれ、どの程度かをシミュレーションで予測し、電子ホログラフィーという手法で、検証を行ったことが発表されている。デバイス設計、観測技術と連携して、シミュレーションが有用な手段であることが示されている。その際、有効なモデリングが不可欠である。

ロードマップ的に今後のデバイスである FinFET (Triple-Gate) あるいは総称して Multi Gate FETと呼ばれる 3 次元デバイスの特性予測が要求されている。

文献[16] はバルク FinFET の離散不純物の揺らぎによる  $V_{TH}$  ばらつきを計算で算出したものである。バルク FinFET の  $V_{TH}$ 標準偏差は、離散不純物起因の $(WL)^{-\gamma}$ 依存性、が通常の  $\gamma$ =0.5 でなく  $\gamma$ =0.75 と大きく、サイズ や形状ばらつきにより敏感であるが、不純物濃度自体は低くおさえられるため、通常の planar MOSFET の計算値に比較して小さいと定量的な予測を行っている。

また、Multi Gate MOSFET の試作例も報告されている。文献[17]ではL80nm やL55nm の電源電圧  $V_{DD}$  ゲート遅延 $t_D$ 特性や、オフ電流  $I_{OFF}$   $-t_D$ 特性などが良好であり、種々の回路設計に適用可能であることが示されている。また、バルクとインテグレートすることも可能で、ESD に強い素子構成が可能であることが述べられている。ただ、Silicon on Insulator (SOI) ベース構造であるため熱的な問題点が残っている。文献[18]では、W213nm,H55nm で約 20Fin, buried oxide (BOX)厚さ 145nm の例について、3 次元の配線構造を考慮した Self-Heating による熱上昇値や熱抵抗値を見積もっている。予想されていることではあるが、SiO2 は、Si に比べ、熱伝導率が 2 桁小(約 1/100)であるため、基板側へ熱が逃げにくく、やはり熱的問題が懸念される結果が報告されている。熱を考慮して、バルクとあわせてインテグレートするデバイス設計が必要になると予測される。

装置シミュレーション、形状シミュレーションについては、今年度WG内で特に新たな内容を追加できなかったが、M&Sに関係して参考となる情報が、SEAJホームページ(http://www.seaj.or.jp)のロードマップ活動報告 [19]にあり、公開されているので参照されたい。

#### 12-5 まとめと今後

2007 年度は、M&S の直面課題は何かを議論し、主に、「揺らぎ/ばらつきモデリング」と「材料モデリング」 に取り組むことを決めた。材料モデリングは、ゲートスタック構造の High-k/メタル材料などで、今後 M&S と密接 に関わるため、現状調査から始めることにした。

2007 年度の ITRS M&S 成果は、ITRS2007M&S の改訂である。主に、困難な技術課題の内容に変更を加えた。具体的には、「回路パラメータ分散の予測」は、長期的に困難な技術課題(旧版)では最早なく、既に実現されつつある短期の課題に位置付けるように変更したことである。これは、日本 WG でばらつきに関し議論した際のメッセージが反映されたものである。

STRJ M&S の活動成果は、揺らぎ/ばらつきのヒアリング、文献調査を行い、ツールや定量化手法、モデリングについて理解を深めたことである。

また、「材料モデリング」の現状に関しては、「ナノ・シミュレーション・システム」としてナノ・物質・材料(High-k, Low-k) などもテーマに含まれるプログラム開発が行われていること、特に、誘電率計算プログラムは High-k ゲート材料設計用に、十分、実用性のあるプログラムであることが分かった。

他に幾つかの、M&Sの活用事例を示し、M&Sの活用を促進する活動を行った。

以下、これまでの M&S 活動についての個人的な考えと今後への提言を簡単に述べる。

これまでのM&S活動で学ぶこと、M&Sの力を実感できるものが多数あった。一方で、M&Sについて認知されなかったことや、M&Sの力が機能する余地がまだまだあると感じている。今後も、出きる限り、M&Sへ寄与したいと考えている。

M&S の今後に対し、提言する。

M&S は、デバイス開発各分野の多くの力の結集で成立っている。ロードマップ活動は、組織枠を超えて横断的に、分野の内外の専門家と接点を持つ機会や、協力の場にもなる。

一方、活動は独断になりやすい面がある。委員は相互チェックすべきである。

活動にはそれなり工数が要る。委員は前もって工数を確保する。

講演会企画やヒアリングを委員が(他WGとも)協力して行う。

過去に捉われず、活動を進める。

## 猫文

- [1] ITRS 2007Edition (2007) <a href="http://www.itrs.net/Links/2007/Home2007">http://www.itrs.net/Links/2007/Home2007</a>.htm

- [2] STRJ Workshop 2007 M&S 活動報告(2008年3月7日) <a href="http://strj-jeita.elisasp.net/">http://strj-jeita.elisasp.net/</a>

- [3] Semiconductor Leading Edge Technologies (Selete) <a href="http://www.selete.co.jp/">http://www.selete.co.jp/</a>

Selete TCAD システムの総称: ENEXSS (Environment for Exploration of Semiconductor Simulation)

- [4] SUGERT http://www.iisb.fraunhofer.de/en/arb\_geb/sugert.htm

- [5]「半導体技術ロードマップ専門委員会(STRJ)2006 年度報告」, pp.203-210, STRJ 2006, http://strj-jeita.elisasp.net/

- [6] P. Prodhomme et. al., SISPAD2007 P34, p.437

- [7] H. Hayashi et. al., SISPAD2005, 6-1

- [8] ITRS 2006 Update (2006) <a href="http://www.itrs.net/Links/2006Update/2006UpdateFinal.htm">http://www.itrs.net/Links/2006Update/2006UpdateFinal.htm</a>

- [9]「戦略的基盤ソフトウェアの開発」プロジェクト http://www.ciss.iis.u-tokyo.ac.jp/fsis/

- [10]ナノシミュレーションソフトウエア情報

http://www.ciss.iis.u-tokyo.ac.jp/fsis/theme/nanoscal/software/index.html

- [11] M Kanno et. al., VL2007, 6A-2

- [12] K. Takeuchi et. al., IEDM2007, 18-1

- [13] M. Miyamura et. al., VL2007 3A.1

- [14] S Nassif et. al., IEDM2007, 21-6

- [15] K. Uejima et. al., IEDM2007, 6-7

- [16] Y. Li et. al., SSDM 2007, B-8-4

- [17] G. Knoblinger et. al., ESSDERC2006

- [18] W. Molzer et. al., ESSDERC2006

- [19] SEAJ ロードマップ活動報告 http://www.seaj.or.jp/activity/roadmap/rm2005report.html